## **LECTURE NOTES ON**

# **DIGITAL SYSTEM DESIGN**

II B.Tech III semester

(Autonomous R18) (2019-20)

Dr. V Vijay, Associate Professor Dr. P Munaswamy, Professor Dr. Lalit Kumar Kaul, Professor

ELECTRONICS AND COMMUNICATIONENGINEERING

**INSTITUTE OF AERONAUTICAL ENGINEERING**

(Autonomous)

Dundigal Hyderabad 500043

# **DIGITAL SYSTEM DESIGN**

**LECTURE NOTES**

#### UNIT I

## LOGIC SIMPLIFICATION AND COMBINATIONAL LOGIC DESIGN

#### **1.1 LOGICAL STATEMENTS AND ARGUMENTS**

Logic is reasoning. A logical statement is one which may be either true or false. There is no scope for ambiguity in a logical statement. The statement 'I am wearing a sweater' will either be true or false. There cannot be any ambiguity in the truth or falsehood of the statement. On the other hand the statement 'When I feel cold I may wear a sweater ' is a statement which has no true or false answer and is quite ambiguous. This statement could well be broken down into several components as a) I shall feel cold if the temperature falls below 15 degrees Celsius or if I have fever b) I shall wear a sweater. The statement in a) has three independent statements i) 'I shall feel cold' will be true if ii) The temperature falls below 15 degrees Celsius or iii) 'I have fever' We may tabulate the statements made above as shown in TABLE 1.1 (a). From this table, we observe all possible answers that the two component statements and the resulting statement can have. We allot symbols to the statements or represent them with switches as follows. If the statements are true we will say the switch is ON and if it is false we may say the switch is off.

- 'A' The temperature is below 15 degrees Celsius

- 'B' I have fever

- 'X' I shall wear a sweater

In TABLE 1.1 (b) the same argument depicted in TABLE 1.1 (a) is shown by representing TRUE with ON and FALSE with OFF.

In the table 1.1 (b) we may consider 'A', 'B', and 'X' as variables which can have one of two values '1' for ON and '0' for OFF. We may further represent table 9.1 (b) as table 9.1 (c) replacing 'ON' with '1' and ' OFF' with '0'.

George Boole symbolised logic i.e., provided symbols to represent logical statements and defined the operators between logical statements to build logical arguments. In the above argument 'A', 'B' and 'X' are Boolean variable and 'OR' is the operation between 'A' and 'B'. X is the resulting statement. We can represent the truth table shown in table 1.1 (c) shown above in the form of a Boolean Expression as (A+B = X) the '+' sign between 'A' and 'B' represents a logical OR operation in Boolean Algebra and not addition.

#### 1.2 LOGIC GATES AND OPERATIONS:- AND, OR & NOT

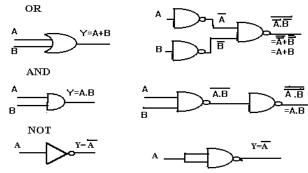

Logic gates are diagrammatic representations of the Logic Operators like 'OR', 'AND' and 'NOT'. The logic gates have one or more inputs and only one output. There are three basic logic gates which perform the three basic logic functions 'OR', 'AND' and 'NOT'. The FIG. 1.1 shows the logic diagram for each of these and also their algebraic symbols. In section 1.1 the truth table for each of these operations has already been shown.

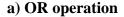

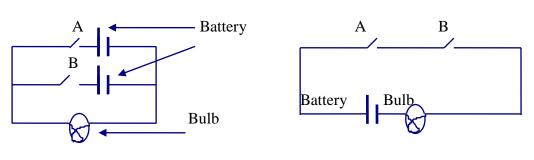

We may show electrical connections of switches to depict the OR and AND operations as in FIG. 1.2(a) and FIG. 1.2 (b). It may be observed that in OR operation the bulb will light if 'A' OR 'B' switch is closed or both are closed. In AND operation the bulb will light only if switches 'A' and 'B' are both closed. FIG. 1.2 ( c) the bulb will light only if switch 'A' is off indicating the 'NOT' function.

#### **1.3 BOOLEAN ALGEBRA**

Boolean algebra provides a symbolic representation of logical arguments which are made up of logical statements. A Boolean expression will have Boolean variables and operators.

From the discussion presented in section 9.1 above we may summarise the following in connection with Boolean Algebra:

a) A Boolean variable can have one of two values '1' or '0'.

b) The only operators permitted in Boolean algebra are 'OR', 'AND' and 'NOT'  $% \left( A^{\prime}\right) =0$

#### **b) AND Operation**

#### c) NOT Operation

#### 1.3.1 Some Basic Postulates of Boolean Algebra

We may enumerate some basic postulates of Boolean Algebra mainly to highlight its

differences with conventional algebra and also to familiarise with symbolic logic.

a) A + 0 = A

b) A+1 = 1, In fact 1 OR anything will be 1 as , as long as one of the inputs for the

OR operation is true the output will be true.

c) A. 0 = 0, 0 AND anything will be 0 as all the inputs for the AND operation must

be true for the output to be true.

d) A.1 = A

e) A+ A'= 1, As if A is 0 , A' will be 1 and if A is 1 ,A' will be 0. 1 OR anything is 1

A+A', is *Tautology* as its value is always true.

f) A. A' = 0, As either a or A' will be 0 as 0 and anything is 0.A.A' is *Fallacy* as its value is always false.

g)

$$A+A=A$$

h)  $A. A = A$

Proof:  $A+A=(A+A).1=(A+A)(A+A')=A+A.A'=A$

Proof:  $A.A=A.A+0=A.A+A.A'=A(A+A')=A.1=A$

i) A.B=B.A

LHS=RHS

j) A+B=B+A

k)

$$(A+B)+C=A+(B+C)$$

l)  $(A.B).C=A.(B.C)$

m) A+ AB = A,

Proof: By truth table

Associative Law

Proof: By truth table

Associative Law

Proof: A+AB= A(1+B) = A. 1= A

$$Absorption Law$$

n) A.(A+B)=A

o) A.(B+C)=AB+AC

p) A+BC=(A+B).(A+C)

$$A+BC=(A+B).(A+C)$$

$$A$$

#### 1.3.2 De'Morgan's Theorems

De'Morgan's Theorems' are useful in changing the forms of Boolean expressions . The two theorems are:

i) The complement of the sum is equivalent to the product of individual complements.

$$(A+B)' = A' \cdot B'$$

Proof: The truth table for the expression is as shown in Table 1.4 below:

From table 1.4 it may be observed that for all possible input combinations of A and B the LHS (Left Hand Side) is the same as RHS (Right Hand Side). The table thus shows the proof of the theorem.

ii) The complement of the product is equal to the sum of individual complements.

(A.B)' = A' + B'

Proof: The truth table for the above expression is shown in Table 1.5

From Table 1.5 it is observed that the LHS and RHS of the expression have the same value for all possible input combinations of 'A' and 'B'. The theorem is thus proved.

1.3.3 Proof of De' Morgan's theorem by induction

I) To prove

$$(A+B)' = A'.B$$

Now as (A+B). A'.B'=0 and (A+B) + A'.B'=1  $X \cdot Y = 0 \quad X + Y = 1$

$$(A+B). A'.B' = A'.B'. (A+B) *ANDing both sides by (A+B) = A'.B'.A + A'.B'.B = A.A'.B + A'.B'.B = 0.B + A'.0 *A.A' = 0 = 0 + 0 = 0 A + B + A'.B' = (A+B+A').(A+B+B') = (1+B).(A+1) = 1 = 1$$

i.e., (A+B)' = A'.B'

II) To prove (A.B)' = A' + B'

Now as

$$A.B(A' + B') = 0$$

and  $A.B + (A'+B') = 1$

$X \cdot Y = 0$   $X + Y = 1$

$X' = Y$

$A B(A' + B') = A B A' + A B B'$

$$A.B(A + B) = A.B.A + A.B.B$$

= A.A'.B + A.B.B'

= 0.B + A.0

= 0 + 0 = 0

$$A.B + (A' + B') = (A' + B' + A). (A' + B' + B)$$

= (1+B').(A' +1)

=1.1 =1

i.e.,

$$(A.B)' = A' + B'$$

## **TABLE 1.4 DE' MORGAN'S THEOREM**

| Α | В | LHS=(A+B)'     | RHS= A' . B'    |

|---|---|----------------|-----------------|

| 0 | 0 | (0+0)'=0'=1    | 0'. 0'= 1.1 = 1 |

| 0 | 1 | (0+1)'= 1' = 0 | 0'.1'= 1.0=0    |

| 1 | 0 | (1+0)'= 1'= 0  | 1'.0'=0.1=0     |

| 1 | 1 | (1+1)'= 1'= 0  | 1'.1'= 0.0 = 0  |

#### **TABLE 1.5 DE'MORGAN'S THEOREM**

| А | В | LHS=(A.B)'     | RHS= A'+. B'    |

|---|---|----------------|-----------------|

| 0 | 0 | (0.0)'= 0' = 1 | 0'+ 0'= 1+1 = 1 |

| 0 | 1 | (0.1)'=0'=1    | 0'+0'= 1+1 = 1  |

| 1 | 0 | (1.0)'=0'=1    | 1'+0'= 0+1 = 1  |

| 1 | 1 | (1+1)'= 1'= 0  | 1'+1'= 0+0 = 0  |

## **1.4 TRUTH TABLES**

While writing truth tables the following points should be remembered:

- a) A truth table with 'n' inputs should have  $2^n$  rows.

- b) All inputs are entered in the left most column of the truth table.

- c) Outputs are entered in the right most column.

- d) The order of inputs should be such that the decimal values obtained from the conversion of bits should be in ascending order row wise.

## **1.5 PRINCIPLE OF DUALITY**

According to this principle, *For every valid expression in Boolean Algebra there exists an equally valid dual expression.* The dual expression can be obtained by following the following three steps:

i) Complement each 0 and 1 (Change the 0's to 1's and 1's to 0's)

ii) Replace each OR (+) sign by AND (.) and each AND (.) sign by OR (+)iii) Leave NOTs unchanged.

The dual of i) X.1 = X is X + 1 = Xii) X + (YZ) is  $X \cdot (Y+Z)$ iii) X.(Y+Z) is X+(Y.Z)

#### 1.6 SIMPLIFICATION OF BOOLEAN (LOGICAL) EXPRESSIONS

We have already seen a number of identities and also the De' Morgans theorems. These can be used in reducing Boolean expressions. The main purpose of reducing Boolean expressions is to implement the logic with the use of minimum hardware. The minimisation of hardware would involve reducing the the number of inputs to a logic gate and also the number of gates without altering the truth table of the expressions. In other words simplifying the logical argument without beating around the bush.

The following examples demonstrate the utility of the identities and De' Morgan's theorems in reducing Boolean expressions:

Reduce the following

i) (xyz+x(yz)'+ xy'z)' = (xyz)'. (x(yz)')'. (xy'z)'\* Removing the outermost complement using = (x'+y'+z')(x'+(yz)'')(x'+y''+z')De'Morgans theorems = (x'+y'+z')(x'+yz)(x'+y+z')= (x'+x'yz+x'y'+0+x'z'+0)(x'+y+z')= x'(1+yz+y'+z')(x'+y+z')= x'(1)(x'+y+z')\* 1 OR anything will be 1 = x' + x'y + x'z'= x'(1+y+z')= x'ii)((x+y+z)'+(xyz)')'= (x+y+z)'' . (xyz)''= (x+y+z).xyz= xyz + xyz + xyz= xyziii) (x (yz)' ((xy)'z(xyz)'+xyz'+x(yz)'))' $= \overline{x yz} (\overline{xy} z . \overline{xyz} + xy \overline{z} + \overline{x yz})$

$$= x yz + xy z \cdot xyz + xy z + x yz$$

$$= \overline{x + yz} + \overline{xy} \overline{z + xyz} \cdot \overline{xy} \overline{z} \cdot x \overline{yz}$$

$$= \overline{x + yz} + (xy + \overline{z} + xyz) \cdot (\overline{x + y} + z) \cdot (\overline{x} + yz)$$

$$= \overline{x + yz + xy + \overline{z}} = \overline{x} + y + \overline{z}$$

\*Using A' + AB= A'+B

## 1.7 CANONICAL FORMS OF BOOLEAN EXPRESSIONS

Canonical forms are standard forms. Let us consider the Boolean expression in three variables whose truth table is shown in table 1.6

From truth table 1.6 we have the Boolean expression :

A'B'C' + AB'C + ABC' + ABC = 1 .....I

In this expression we see that there are four terms and each term contains all the variables which occur in the expression. The expression is true for any of the terms which occur in the expression. Each one of the product terms which occur in the expression having all the variables of the expression is called a min term and the expression itself is in min terms canonical form.

From the same truth table 1.6 we can also write the following expression :

A'B'C+A'BC'+A'BC+AB'C'=0 .....II

Normally the Boolean expression is written for a true value. If we commplement both sides of expression II we have:

(A'B'C+A'BC'+A'BC+AB'C')' = 0'

or (A+B+C')(A+B'+C)(A+B'+C')(A'+B+C) = 1 \*By using De'Morgan's theorem ....III

Scrutinising expression III we see that each sum term in the product of sums has all the three variables of the expression. Each one of these terms is called a max term and the expression III is an expression in max terms canonical form or Product Of Sums (POS) canonical form .

#### 1.8 THE THREE VARIABLE KARNAUGH MAP

From the truth table we can make a Karnaugh Map, these maps are very useful in reducing Boolean expressions as we shall see shortly. While making a Karnaugh map

it must be ensured that in adjacent cells of the map only one variable should change. The Karnaugh map for the truth table 1.6 is shown in FIG. 1.3

#### FIG 1.3 KARNAUGH MAP FOR TRUTH TABLE 9.6

The expression is A'B'C' + AB'C + ABC' + ABC = 1

|      | C'    | С     |

|------|-------|-------|

| A'B' | 1 (0) | 0 (1) |

| A'B  | 0 (2) | 0 (3) |

| AB   | 1 (6) | 1 (7) |

| AB'  | 0 (4) | 1 (5) |

In FIG 1.3 the truth values in each cell are reproduced from the truth table 1.6 and within parenthesis the cell numbers are marked for ready reference. We may also observe that only one variable varies in adjacent cells. The Karnaugh maps may be folded from left to right and also from top to bottom, thus cells (0) and (1) are adjacent and cells (0) and (4) are also adjacent. Cells (1) and (5) are adjacent but cells (0) and (5) are not adjacent. Let us take cell (0) in this the variables are A'B'C' and in cell (5) the variable are AB'C thus A and C change in these two cells so they are not adjacent.

Let us now consider the two adjacent cells (6) and (7). Considering these two cells alone we get the expression :

ABC'+ABC = 1 i.e., AB(C+C') = 1, i.e., AB = 1. The variable C which changes in these two cells gets eliminated. We can thus presume that if we have a pair of 1's in adjacent cells we can eliminate one variable. FIG. 1.4 shows the combinations which can be made to reduce the Boolean expression I.

We have an isolated 1 in the cell A'B'C' and two pairs in cells ABC', ABC and ABC, AB'C as shown enclosed in boxes.

The reduced expression thus becomes A'B'C'+AB+AC=1..

From the Karnaugh map 1.4 we also get expression II, i.e., A'B'C+A'BC'+A'BC'=0. We may consider the adjacent cell 0's. We see

that we have 0's in adjacent cells (1),(3) and (2)(3) and there is an isolated 0 in cell 4. Eliminating the changing variable in adjacent cells we have A'C+A'B+AB'C'=0. Complementing both sides of this expression we get the expression (A+C')(A+B')(A'+B+C) = 1. Thus from the same Karnaugh map we can get two reduced expressions which are true, one in a Sum of Products (SOP) form and another in a Product of Sums(POS) form.

The expression

A'B'C' + AB'C + ABC' + ABC = 1 as  $f(A,B,C) = \sum (0, 5, 6,7)$  i.e. Sum of Products of cell numbers 0, 5, 6 and 7

and the expression

(A+B+C')(A+B'+C)(A+B'+C')(A'+B+C) = 1 as f(A, B, C) = -7(1, 2, 3, 4) i.e., the Product of Sums of cells 1, 2, 3 and 4..

#### **1.8 THE FOUR VARIABLE KARNAUGH MAP**

The Karnaugh maps in theory can be drawn for Boolean expressions with any number of variables. We shall however restrict or discussions up-to four variables. In section 1.7 we had restricted ourselves only to forming pairs with adjacent cells. We shall soon see that we can combine adjacent cells making groups of  $2^n$  where n is an integer. Thus we can combine adjacent cells  $2^2 = 4$  cells or **quads**  $2^3 = 8$  cells called **Octets** etc. A quad will eliminate two variables, an Octet will eliminate three variables as we shall soon see.

Let us consider the Boolean expression:

The expression in sum of products canonical form is:

A'B'C'D'+A'B'C'D+A'B'CD+A'BC'D'|+A'BCD+AB'C'D'+AB'C'D+AB'CD+ ABC'D' = 1 .....I

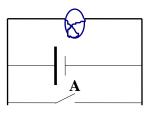

Table 1.7 A shows the truth table for the expression alongwith the cell numbers and min terms represented by each cell. FIG.1.5 shows the Karnaugh map for the expression with cell numbers given in parenthesis. FIG. 1.5A shows that two quads

'a' and 'b' can be formed by combining adjacent cells with a truth value of '1' and a pair 'c' can also be formed with truth value '1' in adjacent cells. Let us now consider the two quads 'a' and 'b' and the pair 'c' individually.

From quad 'a' we get:

A'B'C'D'+A'BC'D'+ABC'D'+AB'C'D' = 1OR A'C'D'(B'+B)+AC'D'(B+B')=1OR A'C'D'+AC'D'=1OR C'D'(A'+A)=1OR C'D' = 1.....i

## Note that in this quad the variables A and B change and hence can be eliminated.

The truth table for the expression is shown in table 1.7

TABLE 1.7 TRUTH TABLE FOR F (A, B, C, D) =

(0,1,3,4,7,8,9,11, 12)

| Α | В | С | D | F | CELL NO. | MIN TERM |

|---|---|---|---|---|----------|----------|

| 0 | 0 | 0 | 0 | 1 | 0        | A'B'C'D' |

| 0 | 0 | 0 | 1 | 1 | 1        | A'B'C'D  |

| 0 | 0 | 1 | 0 | 0 | 2        | A'B'CD'  |

| 0 | 0 | 1 | 1 | 1 | 3        | A'B'CD   |

| 0 | 1 | 0 | 0 | 1 | 4        | A'BC'D'  |

| 0 | 1 | 0 | 1 | 0 | 5        | A'BC'D   |

| 0 | 1 | 1 | 0 | 0 | 6        | A'BCD'   |

| 0 | 1 | 1 | 1 | 1 | 7        | A'BCD    |

| 1 | 0 | 0 | 0 | 1 | 8        | AB'C'D'  |

| 1 | 0 | 0 | 1 | 1 | 9        | AB'C'D   |

| 1 | 0 | 1 | 0 | 0 | 10       | AB'CD'   |

| 1 | 0 | 1 | 1 | 1 | 11       | AB'CD    |

| 1 | 1 | 0 | 0 | 1 | 12       | ABC'D'   |

| 1 | 1 | 0 | 1 | 0 | 13       | ABC'D    |

| 1 | 1 | 1 | 0 | 0 | 14       | ABCD'    |

| 1 | 1 | 1 | 1 | 0 | 15       | ABCD     |

|   |   |   |   |   |          |          |

#### FIG 1.5 KARNAUGH MAP

| C'D' |       | C'D   | CD    | CD'   |

|------|-------|-------|-------|-------|

| A'B' | 1 (0) | 1(1)  | 1 (3) | 0(2)  |

| A'B  | 1(4)  | 0(5)  | 1(7)  | 0(6)  |

| AB   | 1(12) | 0(13) | 0(15) | 0(14) |

| AB'  | 1(8)  | 1(9)  | 1(11) | 0(10) |

\*The cell numbers are marked in parenthesis

## FIG. 1.5 A

Reproducing the Karnaugh map without cell nos. and combining adjacent cells

From quad 'b' (Obtained by folding or wrapping around the Karnaugh map) we get:

A'B'C' D + A'B'CD + AB' C'D + AB' CD = 1OR A'B'D(C'+C) + AB'D(C'+C) = 1OR A'B'D + AB'D = 1OR B'D(A'+A) = 1OR B'D = 1 .....ii Note that in this quad the variables A and C change and can be eliminated

From the pair 'c' we get:

A'B'CD + A'BCD = 1OR A'CD(B'+B) = 1OR A'CD = 1 .....iii Note that in this pair only the variable B changes and can be eliminated.

From i, ii and iii above we get:

C'D' + B'D + A'CD = 1....(X)

The original expression

(

A'B'C'D'+A'B'C'D+A'BC'D'+A'BCD+A'BCD+AB'C'D'+AB'C'D+AB'CD+A BC'D' = 1) reduces to the expression (C'D' + B'D + A'CD = 1) with the help of the Karnaugh map.

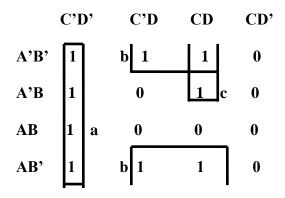

The Karnaugh map of FIG. 1.5A is reproduced in FIG. 1.5B. We shall now reduce the expression to obtain a simplified expression in product of sums form.

#### С'D' C'D CD CD' **A'B'** 1 1 1 A'B 1 1 0 b AB 1 0 C AB' 1 1 1

FIG.1. 5B SIMPLIFICATION FOR POS FORM

Combining the 0's we get the following simplified expression:

CD' (FROM QUAD 'A') + BC'D (FROM PAIR 'b') + ABD (from pair 'c') = 0 complementing both sides we have:

CD' + BC'D + ABD = 0OR (CD')'. (BC'D)'. (ABD)' = 1 OR (C' + D). (B'+C+D'). (A'+B'+D') = 1 .....(Y)

Note : You may verify that if all the cells in a Karnaugh map contain a 1 then the sum of all min terms will be 1 and the Boolean expression will be true for all possible input combinations. Similarly if all cells are 0 then the output is false for possible input combinations.

## LOGIC GATES

We have seen the basic logic gates, namely, OR AND and NOT in section 1.2 in chapter I

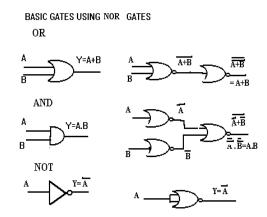

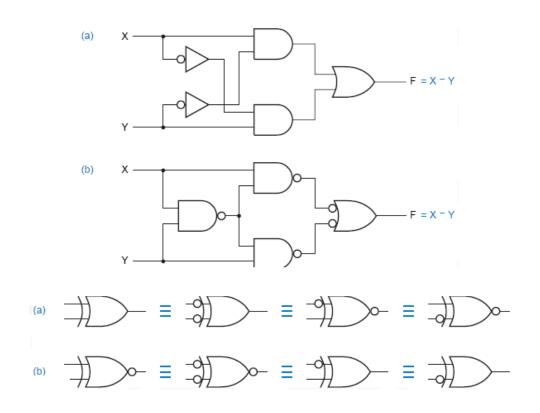

With the help of the basic logic gates shown in the FIG. 1.1 some combinational gates as shown in FIG. 2.1 are built which are very commonly used. These gates and their truth tables are shown in FIG. 2.1. The NOT gate following the OR gate results in a NOR gate. The NOT gate following the AND gate results in a NAND gate. The combination of basic gates required to form the EXCLUSIVE OR (EX-OR) gate is also shown in FIG. 2.1. The EX-OR gate is very useful and is also used for constructing the adders as will be shown in the next section. The EX-OR gate gives a true output if the inputs are not similar. For similar inputs the EX-OR gate gives a false output. In the truth tables shown in FIG. 2.1 '1' represents true and '0' represents false . The EXCLOSIVE NOR (EX-NOR) gate gives a true output for similar inputs. The NAND gates and NOR gates are called universal building blocks as any logic can be implemented by using either NAND gates alone or NOR gates alone, as will be shown later in this chapter.

#### 2.2 USING LOGIC GATES TO ADD BITS

#### Adding two bits

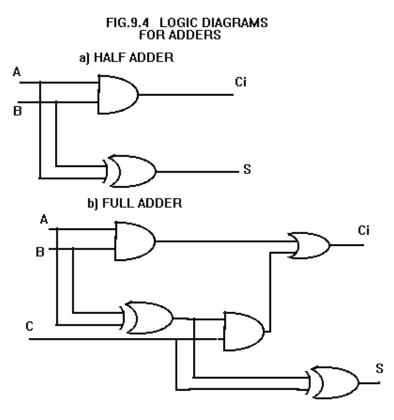

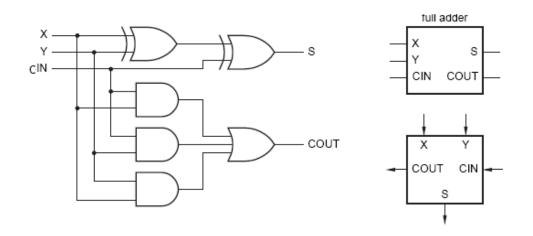

We can use a combination of logic gates to add two bits. Let us say that the two bits to be added are 'A' and 'B'. Each of these bits may have a value of '0' or '1'. Taking all possible combinations of 'A' and 'B' their sum in binary will be as shown in TABLE 2.1 below: The logic diagram for the implementation of the half adder is shown in FIG. 2.2 (a)

#### **Adding three bits**

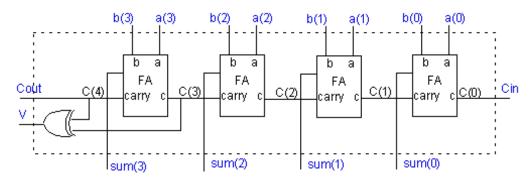

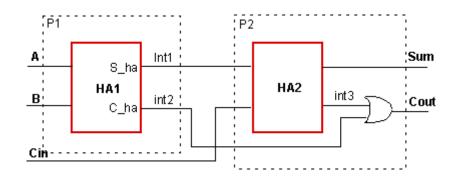

The logic diagram for adding three bits (full adder) is shown in FIG 2.2 (b) and the truth table for this logic diagram is shown in TABLE 2.2. We may observe from the logic diagram of the full adder shown in FIG. 2.2 (b) that if two half adders are cascaded and the carry outputs of the two half adders input to an OR gate for generating the carry we can add one more bit. Similarly if a number of half adders are cascaded we can add more and more bits. In an Integrated Circuit (IC) a number of half adders of a number of bits.

You may verify from the truth table of the full adder that the Boolean expressions for the carry 'Ci' and the sum 'S' are as follows:

## Ci = A'BC+AB'C+ABC'+ABC S = A'B'C+A'BC'+AB'C'+ABC

We can use logic circuits for adding the complement of negative numbers to perform subtraction. Since multiplication is repeated addition and division is repeated subtraction, all arithmetic operations can be performed by using logic gates.

FIG. 9.5 UNIVERSAL BUILDING BLOCKS

a) BASIC GATES USING NAND GATES

#### FIG. 9.6 UNIVERSAL BUILDING BLOCKS

#### **1.3 UNIVERSAL BUILDING BLOCKS**

In section 2.1 above it was mentioned that with the help of 'NAND' gates alone or 'NOR' gates alone any logic can be implemented. The basic gates are 'OR', 'AND' and 'NOT'. It therefore follows that if these three basic gates can be implemented , any logic can be implemented. In FIG. 2.3A implementation of the basic gates by 'NAND' gates is shown. and in FIG. 2.3B implementation of the basic gates by 'NOR' gates is shown.

The NAND gates alone could be used to implement any logic as it is possible to implement the basic gates (OR, AND and NOT) using NAND gates. Similarly NOR gates alone could be used to implement any logic. Production of only one type of gates would be more convenient than production of an assortment of gates. The NAND gates are universal building blocks.

## 1.4 USING LOGIC GATES TO IMPLEMENT LOGICAL ARGUMENTS

We have seen in section 2.2 how logic gates could be used to perform arithmetic functions. The logic gates could also be used to implement logical arguments. Let us say I have two friends, A and B. B plays badminton, A plays tennis and all of us play cricket. I have a holiday and I invite both my friends. Four situations could arise as follows:

- i ) If non of my friends come I shall read a book.

- ii ) If only B accepts my invitation I shall play badminton with him.

- iii) If only A accepts the invitation I shall play tennis with him.

- iv) If both come we shall all play cricket.

FIG. 2.4 shows how this argument can be implemented using Logic gates.

In FIG. 2.4 there are two inputs 'A' and 'B'. These inputs are fed two AND gates either in complemented or uncomplemented form . If the inputs are uncomplemented they are represented by '1' (True) and if they are in uncomplemented form they are represented by '0'(false). One of the four outputs of the AND gates will be true depending whether the inputs are true or false. If 'A' and 'B' are both absent, then 'A' and 'B' will both be '0' and their complements '1', so the top most AND gate will give a True output and all other AND gates will give a False output. Under these conditions I shall read a book. Proceeding similarly for other values of 'A' and 'B' as shown in the truth table one of the output paths will be selected.

Two inputs enable us to select from 4 output paths. Three inputs will enable selection from among 8 output paths. for selection from among '2n' output paths we will require n inputs.

#### **UNIT II**

#### **MSI DEVICES**

#### **Combinational Logic Design**

#### **Decoders**

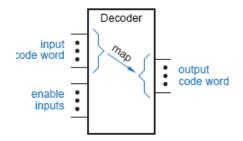

A decoder is a multiple-input, multiple-output logic circuit that converts coded inputs into coded outputs, where the input and output codes are different. The input code generally has fewer bits than the output code, and there is a one-to one mapping from input code words into output code words. In a one-to-one mapping, each input code word produces a different output code word. The general structure of a decoder circuit is shown in Figure. The enable inputs, if present, must be asserted for the decoder to perform its normal mapping function. Otherwise, the decoder maps all input code words into a single, "disabled," output code word. The most commonly used input code is an *n*-bit binary code, where an *n*-bit word represents one of 2*n* different coded values, normally the integers from 0 through  $2n \Box 1$ . Sometimes an *n*-bit binary code is truncated to represent fewer than 2n values. For example, in the BCD code, the 4-bit combinations 0000 through 1001 represent the decimal digits 0-9, and combinations 1010 through 1111 are not used. The most commonly used output code is a 1-out-ofm code, which contains m bits, where one bit is asserted at any time. Thus, in a 1-outof-4 code with active-high outputs, the code words are 0001, 0010, 0100, and 1000. With active-low outputs, the code words are 1110, 1101, 1011, and 0111.

DECODER

#### **Binary Decoders**

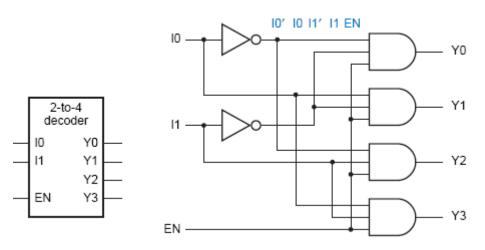

The most common decoder circuit is an *n*-to-2*n* decoder or *binary decoder*. Such a decoder has an *n*-bit binary input code and a 1-out-of-2*n* output code. A binary decoder is used when you need to activate exactly one of 2*n* outputs based on an *n*-bit input value.For example, Y*i* equal to 1 if and onlyif the input code word is the

binary representation of *i* and the *enable input* EN is 1. If EN is 0, then all of the outputs are 0. A gate-level circuit for the 2-to-4 decoder is shown in Figure. Each AND gate *decodes* one combination of the input code word I1,I0. The binary decoder's truth table introduces a "don't-care" notation for input combinations. If one or more input values do not affect the output values for some combination of the remaining inputs, they are marked with an "x" for that input combination. This convention can greatly reduce the number of rows in the truth table, as well as make the functions of the inputs more clear.

2-4 DECODER

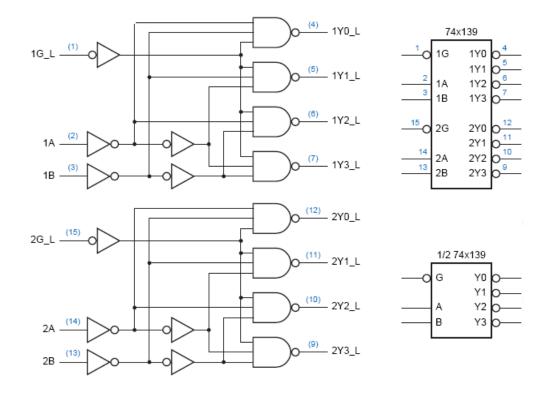

## The 74x139 Dual 2-to-4 Decoder

Two independent and identical 2-to-4 decoders are contained in a single MSI part, the 74x139. The gate-level circuit diagram for this IC is shown in Figure. Notice that the outputs and the enable input of the '139 are active-low. Most MSI decoders were originally designed with active-low outputs, since TTL inverting gates are generally faster than non inverting ones. Also notice that the '139 has extra inverters on its select inputs. Without these inverters, each select input would present three AC or DC loads instead of one.

A logic symbol for the 74x139 is shown in Figure. Notice that all of the signal names inside the symbol outline are active-high (no "\_L"), and that inversion bubbles indicate active-low inputs and outputs. Often a schematic may use a generic symbol for just one decoder, one-half of a '139, as shown in (c). In this case, the assignment of the generic function to one half or the other of a particular '139 package can be deferred until the schematic is completed.

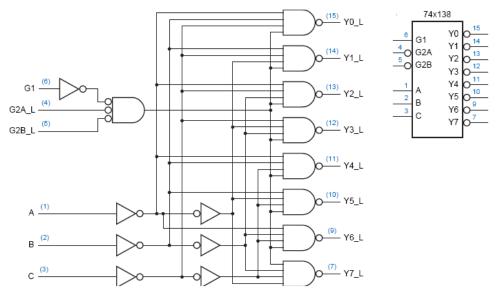

## The 74x138 3-to-8 Decoder

Like the 74x139, the 74x138 has active-low outputs, and it has three enable inputs (G1, /G2A, /G2B), all of which must be asserted for the selected output to be asserted. The logic function of the '138 is straightforward—an output is asserted if and only if the decoder is enabled and the output is selected. Thus, we can easily write logic equations for an internal output signal such as Y5 in terms of the internal input signals: However, because of the inversion bubbles, we have the following relations between internal and external signals: Therefore, if we're interested, we can write the following equation for the external output signal Y5\_L in terms of external input signals:

On the surface, this equation doesn't resemble what you might expect for a decoder, since it is a logical sum rather than a product. However, if you practice bubble-to-

bubble logic design, you don't have to worry about this; you just give the output signal an active-low name and remember that it's active low when you connect it to other inputs.

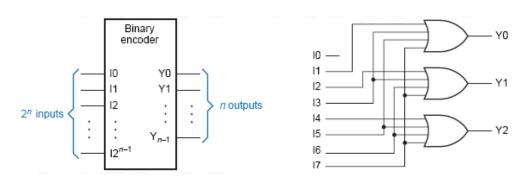

### Encoders

A decoder's output code normally has more bits than its input code. If the device's output code has *fewer* bits than the input code, the device is usually called an *encoder*. For example, consider a device with eight input bits representing an unsigned binary number, and two output bits indicating whether the number is prime or divisible by 7. We might call such a device a lucky/prime encoder. Probably the simplest encoder to build is a 2n-to-n or *binary encoder*. As shown in Figure, it has just the opposite function as a binary *de*coder— its input code is the 1-out-of-2n code and its output code is n-bit binary.

#### Binary Encoder

## **Priority Encoders**

The 1-out-of-2n coded outputs of an *n*-bit binary decoder are generally used to control a set of 2n devices, where at most one device is supposed to be active at any time.

Conversely, consider a system with 2*n inputs*, each of which indicates a request for service, as in Figure. This structure is often found in microprocessor input/output subsystems, where the inputs might be interrupt requests. In this situation, it may seem natural to use a binary encoder of the type shown in Figure to observe the inputs and indicate which one is requesting service at any time. However, this encoder works properly only if the inputs are guaranteed to be asserted at most one at a time. If multiple requests can be made simultaneously, the encoder gives undesirable results. For example, suppose that inputs I2 and I4 of the 8-to-3 encoder are both 1; then the output is 110, the binary encoding of 6. Either 2 or 4, not 6, would be a useful output in the preceding example, but how can the encoding device decide which? The solution is to assign *priority* to the input lines, so that when multiple requests are asserted, the encoding device produces the number of the highest-priority requestor. Such a device is called a *priority encoder*.

#### The 74x148 Priority Encoder

The 74x148 is a commercially available, MSI 8-input priority encoder. Its logic symbol is shown in Figure and its schematic is shown in Figure. The main difference between this IC and the "generic" priority encoder of Figure 5-47 is that its inputs and outputs are active low. Also, it has an enable input, EI\_L, that must be asserted for any of its outputs to be asserted. The complete truth table is given in Table 5-22. Instead of an IDLE output, the '148 has a GS L output that is asserted when the device is enabled and one or more of the request inputs is asserted. The manufacturer calls this "Group Select," but it's easier to remember as "Got Something." The EO L signal is an enable *output* designed to be connected to the EI\_L input of another '148 that handles lower-priority requests. /EO is asserted if EI\_L is asserted but no request input is asserted; thus, a lower-priority '148 may be enabled. Figure 5-50 shows how four 74x148s can be connected in this way to accept 32 request inputs and produce a 5-bit output, RA4-RA0, indicating the highest-priority requestor. Since the A2-A0 outputs of at most one '148 will be enabled at any time, the outputs of the individual '148s can be ORed to produce RA2–RA0. Likewise, the individual GS\_L outputs can be combined in a 4-to-2 encoder to produce RA4 and RA3. The RGS output is asserted if any GS output is asserted.

**Truth table for a 74x148 8-input priority encoder. Inputs Outputs** /EI /I0 /I1 /I2 /I3 /I4 /I5 /I6 /I7 /A2 /A1 /A0 /GS /EO 1 x x x x x x x x 1 1 1 1 1

## **Multiplexers**

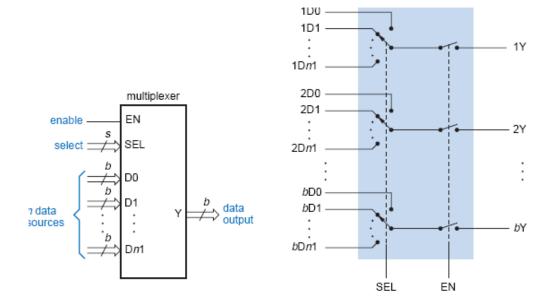

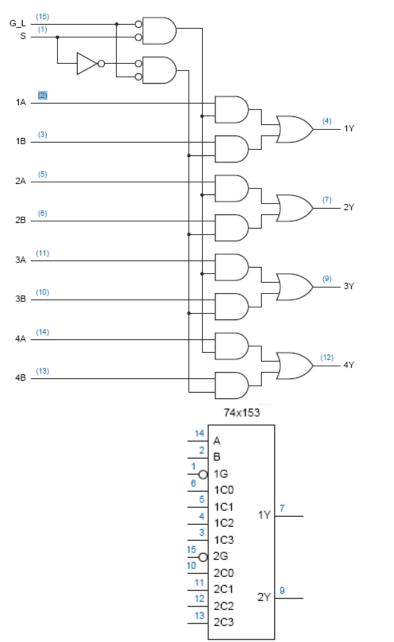

A *multiplexer* is a digital switch—it connects data from one of *n* sources to its output. Figure shows the inputs and outputs of an *n*-input, *b*-bit multiplexer. There are *n* sources of data, each of which is *b* bits wide, and there are *b* output bits. In typical commercially available multiplexers,  $n \approx 1, 2, 4, 8$ , or 16, and  $b \approx 1, 2$ , or 4.

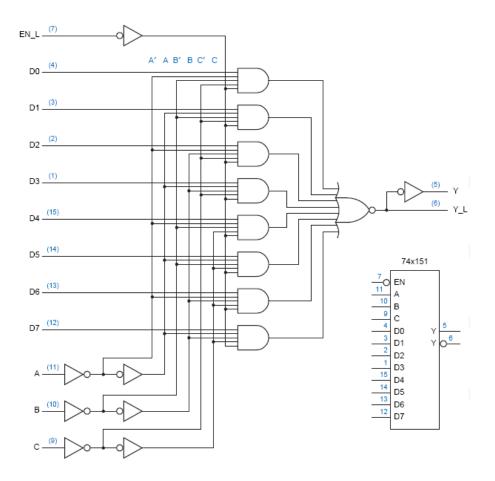

#### **Standard MSI Multiplexers**

The sizes of commercially available MSI multiplexers are limited by the number of pins available in an inexpensive IC package. Commonly used muxes come in 16-pin packages. At one extreme is the 74x151, shown in Figure, which selects among eight 1-bit inputs. The select inputs are named C, B, and A, where C is most significant numerically. The enable input EN\_L is active low; both active-high (Y) and active-low (Y\_L) versions of the output are provided.

#### **EXCLUSIVE OR Gates and Parity Circuits** EXCLUSIVE OR and EXCLUSIVE NOR Gates

An Exclusive OR (XOR) gate is a 2-input gate whose output is 1 if exactly one of its inputs is 1. Stated another way, an XOR gate produces a 1 output if its inputs are different. An Exclusive NOR (XNOR) or Equivalence gate is just the opposite—it produces a 1 output if its inputs are the same.

The logic symbols for XOR and XNOR functions are shown in Figure. There are four equivalent symbols for each function. All of these alternatives are a consequence of a simple rule: Any two signals (inputs or output) of an XOR or XNOR gate may be complemented without changing the resulting logic function. In bubble-to-bubble logic design, we choose the symbol that is most expressive of the logic function being performed.

## **Parity Circuits**

As shown in Figure *n* XOR gates may be cascaded to form a circuit with  $n \square \square 1$  inputs and a single output. This is called an *odd-parity circuit*, because its output is 1 if an odd number of its inputs are 1. The circuit in (b) is also an odd parity circuit, but it's faster because its gates are arranged in a tree-like structure. If the output of either circuit is inverted, we get an *even-parity circuit*, whose output is 1 if an even number of its inputs are 1.

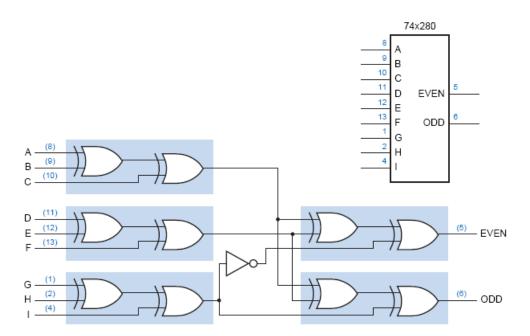

## The 74x280 9-Bit Parity Generator

Rather than build a multibit parity circuit with discrete XOR gates, it is more economical to put all of the XORs in a single MSI package with just the primary inputs and outputs available at the external pins. The 74x280 9-bit parity generator, shown in Figure, is such a device. It has nine inputs and two outputs that indicate whether an even or odd number of inputs are 1.

## **Parity-Checking Applications**

Error-detecting codes use an extra bit, called a parity bit, to detect errors in the transmission and storage of data. In an even parity code, the parity bit is chosen so that the total number of 1 bits in a code word is even. Parity circuits like the 74x280 are used both to generate the correct value of the parity bit when a code word is stored or transmitted, and to check the parity bit when a code word is retrieved or received.

## **Comparators**

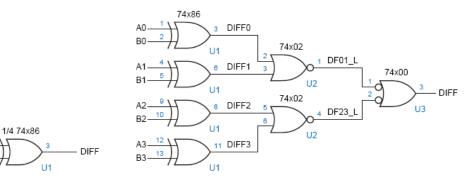

Comparing two binary words for equality is a commonly used operation in computer systems and device interfaces. A circuit that compares two binary words and indicates whether they are equal is called a *comparator*. Some comparators interpret their input words as signed or unsigned numbers and also indicate an arithmetic relationship (greater or less than) between the words. These devices are often called *magnitude comparators*.

## **Comparator Structure**

EXCLUSIVE OR and EXCLUSIVE NOR gates may be viewed as 1-bit comparators. Figure shows an interpretation of the 74x86 XOR gate as a 1-bit comparator. The active-high output, DIFF, is asserted if the inputs are different. The outputs of four

XOR gates are ORed to create a 4-bit comparator in (b). The DIFF output is asserted if any of the input-bit pairs are different. Given enough XOR gates and wide enough OR gates, comparators with any number of input bits can be built.

## Adders, Subtractors, and ALUs

B0

Addition is the most commonly performed arithmetic operation in digital systems. An *adder* combines two arithmetic operands using the addition rules. The addition rules and therefore the same adders are used for both unsigned and two's-complement numbers. An adder can perform subtraction as the addition of the minuend and the complemented (negated) subtrahend, but you can also build *subtractor* circuits that perform subtraction directly.

#### Half Adders and Full Adders

The simplest adder, called a *half adder*, adds two 1-bit operands X and Y, producing a 2-bit sum. The sum can range from 0 to 2, which requires two bits to express. The low-order bit of the sum may be named HS (half sum), and the high-order bit may be named CO (carry out). To add operands with more than one bit, we must provide for carries between bit positions. The building block for this operation is called a *full adder*. Besides the addend-bit inputs X and Y, a full adder has a carry-bit input, CIN.

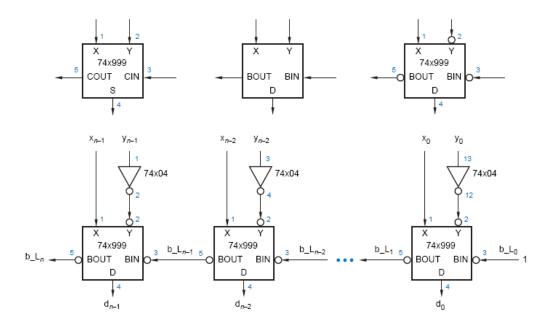

#### **Subtractors**

A binary subtraction operation analogous to binary addition.. A *full subtractor* handles one bit of the binary subtraction algorithm, having input bits X (minuend), Y (subtrahend), and BIN (borrow in), and output bits D (difference) and BOUT (borrow out).

## **MSI Arithmetic and Logic Units**

An *arithmetic and logic unit (ALU)* is a combinational circuit that can perform any of a number of different arithmetic and logical operations on a pair of *b*-bit operands. The operation to be performed is specified by a set of function-select inputs. Typical MSI ALUs have 4-bit operands and three to five function select inputs, allowing up to 32 different functions to be performed. Figure is a logic symbol for the 74x181 4-bit ALU. Note that the identifiers A, B, and F in the table refer to the 4-bit words A3– A0, B3–B0, and F3–F0; and the symbols .  $\Box$  and  $\Box$   $\Box$  refer to logical AND and OR operations. The 181's M input selects between arithmetic and logical operations. When M = $\Box$ 1, logical operations are selected, and each output Fi is a function only of the corresponding data inputs, Ai and Bi. No carries propagate between stages, and the CIN input is ignored. The S3–S0 inputs select a particular logical operation; any of the 16 different combinational logic functions on two variables may be selected.

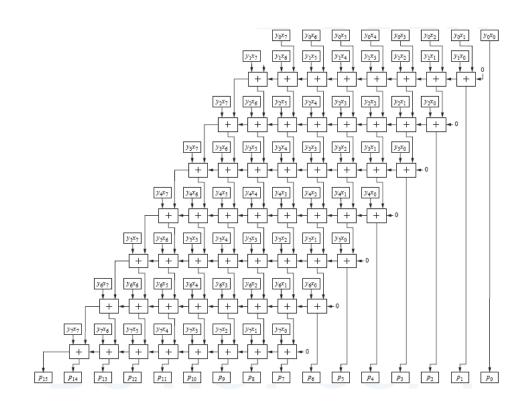

## **Combinational Multipliers**

**Combinational Multiplier Structures**

Although the shift-and-add algorithm emulates the way that we do paper-and-pencil multiplication of decimal numbers, there is nothing inherently "sequential" or "time dependent" about multiplication. That is, given two *n*-bit input words X and Y, it is possible to write a truth table that expresses the 2n-bit product  $P = \Box XY$  as a combinational function of X and Y. A combinational multiplier is a logic circuit with such a truth table. Most approaches to combinational multiplication are based on the paperand- pencil shift-and-add algorithm. Figure illustrates the basic idea for an 8\*8 multiplier for two unsigned integers, multiplicand X = x7x6x5x4x3x2x1x0 and multiplier Y = y7y6y5y4y3y2y1y0. We call each row a *product component*, a shifted multiplicand that is multiplied by 0 or 1 depending on the corresponding multiplier bit. Each small box represents one product-component bit *yixi*, the logical AND of multiplier bit *yi* and multiplicand bit *xj*. The product  $P = p15p14 \dots p2p1p0$  has 16 bits and is obtained by adding together all the product components. Figure shows one way to add up the product components. Here, the product-component bits have been spread out to make space, and each "+" box is a full adder equivalent to Figure. The carries in each row of full adders are connected to make an 8-bit ripple adder. Thus, the first ripple adder combines the first two product components to product the first partial product. Subsequent adders combine each partial product with the next product component.

## UNIT III Sequential Logic Design

## **Latches and Flip-Flops**

#### **SSI Latches and Flip-Flops**

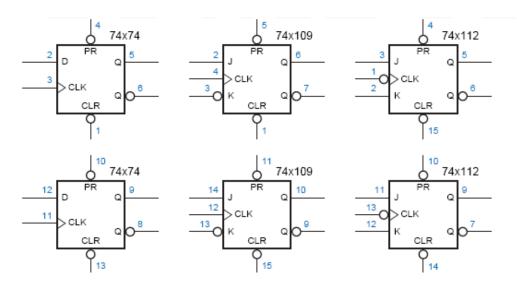

Several different types of discrete latches and flip-flops are available as SSI parts. These devices are sometimes used in the design of state machines and "unstructured" sequential circuits that don't fall into the categories of shift registers, counters, and other sequential MSI functions presented later in this chapter. However, SSI latches and flip-flops have been eliminated to a large extent in modern designs as their functions are embedded in PLDs and FPGAs. Nevertheless, a handful of these discrete building blocks still appear in many digital systems, so it's important to be familiar with them. Figure shows the pinouts for several SSI sequential devices. The only latch in the figure is the 74x375, which contains four D latches. Because of pin limitations, the latches are arranged in pairs with a common C control line for each

pair. Among the devices in Figure, the most important is the 74x74, which contains two independent positive-edge-triggered D flip-flops with preset and clear inputs. Besides the 74x74's use in "random" sequential circuits, fast versions of the part, such as the 74F74 and 74ACT74, find application in synchronizers for asynchronous input signals. The 74x109 is a positive-edge-triggered J-K flip-flop with an active-low K input (named K or K\_L). We Another J-K flip-flop is the 74x112, which has an active-low clock input.

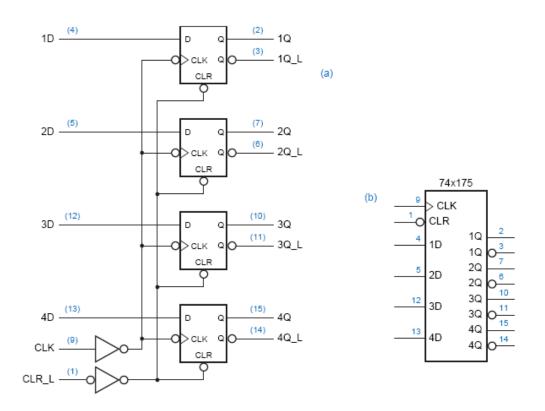

#### **Multibit Registers and Latches**

A collection of two or more D flip-flops with a common clock input is called a *register*. Registers are often used to store a collection of related bits, such as a byte of data in a computer. However, a single register can also be used to store unrelated bits of data or control information; the only real constraint is that all of the bits are stored using the same clock signal. Figure shows the logic diagram and logic symbol for a commonly used MSI register, the 74x175. The 74x175 contains four edge-triggered D flip-flops with a common clock and asynchronous clear inputs. It provides both active high and active-low outputs at the external pins of the device. The individual flip-flops in a '175 are negative-edge triggered, as indicated by the inversion bubbles on their CLK inputs. However, the circuit also contains an inverter that makes the flip-flops positive-edge triggered with respect to the device's external CLK input pin. The common, active-low, clear signal (CLR\_L) is connected to the asynchronous clear inputs of all four flip-flops. Both CLK and CLR\_L are buffered before fanning out to the four flip-flops, so that a device driving one of these inputs sees only one unit load

instead of four. This is especially important if a common clock or clear signal must drive many such registers.

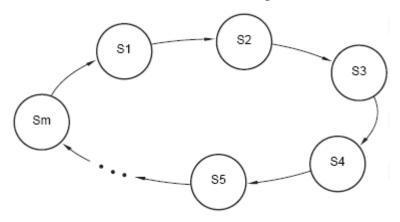

#### Counters

The name *counter* is generally used for any clocked sequential circuit whose state diagram contains a single cycle, as in Figure. The *modulus* of a counter is the number of states in the cycle. A counter with *m* states is called a *modulo-m counter* or, sometimes, a *divide-by-m counter*. A counter with a non power- of-2 modulus has extra states that are not used in normal operation.

## **Ripple Counters**

An *n*-bit binary counter can be constructed with just *n* flip-flops and no other components, for any value of *n*. Figure shows such a counter for n=4. Recall that a T flip-flop changes state (toggles) on every rising edge of its clock input. Thus, each bit of the counter toggles if and only if the immediately preceding bit changes from 1 to 0. This corresponds to a normal binary counting sequence—when a particular bit changes from 1 to 0, it generates a carry to the next most significant bit. The counter is called a *ripple counter* because the carry information ripples from the less significant bits to the more significant bits, one bit at a time.

#### **Synchronous Counters**

Although a ripple counter requires fewer components than any other type of binary counter, it does so at a price—it is slower than any other type of binary counter. In the worst case, when the most significant bit must change, the output is not valid until time n=t/TQ after the rising edge of CLK, where TQ is the propagation delay from input to output of a T flip-flop. A *synchronous counter* connects its entire flip-flop clock inputs to the same common CLK signal, so that all of the flip-flop outputs change at the same time, after only t TQ ns of delay. As shown in Figure this requires the use of T flip-flops with enable inputs; the output toggles on the rising edge of T if and only if EN is asserted. Combinational logic on the EN inputs determines which, if any, flip-flops toggle on each rising edge of T.

### **MSI** Counters and Applications

The most popular MSI counter is the 74x163, a synchronous 4-bit binary counter with active-low load and clear inputs, with the traditional logic symbol shown in Figure. Its function is summarized by the state table in Table and its internal logic diagram is shown in Figure. The '163 uses D flip-flops rather than T flip-flops internally to facilitate the load and clear functions. Each D input is driven by a 2-input multiplexer consisting of an OR gate and two AND gates. The multiplexer output is 0 if the CLR\_L input is asserted. Otherwise, the top AND gate passes the data input (A, B, C, or D) to the output if LD\_L is asserted. If neither CLR\_L nor LD\_L is asserted, the bottom AND gate passes the output of an XNOR gate to the multiplexer output.

State table for a 74x163 4-bit binary counter.

Inputs Current State Next State

CLR\_L LD\_L ENT ENP QD QC QB QA QD QC QB QA

0 x x x x x x 0 0 0 0

1 0 x x x x x x D C B A

1 1 0 x x x x QD QC QB QA

1 1 1 1 0 0 0 0 0 0 1

1 1 1 1 0 0 1 0 0 1 0

| 111100100011                                    |

|-------------------------------------------------|

| 111100110100                                    |

| $1 \ 1 \ 1 \ 1 \ 0 \ 1 \ 0 \ 0 \ 0 \ 1 \ 0 \ 1$ |

| 111101010110                                    |

| 111101100111                                    |

| 111101111000                                    |

| 111110001001                                    |

| 111110011010                                    |

| 111110101011                                    |

| 111110111100                                    |

| 111111001101                                    |

| 111111011110                                    |

| 111111101111                                    |

| 11111110000                                     |

| $\begin{array}{c} 2 \\ 1 \\ 0 \\ 0 \\ 0 \\ 10 \\ 7 \\ ENP \\ 10 \\ 10 \\ ENT \\ 3 \\ A \\ QA \\ 12 \\ 14 \\ 10 \\ 10 \\ 10 \\ 10 \\ 10 \\ 10 \\ 10$ | 74x163                           |                                                 |                      |                |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------|----------------------|----------------|--|--|

| 4         B         QB         13           5         C         QC         12           6         D         QD         11           RCO             | 1<br>9<br>7<br>10<br>3<br>4<br>5 | > CLK<br>CLR<br>LD<br>ENP<br>ENT<br>A<br>B<br>C | QA<br>QB<br>QC<br>QD | 13<br>12<br>11 |  |  |

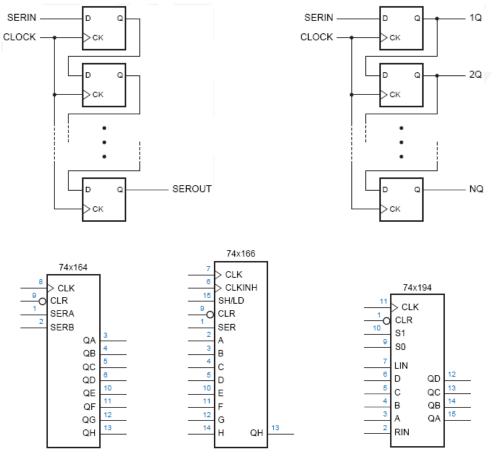

## **Shift Registers**

#### Shift-Register Structure

A *shift register* is an *n*-bit register with a provision for shifting its stored data by one bit position at each tick of the clock. Figure shows the structure of a serial-in, serial-out shift register. The *serial input*, SERIN, specifies a new bit to be shifted into one end at each clock tick. This bit appears at the *serial output*, SEROUT, after *n* clock ticks, and is lost one tick later. Thus, an *n*-bit serial-in, serial-out shift register can be used to delay a signal by *n* clock ticks. A *serial-in, parallel-out shift register*, shown in Figure, has outputs for all of its stored bits, making them available to other circuits. Such a shift register can be used to perform *serial-to-parallel conversion*, as explained later in this section. Conversely, it is possible to build a *parallel-in, serial-out shift register*. Figure shows the general structure of such a device. At each clock tick, the register either loads new data from inputs 1D–ND, or it shifts its current contents, depending on the value of the LOAD/SHIFT control input (which could be named LOAD or SHIFT\_L). Internally, the device uses a 2-input multiplexer on each flip-flop's D input to select between the two cases. A parallel-in, serial-out shift register can be used to perform *parallel-to-serial conversion*, as explained later in this

section. By providing outputs for all of the stored bits in a parallel-in shift register, we obtain the parallel-in, parallel-out shift register shown in Figure, Such a device is general enough to be used in any of the applications of the previous shift registers.

# **Impediments to Synchronous Design**

Although the synchronous approach is the most straightforward and reliable method of digital system design, a few nasty realities can get in the way. We'll discuss them in this section.

## **Clock Skew**

Synchronous systems using edge-triggered flip-flops work properly only if all flipflops see the triggering clock edge at the same time. Figure shows what can happen otherwise. Here, two flip-flops are theoretically clocked by the same signal, but the clock signal seen by FF2 is delayed by a significant amount relative to FF1's clock. This difference between arrival times of the clock at different devices is called *clock skew*. We've named the delayed clock in Figure "CLOCKD." If FF1's propagation delay from CLOCK to Q1 is short, and if the physical connection of Q1 to FF2 is short, then the change in Q1 caused by a CLOCK edge may actually reach FF2 *before* the corresponding CLOCKD edge. In this case, FF2 may go to an incorrect next state determined by the *next* state of FF1 instead of the current state, as shown in (b). If the change in Q1 arrives at FF2 only slightly early relative to CLOCKD, then FF2's holdtime specification may be violated, in which case FF2 may become metastable and produce an unpredictable output..

# **Read-Only Memory (ROM)**

One major type of memory that is used in PCs is called *read-only memory*, or *ROM* for short. ROM is a type of memory that normally can only be read, as opposed to RAM which can be both read and written. There are two main reasons that read-only memory is used for certain functions within the PC:

- **Permanence:** The values stored in ROM are always there, whether the power is on or not. A ROM can be removed from the PC, stored for an indefinite period of time, and then replaced, and the data it contains will still be there. For this reason, it is called *non-volatile storage*. A hard disk is also non-volatile, for the same reason, but regular RAM is not.

- Security: The fact that ROM cannot easily be modified provides a measure of security against accidental (or malicious) changes to its contents. You are not going to find viruses infecting true ROMs, for example; it's just not possible. (It's technically possible with *erasable* EPROMs, though in practice never seen.)

Read-only memory is most commonly used to store system-level programs that we want to have available to the PC at all times. The most common example is the system BIOS program, which is stored in a ROM called (amazingly enough) the *system BIOS ROM*. Having this in a permanent ROM means it is available when the power is turned on so that the PC can use it to boot up the system. Remember that when you first turn on the PC the system memory is empty, so there has to be *something* for the PC to use when it starts up. See this section for a description of the system BIOS ROM; see here for a description of the system boot sequence.

While the whole point of a ROM is supposed to be that the contents cannot be changed, there are times when being able to change the contents of a ROM can be very useful. There are several ROM variants that can be changed under certain circumstances; these can be thought of as "*mostly* read-only memory". The following are the different types of ROMs with a description of their relative modifiability:

• **ROM:** A regular ROM is constructed from hard-wired logic, encoded in the silicon itself, much the way that a processor is. It is designed to perform a specific function and cannot be

changed. This is inflexible and so regular ROMs are only used generally for programs that are static (not changing often) and mass-produced. This product is analogous to a commercial software CD-ROM that you purchase in a store.

- **Programmable ROM (PROM):** This is a type of ROM that can be programmed using special equipment; it can be written to, but only once. This is useful for companies that make their own ROMs from software they write, because when they change their code they can create new PROMs without requiring expensive equipment. This is similar to the way a CD-ROM recorder works by letting you "burn" programs onto blanks once and then letting you read from them many times. In fact, programming a PROM is also called *burning*, just like burning a CD-R, and it is comparable in terms of its flexibility.

- Erasable Programmable ROM (EPROM): An *EPROM* is a ROM that can be erased and reprogrammed. A little glass window is installed in the top of the ROM package, through which you can actually see the chip that holds the memory. Ultraviolet light of a specific frequency can be shined through this window for a specified period of time, which will erase the EPROM and allow it to be reprogrammed again. Obviously this is much more useful than a regular PROM, but it does require the erasing light. Continuing the "CD" analogy, this technology is analogous to a reusable CD-RW.

- Electrically Erasable Programmable ROM (EEPROM): The next level of erasability is the *EEPROM*, which can be erased under software control. This is the most flexible type of ROM, and is now commonly used for holding BIOS programs. When you hear reference to a "flash BIOS" or doing a BIOS upgrade by "flashing", this refers to reprogramming the BIOS EEPROM with a special software program. Here we are blurring the line a bit between what "read-only" really means, but remember that this rewriting is done maybe once a year or so, compared to real read-write memory (RAM) where rewriting is done often many times per second!

## **ROM CIRCUIT DIAGRAM**

CS150 Newton

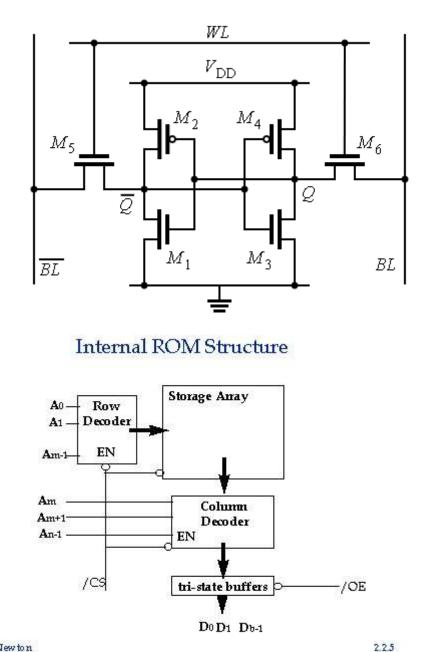

The memory matrix is the main part of the ROM. For each wordline, a connection is made to those bitlines (vertical) that should be activated for the corresponding memory word. In bipolar technology, simple diodes can be used to make the connections of wordlines to bitlines. However, usually transistors are used to amplify the wordline signal.

In MOS technologies, N-type transistors are preferred, because they are faster than Ptype transistors of the same size. The transistor gate is connected to the wordline, drain to the bitline, and the transistor source to Vss (ground). This results in the wired-AND structure shown in the applet. The pullup resistors on each bitline drive the bitline to a weak high voltage (logical H), when no transistors are active. If a transistor is used at the connection of a wordline and bitline, the transistor will conduct whenever the wordline is active, driving the bitline to a low voltage (logical 0).

As N-type transistors are used in the memory matrix, an active bitline is driven to zero voltage, while an inactive bitline remains at (weak) high. Therefore, an additional stage of amplifiers and output buffers is required to generate a strong output signal. The applet uses a single stage of inverters.

All together, the ROM shown in the applet implements the following logical function:

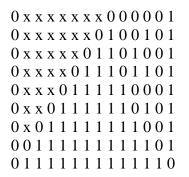

addr A3 A3 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0

Due to electrical reasons it is difficult to connect more that a few hundred transistors to one bitline or wordline. Therefore, larger ROMs use a slightly different architecture, with a set of smaller memory blocks instead of one single large memory block. Each memory block uses approximately the same number of wordlines and bitlines (the applet has 16 wordlines and 8 bitlines). For example, a good size for one memory block might consist of 256 wordlines and 256 bitlines. This means that a 64Kx8 bit ROM would be organized internally as a set of (65536x8) / (256x256) = 8 memory blocks. The top 3 address bits select the memory block to use, the next 8 bits

select the wordline to use, and the remaining 5 address bits select which part of the memory block output of 256 bits is to be sent to the 8 data outputs.

Each bit in an SRAM is stored on four transistors that form two cross-coupled inverters. This storage cell has two stable states which are used to denote **0** and **1**. Two additional *access* transistors serve to control the access to a storage cell during read and write operations. A typical SRAM uses six MOSFETs to store each memory bit. In addition to such 6T SRAM, other kinds of SRAM chips use 8T, 10T, or more transistors per bit. This is sometimes used to implement more than one (read and/or write) port, which may be useful in certain types of video memory and register files implemented with multi-ported SRAM circuitry.Generally, the fewer transistors needed per cell, the smaller each cell can be. Since the cost of processing a silicon wafer is relatively fixed, using smaller cells and so packing more bits on one wafer reduces the cost per bit of memory.

Memory cells that use fewer than 6 transistors are possible — but such 3T or 1T cells are DRAM, not SRAM (even the so-called 1T-SRAM).Access to the cell is enabled by the word line (WL in figure) which controls the two *access* transistors  $M_5$  and  $M_6$ which, in turn, control whether the cell should be connected to the bit lines: BL and BL. They are used to transfer data for both read and write operations. Although it is not strictly necessary to have two bit lines, both the signal and its inverse are typically provided in order to improve noise margins.

During read accesses, the bit lines are actively driven high and low by the inverters in the SRAM cell. This improves SRAM bandwidth compared to DRAMs—in a DRAM, the bit line is connected to storage capacitors and charge sharing causes the bitline to swing upwards or downwards. The symmetric structure of SRAMs also allows for differential signaling, which makes small voltage swings more easily detectable. Another difference with DRAM that contributes to making SRAM faster is that commercial chips accept all address bits at a time. By comparison, commodity DRAMs have the address multiplexed in two halves, i.e. higher bits followed by lower bits, over the same package pins in order to keep their size and cost down.The size of an SRAM with *m* address lines and *n* data lines is  $2^m$  words, or  $2^m \times n$  bits.

#### **SRAM** operation

An SRAM cell has three different states. It can be in: *standby* (the circuit is idle), *reading* (the data has been requested) and *writing* (updating the contents). The SRAM to operate in read mode and write mode should have "readability" and "write stability" respectively. The three different states work as follows:

• Standby

If the word line is not asserted, the *access* transistors  $M_5$  and  $M_6$  disconnect the cell from the bit lines. The two cross-coupled inverters formed by  $M_1 - M_4$  will continue to reinforce each other as long as they are connected to the supply.

• Reading

Assume that the content of the memory is a **1**, stored at Q. The read cycle is started by precharging both the bit lines to a logical **1**, then asserting the word line WL, enabling both the *access* transistors. The second step occurs when the values stored in Q and Q are transferred to the bit lines by leaving BL at its precharged value and discharging BL through  $M_1$  and  $M_5$  to a logical **0** (i. e. eventually discharging through the transistor  $M_1$  as it is turned on because the Q is logically set to **1**). On the BL side, the transistors  $M_4$  and  $M_6$  pull the bit line toward  $V_{DD}$ , a logical **1** (i. e. eventually being charged by the transistor  $M_4$  as it is turned on because Q is logically set to **0**). If the content of the memory was a **0**, the opposite would happen and BL would be pulled toward **1** and BL toward **0**. Then these BL and BL will have a small difference of delta between them and then these lines reach a sense amplifier, which will sense which line has higher voltage and thus will tell whether there was **1** stored or **0**. The higher the sensitivity of sense amplifier, the faster the speed of read operation is.

• Writing

The start of a write cycle begins by applying the value to be written to the bit lines. If we wish to write a 0, we would apply a 0 to the bit lines, i.e. setting BL to 1 and BL to 0. This is similar to applying a reset pulse to an SR-latch, which causes the flip flop to change state. A 1 is written by inverting the values of the bit lines. WL is then asserted and the value that is to be stored is latched in. Note that the reason this works is that the bit line input-drivers are designed to be much stronger than the relatively weak transistors in the cell itself, so that they can easily override the previous state of the cross-coupled inverters. Careful sizing of the transistors in an SRAM cell is needed to ensure proper operation.

## Bus behavior

RAM with an access time of 70 ns will output valid data within 70 ns from the time that the address lines are valid. But the data will remain for a hold time as well (5-10 ns). Rise and fall times also influence valid timeslots with approximately  $\sim$ 5 ns. By reading the lower part of an address range bits in sequence (page cycle) one can read with significantly shorter access time (30 ns).<sup>[7]</sup>

## **Applications and uses**

# Characteristics

SRAM is more expensive, but faster and significantly less power hungry (especially idle) than DRAM. It is therefore used where either bandwidth or low power, or both, are principal considerations. SRAM is also easier to control (interface to) and generally more truly *random access* than modern types of DRAM. Due to a more complex internal structure, SRAM is less dense than DRAM and is therefore not used for high-capacity, low-cost applications such as the main memory in personal computers.

#### Clock rate and power

The power consumption of SRAM varies widely depending on how frequently it is accessed; it **can** be as power-hungry as dynamic RAM, when used at high frequencies, and some ICs can consume many watts at full bandwidth. On the other hand, static RAM used at a somewhat slower pace, such as in applications with moderately clocked microprocessors, draws very little power and can have a nearly negligible power consumption when sitting idle — in the region of a few micro-watts.

Static RAM exists primarily as:

- general purpose products

- with *asynchronous* interface, such as the 28 pin 32Kx8 chips (usually named XXC256), and similar products up to 16 Mbit per chip

- with synchronous interface, usually used for caches and other applications requiring burst transfers, up to 18 Mbit (256Kx72) per chip

- integrated on chip

- as RAM or cache memory in micro-controllers (usually from around 32 bytes up to 128 kilobytes)

- as the primary caches in powerful microprocessors, such as the x86 family, and many others (from 8 kB, up to several megabytes)

- to store the registers and parts of the state-machines used in some microprocessors (see register file)

- o on application specific ICs, or ASICs (usually in the order of kilobytes)

- in FPGAs and CPLDs

# **Embedded** use

Many categories of industrial and scientific subsystems, automotive electronics, and similar, contain static RAM. Some amount (kilobytes or less) is also embedded in practically all modern appliances, toys, etc. that implement an electronic user interface. Several megabytes may be used in complex products such as digital cameras, cell phones, synthesizers, etc.

SRAM in its dual-ported form is sometimes used for realtime digital signal processing circuits

# In computers

SRAM is also used in personal computers, workstations, routers and peripheral equipment: internal CPU caches and external burst mode SRAM caches, hard disk buffers, router buffers, etc. LCD screens and printers also normally employ static RAM to hold the image displayed (or to be printed). Small SRAM buffers are also found in CDROM and CDRW drives; usually 256 kB or more are used to buffer track data, which is transferred in blocks instead of as single values. The same applies to cable modems and similar equipment connected to computers.

# **Types of SRAM**

# Non-volatile SRAM

Non-volatile SRAMs have standard SRAM functionality, but they save the data when the power supply is lost, ensuring preservation of critical information. nvSRAMs are used in a wide range of situations—networking, aerospace, and medical, among many others<sup>[9]</sup> —where the preservation of data is critical and where batteries are impractical.

# Asynchronous SRAM

Asynchronous SRAM are available from 4 Kb to 64 Mb. The fast access time of SRAM makes asynchronous SRAM appropriate as main memory for small cache-less embedded processors used in everything from industrial electronics and measurement systems to hard disks and networking equipment, among many other applications. They are used in various applications like switches and routers, IP-Phones, IC-Testers, DSLAM Cards, to Automotive Electronics.

# By transistor type

- Bipolar junction transistor (used in TTL and ECL) very fast but consumes a lot of power

- MOSFET (used in CMOS) low power and very common today

# By function

- Asynchronous independent of clock frequency; data in and data out are controlled by address transition

- Synchronous all timings are initiated by the clock edge(s). Address, data in and other control signals are associated with the clock signals

# By feature

ZBT (ZBT stands for zero bus turnaround) — the turnaround is the number of clock cycles it takes to change access to the SRAM from write to read and vice versa. The turnaround for ZBT SRAMs or the latency between read and write cycle is zero.

- syncBurst (syncBurst SRAM or synchronous-burst SRAM) features synchronous burst write access to the SRAM to increase write operation to the SRAM

- DDR SRAM Synchronous, single read/write port, double data rate I/O

- Quad Data Rate SRAM Synchronous, separate read & write ports, quadruple data rate I/O

# By flip-flop type

- Binary SRAM

- Ternary SRAM

# Dynamic random-access memory (DRAM)

It is a type of random-access memory that stores each bit of data in a separate capacitor within an integrated circuit. The capacitor can be either charged or discharged; these two states are taken to represent the two values of a bit, conventionally called 0 and 1. Since capacitors leak charge, the information eventually fades unless the capacitor charge is refreshed periodically. Because of this refresh requirement, it is a *dynamic* memory as opposed to SRAM and other *static* memory.

The main memory (the "RAM") in personal computers is Dynamic RAM (DRAM). It is the RAM in laptop, notebook and workstation computers as well as some of the RAM of home game consoles (PlayStation3, Xbox 360 and Wii),

The advantage of DRAM is its structural simplicity: only one transistor and a capacitor are required per bit, compared to six transistors in SRAM. This allows DRAM to reach very high densities. Unlike flash memory, DRAM is volatile memory (cf. non-volatile memory), since it loses its data quickly when power is removed. The transistors and capacitors used are extremely small; billions can fit on a single memory chip.

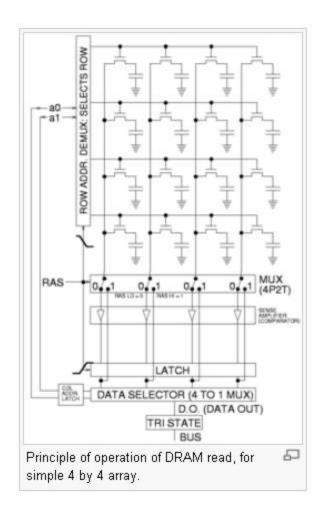

DRAM is usually arranged in a square array of one capacitor and transistor per data bit storage cell. The illustrations to the right show a simple example with 4 by 4 cells (modern DRAM matrices are many thousands of cells in height and width).

The long horizontal lines connecting each row are known as word Lines. Each column of cells is actually composed of two bit lines, each one connected to every other storage cell in the column (the illustration to the right does not include this important detail). They are generally known as the + and - bit lines. A sense amplifier is essentially a pair of cross-connected inverters between the bit lines, with the first inverter connected from the + bit line to the - bit line, and the second from the - bit line to the + bit line. This is an example of positive feedback, and the arrangement is only stable after one bit line is high and one bit line is low.

To read a bit from a column, the following operations take place:

- 1. The sense amplifier is disconnected, then the bit lines are precharged to exactly equal voltages that are in-between high and low logic levels. The bit lines are physically symmetrical to keep the capacitance as equal and therefore the voltages as equal as possible.

- The precharge circuit is switched off. Because the bit lines are relatively long, they have enough capacitance to maintain the pre-charged voltage for a brief time. This is an example of dynamic logic.

- 3. The desired row's word line is then driven high to connect a cell's storage capacitor to its bit line. This causes the transistor to conduct, transferring charge between the storage cell and the connected bit line. If the storage cell capacitor is discharged, it will greatly decrease the voltage on the bit-line as the precharge is transferred to the storage capacitor. If the storage cell is charged, the bit-line voltage decreases only slightly; this is because every effort is made to keep the capacitance of the storage cells high and the capacitance of the bit lines low.

- 4. The sense amplifier is switched on. The positive feedback takes over and amplifies the small voltage difference between bit-lines until one bit line is fully at the lowest voltage and the other is at the maximum high voltage. Once this has happened, the row is "open" (the desired cell data is available).

- 5. All columns are sensed in simultaneously and the result sampled into the data latch. A provided Column address then selects which latch bit to connect to the external circuit. Many reads can be performed quickly without delay sense for the open row, all data has already been sensed and latched.

- 6. While reading all columns proceeds (the normal and desirable method because it most quickly provides data), current is flowing back up the bit lines from the sense amplifiers to the storage cells. This reinforces (i.e. "refreshes") the charge in the storage cell by increasing the voltage in the storage capacitor if it was charged to begin with, or by keeping it discharged if it was empty. Note that due to the length of the bit lines creating a fairly long propagation delay for the charge to be transferred, this takes significant time beyond the end of sense amplification, and thus overlaps with one or more column reads.

- 7. When done with the reading all the columns in the current row, the word line is switched off to disconnect the cell storage capacitors (the row is "closed"), the sense amplifier is switched off, and the bit lines are precharged again.

To write to memory, the row is opened and a given column's sense amplifier is temporarily forced to the desired high or low voltage state, thus it drives the bit line to charge or discharge the cell storage capacitor to the desired value. Due to positive feedback, the amplifier will then hold it stable even after the forcing is removed. During a write to a particular cell, all the columns in a row are sensed simultaneously just as in reading, a single column's cell storage capacitor charge is changed, and then the entire row is written back in, as illustrated in the figure to the right.

Typically, manufacturers specify that each row must have its storage cell capacitors refreshed every 64 ms or less, as defined by the JEDEC (Foundation for developing Semiconductor Standards) standard. Refresh logic is provided in a DRAM controller which automates the periodic refresh, that is no software or other hardware has to perform it. This makes the controller's logic circuit more complicated, but this drawback is outweighed by the fact that DRAM is much cheaper per storage cell and because each storage cell is very simple, DRAM has much greater capacity per geographic area than SRAM.

Some systems refresh every row in a burst of activity involving all rows every 64 ms. Other systems refresh one row at a time staggered throughout the 64 ms interval. For example, a system with  $2^{13} = 8192$  rows would require a staggered refresh rate of one row every 7.8 µs which is 64 ms divided by 8192 rows. A few real-time systems refresh a portion of memory at a time determined by an external timer function that governs the operation of the rest of a system, such as the vertical blanking interval that occurs every 10–20 ms in video equipment. All methods require some sort of counter to keep track of which row is the next to be refreshed. Most DRAM chips include that counter. Older types require external refresh logic to hold the counter (under some conditions, most of the data in DRAM can be recovered even if the DRAM has not been refreshed for several minutes).

## Synchronous DRAM

This is the basic form from which all others derive. An asynchronous DRAM chip has power connections, some number of address inputs (typically 12), and a few (typically one or four) bidirectional data lines. There are four active-low control signals:

- /RAS, the Row Address Strobe. The address inputs are captured on the falling edge of /RAS, and select a row to open. The row is held open as long as /RAS is low.

- /CAS, the Column Address Strobe. The address inputs are captured on the falling edge of /CAS, and select a column from the currently open row to read or write.

- /WE, Write Enable. This signal determines whether a given falling edge of /CAS is a read (if high) or write (if low). If low, the data inputs are also captured on the falling edge of /CAS.

- /OE, Output Enable. This is an additional signal that controls output to the data I/O pins. The data pins are driven by the DRAM chip if /RAS and /CAS are low, /WE is high, and /OE is low. In many applications, /OE can be permanently connected low (output always enabled), but it can be useful when connecting multiple memory chips in parallel.

This interface provides direct control of internal timing. When /RAS is driven low, a /CAS cycle must not be attempted until the sense amplifiers have sensed the memory state, and /RAS must not be returned high until the storage cells have been refreshed. When /RAS is driven high, it must be held high long enough for precharging to complete.

Although the RAM is asynchronous, the signals are typically generated by a clocked memory controller, which limits their timing to multiples of the controller's clock cycle.

# UNIT IV LOGIC FAMILIES AND SEMICONDUCTOR MEMORIES

# **Introduction to logic families**

# **Logic Signals and Gates**

Digital logic hides the pitfalls of the analog world by mapping the infinite set of real values for a physical quantity into two subsets corresponding to just two possible numbers or logic values—0 and 1. As a result, digital logic circuits can be analyzed and designed functionally, using switching algebra, tables, and other abstract means to describe the operation of well-behaved 0s and 1s in a circuit.

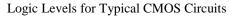

A logic value, 0 or 1, is often called a binary digit, or bit. If an application requires more than two discrete values, additional bits may be used, with a set of n bits representing 2n different values. Examples of the physical phenomena used to represent bits in some modern (and not-so-modern) digital technologies are given in Table 3-1. With most phenomena, there is an undefined region between the 0 and 1 states (e.g., voltage = 1.8 V, dim light, capacitor slightly charged, etc.). This undefined region is needed so that the 0 and 1 states can be unambiguously defined and reliably detected. Noise can more easily corrupt results if the boundaries separating the 0 and 1 states are too close. When discussing electronic logic circuits such as CMOS and TTL, digital designers often use the words "LOW" and "HIGH" in place of "0" and "1" to remind them that they are dealing with real circuits, not abstract quantities:

LOW A signal in the range of algebraically lower voltages, which is interpreted as a logic 0.

HIGH A signal in the range of algebraically higher voltages, which is interpreted as a logic 1.

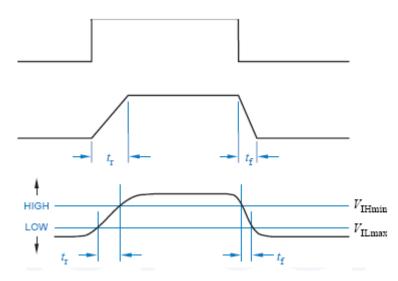

Note that the assignments of 0 and 1 to LOW and HIGH are somewhat arbitrary. Assigning 0 to LOW and 1 to HIGH seems most natural, and is called positive logic. The opposite assignment, 1 to LOW and 0 to HIGH, is not often used, and is called negative logic. Because a wide range of physical values represent the same binary value, digital logic is highly immune to component and power supply variations and noise. Furthermore, buffer amplifier circuits can be used to regenerate "weak" values into "strong" ones, so that digital signals can be transmitted over arbitrary distances without loss of information. For example, a buffer amplifier for CMOS Digital logic hides the pitfalls of the analog world by mapping the infinite set of real values for a physical quantity into two subsets corresponding to just two possible numbers or logic values—0 and 1. As a result, digital logic circuits can be analyzed and designed functionally, using switching algebra, tables, and other abstract means to describe the operation of well-behaved 0s and 1s in a circuit.