#### **COMPUTER ORGANIZATION AND ARCHITECTURE Course code: ACSB07** IV. B.Tech II semester **Regulation: IARE R-18** Prepared by: Mr. E Sunil Reddy, Assistant Professor Ms. B.Dhana Laxmi, Assistant Professor **Dr.P.L.Srinivasa Murthy. Professor** Mr. N Rajasekhar, Assistant Professor **COMPUTER SCIENCE AND ENGINEERING INSTITUTE OF AERONAUTICAL ENGINEERING** (Autonomous) **DUNDIGAL, HYDERABAD - 500 043**

#### **Course Outcomes**

The course should enable the students to:

- CO 1 Understand the organization and levels of design in computer architecture and To understand the concepts of programming methodologies.

- CO 2 Describe Register transfer languages, arithmetic micro operations, logic micro operations, shift micro operations address sequencing, micro program example, and design of control unit.

- CO 3 Understand the Instruction cycle, data representation, memory reference instructions, input-output, and interrupt, addressing modes, data transfer and manipulation, program control. Computer arithmetic: Addition and subtraction, floating point arithmetic operations, decimal arithmetic unit.

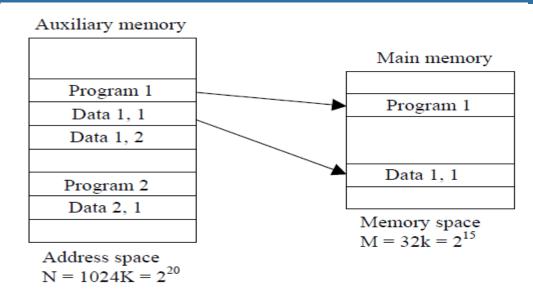

- CO 4 Knowledge about Memory hierarchy, main memory, auxiliary memory, associative memory, cache memory, virtual memory Input or output Interface, asynchronous data transfer, modes of transfer, priority interrupt, direct memory access.

- CO 5 Explore the Parallel processing, pipelining-arithmetic pipeline, instruction pipeline Characteristics of multiprocessors, inter connection structures, inter processor arbitration, inter processor Communication and synchronization

#### **MODULE –I**

#### **INTRODUCTION TO COMPUTER ORGANIZATION**

#### The course will enable the students to:

| CLO 1 | Describe the various components like input/output units,<br>memory unit, control unit, arithmetic logic unit connected in<br>the basic encouring tion of a commuter |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | the basic organization of a computer.                                                                                                                               |

| CLO 2 | Understand the interfacing concept with memory<br>subsystem organization and input/output subsystem<br>organization.                                                |

| CLO 3 | Understand instruction types, addressing modes and their formats in the assembly language programs.                                                                 |

| CLO 4 | Describe the instruction set architecture design for relatively simple microprocessor or Central Processing Unit.                                                   |

| CLO 5 | Understand the organization and levels of design in computer architecture and To understand the concepts of programming methodologies.                              |

## Contents

#### **Basic computer organization**

- CPU organization

- Memory subsystem organization and interfacing

- Input or output subsystem organization and interfacing

- A simple computer levels of programming languages

- Assembly language instructions

- Instruction set architecture design

- A simple instruction set architecture.

## **Basic Computer Organization**

- EDUCHTION FOR LIBERT

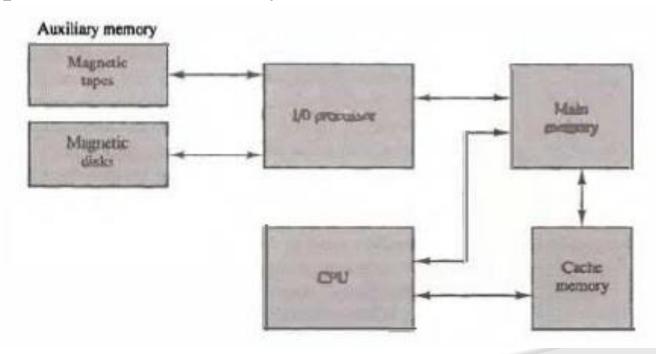

- The basic computer organization has three main components:

- CPU

- Memory subsystem

- I/O subsystem

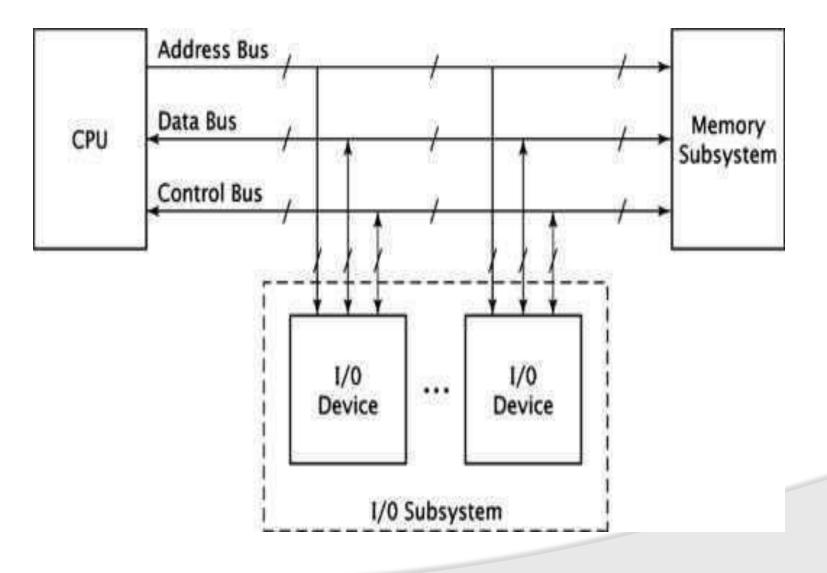

## **Generic computer Organization**

### system bus

- The system bus has three buses:

- Address bus: The uppermost bus is the address bus. When the CPU reads data or instructions from or writes data to memory, it must specify the address of the memory location it wishes to access.

- **Data bus:** Data is transferred via the Data bus. When CPU fetches data from memory it first outputs the memory address on to its address bus. Then memory outputs the data onto the data bus. Memory then reads and stores the data at the proper locations.

- **Control bus:** Control bus carries the control signal. Control signal is the collection of individual control signals. These signals indicate whether data is to be read into or written out of the CPU.

- Each program is a sequence of instructions.

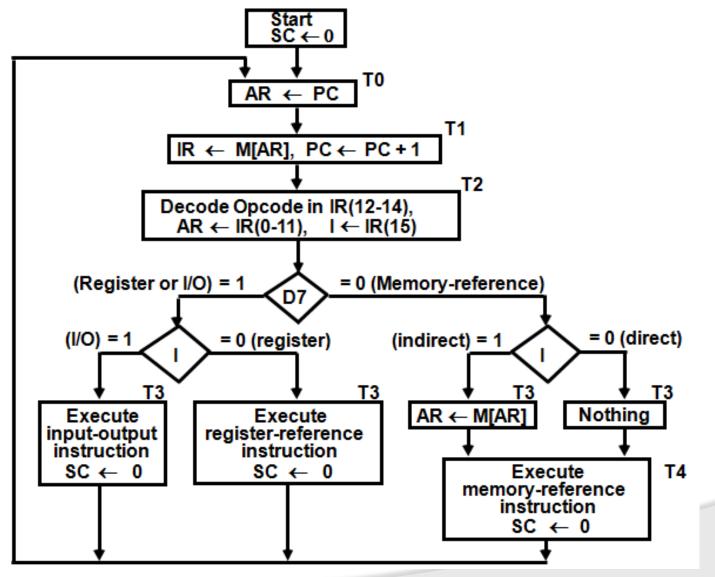

- The basic computer system each instruction is subdivided into Four phases:

- **1. Fetch an Instruction from memory.**

- 2. Decode the Instruction.

- 3. Read the effective address from the memory if the instruction has an indirect address.

- 4. Execute the Instruction.

- The above process continues indefinitely unless a HALT instruction is encountered.

#### **Fetch and Decode**

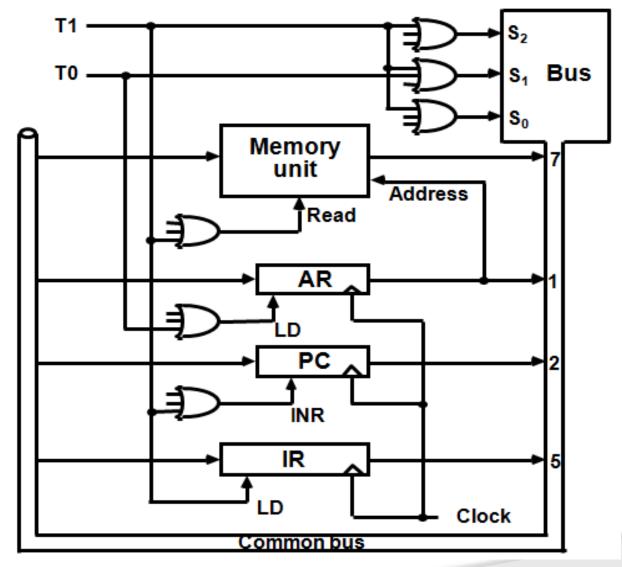

• Initially the program counter PC is loaded with the address of the first instruction.

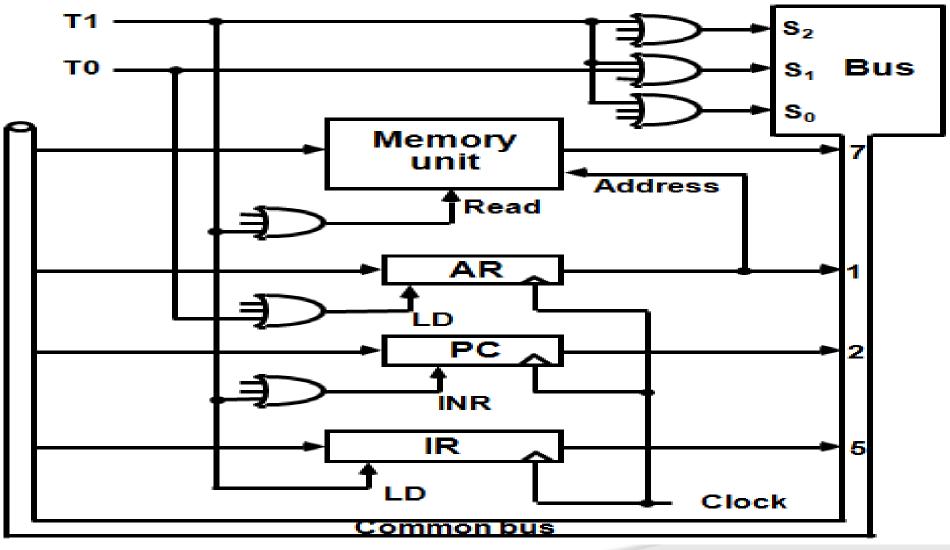

T0: AR ← PC (S<sub>0</sub>S<sub>1</sub>S<sub>2</sub>=010, T0=1) T1: IR ← M [AR], PC ← PC + 1 (S0S1S2=111, T1=1) T2: D0, ..., D7 ← Decode IR(12-14), AR ← IR(0-11), I ← IR(15)

Fig: Register Transfer for the fetch phase

- In the above diagram shows the transfer of first two statements(T0 and T1).

- When timing signal T0=1then

- 1. Place the contents of PC onto the bus by making the bus selection inputs S2S1S0 equal to 010.

- 2. Transfer the contents of the bus to AR by enabling the LD input of AR.

- When timing signal T1=1 then

- 1. Enable the read input of memory.

- 2. Place the contents of Memory onto the bus by making S2S1S0=111.

- 3. Transfer the contents of the bus to IR by enabling the LD input of IR.

- 4. Increment PC by enabling the INR input of PC.

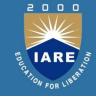

### **Determine the Type of Instruction**

- After executing the timing signal T1 the control unit determines the type of instruction that is read from memory.

- If D7=1 and the instruction must be a register-reference or input-out type.

- If D7=0 the operation code must be one of the other seven values 000 through 110 specifying a memory –reference Instruction.

- The symbolic representation is :

| D'7IT3 :  | $AR \leftarrow M[AR]$               |

|-----------|-------------------------------------|

| D'7I'T3 : | Nothing                             |

| D7I'T3 :  | Execute a register-reference instr. |

| D7IT3 :   | Execute an input-output instr.      |

Fig : Flowchart for Instruction Cycle

## **Control signals**

- The **READ** signal is a signal on the control bus which the microprocessor asserts when it is ready to read data from memory or I/O device.

- When **READ** signal is asserted the memory subsystem places the instruction code be fetched on to the computer system's data bus. The microprocessor then inputs the data from the bus and stores its internal register.

- **READ** signal causes the memory to read the data, the **WRITE** operation causes the memory to store the data

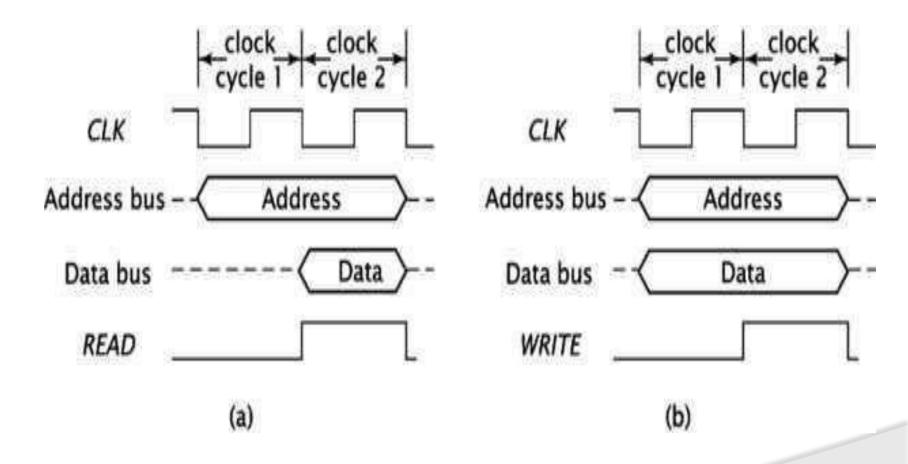

# **Timing diagrams**

- In fig (a) the microprocessor places the address on to the bus at the beginning of a clock cycle, a 0/1 sequence of clock. One clock cycle later, to allow for memory to decode the address and access its data, the microprocessor asserts the READ control signal.

- This causes the memory to place its data onto the system data bus. During this clock cycle, the microprocessor reads the data off the system bus and stores it in one of the registers.

- At the end of the clock cycle it removes the address from the address bus and de asserts the READ signal. Memory then removes the data from the data from the data bus completing the memory read operation

### Memory write operation

- In fig(b) the processor places the address and data onto the system bus during the first clock pulse.

- The microprocessor then asserts the WRITE control signal at the end of the second clock cycle.

- At the end of the second clock cycle the processor completes the memory write operation by removing the address and data from the system bus and deasserting the WRITE signal.

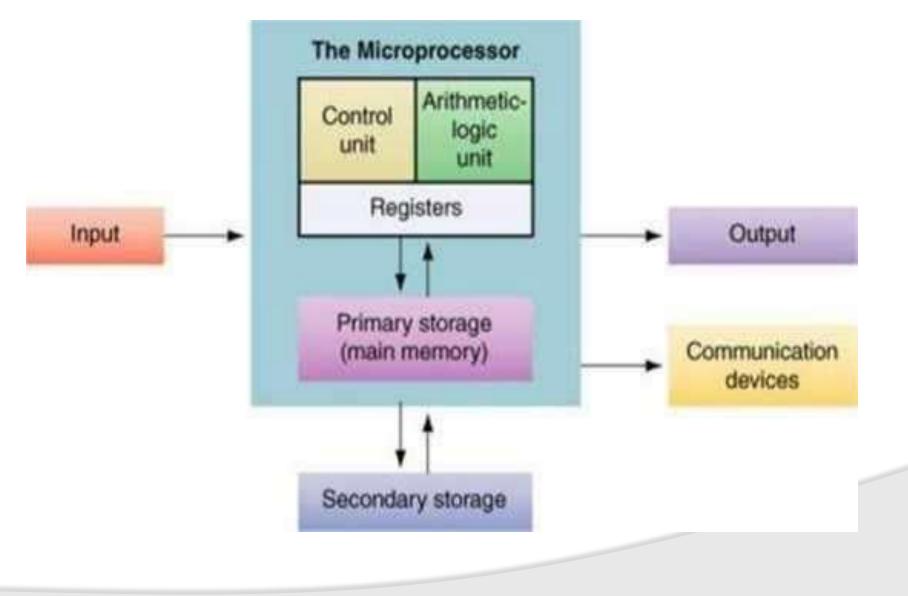

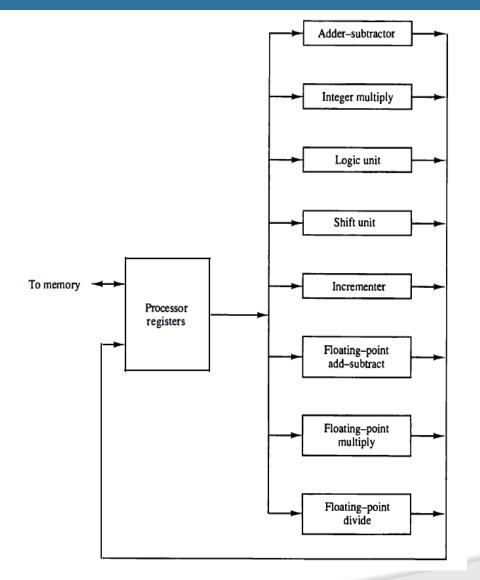

# **CPU Organization**

- FOUCHION FOR UNBERF

- Central processing unit (CPU) is the electronic circuitry within a computer that carries out the instructions of a computer program by performing the basic arithmetic, logical, control and input/output (I/O) operations specified by the instructions.

- In the computer all the all the major connected with the help of the **system bus**.

- **Data bus** is used to shuffle data between the various components in a computer system.

- When the software wants to access some particular memory location or I/O device it places the corresponding address on the **address bus**.

- The **control bus** is an eclectic collection of signals that control how the processor communicates with the rest of the system. The **read** and **write** control lines control the direction of data on the data bus.

#### **CPU Organization**

- The register section, as its name implies, includes a set of registers and a bus or other communication mechanism.

- The register in a processor's instruction set architecture are found in the section of the CPU.

- The system address and data buses interact with this section of CPU. The register section also contains other registers that are not directly accessible by the programmer.

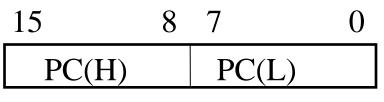

- The fetch portion of the instruction cycle, the processor first outputs the address of the instruction onto the address bus. The processor has a register called the **program counter**.

- At the end of the instruction fetch, the CPU reads the instruction code from the system data bus.

- It stores this value in an internal register, usually called the **instruction register**".

#### **CPU Organization**

- The **arithmetic / logic unit (or) ALU** performs most arithmetic and logic operations such as adding and ANDing values.

- CPU controls the computer, the **control unit** controls the CPU. The control unit receives some data values from the register unit, which it used to generate the control signals.

- The **control unit** also generates the signals for the system control bus such as READ, WRITE, IO/ signals

- Memory is the group of circuits used to store data.

- Memory components have some number of memory locations, each word of which stores a binary value of some fixed length.

- The number of locations and the size of each location vary from memory chip to memory chip, but they are fixed within individual chip.

- Memory is usually organized in the form of arrays, in which each cell is capable of storing one bit information.

- Each row of cell constitutes a memory word, and all cells of a row are connected to a common column called word line, which is driven by the address decoder on the chip

# **Types of Memory**

EDUCATION FOR LIBERT

- There are **two types** of memory chips,

- 1. Read Only Memory (ROM)

- 2. Random Access Memory (RAM)

- Masked ROM(or) simply ROM

- PROM(Programmed Read Only Memory)

- EPROM(Electrically Programmed Read Only Memory)

- EEPROM(Electrically Erasable PROM)

- Flash Memory

# **ROM Chips**

#### Masked ROM

- A masked ROM or simply ROM is programmed with data as chip is fabricated.

- The mask is used to create the chip and chip is designed with the required data hardwired in it.

- PROM

- Some ROM designs allow the data to be loaded by the user, thus providing programmable ROM (PROM).

- Once a program has been written onto a PROM, it remains there forever.

- Unlike main memory, PROMs retain their contents when the computer is turned off.

- PROM (programmable read-only memory) is a memory chip on which data can be written only once.

# **ROM Chips**

- EPROM

- EPROM is the another ROM chip allows the stored data to be erased and new data to be loaded. Such an erasable reprogrammable ROM is usually called an EPROM.

- EPROM is done by charging of capacitors. The charged and uncharged capacitors cause each word of memory to store the correct value.

- The chip is erased by beingplaced under UV light, which causes the capacitor to leak their charge.

# **ROM Chips**

#### • EEPROM

- A significant disadvantage of the EPROM is the chip is physically removed from the circuit for reprogramming and that entire contents are erased by the UV light.

- Another version of EPROM is EEPROM that can be both programmed and erased electrically, such chips called EEPROM, do not have to remove for erasure.

- The only disadvantage of EEPROM is that different voltages are need for erasing, writing, reading and stored data

#### • Flash Memory

- A special type of EEPROM is called a flash memory is electrically erase data in blocks rather than individual locations.

- It is well suited for the applications that writes blocks of data and can be used as a solid state hard disk. It is also used for data storage in digital computers.

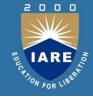

## **Memory Subsystem Organization**

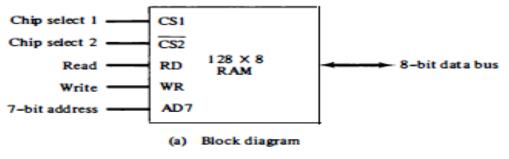

#### • RAM Chips:

- RAM stands for Random access memory. This often referred to as read/write memory. Unlike the ROM it initially contains no data.

- The data pins are bidirectional unlike in ROM.

- A ROM chip loses its data once power is removed so it is a volatile memory.

- RAM chips are differentiated based on the data they maintain.

- Dynamic RAM (DRAM)

- Static RAM (SRAM)

# Memory chips Internal organization

#### • Dynamic RAM

- DRAM chips are like leaky capacitors. Initially data is stored in the DRAM chip, charging its memory cells to their maximum values.

- The charging slowly leaks out and would eventually go too low to represent valid data.

- Before this a refresher circuit reads the content of the DRAM and rewrites data to its original locations.

- DRAM is used to construct the RAM in personal computers.

- Static RAM

- Static RAM are more likely the register .Once the data is written to SRAM, its contents stay valid it does not have to be refreshed.

- Static RAM is faster than DRAM but it is also much more expensive. Cache memory in the personal computer is constructed from SRAM.

#### Memory subsystem configuration

(b)

# Multi byte organization

- There are two commonly used organizations for multi byte data.

- Big endian

- Little endian

- In BIG-ENDIAN systems the most significant byte of a multi- byte data item always has the lowest address, while the least significant byte has the highest address.

- In LITTLE-ENDIAN systems, the least significant byte of a multi-byte data item always has the lowest address, while the most significant byte has the highest address.

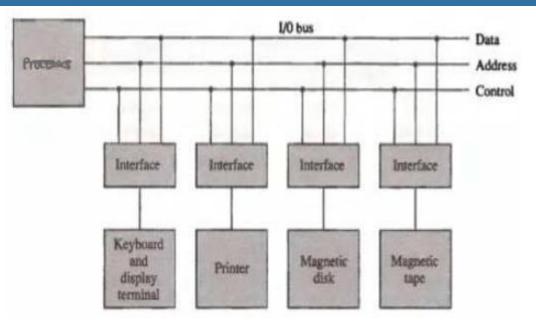

The I/O subsystem is treated as an independent unit in the computer The CPU initiates I/O commands generically

- Read, write, scan, etc.

- This simplifies the CPU

## **Input Device**

The I/O subsystem is treated as an independent unit in the computer The CPU initiates I/O commands generically

- Read, write, scan, etc.

- This simplifies the CPU

#### **Input Device**

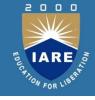

- The data from the input device goes to the tri-state buffers. When the value in the address and control buses are correct, the buffers are enabled and data passes on the data bus.

- The CPU can then read this data. If the conditions are not right the logic block does not enable the buffers and do not place on the bus.

- The enable logic contains 8-bit address and also generates two control signals RD and I/O.

## **Output Device**

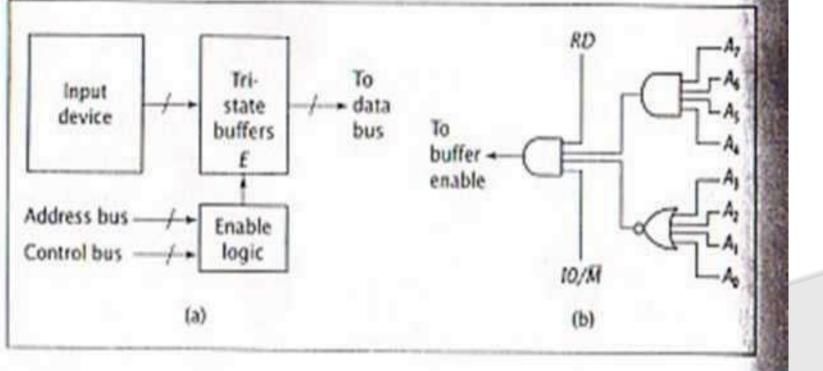

- The design of the interface circuitry for an output device such as a computer monitor is somewhat different than for the input device.

- Tri-state buffers are replaced by a register.

- The tri-state buffers are used in input device interfaces to make sure that one device writes data to the bus at any time.

- Since the output devices read from the bus, rather that writes data to it, they don't need the buffers.

- The data can be made available to all output devices but the devices only contains the correct address will read it in

# **Output Device**

An output device: (a) with its interface and (b) the enable logic for the registers

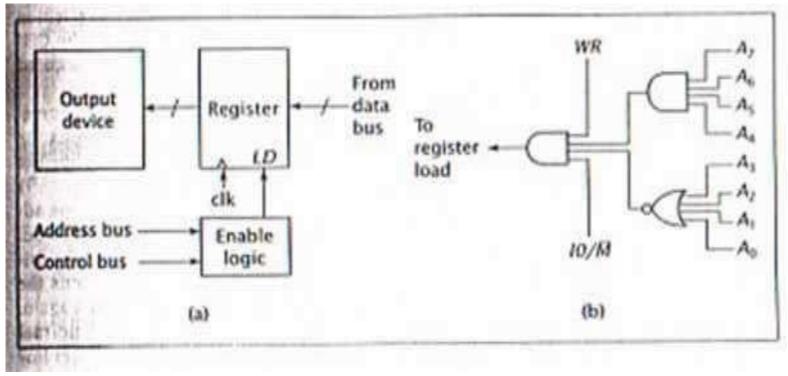

- Some devices are used for both input and output. Personal computer and hard disk devices are falls into this category. Such a devices requires a combined interface that is essential two interfaces.

- A bidirectional I/O device with its interface and enable load logic is shown in the Figure below.

# **Output Device**

2 0 0 0

IARE

Figure : A bidirectional I/O device with its interface and enable/load logic

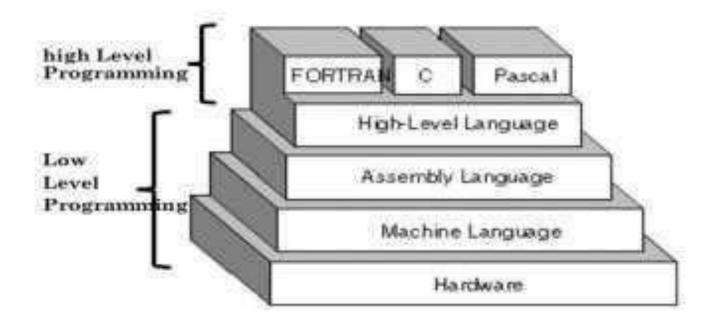

- Computer programming languages are divided into 3 categories.

- High level language

- Assembly level language

- Machine level language

- **High level languages** are platform independent that is these programs can run on computers with different microprocessor and operating systems without modifications. Languages such as C++, Java and FORTRAN are high level languages.

- Assembly languages are at much lower level of abstraction. Each processor has its own assembly language

- The lowest level of programming language is **machine level** languages. These languages contain the binary values that cause the microprocessor to perform certain operations. When microprocessor reads and executes an instruction it's a machine language instruction.

#### Figure 1.8: Levels of programming languages

- High level language programs are compiled and assembly level language programs are assembled.

- A program written in the high level language is input to the compiler.

- compiler checks to make sure every statement in the program is valid. When the program has no syntax errors the compiler finishes the compiling the program that is source code and generates an object code file.

- An **object code** is the machine language equivalent of source code.

- A **linker** combines the object code to any other object code. This combined code stores in the **executable file**.

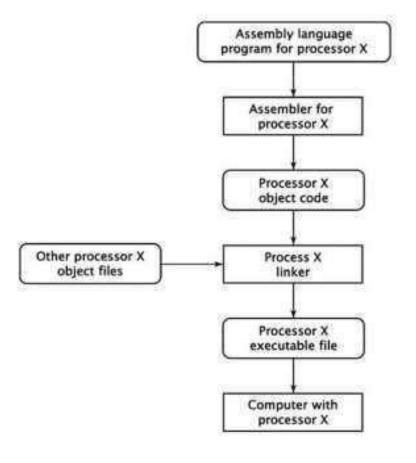

### Assembling programs

- Assembly language is specific to one microcontroller

- Converts the source code into object code

- The linker will combine the object code of your program with any other required object code to produce executable code

- Loader will load the executable code into memory, for execution

- Programmers don't written the programs in machine language rather programs written in assembly or high level are the converted into machine level and then executed by microprocessor.

- High level language programs are compiled and assembly level language programs are assembled.

- A program written in the high level language is input to the compiler. The compiler checks to make sure every statement in the program is valid. When the program has no syntax errors the compiler finishes the compiling the program that is source code and generates an object code file.

- An object code is the machine language equivalent of source code.

- A **linker** combines the object code to any other object code. This combined code stores in the **executable file.**

# **Assembly Language Instructions**

- Instruction types

- Assembly languages instructions are grouped together based on the operation they performed.

- Data transfer instructions

- Data operational instructions

- Program control instructions

- Data transfer instructions

- Load the data from memory into the microprocessor: These instructions copy data from memory into a microprocessor register.

- Store the data from the microprocessor into the memory: This is similar to the load data expect data is copied in the opposite direction from a microprocessor register to memory.

- Move data within the microprocessor: These operations copies data from one microprocessor register to another.

- **Input the data to the microprocessor**: The microprocessor inputs the data from the input devices ex: keyboard in to one of its registers.

# **Assembly Language Instructions**

- Data operational instructions

- **Data operational instructions** do modify their data values. They typically perform some operations using one or two data values (operands) and store result.

- Arithmetic instructions make up a large part of data operations instructions. Instructions that add, subtract, multiply, or divide values fall into this category. An instruction that increment or decrement also falls in to this category.

- Logical instructions perform basic logical operations on data. They AND, OR, or XOR two data values or complement a single value.

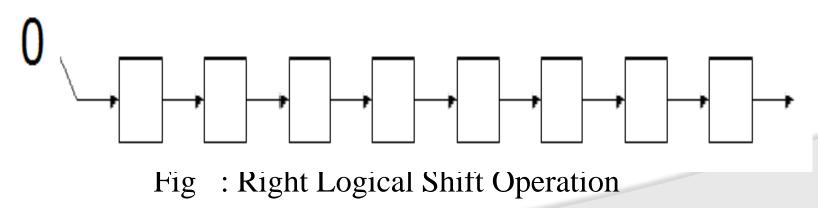

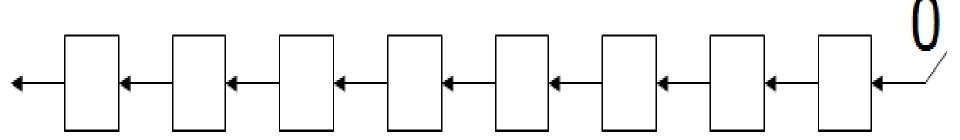

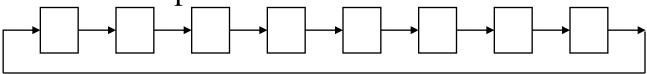

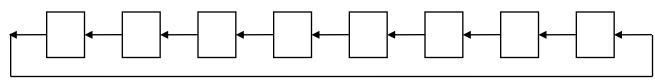

- Shift operations as their name implies shift the bits of a data values also comes under this category

# **Assembly Language Instructions**

#### Program control instructions

- Program control instructions are used to control the flow of a program. Assembly language instructions may include subroutines like in high level language program may have subroutines, procedures, and functions.

- A jump or branch instructions are generally used to go to another part of the program or subroutine.

# **Instruction Set Architecture Design**

- Designing of the instructions the most important in designing the microprocessor. A poor designed ISA even it is implemented well leads to bad micro processor.

- A well designed instruction set architecture on the other hand can result in a powerful processor that can meet variety of needs.

- In designing ISA the designer must evaluate the tradeoffs in performance and such constrains issues as size and cost when designing ISA specifications.

- The issue of **completeness** of the ISA is one of the criteria in designing the processor that means the processor must have complete set of instructions to perform the task of the given application.

- Another criterion is instruction **orthogonality.** Instructions are orthogonal if they do not overlap, or perform the same function. A good instruction set minimizes the overlap between instructions.

# **Instruction Set Architecture Design**

- Another area that the designer can optimize the ISA is the **register set**. Registers have a large effect on the performance of a CPU. The CPU Can store data in its internal registers instead of memory. The CPU can retrieve data from its registers much more likely than form the memory.

- Having too few registers causes a program to make more reference to the memory thus reducing performance

# **Simple Instruction Set**

- EUCHTION FOR LIBER

- This processor inputting the data from and outputting the data to external devices such as microwave ovens keypad and display are treated as memory accesses. There are two types of input/output interactions that can design a CPU to perform.

- An **isolated I/O** input and output devices are treated as being separated from memory. Different instructions are used for memory and I/O.

- Memory mapped I/O treats input and output devices as memory locations the CPU access these I/O devices using the same instructions that it uses to access memory. For relatively simple CPU memory mapped I/O is used.

- There are three registers in ISA of this processor.

- Accumulator (AC)

- Register R

- Zero flag (Z)

# **Simple Instruction Set**

| Instruction | Instruction<br>Code | Operation                                                             |

|-------------|---------------------|-----------------------------------------------------------------------|

| NOP         | 0000 0000           | No operation                                                          |

| LDAC        | 0000 0001 Г         | $AC = M[\Gamma]$                                                      |

| STAC        | 0000 0010 Г         | $M[\Gamma] = AC$                                                      |

| MVAC        | 0000 0011           | R = AC                                                                |

| MOVR        | 0000 0100           | AC = R                                                                |

| JUMP        | 0000 0101 Г         | GOTO L                                                                |

| JMPZ        | 0000 0110 Г         | IF (Z=1) THEN GOTO $\Gamma$                                           |

| JPNZ        | 0000 0111 Г         | IF (Z=0) THEN GOTO $\Gamma$                                           |

| ADD         | 0000 1000           | AC = AC + R, If $(AC + R = 0)$ Then $Z = 1$ Else $Z = 0$              |

| SUB         | 0000 1001           | AC = AC - R, If $(AC - R = 0)$ Then $Z = 1$ Else $Z = 0$              |

| INAC        | 0000 1010           | AC = AC + 1, If $(AC + 1 = 0)$ Then $Z = 1$ Else $Z = 0$              |

| CLAC        | 0000 1011           | AC = 0, Z = 1                                                         |

| AND         | 0000 1100           | $AC = AC \wedge R$ , If $(AC \wedge R = 0)$ Then $Z = 1$ Else $Z = 0$ |

| OR          | 0000 1101           | $AC = AC \lor R$ , If $(AC \lor R = 0)$ Then $Z = 1$ Else $Z = 0$     |

| XOR         | 0000 1110           | $AC = AC \oplus R$ , If $(AC \oplus R = 0)$ Then $Z = 1$ Else $Z = 0$ |

| NOT         | 0000 1111           | AC = AC', If $(AC' = 0)$ Then $Z = 1$ Else $Z = 0$                    |

# **Simple Instruction Set**

- The final component is the instruction set architecture for this relatively simple CPU is shown in the table above.

- The LDAC, STAC, JUMP, JMPZ AND JPNZ instructions all require a 16-bit memory address represented by the symbol Γ.

- Since each byte of memory is 8-bit wide these instructions requires 3 bytes in memory. The first byte contains the opcode for the instruction and the remaining 2 bytes for the address.

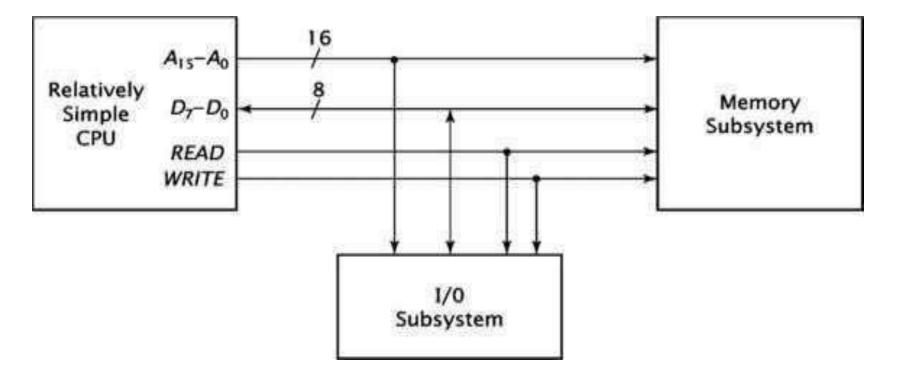

# **Relatively Simple Computer**

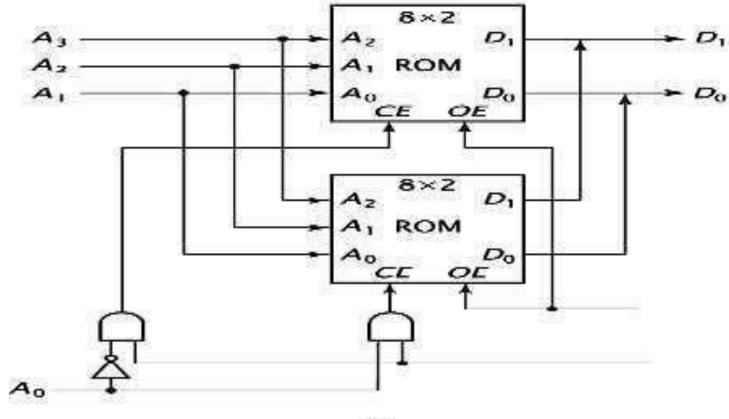

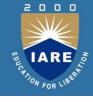

- In this relatively simple computer Figure 1:11 shown below, we put all the hard ware components of the computer together in one system. This computer will have 8K ROM starting at address 0 fallowed by 8K RAM. It also has a memory mapped bidirectional I/O port at address 8000H.

- First let us look at the CPU since it uses 16 bit address labeled A15 through A0. System bus via pins through D7 to D0. The CPU also has the two control lines READ and WRITE.

- Since it uses the memory mapped I/O it does not need a control signal such as .

- The relatively simple computer is shown in the figure below. It only contains the CPU details. Each part will be developed in the design.

### **Relatively Simple Computer**

2000

TARE PHON FOR LIBER

Figure 1:11: A relatively simple computer: CPU details only

# **Relatively Simple Computer**

- To access a memory chip the processor must supply an address used by the chip. An 8K memory chip has 213 internal memory locations it has 13bit address input to select one of these locations.

- The address input of each chip receives CPU address bits A12 to A0 from system address bus. The remaining three bits A15, A14, and A13 will be used to select one of the memory chips.

#### **MODULE-II**

### **ORGANIZATION OF A COMPUTER**

# **Course Outcomes**

- CO 1 Describe Register transfer languages, arithmetic micro operations, logic micro operations, shift micro operations address sequencing, micro program example, and design of control unit.

- CO 2 Classify the functionalities of various micro operations such as arithmetic, logic and shift micro operations.

- CO 3 Describe the Control unit and Control memory operations.

- CO 4 Knowledge about address sequencing in Control memory

- CO 5 Explore the micro program example and design of control unit

#### Contents

2000

#### **Register transfer:**

- Register transfer language

- Register transfer

- Bus and memory transfers

- Arithmetic micro operations

- Logic micro operations

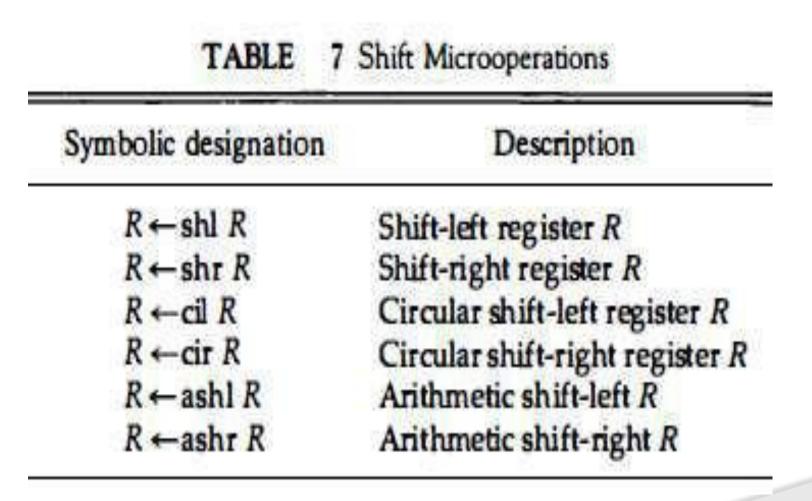

- Shift micro operations

**Control unit:**

- Control memory

- Address sequencing

- Micro program example

- and Design of control unit.

- A digital system is a Interconnection of digital hardware modules that accomplish a specific information processing task.

- Digital system uses a modular approach.

- The modules are constructed from such as digital components as registers ,decoders , arithmetic elements and control logic.

- The operations are performed on the data in the registers.

- The operations executed on the data in registers are called micro operations.

- The functions built into registers are examples of micro operations

- Shift

- Load

- Clear

- Increment .....

# **Register Transfer Language**

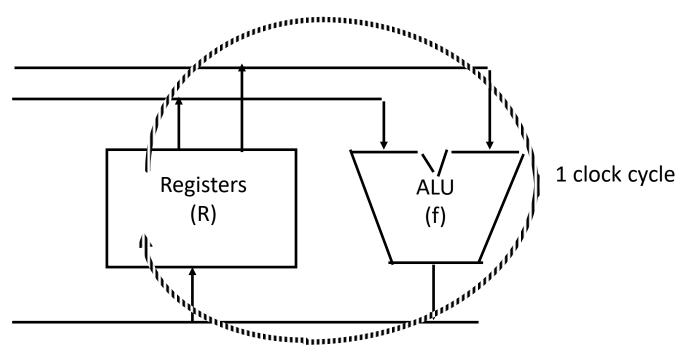

• The Micro operation is an elementary operation performed (during one clock pulse) on the information stored in one or more registers.

- $R \leftarrow f(R, R)$

- f: shift, load, clear, increment, add, subtract, complement, and, or, xor, ...

# **Register Transfer Language**

- The internal organization of a computer is Defined as:

- Set of registers and their functions

- Micro operations set

- Set of allowable microoperations provided by the organization of the computer

- Control signals that initiate the sequence of micro operations (to perform the functions)

• The symbolic notation used to describe the micro operation transfers among registers is called a register transfer language.

- Registers are designated by capital letters, sometimes followed by numbers (e.g., A, R13, IR)

- Often the names indicate function:

- MAR memory address register

- PC program counter

- IR instruction register

- Information Transfer from one register to another register is designated in symbolic form by using a replacement operator.

#### R2 ← R1

- Registers and their contents can be viewed and represented in *various ways*:

- A register can be viewed as a single entity:

- Registers may also be represented showing the bits of data they contain

7

6

5

4

3

2

1

0

Showing individual bits

- Numbering db a registers 0 R2

Numbering of bits

Portion of register

#### Subfields

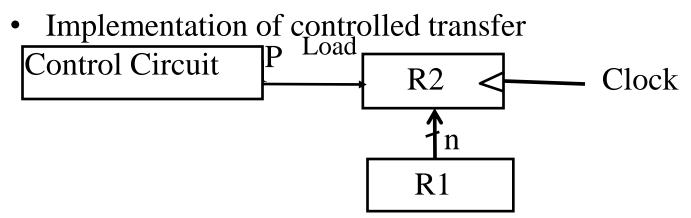

**Control Function**

- The actions are performed only when certain conditions are true.

- This is similar to an "if" statement in a programming language.

- In digital systems, this is often done via a control signal, called a control function . control function is a Boolean variable.

- If the signal is 1, the action takes place

- This is represented as:

P: R2  $\leftarrow$  R1

2000

• Which means "if P = 1, then load the contents of register R1 into register R2", i.e., if (P = 1) then (R2  $\leftarrow$  R1).

Fig: Block Diagram

• The same clock controls the circuits that generate the control function and the destination register.

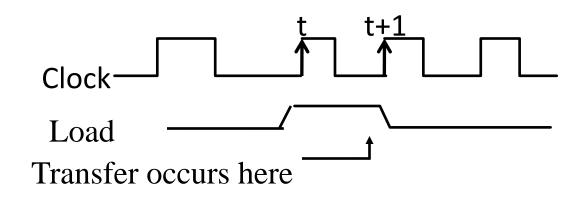

Fig :Timing Diagram

- If two or more operations are to occur simultaneously, they are separated with commas

- P:  $R3 \leftarrow R5,MAR \leftarrow IR$

- Here, if the control function P = 1, load the contents of R5 into R3, and at the same time (clock), load the contents of register IR into register MAR

- Basic Symbols Used for Register Transfer is

- Letters and Numerals to denote a registers. Ex: MAR, IR, R2.

- Parentheses () to denote a part of a register . Ex: R2(0-7), R2(L).

- Arrow to denote transfer of Information. Ex: R2 R1

- Comma , Separates two micro operations . Ex:  $R2 \leftarrow R1, R3 \leftarrow R4$

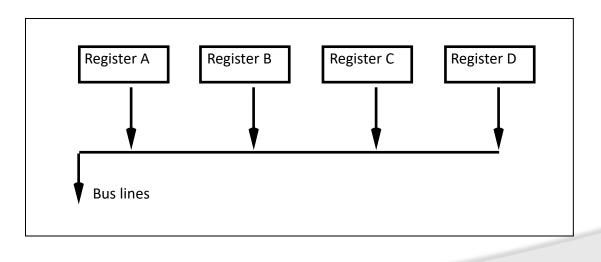

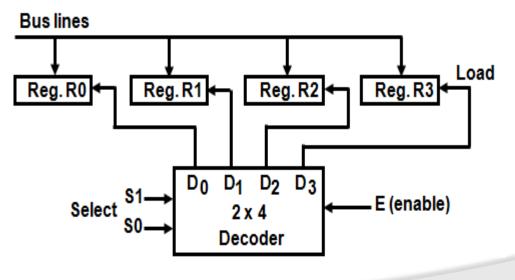

- In a digital system with many registers, it is impractical to have data and control lines to directly allow each register to be loaded with the contents of every possible other registers

- To completely connect n registers  $\rightarrow$  n(n-1) lines

- $O(n^2) \cos t$

- This is not a realistic approach to use in a large digital system

- Instead, take a different approach

- Have one centralized set of circuits for data transfer the bus

- Have control circuits to select which register is the source, and which is the destination

- Bus is a path(of a group of wires) over which information is transferred, from any of several sources to any of several destinations.

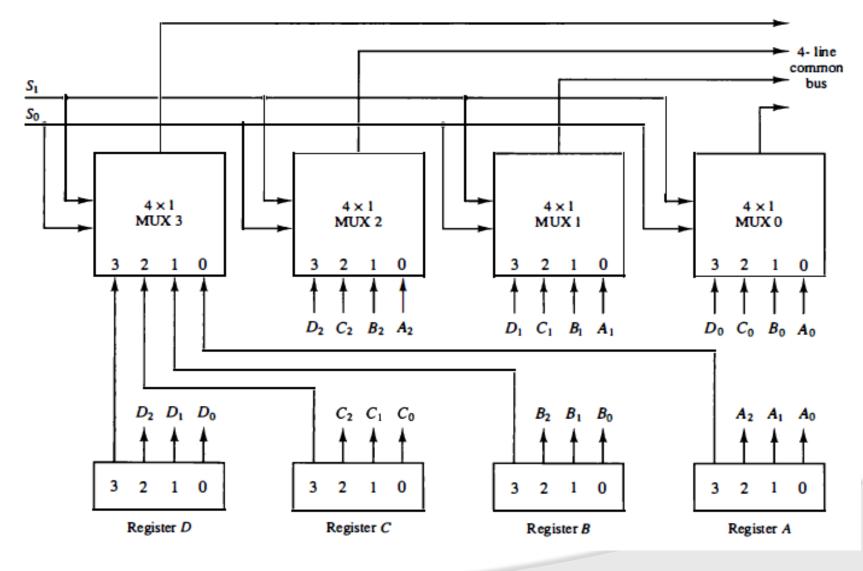

- One way to construct a common bus system is by using multiplexers.

- The multiplexer select the source register whose binary information is then placed into the bus.

- To transfer data from  $R1 \leftarrow C$ . i.e  $BUS \leftarrow C$ ,  $R1 \leftarrow BUS$

| S1 | S2 | Register Selected |

|----|----|-------------------|

| 0  | 0  | A                 |

| 0  | 1  | В                 |

| 1  | 0  | C                 |

| 1  | 1  | D                 |

#### Function Table For Bus

#### Fig : Transfer From Bus to Destination Register

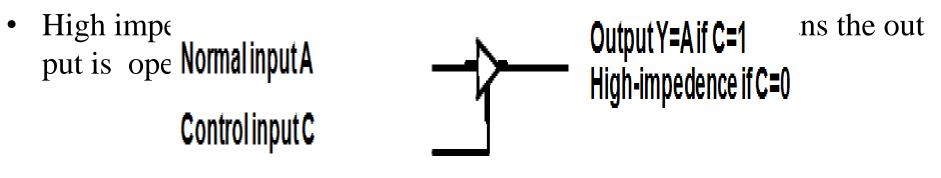

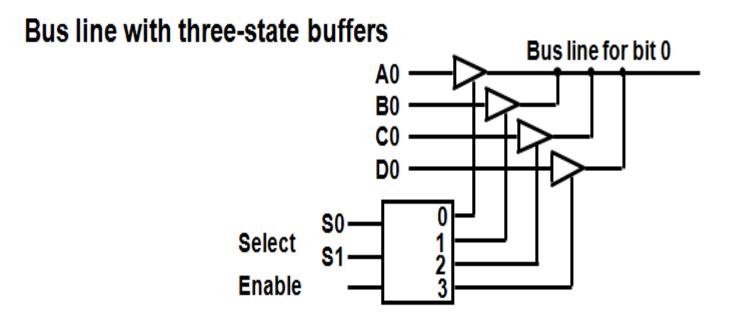

- A bus system can be implemented with three state gates instead of multiplexers.

- A three state gate is a digital circuit that exhibits three states.

- Two sates are normal signal states 1 and 0. The third state is a high impedance state.

Fig: Graphic Symbol for Three State buffer

### **Three State Bus Buffers**

0 0 0

Fig : Bus Line with three state –Buffer

• To Construct a Common bus for four registers of n bits each using three state-bus buffer, we need n circuits with four buffers.

# **Memory Transfer**

- The transfer of information from memory word to the outside environment is called Memory read operation.

- The transfer of new information to be stored into the memory is called memory write operation.

- Memory word is symbolically represented by using letter M.

Read :  $DR \leftarrow M[AR]$ Write :  $M[AR] \leftarrow R1$

#### SUMMARY OF R. TRANSFER MICROOPERATIONS

|        | 2  |      |     |     |    |

|--------|----|------|-----|-----|----|

|        |    | 11   | 11  |     |    |

|        | -  | 7    | 1/2 |     |    |

| $\sim$ | 1  |      |     |     |    |

| ED     |    | A    | R   | E/  | NO |

| 60     | 2. |      |     |     |    |

|        | 10 | N FC |     | BET |    |

|        |    |      |     |     |    |

| A ← B                    | Transfer content of reg. B into reg. A                   |

|--------------------------|----------------------------------------------------------|

| $AR \leftarrow DR(AD)$ T | ransfer content of AD portion of reg. DR into reg. AR    |

| $A \leftarrow constant$  | Transfer a binary constant into reg. A                   |

| $ABUS \leftarrow R1$ ,   | Transfer content of R1 into bus A and, at the same time, |

| $R2 \leftarrow ABUS$ t   | ransfer content of bus A into R2                         |

| AR                       | Address register                                         |

| DR                       | Data register                                            |

| M[R]                     | Memory word specified by reg. R                          |

| Μ                        | Equivalent to M[AR]                                      |

| $DR \leftarrow M$        | Memory read operation: transfers content of              |

|                          | memory word specified by AR into DR                      |

| $M \leftarrow DR$        | Memory write operation: transfers content of             |

|                          | DR into memory word specified by AR                      |

|                          |                                                          |

# **Micro Operations**

- Micro operation is an elementary operation performed with the data stored in registers.

- Computer system micro operations are of four types:

- 1. Register transfer micro operations

- 2. Arithmetic micro operations

- 3. Logic micro operations

- 4. Shift micro operations

- In register transfer micro operations the contents of the register can not be altered when transfer the data from the source to destination.

- The remaining three micro operations alter the data when transfer the data from one place to another.

# **Micro Operations**

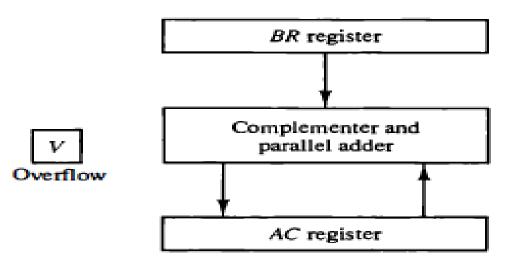

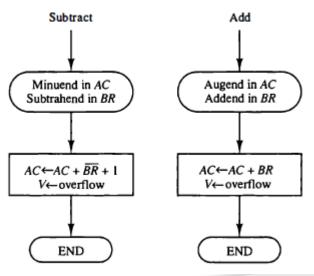

#### Arithmetic Micro Operations

- The basic arithmetic micro operations are addition , subtraction , increment , decrement and shift operations.

- $R1 \leftarrow R2 + R3$  this micro operation specifies an add operation .

- It states that the contents of register R2 and R3 are added and result stored into register R1.

- R1←R2+R3+1(R2-R3) this micro operation specifies a subtract operation.

- The subtract operation is implemented through complementation and addition.

#### Arithmetic Micro Operations

| R3 ← R1 + R2                | Contents of R1 plus R2 transferred to R3   |

|-----------------------------|--------------------------------------------|

| R3 ← R1 - R2                | Contents of R1 minus R2 transferred to R3  |

| R2 ← R2                     | Complement the contents of R2              |

| R2 ← R2 + 1                 | 2's complement the contents of R2 (negate) |

| $R3 \leftarrow R1 + R2 + 1$ | subtraction                                |

| <b>R1 ← R1 + 1</b>          | Increment                                  |

| R1 ← R1 - 1                 | Decrement                                  |

# **Micro Operations**

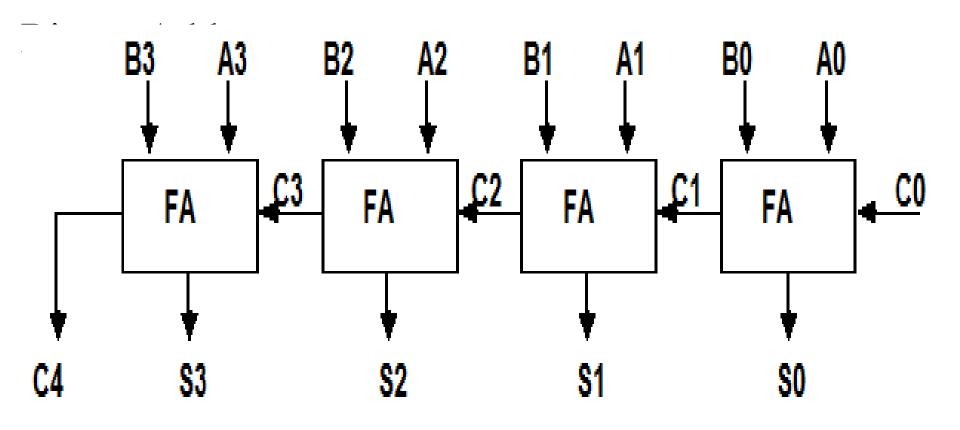

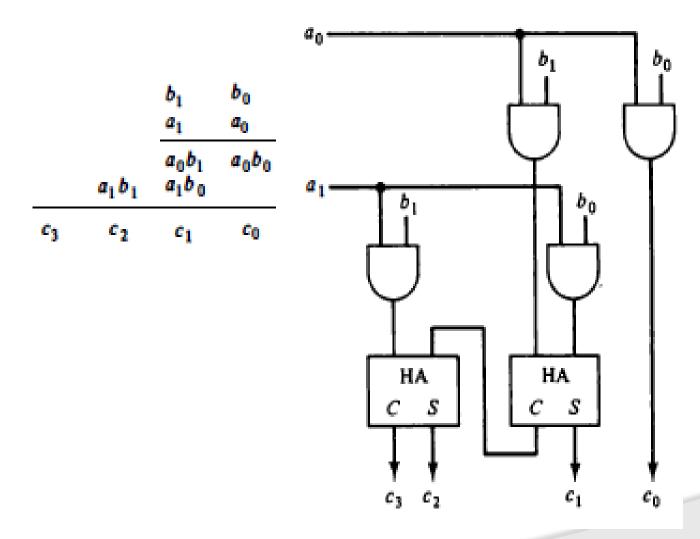

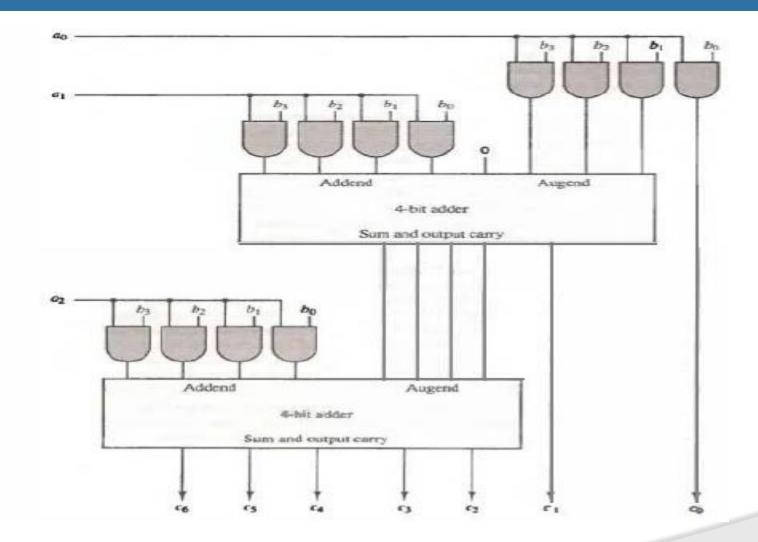

# Binary Adder

- Basic hardware required to implement add operation is registers and digital component that perform add operation.

- The digital circuit that forms the arithmetic sum of two bits and previous carry is called a full adder.

- The digital circuit that generates the arithmetic sum of two binary numbers of any length is called a binary adder.

- The binary adder is constructed with full adder circuits connected in cascade , with the out put carry from one full adder connected to the input carry of the next full adder.

- An n bit binary adder requires n full adders.

- The output carry from each full adder is connected to the input carry of the next-higher –order full adder.

## **Micro Operations**

Fig: 4-bit binary adder

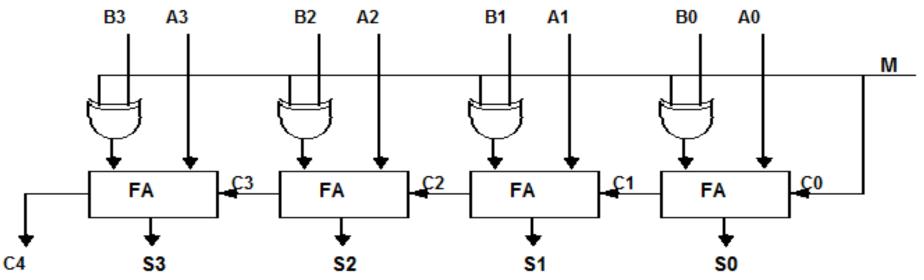

#### **Binary Adder- Sub tractor**

2000

- The Subtraction of A-B can be done by taking the 2's Complement of B and adding it to A.

- The addition and subtraction can be implemented by one common

Fig: 4-bit Adder- subtractor

# **Binary Adder- Sub tractor**

- Here the mode input M controls the operation.

- When M=0 the circuit works like an adder and M=1 the circuit works like a subtractor .

- Each exclusive-OR gate receives input M and one of the inputs of B.

- When M=0 the operation specifies  $B \bigoplus 0=B$ .

- The full-adder receives the value of B ,the input carry is 0 ,and the circuit performs A plus B.

- When M=1 the operation specifies  $B \oplus 1=B'$  and  $C_0=1$ .

- The B inputs are all complemented and 1 is added through the input carry .

- Then the circuit performs operation A +2's Complement of B.

- Unsigned Numbers it gives A-B if A>=B or the 2's complement of (B-A)if A<B.</li>

- Signed Numbers the result is A-B provided that there is no overflow.

## **Binary Incrementer**

0 0 0

- The increment micro operation adds one to a number in a register.

- This is implemented by using a binary counter.

- The binary counter is implemented by using half adders connected in **A2** casqade. **A**1 AO Х х Х х V HA HA HA HA S С S С S С S **S**3 **S2 SO S1**

Fig : 4- bit binary Incrementer

- One of the inputs to the least significant half adder (HA)is connected to logic-1 and the other input is connected to the least significant bit of the number to be incremented.

- The output carry from one half adder is connected to one of the inputs of the next-higher-order half adder.

- The generated out is displayed in s0 through s3.

- The above circuit can be implemented to an n-bit binary incermenter by including n-half adders.

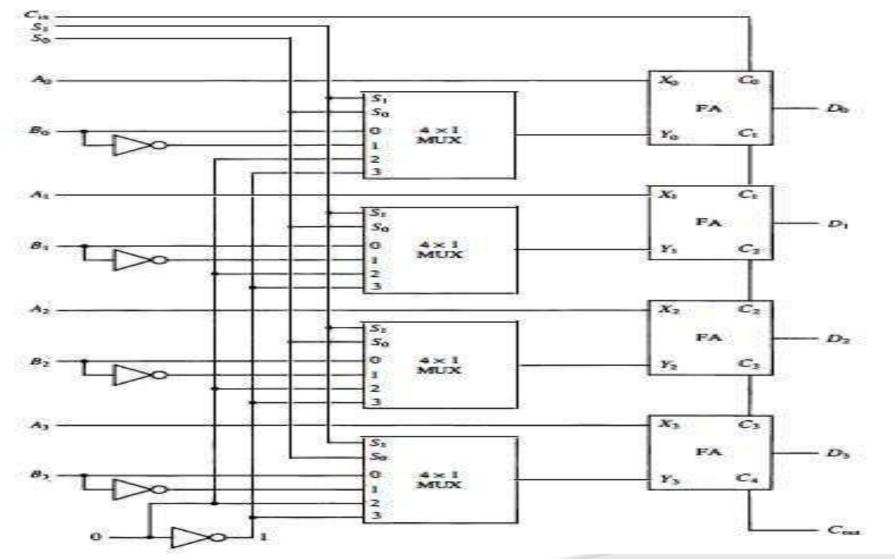

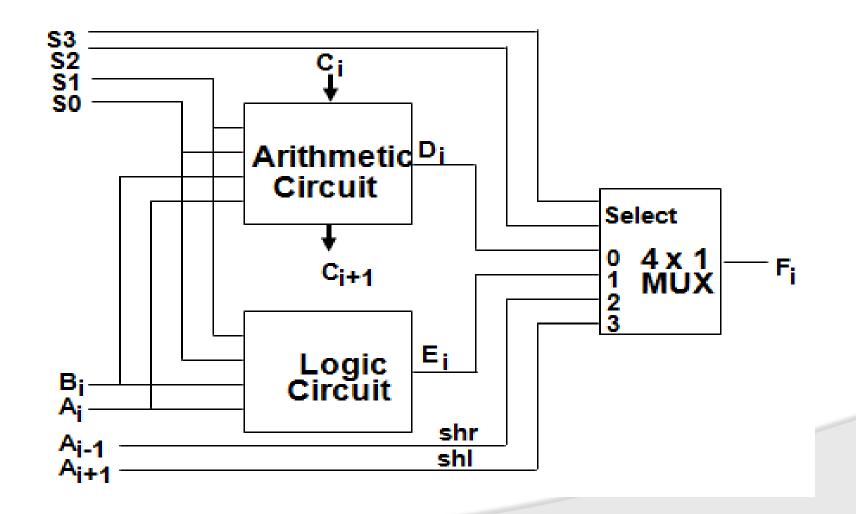

- The arithmetic operation can be implemented by using single composite arithmetic circuit.

- The basic component of an arithmetic circuit is parallel adder. By controlling the input of the parallel adder we obtain the different types of arithmetic operations.

- In a 4-bit Arithmetic circuit it contains 4 full adders and four multiplexers to choose different operations.

- There are two 4-bit inputs A and B and a 4-bit output D.

- The four Inputs From A directly connected to Adder and the B input is given to input of Multiplexers.

- The multiplexers data also receives the complement of B .

- The remaining two data inputs are connected to the Logic-0 and 1.

- The four multiplexers are controlled by two selection inputs , S1 and S0.

Fig: 4-bit Arithmetic circuit

- The input carry Cin goes to the carry input of the FA in the least significant position .

- The other carries a connected from one stage to the next.

- The output of the Binary Adder is calculated by using Arithmetic sum D=A+Y+Cin

- here A is 4-bit Binary number at X inputs.

Y is 4-bit binary number at Y inputs of the binary adder. Cin is the input carry.

• In the above equation by controlling the value of Y with two control inputs S1 and S0 and making the Cin 1 or 0 the above circuit performs all the arithmetic operations.

| <b>S1</b> | SO | Cin | Y | Output                 | Microoperation       |

|-----------|----|-----|---|------------------------|----------------------|

| 0         | 0  | 0   | В | D=A+B                  | Add                  |

| 0         | 0  | 1   | В | D=A+B+1                | Add with carry       |

| 0         | 1  | 0   | В | $D = A + \overline{B}$ | Subtract with borrow |

| 0         | 1  | 1   | В | D = A + B+ 1           | Subtract             |

| 1         | 0  | 0   | 0 | D=A                    | Transfer A           |

| 1         | 0  | 1   | 0 | D=A+1                  | Increment A          |

| 1         | 1  | 0   | 1 | D=A-1                  | DecrementA           |

| 1         | 1  | 1   | 1 | D=A                    | Transfer A           |

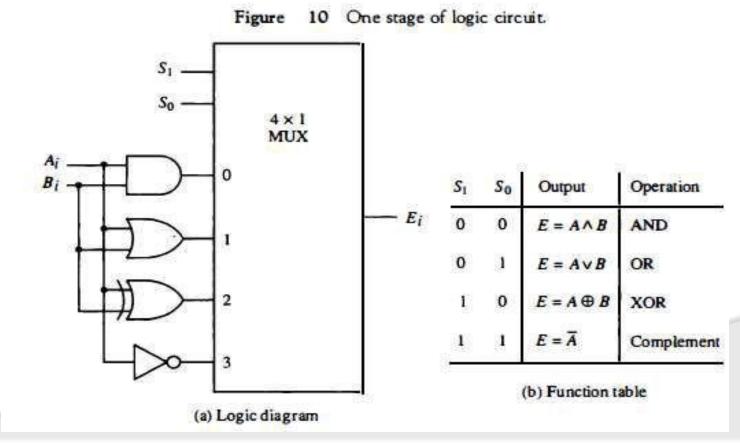

- Logic micro operations specify the operations for strings of bits stored in registers.

- Logic microoperations are bit-wise operations, i.e., they work on the individual bits of data.

- The logic microoperation exclusive-OR with the contents of two registers R1 and R2 is symbolized by the statement:

$P: R1 \leftarrow R1 \oplus R2$

Ex: R1=1010 R2=1100 if P=1 then 1010 = R11100 = R20110 = R1 after P=1

| Name     | Graphic<br>symbol | Algebraic<br>function     | Truth<br>table                                                                                                                                        |

|----------|-------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| AND      |                   | $x = A \cdot B$<br>x = AB | A         B         x           0         0         0           0         1         0           1         0         0           1         1         1 |

| OR       |                   | - x x = A + B             | A B x<br>0 0 0<br>0 1 1<br>1 0 1<br>1 1 1                                                                                                             |

| Inverter | A                 | x x = A'                  | A x<br>0 1<br>1 0                                                                                                                                     |

| Buffer   |                   | — I X = A                 | A x<br>0 0<br>1 1                                                                                                                                     |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | - |    |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|----|

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A | B | x  |

| NAND            | $A = (AB)^{\prime}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0 | 0 | I. |

|                 | B - (36)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0 | 1 | 1  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 | 0 | 1  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 |   | 0  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |   |    |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A | B | x  |

| NOR             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0 | 0 | 1  |

| NUK             | $a = \frac{1}{B} = $ | ō |   | ò  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ĩ | ō | 0  |

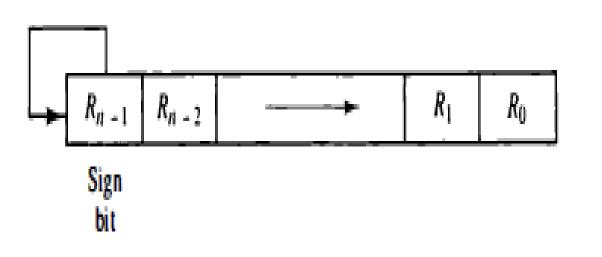

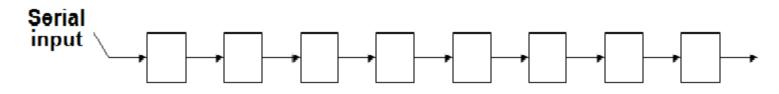

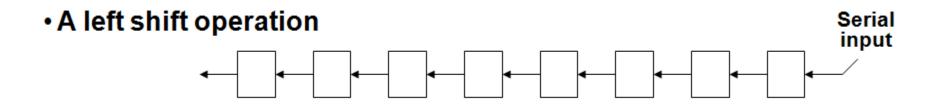

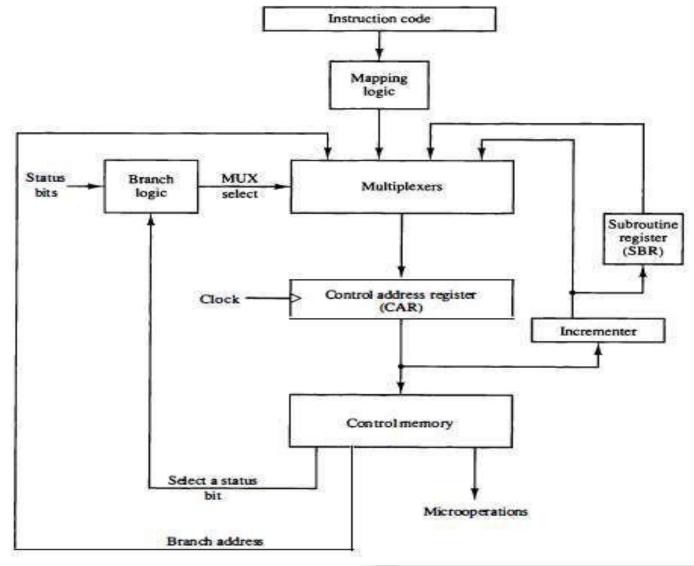

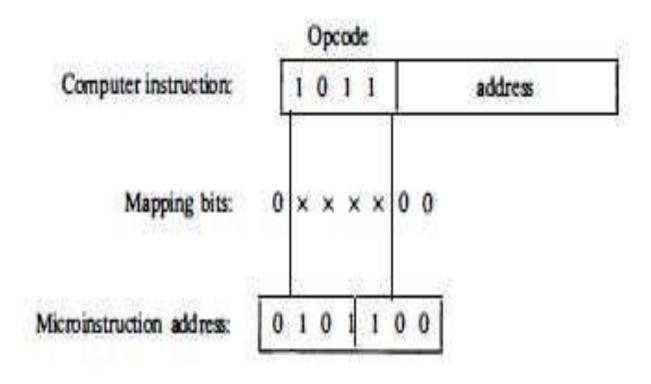

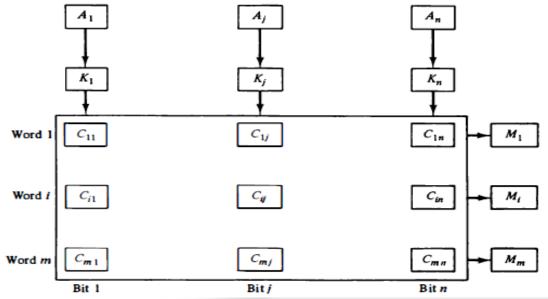

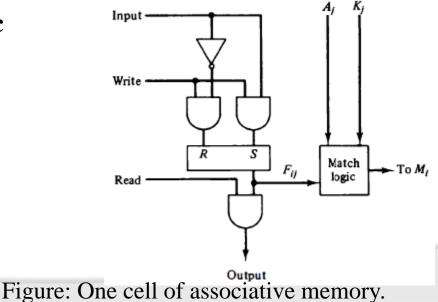

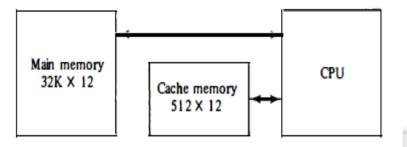

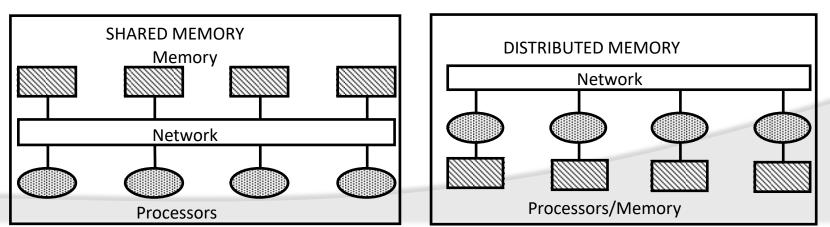

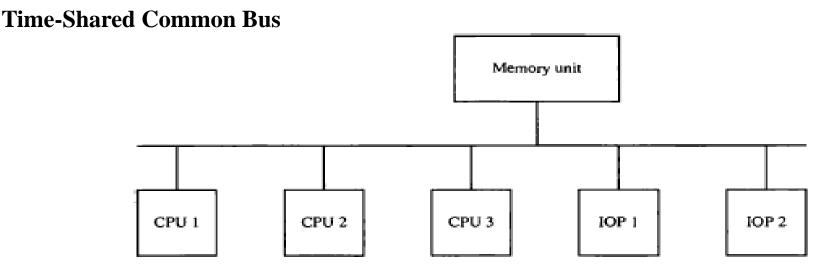

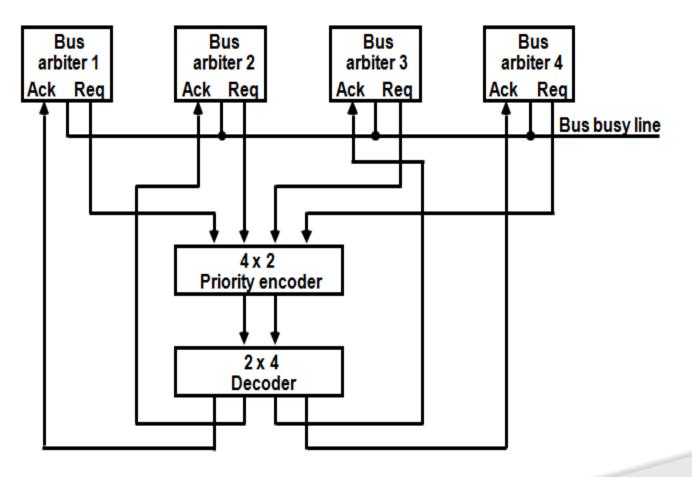

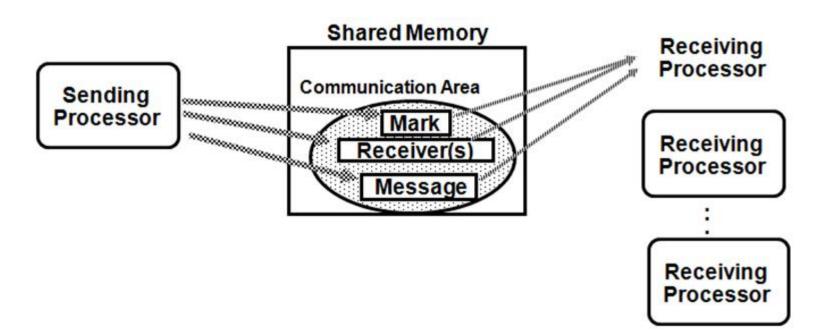

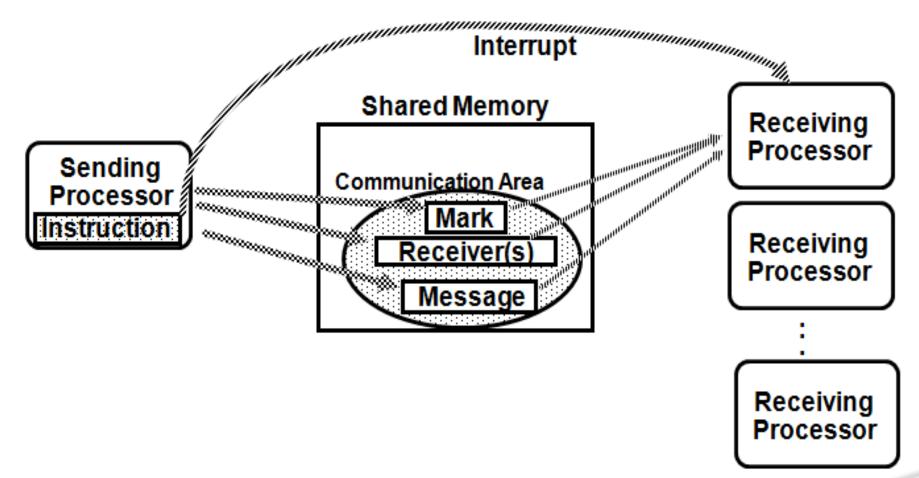

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | i | ĩ | õ  |