## MICRO PROCESSORS AND INTERFACING V Semester – IT IARE-R18 A.Y: 2020-2021 Course Code – AECB55 (Open Elective-1)

INSTITUTE OF AERONAUTICAL ENGINEERING Prepared By B. Lakshmi Prasanna

| MODULE-I   | INTRODUCTION TO 8 BIT AND 16 BIT<br>MICROPROCESSOR |

|------------|----------------------------------------------------|

| MODULE-II  | <b>OPERATION OF 8086 AND INTERRUPTS.</b>           |

| MODULE-III | INTERFACING WITH 8086.                             |

| MODULE-IV  | ADVANCED MICRO PROCESSORS                          |

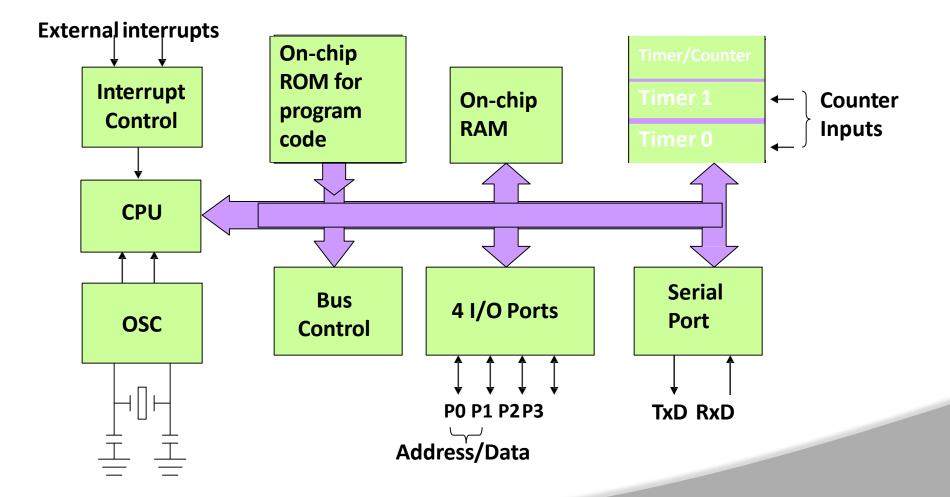

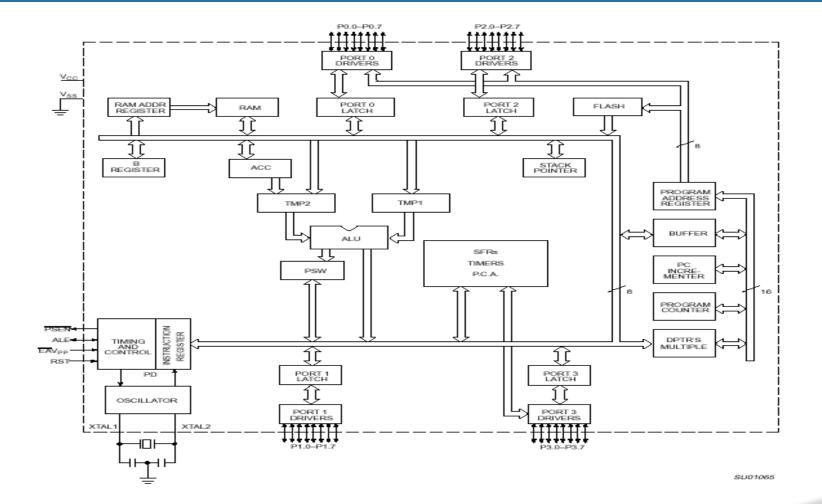

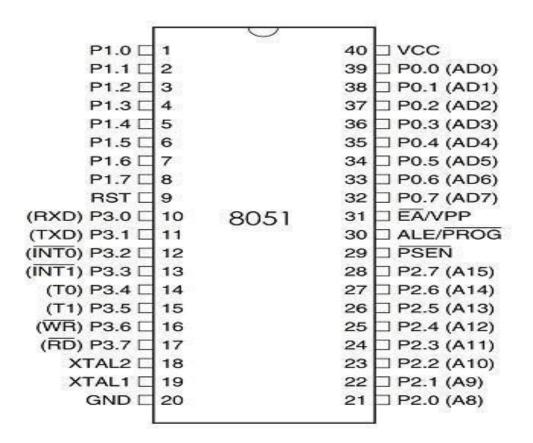

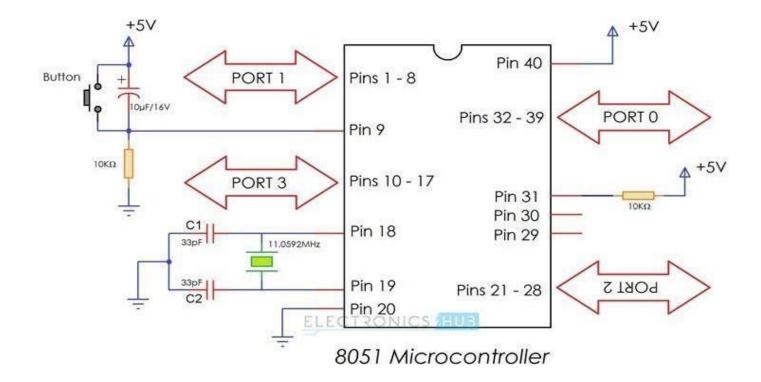

| MODULE-V   | 8051 MICROCONTROLLER ARCHITECTURE                  |

## **COURSE OUTCOMES**

| CO1 | Outline the internal architecture of 8085, 8086 and 8051 microcomputers to study the functionality.                                                    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| CO2 | Illustrate the organization of registers and memory in 8086 for programming and memory allocation within processor.                                    |

| CO3 | Explain various addressing modes and instruction set of target<br>microprocessor and microcontroller useful for writing assembly<br>language programs. |

| CO4 | Distinguish between minimum mode and maximum mode operation of 8086 microprocessor with timing diagrams.                                               |

| CO5 | Interpret the functionality of various types of interrupts and their structure for controlling the processor or controller and program execution flow. |

4

| CO6        | Demonstrate the internal architecture and various modes of operation of the devices used for interfacing memory and I/O devices with microprocessor.                       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>CO7</b> | Choose an appropriate data transfer scheme and hardware to perform serial data transfer among the devices.                                                                 |

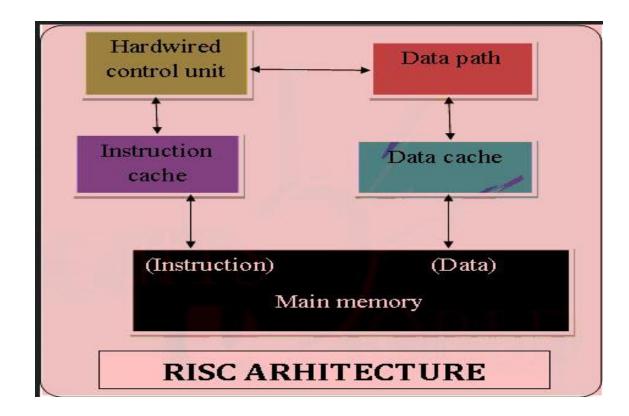

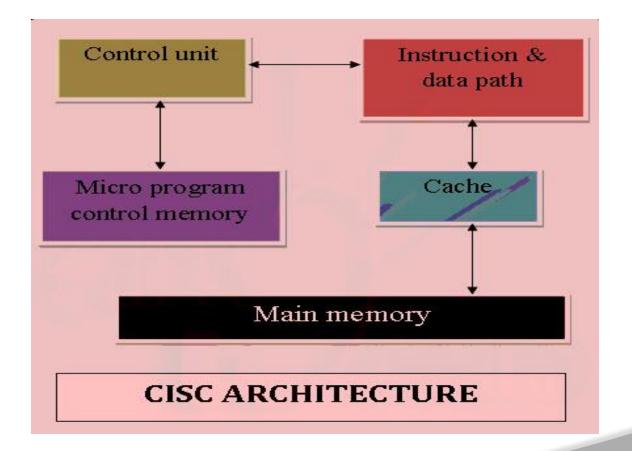

| CO8        | Outline the salient features of 80286, 80386 and RISC processors in relation to basic 8086 microprocessor.                                                                 |

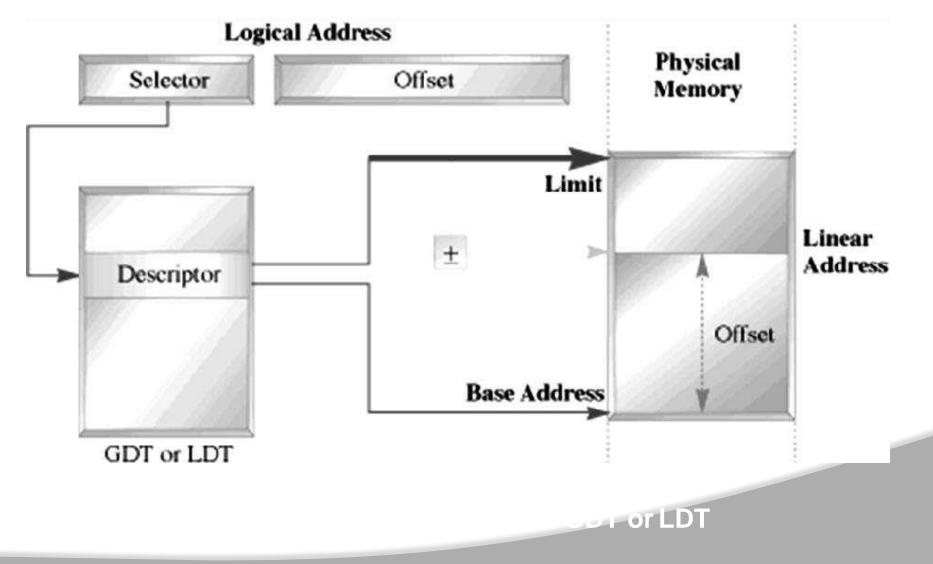

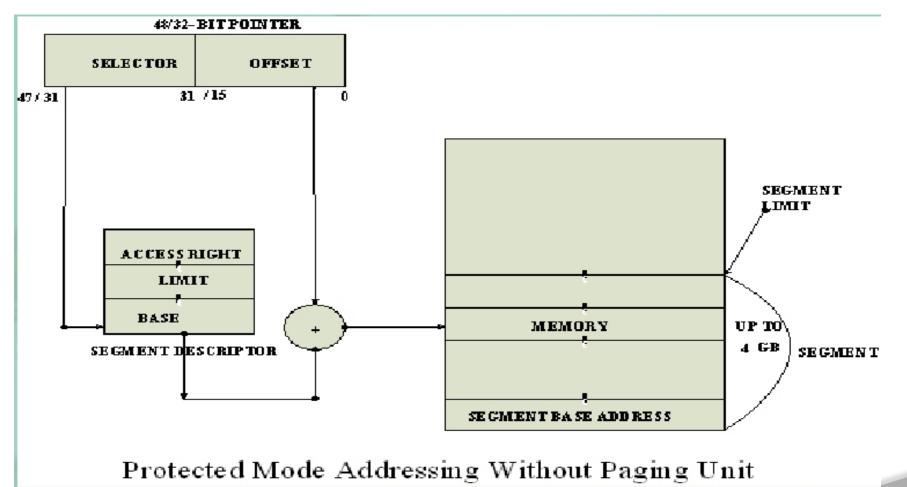

| CO9        | Illustrate the paging operation and segmentation of advanced microprocessors for memory management.                                                                        |

| CO10       | Interpret the internal building blocks and registers of 8051 microcontroller used to perform serial data transfer, timer operation, interfacing of memory and I/O devices. |

| CO11       | Build necessary hardware and software interface using microcomputer based systems to provide solution for real world problems.                                             |

## MODULE-I Introduction to 8 bit and 16 bit Microprocessor

| <b>CO1</b> | Outline the internal architecture of 8085, 8086 and 8051 microcomputers to study the functionality.                                              |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| CO2        | Illustrate the organization of registers and memory in 8086 for programming and memory allocation within processor.                              |

| CO3        | Explain various addressing modes and instruction set of target microprocessor and microcontroller useful for writing assembly language programs. |

## An over view of 8085

#### Introduction to processor:

- A processor is the logic circuitry that responds to and processes the basic instructions that drives a computer.

- The term processor has generally replaced the term central processing unit. The processor in a personal computer or embedded in small devices is often called a microprocessor.

- The processor (CPU, for Central Processing Unit) is the computer's brain. It allows the processing of numeric data, meaning information entered in binary form, and the execution of instructions stored in memory.

#### **Evolution of Microprocessor:**

- Microprocessor is a program-controlled device, which fetches the instructions from memory, decodes and executes the instructions. Most Micro Processor are single- chip devices.

- Microprocessor is a backbone of computer system. which is called CPU

- Microprocessor speed depends on the processing speed depends on DATA BUS WIDTH.

- A common way of categorizing microprocessors is by the no. of bits that their ALU can Work with at a time

- The address bus is unidirectional because the address information is always given by the Micro Processor to address a memory location of an input / output devices.

- The data bus is Bi-directional because the same bus is used for transfer of data between Micro Processor and memory or input / output devices in both the direction.

- It has limitations on the size of data. Most Microprocessor does not support floating-point operations.

- Microprocessor contain ROM chip because it contain instructions to execute data.

- Storage capacity is limited. It has a volatile memory. In secondary storage device the storage capacity is larger. It is a nonvolatile memory.

Primary devices are: RAM (Read / Write memory, High Speed, Volatile Memory) / ROM (Read only memory, Low Speed, Non Voliate Memory)

Secondary devices are: Floppy disc / Hard disk

Compiler:

Compiler is used to translate the high-level language program into machine code at a time. It doesn't require special instruction to store in a memory, it stores automatically. The Execution time is less compared to Interpreter

## 8085 MICROPROCESSOR

- •It is an 8-bit microprocessor designed by Intel in 1977. It has the following configuration –(FEATURES)

- •8-bit data bus

- •16-bit address bus, which can address up to 64KB

- •A 16-bit program counter

- •A 16-bit stack pointer

- •Six 8-bit registers arranged in pairs: BC, DE, HL

- •Requires +5V supply to operate.

It is a single chip with 40 pins.

- It has multiplexed address and data bus(AD0 AD7)

- The maximum clock frequency is 3 MHz while minimum frequency is 500 KHz.

- It provides 74 instruction with 5 different addressing modes.

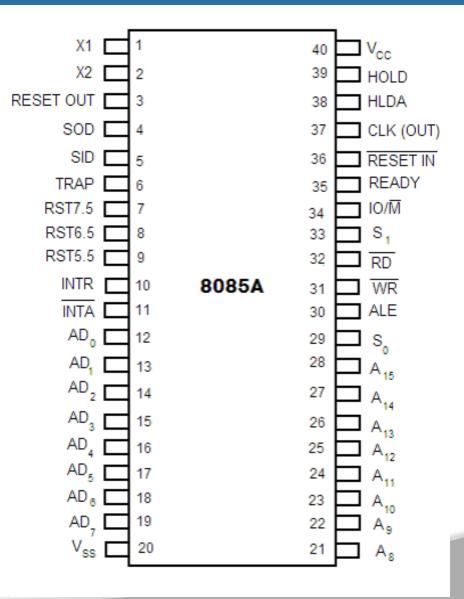

#### Pin Diagram of 8085

## **PIN DESCRIPTION**

#### Address bus

A15-A8, it carries the most significant 8-bits of memory/IO address. **Data bus**

AD7-AD0, it carries the least significant 8-bit address and data bus. **Power supply**

There are 2 power supply signals VCC & VSS. VCC indicates +5v power supply and VSS indicates ground signal.

#### **Control and status signals**

#### There are 3 control signal and 3 status signals.

- Three control signals are RD', WR' & ALE.

- **RD'** When it is enabled, CPU reads the data available on data bus send by memory or I/O device.

- **WR'** When it is enabled ,CPU write the data on to the data bus from memory or I/O device .

- **ALE** It is a multiplexed signal .When the pulse goes high, it indicates address. When the pulse goes down it indicates data.

#### Three status signals are IO/M', S0 & S1.

## IO/M'

This signal is used to differentiate between IO and Memory operations, i.e. when it is high indicates IO operation and when it is low then it indicates memory operation.

#### S1 & S0

These signals are used to identify the type of current operation.

|       | -  |    |                       |

|-------|----|----|-----------------------|

| IO/M' | S1 | S0 | DATA BUS STATUS       |

| 0     | 1  | 1  | Opcode fetch          |

| 0     | 1  | 0  | Memory read           |

| 0     | 0  | 1  | Memory write          |

| 1     | 1  | 0  | I/O read              |

| 1     | 0  | 1  | I/O write             |

| 1     | 1  | 1  | Interrupt acknowledge |

| 0     | 0  | 0  | Halt                  |

#### **Clock signals**

There are 3 clock signals, i.e. X1, X2, CLK OUT.

**X1, X2** – A crystal (RC, LC N/W) is connected at these two pins and is used to set frequency of the internal clock generator. This frequency is internally divided by 2.

**CLK OUT** – This signal is used as the system clock for devices connected with the microprocessor.

#### Interrupts & externally initiated signals

Interrupts are the signals generated by external devices to request the microprocessor to perform a task. There are 5 interrupt signals, i.e. TRAP, RST 7.5, RST 6.5, RST 5.5, and INTR.

**INTA'** – It is an interrupt acknowledgment signal.

**RESET IN'** – This signal is used to reset the microprocessor by setting the program counter to zero.

**RESET OUT** – This signal is used to reset all the connected devices when the microprocessor is reset.

**READY** – This signal indicates that the device is ready to send or receive data. If READY is low, then the CPU has to wait for READY to go high.

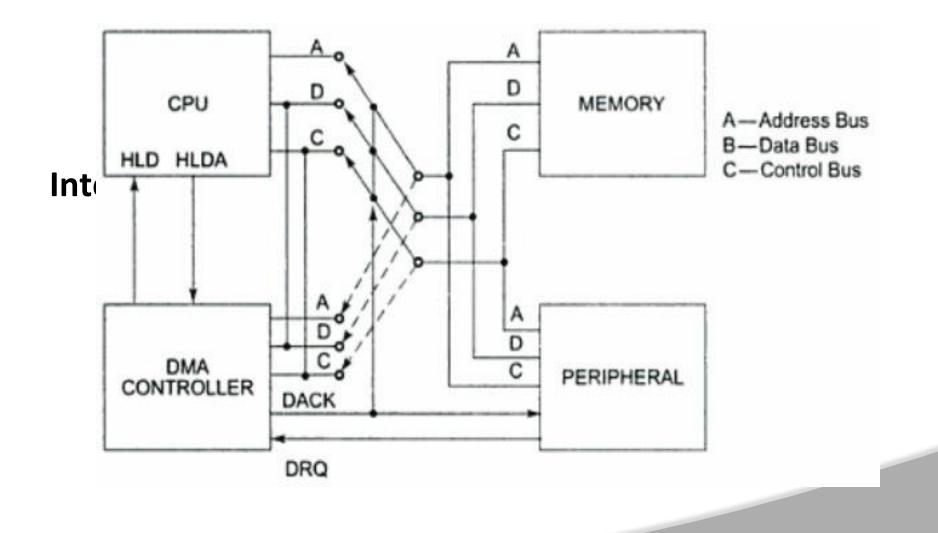

**HOLD** – This signal indicates that another master is requesting the use of the address and data buses.

**HLDA (HOLD Acknowledge)** – It indicates that the CPU has received the HOLD request and it will gives the bus in the next clock cycle. HLDA is set to low after the HOLD signal is removed.

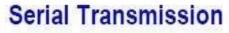

#### Serial I/O signals

There are 2 serial signals, i.e. SID and SOD and these signals are used for serial communication.

**SOD** (Serial output data line) – The output SOD is set/reset as specified by the SIM instruction.

**SID** (Serial input data line) – The data on this line is loaded into accumulator whenever a RIM instruction is executed.

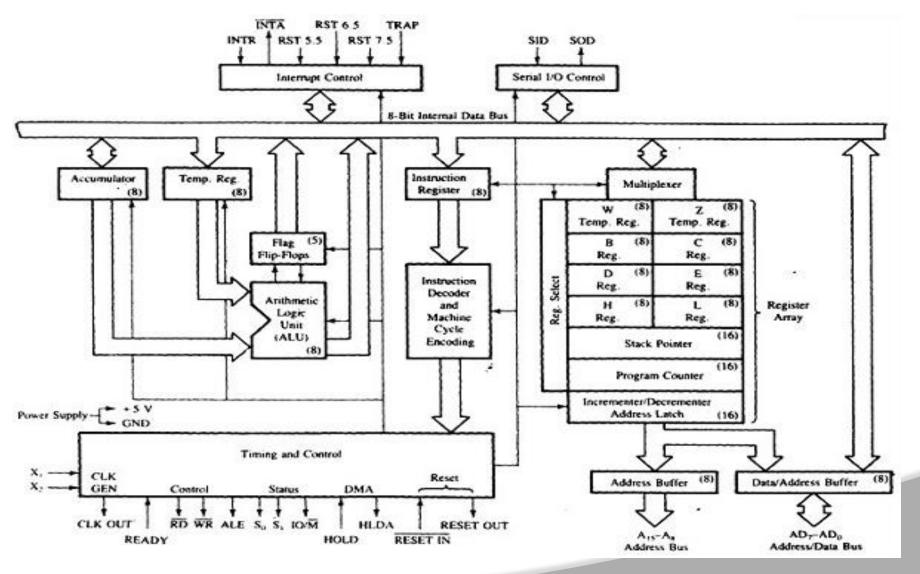

### **8085 ARCHITECTURE**

8085 consists of the following functional units -

Accumulator

It is an 8-bit register used to perform arithmetic, logical, I/O & LOAD/STORE operations. It is connected to internal data bus & ALU. Arithmetic and logic unit

As the name suggests, it performs arithmetic and logical operations like Addition, Subtraction, AND, OR, etc. on 8-bit data.

#### **General purpose register**

There are 6 general purpose registers in 8085 processor, i.e. B, C, D, E, H & L. Each register can hold 8-bit data.

These registers can work in pair to hold 16-bit data and their pairing combination is like B-C, D-E & H-L.

#### **Program counter**

It is a 16-bit register used to store the memory address location of the next instruction to be executed. Microprocessor increments the program counter whenever an instruction is being executed, so that the program counter points to the memory address of the next instruction that is going to be executed.

#### **Stack pointer**

It is also a 16-bit register works like stack, which is always incremented/decremented by 2 during push & pop operations.

#### **Temporary register**

It is an 8-bit register, which holds the temporary data of arithmetic and logical operations.

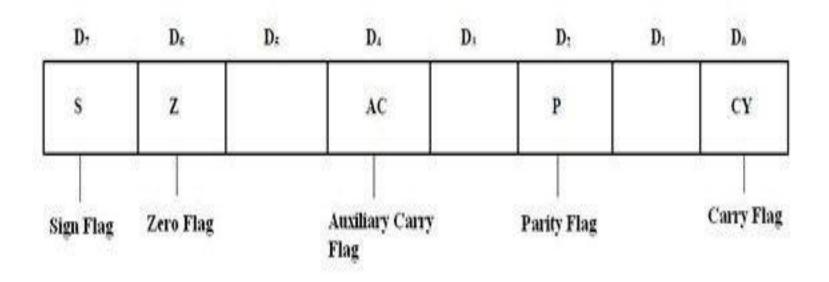

## Flag register

It is an 8-bit register having five 1-bit flip-flops, which holds either 0 or 1 depending upon the result stored in the accumulator.

These are the set of 5 flip-flops –

- i. Sign (S)

- ii. Zero (Z)

- iii. Auxiliary Carry (AC)

- iv. Parity (P)

- v. Carry (C)

#### Instruction register and Instruction decoder

It is an 8-bit register. When an instruction is fetched from memory then it is stored in the Instruction register. Instruction decoder decodes the information present in the Instruction register.

#### Timing and control unit

It provides timing and control signal to the microprocessor to perform operations. Following are the timing and control signals, which control external and internal circuits –

- Control Signals: READY, RD', WR', ALE

- Status Signals: S0, S1, IO/M'

- DMA Signals: HOLD, HLDA

- RESET Signals: RESET IN', RESET OUT

#### **Interrupt control**

As the name suggests it controls the interrupts during a process. When a microprocessor is executing a main program and whenever an interrupt occurs, the microprocessor shifts the control from the main program to process the incoming request. After the request is completed, the control goes back to the main program.

There are 5 interrupt signals in 8085 microprocessor: INTR, RST 7.5, RST 6.5, RST 5.5, TRAP.

#### Serial Input/output control

It controls the serial data communication by using these two instructions: SID (Serial input data) and SOD (Serial output data).

#### Address buffer and address-data buffer

The content stored in the stack pointer and program counter is loaded into the address buffer and address-data buffer to communicate with the CPU. The memory and I/O chips are connected to these buses; the CPU can exchange the desired data with the memory and I/O chips.

#### Address bus and data bus

Data bus carries the data to be stored. It is bidirectional, whereas address bus carries the location to where it should be stored and it is unidirectional. It is used to transfer the data & Address I/O devices.

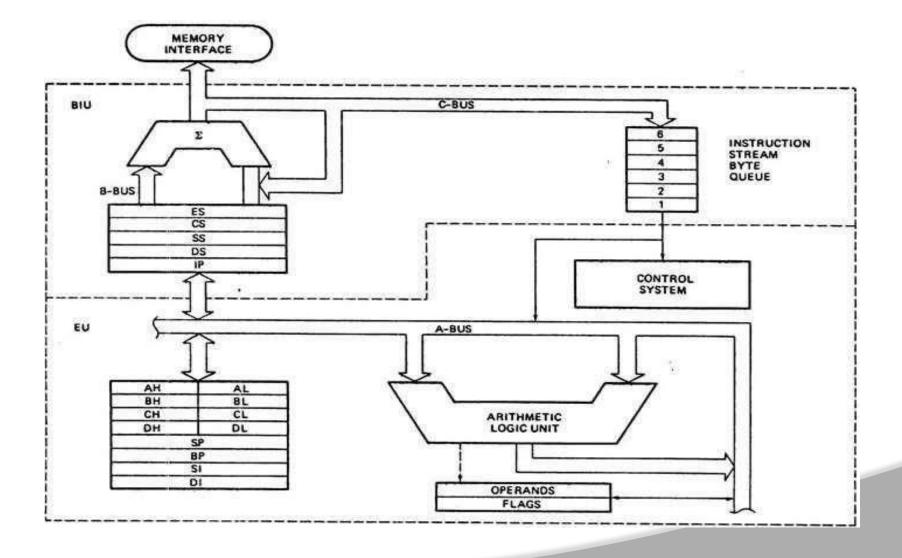

# Architecture of 8086 microprocessor

#### **Architecture :**

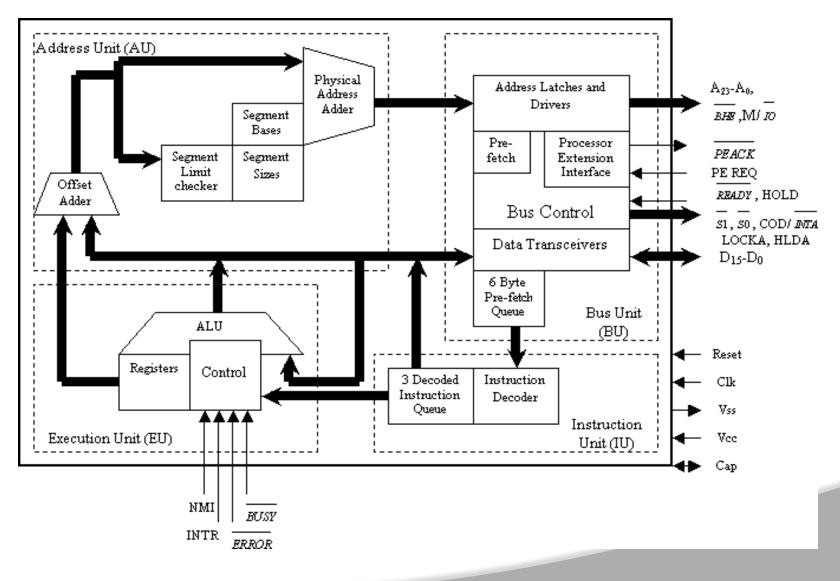

8086 Microprocessor is divided into two functional units, i.e., EU(Execution Unit) and BIU (Bus Interface Unit).

EU (Execution Unit):

- Execution unit gives instructions to BIU stating from where to fetch the data and then decode and execute those instructions.

- Its function is to control operations on data using the instruction decoder & ALU.

- EU has no direct connection with system buses as shown in the above figure, it performs operations over data through BIU.

#### • BIU(Bus Interface Unit):

BIU takes care of all data and addresses transfers on the buses for the EU like sending addresses, fetching instructions from the memory, reading data from the ports and the memory as well as writing data to the ports and the memory. EU has no direction connection with System Buses so this is possible with the BIU. EU and BIU are connected with the Internal BUS.

## **Instruction queue**

BIU contains the instruction queue. BIU gets up to 6 bytes of next instructions and stores them in the instruction queue.

When EU executes instructions and is ready for its next instruction, then it simply reads the instruction from this instruction queue resulting in increased execution speed.

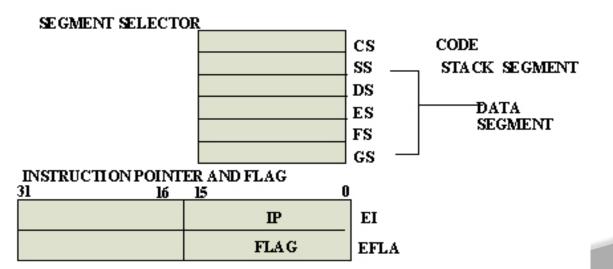

#### • Segment register:

- BIU has 4 segment buses, i.e. CS, DS, SS& ES. It holds the addresses of instructions and data in memory, which are used by the processor to access memory locations.

- It also contains 1 pointer register IP, which holds the address of the next instruction to executed by the EU.

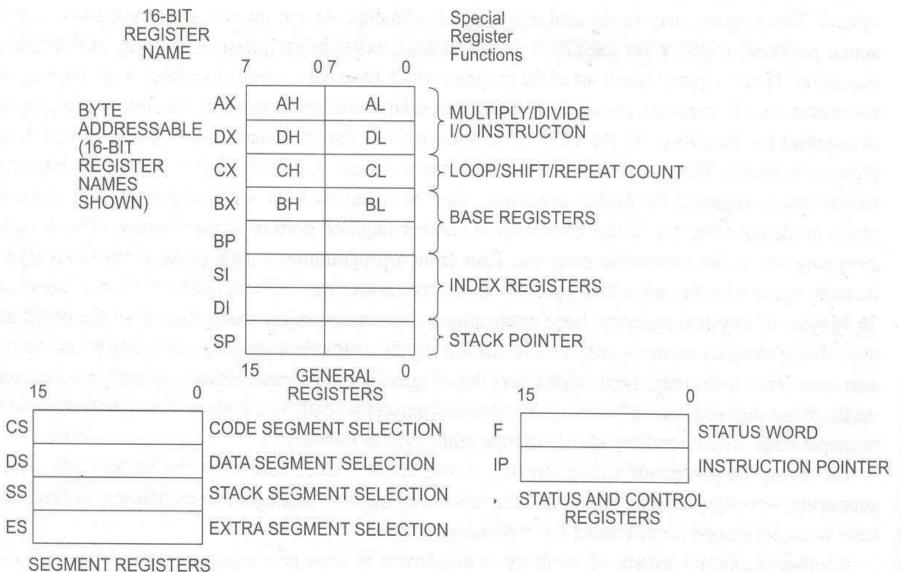

# Register organization of 8086

#### **AX & DX registers:**

- In 8 bit multiplication, one of the operands must be in AL.

The other operand can be a byte in memory location or in another 8 bit register. The resulting 16 bit product is stored in AX, with AH storing the MS byte.

- In 16 bit multiplication, one of the operands must be in AX.

The other operand can be a word in memory location or in another 16 bit register. The resulting 32 bit product is stored in DX and AX, with DX storing the MS word and AX storing the LS word.

#### **BX register :**

In instructions where we need to specify in a general purpose register the 16 bit effective address of a memory location, the register BX is used (register indirect).

### CX register :

- In Loop Instructions, CX register will be always used as the implied counter. In I/O instructions, the 8086 receives into or sends out data from AX or AL depending as a word or byte operation.

- In these instructions the port address, if greater than FFH has to be given as the contents of DX register.

- Ex : IN AL, DX

DX register will have 16 bit address of the I/P device

#### • Segment register:

- BIU has 4 segment buses, i.e. CS, DS, SS& ES. It holds the addresses of instructions and data in memory, which are used by the processor to access memory locations.

- It also contains 1 pointer register IP, which holds the address of the next instruction to executed by the EU.

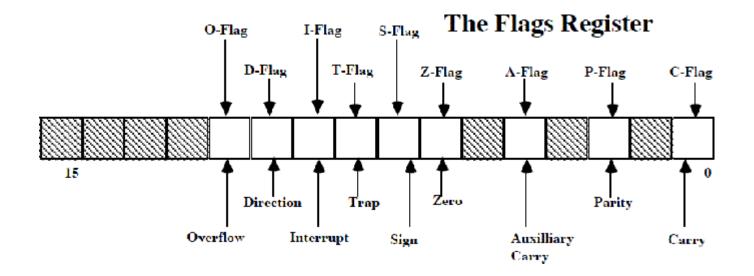

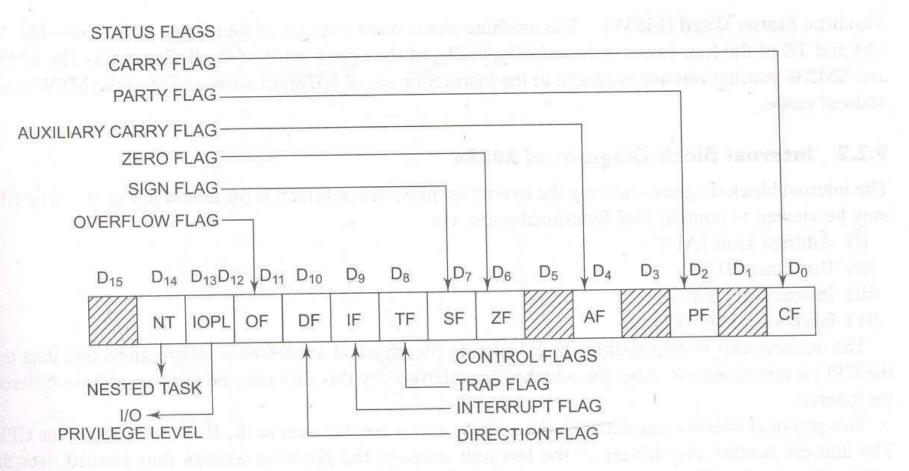

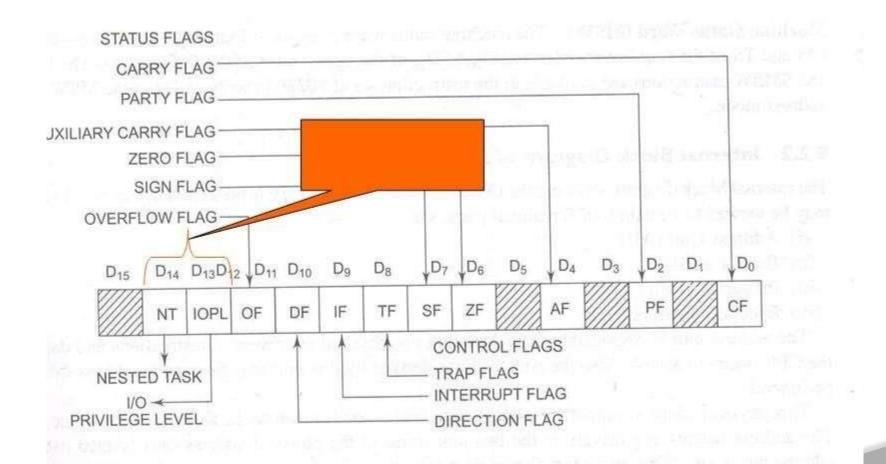

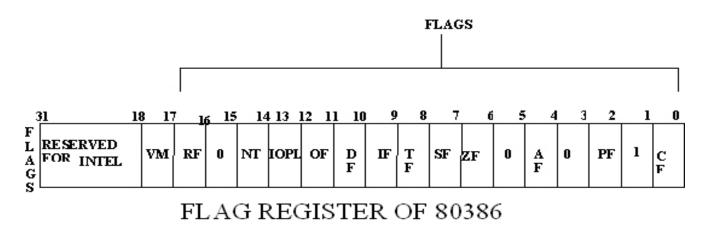

### 8086 flag register

#### **Flag Register**

- Flag Register contains a group of status bits called flags that indicate the status of the CPU or the result of arithmetic operations.

- There are two types of flags:

- The status flags which reflect the result of executing an instruction. The programmer cannot set/reset these flags directly.

- The control flags enable or disable certain CPU operations. The programmer can set/reset these bits to control the CPU's operation.

Nine individual bits of the status register are used as control flags (3 of them) and status flags (6 of them). The remaining 7 are not used.

A flag can only take on the values 0 and 1. We say a flag is set if it has the value 1. The status flags are used to record specific characteristics of arithmetic and of logical instructions.

- Control Flags: There are three control flags

- The Direction Flag (D): Affects the direction of moving data blocks by such instructions as MOVS, CMPS and SCAS. The flag values are 0 = up and 1 = down and can be set/reset by the STD (set D) and CLD (clear D) instructions.

- The Interrupt Flag (I): Dictates whether or not system interrupts can occur. Interrupts are actions initiated by hardware block such as input devices that will interrupt the normal execution of programs. The flag values are 0 = disable interrupts or 1 = enable interrupts and can be manipulated by the CLI (clear I) and STI (set I) instructions.

- The Trap Flag (T): Determines whether or not the CPU is halted after the execution of each instruction. When this flag is set (i.e. = 1), the programmer can single step through his program to debug any errors. When this flag = 0 this feature is off. This flag can be set by the INT 3 instruction.

- Status Flags: There are six status flags

- The Carry Flag (C): This flag is set when the result of an unsigned arithmetic operation is too large to fit in the destination register. This happens when there is an end carry in an addition operation or there an end borrows in a subtraction operation. A value of 1

- = carry and 0 = no carry.

- The Overflow Flag (O): This flag is set when the result of a signed arithmetic operation is too large to fit in the destination register (i.e. when an overflow occurs). Overflow can occur when adding two numbers with the same sign (i.e. both positive or both negative). A value of 1

= overflow and 0 = no overflow.

- The Sign Flag (S): This flag is set when the result of an arithmetic or logic operation is negative. This flag is a copy of the MSB of the result (i.e. the sign bit). A value of 1 means negative and 0 = positive.

- The Zero Flag (Z): This flag is set when the result of an arithmetic or logic operation is equal to zero. A value of 1 means the result is zero and a value of 0 means the result is not zero.

- The Auxiliary Carry Flag (A): This flag is set when an operation causes a carry from bit 3 to bit 4 (or a borrow from bit 4 to bit 3) of an operand. A value of 1 = carry and 0 = no carry.

- The Parity Flag (P): This flags reflects the number of 1s in the result of an operation. If the number of 1s is even its value = 1 and if the number of 1s is odd then its value = 0.

#### **Addressing Modes of 8086:**

- Addressing mode indicates a way of locating data or operands. Depending up on the data type used in the instruction and the memory addressing modes, any instruction may belong to one or more addressing modes or same instruction may not belong to any of the addressing modes.

- The addressing mode describes the types of operands and the way they are accessed for executing an instruction. According to the flow of instruction execution, the instructions may be categorized as

- Sequential control flow instructions and

- Control transfer instructions.

- Sequential control flow instructions are the instructions which after execution, transfer control to the next instruction appearing immediately after it (in the sequence) in the program. For example the arithmetic, logic, data transfer and processor control instructions are Sequential control flow instructions.

- The control transfer instructions on the other hand transfer control to some predefined address or the address somehow specified in the instruction, after their execution. For example INT, CALL, RET & JUMP instructions fall under this category.

- The addressing modes for Sequential and control flow instructions are explained as follows.

- Immediate addressing mode:

- In this type of addressing, immediate data is a part of instruction, and appears in the form of successive byte or bytes.

Example: MOV AX, 0005H.

- In the above example, 0005H is the immediate data

The immediate data may be 8- bit or 16-bit in size.

### Direct addressing mode:

In the direct addressing mode, a 16-bit memory address (offset) directly specified in the instruction as a part of it.

Example: MOV AX, [5000H].

### Register addressing mode:

In the register addressing mode, the data is stored in a register and it is referred using the particular register. All the registers, except IP, may be used in this mode.

Example: MOV BX, AX

#### Register indirect addressing mode:

- Sometimes, the address of the memory location which contains data or operands is determined in an indirect way, using the offset registers. The mode of addressing is known as register indirect mode.

- In this addressing mode, the offset address of data is in either BX or SI or DI Register. The default segment is either DS or ES.

Example: MOV AX, [BX].

- Indexed addressing mode:

- In this addressing mode, offset of the operand is stored one of the index registers. DS & ES are the default segments for index registers SI & DI respectively.

Example: MOV AX, [SI]

- Here, data is available at an offset address stored in SI in DS.

- Register relative addressing mode:

- In this addressing mode, the data is available at an effective address formed by adding an 8-bit or 16-bit displacement with the content of any one of the register BX, BP, SI & DI in the default (either in DS & ES) segment.

Example: MOV AX, 50H [BX]

- Based indexed addressing mode:

- The effective address of data is formed in this addressing mode, by adding content of a base register (any one of BX or BP) to the content of an index register (any one of SI or DI). The default segment register may be ES or DS.

Example: MOV AX, [BX][SI]

- Relative based indexed:

- The effective address is formed by adding an 8 or 16-bit displacement with the sum of contents of any of the base registers (BX or BP) and any one of the index registers, in a default segment.

Example: MOV AX, 50H [BX] [SI]

- Addressing Modes for control transfer instructions:

- Intersegment

- Intersegment direct

- Intersegment indirect

- Intrasegment

- Intrasegment direct

- Intrasegment indirect

0 0 0

#### • Intersegment direct:

In this mode, the address to which the control is to be transferred is in a different segment. This addressing mode provides a means of branching from one code segment to another code segment. Here, the CS and IP of the destination address are specified directly in the instruction.

Example: JMP 5000H: 2000H;

• Jump to effective address 2000H in segment 5000H.

#### • Intersegment indirect:

In this mode, the address to which the control is to be transferred lies in a different segment and it is passed to the instruction indirectly, i.e. contents of a memory block containing four bytes,

i.e. IP(LSB), IP(MSB), CS(LSB) and CS(MSB) sequentially. The starting address of the memory block may be referred using any of the addressing modes, except immediate mode.

• Example: JMP [2000H].

Jump to an address in the other segment specified at effective address 2000H in DS.

#### • Intrasegment direct mode:

In this mode, the address to which the control is to be transferred lies in the same segment in which the control transfers instruction lies and appears directly in the instruction as an immediate displacement value. In this addressing mode, the displacement is computed relative to the content of the instruction pointer.

E LARE

The effective address to which the control will be transferred is given by the sum of 8 or 16 bit displacement and current content of IP. In case of jump instruction, if the signed displacement (d) is of 8-bits (i.e. -128<d<+127), it as short jump and if it is of 16 bits (i.e. - 32768<d<+32767), it is termed as long jump.</p>

Example: JMP SHORT LABEL.

#### Intrasegment indirect mode:

- In this mode, the displacement to which the control is to be transferred is in the same segment in which the control transfer instruction lies, but it is passed to the instruction directly. Here, the branch address is found as the content of a register or a memory location.

- This addressing mode may be used in unconditional branch instructions.

- Example: JMP [BX]; Jump to effective address stored in BX.

# Instruction set of 8086

### **INSTRUCTION SET OF 8086**

- The Instruction set of 8086 microprocessor is classified into 7 Types, they are:-

- Data transfer instructions

- Arithmetic& logical instructions

- Program control transfer instructions

- Machine Control Instructions

- Shift / rotate instructions

- Flag manipulation instructions

- String instructions

#### **Data Transfer instructions**

Oata transfer instruction, as the name suggests is for the transfer of data from memory to internal register, from internal register to memory, from one register to another register, from input port to internal register, from internal register to output port etc

#### **MOV** instruction

It is a general purpose instruction to transfer byte or word from register to register, memory to register, register to memory or with immediate addressing.

- General Form:

- MOV destination, source

- Here the source and destination needs to be of the same size,

that is both 8 bit or both 16 bit.

• MOV instruction does not affect any flags.

### Example:-

MOV BX, 00F2H; load the immediate number 00F2H in BX register

● MOV [589H], BX;

Copy the 16 bit content of BX register on to the memory location,

which at a displacementof 589H from the data segment base.

MOV DS, CX; Move the content of CX to DS

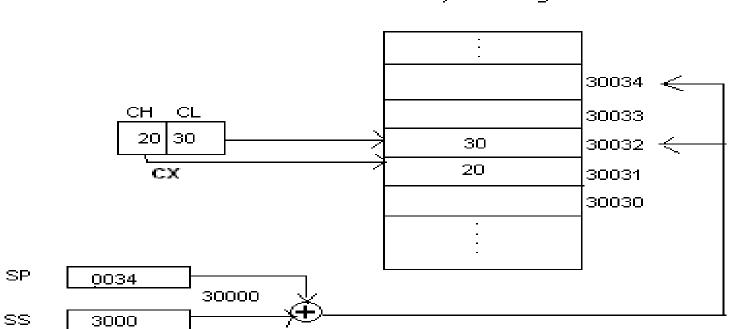

#### PUSH instruction

The PUSH instruction decrements the stack pointer by two and copies the word from source to the location where stack pointer now points. Here the source must of word size data. Source can be a general purpose register, segment register or a memory location.

The PUSH instruction first pushes the most significant byte to sp-1, then the least significant to the sp-2. Push instruction does not affect any flags.

Memory stack segment

#### Example:-

PUSH CX ; Decrements SP by 2, copy content of CX to the stack

#### • POP instruction

- The POP instruction copies a word from the stack location pointed by the stack pointer to the destination. The destination can be a General purpose register, a segment register or a memory location. Here after the content is copied the stack pointer is automatically incremented by two.

- The execution pattern is similar to that of the PUSH instruction. Example: POP CX; Copy a word from the top of the stack to CX and increment SP by 2.

#### • IN & OUT instructions

- The IN instruction will copy data from a port to the accumulator.

If 8 bit is read the data will go to AL and if

AX. Similarly OUT instruction is used to

copy data from accumulator to an output port.

- Both IN and OUT instructions can be done using direct and indirect addressing modes.

Example:

- IN AL, 0F8H;

Copy a byte from the port 0F8H to AL

- MOV DX, 30F8H;Copy port address in DX

- IN AL, DX; Move 8 bit data from 30F8H port

- IN AX, DX; Move 16 bit data from 30F8H port

- OUT 047H, AL; Copy contents of AL to 8 bit port 047H

- MOV DX, 30F8H;Copy port address in DX

### **XCHG** instruction

The XCHG instruction exchanges contents of the destination and source. Here destination and source can be register and register or register and memory location, but XCHG cannot interchange the value of 2 memory locations.

**General Format**

- XCHG Destination, Source

Example:

- XCHG BX, CX; exchange word in CX with the word inBX

- XCHG AL, CL; exchange byte in CL with the byte in AL

- XCHG AX, SUM[BX];here physical address, which isDS+SUM+[BX]. The content at physical address and the content of AX are interchanged.

### Instruction set of 8086 (Arithmetic Instructions in 8086)

| Mnemonic | Meaning                          | Format  | Operation                                   | Flags<br>affected |

|----------|----------------------------------|---------|---------------------------------------------|-------------------|

| ADD      | Addition                         | ADD D,S | (S)+(D) → (D)<br>carry → (CF)               | ALL               |

| ADC      | Add with carry                   | ADC D,S | (S)+(D)+(CF) → (D)<br>carry → (CF)          | ALL               |

| INC      | Incrementby<br>one               | INC D   | (D)+1 → (D)                                 | ALL but CY        |

| AAA      | ASCII adjust for addition        | AAA     | If the sum is >9, AH<br>is incremented by 1 | AF,CF             |

| DAA      | Decimal<br>adjustfor<br>addition | DAA     | Adjust AL for decimal<br>Packed BCD         | ALL               |

| Mnemonic | Meaning                              | Format  | Operation                                                                                 | Flags<br>affected |

|----------|--------------------------------------|---------|-------------------------------------------------------------------------------------------|-------------------|

| SUB      | Subtract                             | SUB D,S | $\begin{array}{ccc} (D) - (S) \rightarrow & (D) \\ Borrow \rightarrow & (CF) \end{array}$ | All               |

| SBB      | Subtract<br>with<br>borrow           | SBB D,S | (D) - (S) - (CF) → (D)                                                                    | All               |

| DEC      | Decrement<br>by one                  | DEC D   | (D) - 1 → (D)                                                                             | All but CF        |

| NEG      | Negate                               | NEG D   |                                                                                           | All               |

| DAS      | Decimal<br>adjust for<br>subtraction | DAS     | Convert the result in ALto<br>packed decimal format                                       | All               |

| AAS      | ASCII<br>adjust for<br>subtraction   | AAS     | (AL) difference<br>(AH) dec by 1 if borrow                                                | CY,AC             |

#### **Multiplication and Division**

| Mnemonic | Meaning                        | Format | Operation                                                                                                                                                                                                        | Flags Affected                      |

|----------|--------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| MUL      | Multiply<br>(unsigned)         | MULS   | $(AL) \cdot (SB) \rightarrow (AX)$<br>$(AX) \cdot (S16) \rightarrow (DX), (AX)$                                                                                                                                  | OF, CF<br>SF, ZF, AF, PF undefined  |

| DIV      | Division<br>(unsigned)         | DIV S  | (1) $Q((AX)/(SB)) \rightarrow (AL)$<br>$R((AX)/(SB)) \rightarrow (AH)$                                                                                                                                           | OF, SF, ZF, AF, PF, CF<br>undefined |

|          | 54 - U                         |        | (2) $Q((DX,AX)/(S16)) \rightarrow (AX)$<br>$R((DX,AX)/(S16)) \rightarrow (DX)$<br>If Q is FF <sub>16</sub> in case (1) or<br>FFFF <sub>16</sub> in case (2), then<br>type 0 interrupt occurs                     |                                     |

| IMUL     | Integer multiply<br>(signed)   | IMUL S | $(AL) \cdot (S8) \rightarrow (AX)$<br>$(AX) \cdot (S16) \rightarrow (DX), (AX)$                                                                                                                                  | OF, CF<br>SF, ZF, AF, PF undefined  |

| IDIV     | Integer divide<br>(signed)     | IDIV S | (1) Q((AX)/(S8)) → (AL)<br>R((AX)/(S8)) → (AH)                                                                                                                                                                   | OF, SF, ZF, AF, PF, CF<br>undefined |

|          |                                |        | (2) Q((DX,AX)/(S16)) → (AX)<br>R((DX,AX)/(S16)) → (DX)<br>If Q is positive and exceeds<br>7FFF <sub>16</sub> or if Q is negative<br>and becomes less than<br>8001 <sub>16</sub> , then type 0 interupt<br>occurs |                                     |

| AAM      | Adjust AL for                  | AAM    | $Q((AL)/10) \rightarrow (AH)$                                                                                                                                                                                    | SF, ZF, PF                          |

|          | multiplication                 |        | $R((AL)/10) \rightarrow (AL)$                                                                                                                                                                                    | OF, AF, CF undefined                |

| AAD      | Adjust AX for<br>division      | AAD    | $\begin{array}{c} (AH) \cdot 10 + (AL) \rightarrow (AL) \\ 00 \rightarrow (AH) \end{array}$                                                                                                                      | SF, ZF, PF<br>OF, AF, CF undefined  |

| CBW      | Convert byte to<br>word        | CBW    | (MSB of AL) $\rightarrow$ (All bits of AH)                                                                                                                                                                       | None                                |

| CWD      | Convert word to<br>double word | CWD    | (MSB of AX) $\rightarrow$ (All bits of DX)                                                                                                                                                                       | None                                |

(a)

(b)

| Multiplication<br>(MUL or IMUL) | Multiplicand | Operand<br>(Multiplier) | Result   |

|---------------------------------|--------------|-------------------------|----------|

| Byte*Byte                       | AL           | Register or memory      | AX       |

| Word*Word                       | AX           | Register or memory      | DX :AX   |

| Dword*Dword                     | EAX          | Register or memory      | EAX :EDX |

| Division<br>(DIV or IDIV) | Dividend | Operand<br>(Divisor) | Quotient: Remainder |

|---------------------------|----------|----------------------|---------------------|

| Word/Byte                 | AX       | Register or Memory   | AL :AH              |

| Dword/Word                | DX:AX    | Register or Memory   | AX : DX             |

| Qword/Dword               | EDX: EAX | Register or Memory   | EAX : EDX           |

# Instruction set of 8086 (Logical Instructions in 8086)

#### **AND instruction**

- This instruction logically ANDs each bit of the source byte/word with the corresponding bit in the destination and stores the result in destination. The source can be an immediate number, register or memory location, register can be a register or memory location.

- The CF and OF flags are both made zero, PF, ZF, SF are affected by the operation and AF is undefined.

- General Format:

- AND Destination, Source

#### Example:

- AND BL, AL ;suppose BL=1000 0110 and AL = 1100 1010 then after the operation BL would be BL= 1000 0010.

- AND CX, AX ;  $CX \leq CX$  AND AX

- AND CL, 08 ;CL<= CL AND (0000 1000)

</p>

#### **OR instruction**

- This instruction logically ORs each bit of the source byte/word with the corresponding bit in the destination and stores the result in destination. The source can be an immediate number, register or memory location, register can be a register or memory location.

- The CF and OF flags are both made zero, PF, ZF, SF are affected by the operation and AF is undefined.

- General Format:

- OR Destination, Source

## EU CHION FOR LIBER

#### Example:

- OR BL, AL; suppose BL=1000 0110 and 1100 1010 then after the AL = BL would be BL= 1100 1110.

Operation

- OR CX, AX;CX <= CX AND AX

- OR CL, 08;CL<= CL AND (0000 1000)

#### NOT instruction

• The NOT instruction complements (inverts) the contents of an operand register or a memory location, bit by bit. The examples are as follows:

Example:

- NOT AX (BEFORE AX= (1011)2= (B) 16 AFTER EXECUTION AX= (0100)2= (4)16).

- NOT [5000H]

#### **XOR instruction**

The XOR operation is again carried out in a similar way to the AND and OR operation. The constraints on the operands are also similar. The XOR operation gives a high output, when the 2 input bits are dissimilar. Otherwise, the output is zero. The example instructions are as follows:

Example:

- XOR AX,0098H

- XOR AX,BX

- XOR AX,[5000H]

#### • Shift / Rotate Instructions

- Shift instructions move the binary data to the left or right by shifting them within the register or memory location. They also can perform multiplication of powers of 2+n and division of powers of 2-n.

- There are two type of shifts logical shifting and arithmetic shifting, later is used with signed numbers while former with unsigned.

#### • SHL/SAL instruction

- Both the instruction shifts each bit to left, and places the MSB in CF and LSB is made 0. The destination can be of byte size or of word size, also it can be a register or a memory location. Number of shifts is indicated by the count.

- All flags are affected.

- General Format:

- SAL/SHL destination, count

Example:

- MOV BL, B7H;

- BL is made B7HSAL BL, 1;

- shift the content of BL register one place to left.

- Before execution,

- CY B7,B6 B5 B4 B3 B2 B1 B0

#### • SHR instruction

- This instruction shifts each bit in the specified destination to the right and 0 is stored in the MSB position. The LSB is shifted into the carry flag. The destination can be of byte size or of word size, also it can be a register or a memory location. Number of shifts is indicated by the count.

- All flags are affected

- General Format: SHR destination, count Example:

- MOV BL, B7H;BL is made B7H

- SHR BL, 1; shift the content of BL register one place to the right.

- Before execution,

- B7 B6 B5 B4 B3 B2 B1 B0 CY

- After execution,

- B7 B6 B5 B4 B3 B2 B1 B0 CY

- ROL instruction

- This instruction rotates all the bits in a specified byte or word to the left some number of bit positions. MSB is placed as a new LSB and a new CF. The destination can be of byte size or of word size, also it can be a register or a memory location. Number of shifts is indicated by the count.

- All flags are affected

- General Format: ROL destination, count

Example:

- MOV BL, B7H;BL is made B7H

- CY B7 B6 B5 B4 B3 B2 B1 B0

- ROL BL, 1;rotates the content of BL register one place to the left.

Before execution,

• CY B7 B6 B5 B4 B3 B2 B1 B0

#### ROR instruction

- This instruction rotates all the bits in a specified byte or word to the right some number of bit positions. LSB is placed as a new MSB and a new CF. The destination can be of byte size or of word size, also it can be a register or a memory location. Number of shifts is indicated by the count.

- General Format: ROR destination,

count Example:

- MOV BL, B7H; BL is made B7H

- ROR BL, 1; shift the content of BL register one place to the right.

- Before execution,

- B7 B6 B5 B4 B3 B2 B1 B0 CY

#### • RCR instruction

- This instruction rotates all the bits in a specified byte or word to the right some number of bit positions along with the carry flag. LSB is placed in a new CF and previous carry is placed in the new MSB. The destination can be of byte size or of word size, also it can be a register or a memory location. Number of shifts is indicated by the count.

- All flags are affected

- General Format: RCR destination, count Example:

- MOV BL, B7H;BL is made B7H

- RCR BL, 1;shift the content of BL register one place to the right.

## instruction set of 8086 (String Instructions)

#### **String Instruction Basics**

Source DS:SI, Destination ES:DI

- You must ensure DS and ES are correct

- You must ensure SI and DI are offsets into DS and ES respectively

- Direction Flag (0 = Up, 1 = Down)

- CLD Increment addresses (left to right)

- STD Decrement addresses (right to

#### **String Control Instructions**

- 1) MOVS/ MOVSB/ MOVSW

- Dest string name, src stringname

- This instruction moves data byte or word from location in DS

- to location in ES.

- 2) REP / REPE / REPZ / REPNE / REPNZ

- Repeat string instructions until specified conditions exist.

- This is prefix a instruction.

#### **String ControlInstructions**

4)SCAS / SCASB / SCASW

Scan a string byte or string word.

Compares byte in AL or word in AX. String address is to be loaded in DI.

#### 5)STOS / STOSB / STOSW

Store byte or word in a string.

Copies a byte or word in AL or AX to memory location pointed by

DI.

#### 6)LODS / LODSB /LODSW

Load a byte or word in AL or AX

Copies byte or word from memory location pointed by SI into AL or AX register.

#### 5. Program Execution TransferInstructions

- instructions are similar to branching or looping instructions. These instructions include unconditional jump or loop instructions.

- > Classification:

- Unconditional transfer instructions

- Conditional transfer instructions

- Iteration control instructions

- Interrupt instructions

#### **Unconditional transferinstructions**

- > CALL: Call a procedure, save return address onstack

- > RET: Return from procedure to the main program.

- >JMP: Goto specified address to get next instruction CALL

- instruction: The CALL instruction is used to transfer

- execution of program to a subprogram or procedure.

#### **CALL** instruction

- Near call

- 1. Direct Near CALL: The destination address is specified in the instruction itself.

- 2. Indirect Near CALL: The destination address is specified in any 16bit register, except IP.

- Far call

- 1. Direct Far CALL: The destination address is specified in the instruction itself. It will be in different Code Segment.

- 2. Indirect Far CALL: The destination address is specified in twoword memory locations pointed by a register.

#### **JMP instruction**

The processor jumps to the specified location rather than the

instruction after the JMP instruction.

- Intra segment jump

- >Inter segment jump

#### RET

RET instruction will return execution from a procedure to The next instruction after the CALL instruction in the calling program.

#### **Conditional Transfer Instructions**

- JA/JNBE: Jump if above / jump if not below or equal

- JAE/JNB: Jump if above /jump if notbelow

- JBE/JNA: Jump if below or equal/ Jump if not above

- JC: jump if carry flag CF=1

- JE/JZ: jump if equal/jump if zero flagZF=1

- JG/JNLE: Jump if greater/ jump if not less than or equal.

#### **Conditional Transfer Instructions**

- JGE/JNL: jump if greater than or equal/ jump if not less than

- JL/JNGE: jump if less than/ jump if not greater than or equal

- JLE/JNG: jump if less than or equal/ jump if not greater than

- JNC: jump if no carry (CF=0).

- JNE/JNZ: jump if not equal/ jump if not zero(ZF=0)

#### **Conditional Transfer Instructions**

- JNO: jump if no overflow(OF=0)

- JNP/JPO: jump if not parity/ jump if parity odd(PF=0)

- JNS: jump if not sign(SF=0)

- JO: jump if overflow flag(OF=1)

- JP/JPE: jump if parity/jump if parityeven(PF=1)

- JS: jump if sign(SF=1).

#### **Iteration Control Instructions**

- These instructions are used to execute a series of instructions for certain number of times.

- LOOP: Loop through a sequence of instructions until CX=0.

- LOOPE/LOOPZ : Loop through a sequence of instructions while

ZF=1 and instructions CX = 0.

- LOOPNE/LOOPNZ : Loop through a sequence of instructions while ZF=0 and CX =0.

- JCXZ : jump to specified

#### **Interrupt Instructions**

Two types of interrupt instructions:

- Hardware Interrupts (External Interrupts)

- Software Interrupts (Internal Interrupts and Instructions)

Hardware Interrupts:

- INTR is a maskable hardware interrupt.

- NMI is a non-maskable interrupt.

#### **Software Interrupts**

- INT : Interrupt program execution, call serviceprocedure

- INTO : Interrupt program execution if OF=1

- IRET: Return from interrupt service procedure to main program.

#### **High Level Language Interface Instructions**

- ≻ENTER : enter procedure.

- ➤ LEAVE: Leave procedure.

➢BOUND: Check if effective address within specified array

bounds.

#### **Processor ControlInstructions**

- I. Flag set/clearinstructions

- STC: Set carry flag CF to 1

- > CLC: Clear carry flag CF to0

- CMC: Complement the state of the carry flagCF

- STD: Set direction flag DF to 1 (decrement stringpointers)

- CLD: Clear direction flag DF to0

- STI: Set interrupt enable flag to 1(enable INTRinput)

- > CLI: Clear interrupt enable Flag to 0 (disable INTRinput)

#### **II. External Hardware synchronizationinstructions**

➤ HLT: Halt (do nothing) until interrupt or reset.

> WAIT: Wait (Do nothing) until signal on the test pin islow.

► ESC: Escape to external coprocessor such as 8087 or 8089.

➢LOCK: An instruction prefix. Prevents another processor from taking the bus while the adjacent instruction executes.

>NOP: No operation. This instruction simply takes up three clock

cycles and does no processing.

### **Assembler Directives**

## Assembler Directives

#### > ASSUME

- > DB -

- > DD

- > DQ

- > DT

- > DW

- Defined Byte.

- Defined Double Word

- Defined Quad Word

- Define Ten Bytes

- Define Word

ASSUME Directive- The ASSUME directive is used to tell the assembler that the name of the logical segment should be used for a specified segment. The 8086 works directly with only 4 physical segments: a Code segment, a data segment, a stack segment, and an extra segment.

#### Example:

**ASUME CS:CODE** ;This tells the assembler that the logical segment named CODE contains the instruction statements for the program and should be treated as a code segment.

**ASSUME DS:DATA** ;This tells the assembler that for any instruction which refers to a data in the data segment, data will found in the logical segment DATA.

- DB DB directive is used to declare a byte- type variable orto store a byte in memory location.

- > Example:

- **1. PRICE DB 49h, 98h, 29h** ;Declare an array of 3 bytes, named as PRICE and initialize.

- 2. NAMEDB'ABCDEF';Declare an array of 6bytes and initialize with ASCII code for letters

- **3. TEMP DB 100 DUP(?)** ;Set 100 bytes of storage in memory and give it the name as TEMP, but leave the 100 bytes uninitialized. Program instructions will load values into these locations.

- DW-The DW directive is used to define a variable of type word or to reserve storage location of type word in memory.

- > Example:

- MULTIPLIER DW 437Ah ; this declares a variable of type word and named it as MULTIPLIER. This variable is initialized with the value 437Ah when it is loaded into memory to run.

- EXP1 DW 1234h, 3456h, 5678h; this declares an array of 3 words and initialized with specified values.

- STOR1 DW 100 DUP(0); Reserve an array of 100 words of memory and initialize all words with 0000.Array is named as STOR1.

- END-END directive is placed after the last statement of a program to tell the assembler that this is the end of the program module. The assembler will ignore any statement after an END directive.

- ENDP-ENDP directive is used along with the name of the procedure to indicate the end of a procedure to the assembler

Example:

- SQUARE\_NUM PROCE ; It start the procedure ;Some steps to find the square root of a number

- SQUARE\_NUM ENDP ;Hear it is the End for the procedure

- > END End Program

- ENDP End Procedure

- ENDS-End SegmentEQUEqu\_ate

- > EVEN

$\succ$

$\succ$

- > EXTRN

- Align on Even Memory Address

ENDS - This ENDS directive is used with name of the segment to indicate the end of that logic segment.

Example: CODE SEGMENT ;Hear it Start the logic segment containing code ;

- CODE ENDS ;End of segment named as CODE

- GLOBAL Can be used in place of a PUBLIC directive or in place of an EXTRN directive.

- GROUP-Used to tell the assembler to group the logical statements named after the directive into one logical group segment, allowing the contents of all the segments to be accessed from the same group segment base.

- INCLUDE Used to tell the assembler to insert a block of source code from the named file into the current source module.

- LABEL- Used to give a name to the current value in the location counter.

- NAME- Used to give a specific name to each assembly module when programs consisting of several modules are written. E.g.: NAME PC\_BOARD

- OFFSET- Used to determine the offset or displacement of a named data item or procedure from the start of the segment which contains it.

- E.g.: MOV BX, OFFSET PRICES

- ORG- The location counter is set to 0000 when the assembler starts reading a segment. The ORG directive allows setting a desired value at any point in the program.

E.g.: ORG 2000H

- PROC- Used to identify the start of a procedure. E.g.: SMART\_DIVIDE PROC FAR

- PTR- Used to assign a specific type to a variable or to a label. E.g.: INCBYTE PTR[BX] tells the

- PUBLIC- Used to tell the assembler that a specified name or label will be accessed from other modules.

- SEGMENT- Used to indicate the start of a logical segment.

E.g.: CODE SEGMENT indicates to the assembler the start of a logical segment called CODE

- SHORT- Used to tell the assembler that only a 1 byte displacement is needed to code a jump instruction. E.g.: JMP SHORT NEARBY\_LABEL

- TYPE Used to tell the assembler to determine the type of a specified variable.

E.g.: ADD BX, TYPE WORD\_ARRAY is used where we want to increment BX to point to the next word in an array of words.

# **Procedures and Macros**

### **Procedures:**

While writing programs, it may be the case that a particular sequence of instructions is used several times. To avoid writing the sequence of instructions again and again in the program, the same sequence can be written as a separate subprogram called a procedure.

### **Defining Procedures:**

Assembler provides PROC and ENDP directives in order to define procedures. The directive PROC indicates beginning of a procedure. Its general form is:

Procedure\_name PROC [NEAR | FAR]

Passing parameters to and from procedures:

The data values or addresses passed between procedures and main program are called parameters. There are four ways of passing parameters:

- > Passing parameters in registers

- Passing parameters in dedicated memory locations

- Passing parameters with pointers passed in registers

- > Passing parameters using the stack

### MACROS:

When the repeated group of instruction is too short or not suitable to be implemented as a procedure, we use a MACRO.

A macro is a group of instructions to which a name is given.

Each time a macro is called in a program, the assembler will replace the macro name with the group of instructions.

### **Defining MACROS:**

- Before using macros, we have to define them. MACRO directive informs the assembler the beginning of a macro. The general form is:

- Macro\_name MACRO argument1, argument2, ...

- Arguments are optional. ENDM informs the assembler the end of

the macro. Its general form is : ENDM

### Differences

| Procedures                                                                              | Macros                                                                               |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Accessed by CALL and RET mechanism during program execution                             | Accessed by name given to macro<br>when<br>defined during assembly                   |

| Machine code for instructions only put<br>in memory once                                | Machine code generated for<br>instructions<br>each time called                       |

| Parameters are passed in registers,<br>memory locations or stackProcedures uses stack   | Parameters passed as part of statementwhich calls macroMacro does not utilize stack  |

| A procedure can be defined anywhere<br>in program using the directives PROC<br>and ENDP | A macro can be defined anywhere in<br>program using the directives MACRO<br>and ENDM |

| Procedures takes huge memory for<br>CALL(3 bytes each time CALL is<br>used) instruction | Length of code is very huge if macro's are called for more number of times           |

# Assembly language programs involving logical, Branch & Call instructions

Write an assembly language program for addition of two 8bit numbers using 8086 microprocessors.

#### DATASEGMENT

A1 DB 50H A2 DB 51H **RES DB**? **DATA ENDS CODE SEGMENT** ASSUME CS: CODE, DS:DATA **MOVAX, DATA** START MOV DS,AX **MOV AL, A1** MOV BL,A2 ADD AL, BL **MOV RES,AL** MOVAX,4C00H **INT 21H CODE ENDS END START**

2000

Write an assembly language program to find the factorial of given number using 8086 microprocessors.

DATA SEGMENT

FIRST DW 03H

SEC DW 01H **DATA ENDS CODE SEGMENT** ASSUME CS:CODE, DS: DATA **MOVAX, DATA** START MOV DS,AX **MOV AX,SEC MOV CX, FIRST** L1: MULCX DEC CX **JCXZ L2** JMP L1 L2: INT 3H **CODE ENDS**

END START

# Write an assembly language program to find the sum of squares using 8086 microprocessors.

DATA SEGMENT

NUM DW 5H

**RES DW ?**

DATA ENDS

**CODE SEGMENT**

ASSUME CS: CODE, DS: DATA

START: MOV AX,DATA MOV DS,AX

MOV CX,NUM

MOV BX,00

L1: MOV AX,CX

MULCX

ADD BX,AX

DEC CX

JNZ L1

**MOV RES, BX**

INT 3H

CODE ENDS END START 2000

### Programs using logical ,Branch and call instructions.

Data segment

| Org 2000h   | Mov [di],ax |

|-------------|-------------|

| N1 dw 5678h | Int 03h     |

| N2 dw 2345h | Code ends   |

| Data ends   | End         |

|             |             |

**Code segment**

Assume cs:code,ds:dats

Mov ax,data

Mov ds,ax

Mov DI,2040h

Mov ax,N1

AND ax,bx

- Org 2000h

- N1 dw 5678h

- N2 dw 2345h

- Data ends

- Code segment

- Assume cs:code,ds:dats

- Mov ax,data

- Mov ds,ax

- Mov DI,2040h

- Mov ax,N1

- MOV bx,N2

- OR ax,bx

- Mov [di],ax

- Int 03h

- Code ends

- End

# Assembly language

#### 3)Data segment

- Org 2000h

- N1 dw 5678h

- N2 dw 2345h

- Data ends

- Code segment

- Assume cs:code,ds:dats

- Mov ax,data

- Mov ds,ax

- Mov DI,2040h

- Mov ax,N1

- MOV bx,N2

- o xor ax,bx

- Mov [di],ax

- Int 03h

- Code ends

- End

2000

- Org 2000h

- N1 dw 5678h

- Data ends

- Code segment

- Assume cs:code,ds:dats

- Mov ax,data

- Mov ds,ax

- Mov DI,2040h

- Mov ax,N1

- SHL ax,04

- Mov [di],ax

- Int 03h

- Code ends

- End

### **Programs using logical ,Branch and call instructions.**

- Org 2000h

- N1 dw 5678h

- Data ends

- Code segment

- Assume cs:code,ds:dats

- Mov ax,data

- Mov ds,ax

- Mov DI,2040h

- Mov ax,N1

- SHR ax,04

- . Mov [di],ax

- . Int 03h

- . Code ends

- . End

- Org 2000h

- N1 dw 5678h

- Data ends

- Code segment

- Assume cs:code,ds:dats

- Mov ax,data

- Mov ds,ax

- Mov DI,2040h

- Mov ax,N1

- ROR ax,02

- Mov [di],ax

- Int 03h

- Code ends

- End

# Assembly language

#### 3)Data segment

- Org 2000h

- N1 dw 5678h

- Data ends

- Code segment

- Assume cs:code,ds:dats

- Mov ax,data

- Mov ds,ax

- Mov DI,2040h

- Mov ax,N1

- RCR ax,03

- Mov [di],ax

- Int 03h

- Code ends

- End

2000

- Org 2000h

- N1 dw 5678h

- Data ends

- Code segment

- Assume cs:code,ds:dats

- Mov ax,data

- Mov ds,ax

- Mov DI,2040h

- Mov ax,N1

- RCL ax,04

- Mov [di],ax

- Int 03h

- Code ends

- End

# Sorting

Assembly language program to sort the given numbers in Ascending order

- ASSUME CS: CODE CODE SEGMENT

- START: MOV AX,0000H

- MOV CH, 0004H DEC CH

- UP1: MOV CL, CH MOV SI, 2000H

- UP: MOV AL, [SI] INC SI CMP AL, [SI]

**JC DOWN** XCHG AL, [SI] DEC SI MOV [SI], AL **INC SI DOWN: DEC CL JNZUP DEC CH JNZ UP1** INT 3 **CODE ENDS**

**END START**

Assembly language program to sort the given numbers in Descending order

| ASSUME CS: CODE |            |        |       |

|-----------------|------------|--------|-------|

| CODE SEGMENT    |            |        |       |

| START:          | MOV        | AX,    | 0000H |

|                 | MOV        | CH,    | 0004H |

|                 | DEC C      | Η      |       |

| UP1:            | MOV CL, CH |        |       |

|                 | MOV        | SI, 20 | 00H   |

| UP:             | MOV        | AL, [S | 51]   |

|                 | INC SI     |        |       |

|                 |            |        |       |

CMP AL, [SI]

### **JNC DOWN** XCHG AL, [SI] **DEC SI** MOV [SI], AL **INC SI DEC CL DOWN**: **JNZ UP DEC CH JNZUP1 I NT 3 CODE ENDS END START**

## **Evaluation of arithmetic expressions**

An Assembly program for performing the following operation Z= ((A-B)/10\*C)

DATA SEGMENT **A DB 60 B DB 20** C DB 5 Z DW? **ENDS** CODE SEGMENT **ASSUME DS: DATA CS: CODE START:** MOV AX, DATA MOV DS, AX MOV AH, 0 ; Clear content of AX MOV AL, A ; Move A to register AL

| SUB AL, B   | ; Subtract AL and B       |

|-------------|---------------------------|

| MUL C       | ; Multiply C to AL        |

| MOV BL, 10  | ; Move 10 to register BL  |

| DIV BL      | ; Divide AL content by BL |

| MOV Z, AX   | ; Move content of AX to Z |

| MOV AH, 4CH |                           |

| INT 21H     |                           |

|             |                           |

ENDS END START

## **Evaluation of arithmetic expressions**

An Assembly program for performing the following operation Z= ((A-B)/10\*C)

DATA SEGMENT **A DB 60 B DB 20** C DB 5 Z DW? **ENDS** CODE SEGMENT **ASSUME DS: DATA CS: CODE START:** MOV AX, DATA MOV DS, AX MOV AH, 0 ; Clear content of AX MOV AL, A ; Move A to register AL

| SUB AL, B   | ; Subtract AL and B       |

|-------------|---------------------------|

| MUL C       | ; Multiply C to AL        |

| MOV BL, 10  | ; Move 10 to register BL  |

| DIV BL      | ; Divide AL content by BL |

| MOV Z, AX   | ; Move content of AX to Z |

| MOV AH, 4CH |                           |

| INT 21H     |                           |

|             |                           |

ENDS END START

### **String manipulation**

**Program For String Transfer**

; start of data segment **DATA SEGMENT** STR1 DB 'HOW ARE YOU' LEN EQU \$-STR1 **STR2 DB 20 DUP (0)** ; end of data segment **DATA ENDS** ; start of code segment **CODE SEGMENT** ASSUME CS: CODE, DS: DATA, ES: DATA MOV AX, DATA; initialize data segment START: **MOV DS, AX**

| MOV ES, AX                           | ; initialize extra segment for string operations                                 |

|--------------------------------------|----------------------------------------------------------------------------------|

| LEA SI, STR1                         | ; SI points to starting address of string at ; STR1                              |

| LEA DI, STR2                         | ; DI points to starting address of where the string<br>has to be transferred     |

| MOV CX, LEN                          | ; load CX with length of the string                                              |

| CLD                                  | ; clear the direction flag for auto increment SI;                                |

| and                                  | DI                                                                               |

| REP MOVSB<br>address<br>decremented) | ; the source string is moved to destination<br>till CX=0(after every move CX is; |

| MOV AH, 4CH<br>INT 21H               | ; terminate the process                                                          |

| CODE ENDS                            | ; end of code segment                                                            |

| END START                            |                                                                                  |

|                                      |                                                                                  |

#### **Program To Reverse A String**

DATA SEGMENT

STR1 DB 'HELLO'

LEN EQU \$-STR1

STR2 DB 20 DUP (0)

**DATA ENDS**

; end of data segment

; start of data segment

**CODE SEGMENT**

; start of code segment

ASSUME CS: CODE, DS: DATA, ES: DATA

START: MOV AX, DATA ; initialize data segment MOV DS, AX

MOV ES, AX

|           | LEA SI, STR1       |

|-----------|--------------------|

|           | LEA DI, STR2+LEN-1 |

|           | MOV CX, LEN        |

| UP:       | CLD                |

|           | LODSB              |

|           | STD                |

|           | STOSB              |

|           | LOOPUP             |

|           | MOV AH, 4CH        |

|           | INT 21H            |

| CODE ENDS |                    |

| END START |                    |

## MODULE-II Operation of 8086 and Interrupts.

| CO4 | Distinguish between minimum mode and maximum mode operation of 8086 microprocessor with timing diagrams.                                               |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CO5 | Interpret the functionality of various types of interrupts and their structure for controlling the processor or controller and program execution flow. |  |

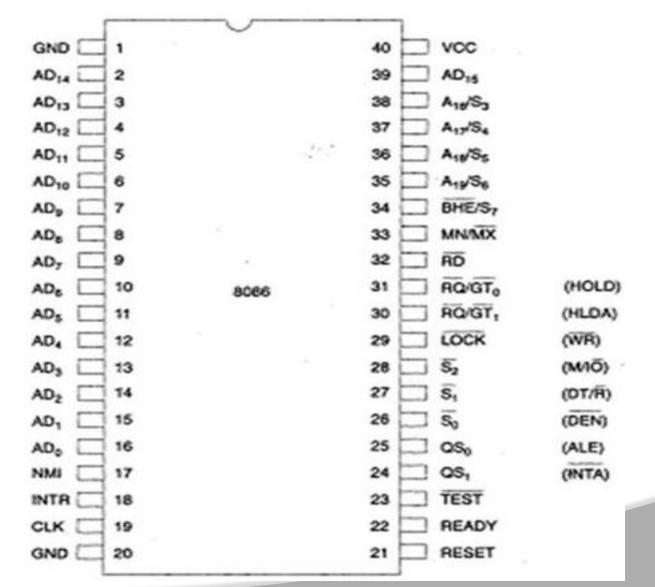

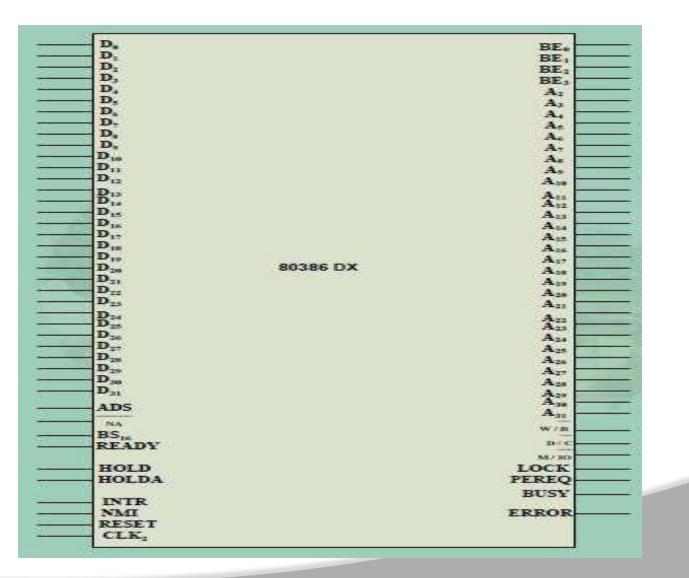

## Pin diagram of 8086

#### **PIN DIAGRAM OF 8086**

153

8086 operates in single processor or multiprocessor configuration to achieve high performance.

8086 is available in three clock rates 5,8,10 MHZ.

8086 signals can be categorised in to three groups

- i) Signals having common functions in minimum as well as maximum mode.

- ii) Signals having special functions for minimum mode.

- iii) Signals having special functions for maximum mode.

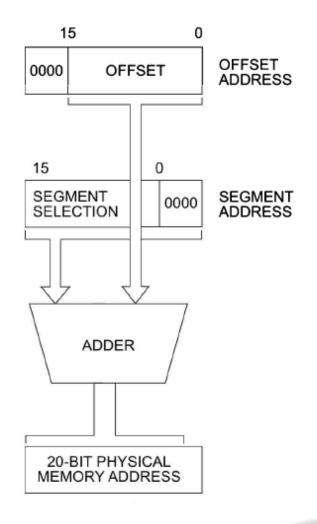

#### <u>AD15-AD0</u>: (Address/Data lines)

These are time multiplexed address and data lines, which carry address when ALE is high and later function as data lines when ALE is low

Address is available on the address lines during T1 state.

Data is available on the data bus during T2,T3,TW,T4 clock states of machine cycles.

TW is wait state of machine cycle.

These lines are active high and float to a tri state during interrupt acknowledge and local bus hold acknowledge cycles.

#### A19/S6,A18/S5,A17/S4,A16/S3: (Address/Status lines)

- These are time multiplexed address and status lines.

- During T1 these are the most significant address lines for memory operations .

- During memory or I/O operations status information is available on these lines for T2,T3,TW and T4.

- The status of the interrupt enable flag bit is updated at the beginning of each clock cycle.

- S4 and S3 indicates which segment register is presently being used for memory access.

| S4 | S3 | indicates                |

|----|----|--------------------------|

| 0  | 0  | Extra Segment(ES)        |

| 0  | 1  | Stack Segment (SS)       |

| 1  | 0  | Code Segment or none(CS) |

| 1  | 1  | Data Segment (DS)        |

These lines float to tri-stat during the local bus hold acknowledge.

S6 is always 0.

S5 is the condition of the interrupt flag.

Address bits are separated from the status bits using latches controlled by ALE signal.

- **<u>BHE'/S7</u>**: Bus high enable signal is used to indicate the transfer of data over higher order (D15 D8) data bus.

- BHE' is low for data transfer over(D15-D8).

- BHE' is low during T1 for read, write and interrupt acknowledge cycles whenever a byte is to be transferred on the higher byte of data bus. The status information is available during T2,T3, and T4.

- The signal is active low and tristated during hold.

- The status of this pin is latched along with the address information. S7 is always 1.

| BHE | $A_0$ | Indication                         |

|-----|-------|------------------------------------|

| 0   | 0     | Whole word (2 bytes)               |

| 0   | 1     | Upper byte from or to odd address. |

| 1   | 0     | Lower byte from or to even address |

| 1   | 1     | None                               |

#### RD': (Read)

When this signal is low data can be received from memory or input devices.

RD' is active low during T2,T3 and Tw of any read cycle.

RD' remains tristated during the hold acknowledgement.

#### Ready:

This is the acknowledgement from the slow device or memory that they have completed the data transfer.

The signal is active high.

If it is at logic low, wait states are inserted into the current bus cycle.

#### **<u>INTR</u>- (Interrupt Request)**

This is a triggered input.

- This is sampled during the last clock cycles of each instruction to determine the availability of the request.

- If any interrupt request is pending, the processor enters the interrupt acknowledge cycle.

- This signal is active high and internally synchronized.

#### <u> TEST':</u>

- This input is examined by a 'WAIT' instruction.

- If the TEST' pin goes low, execution will continue, else the processor remains in an idle state.

- The input is synchronized internally during each clock cycle on leading edge of clock.

#### NMI(Non Maskable Interrupt):

This is an edge triggered input which causes a type-2 interrupt.

A transition from low to high initiates the interrupt response at the end of the current instruction.

This input is internally synchronized.

#### **RESET:**

The input causes the processor to terminate current activity and start execution .

The signal is active high and must be active for atleast four clock cycles.

It restarts execution when the reset returns low.

Reset is also internally synchronized.

#### <u>CLK:</u>

The clock input provides the basic timing for processor operation and bus control activity.

The range of frequency for different 8086 versions is from 5MHZ to 10MHZ.

#### <u>Vcc:</u>

+5V power supply for the operation of internal circuit.

#### <u>GND:</u>

Ground for the internal circuit.

# EUCFITON FOR LIBER

#### INTA' (Interrupt Acknowledge):

In response to INTR, the processor sends acknowledge signal that the interrupt is accepted through INTA pin.

#### M/IO': (Memory/input output)

When M/IO'=1 it performs the memory read/write operations. When M/IO'=0 it performs the I/O read/write operations.

#### <u>WR': (Write)</u>

It is active low pin.

It indicates microprocessor is sending data to memory or I/O devices.

#### DT/R': (Data transmit/Receive)

It indicates transmitting or receiving data over system bus.

If DT/R'=1 data transmit; If DT/R'=0 data receive.

It is used to enable external data buffer.

#### DEN': (Data enable)

It is used to enable external data bus buffer.

When DEN'=0 data transferred on data bus.

#### ALE: (Address Latch Enable)

When ALE=1 multiplexed line carries address only. When ALE=0 multiplexed line carries data.

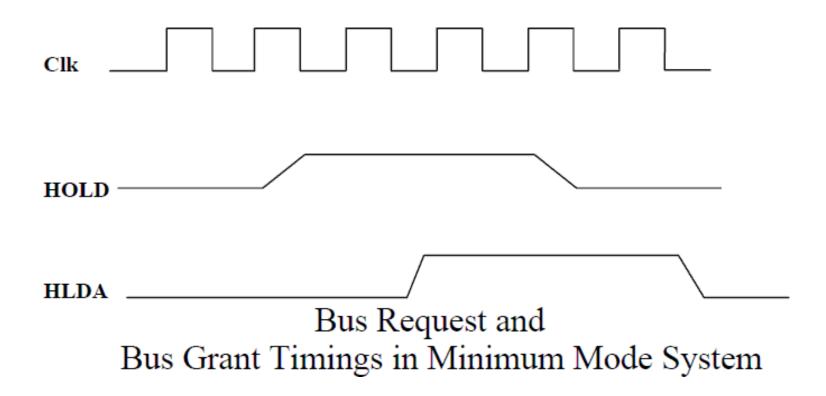

#### HOLD:

When HOLD line is high it indicates processor that another master is requesting bus access.

#### HLDA: (Hold Acknowledgement)

After receiving HOLD request, the processor issues the acknowledge on HLDA pin.

# EU LARE

#### MN/MX':

If MN/MX'=0 it indicates maximum mode of operation.

If MN/MX'=1 it indicates minimum mode of operation.

#### S2',S1',S0': (Status Lines)

It indicates the type of operation carried out by processor.

| $\overline{s}_{2}$ | $\overline{s}_{1}$ | $\overline{s}_{o}$ | Indication            |

|--------------------|--------------------|--------------------|-----------------------|

| 0                  | 0                  | 0                  | Interrupt acknowledge |

| 0                  | 0                  | 1                  | Read I/O port         |

| 0                  | 1                  | 0                  | Write I/O port        |

| 0                  | 1                  | 1                  | Halt                  |

| 1                  | 0                  | 0                  | Code access           |

| 1                  | 0                  | 1                  | Read memory           |

| 1                  | 1                  | 0                  | Write memory          |

| 1                  | 1                  | 1                  | Passive               |

#### RQ1'/GT1'; RQ0'/GT0: (Request/Grant)

If the other processor wants to access the system bus, then it is going to request the processor which is currently using system bus through this pin.

These are bidirectional pins.

It will send the acknowledge through same pins.i.e; grant.

#### **LOCK'**:

When this signal is enabled the system bus is locked for certain duration. So it cannot be used by other masters for some duration.

#### QS1,QS0:(Queue status):

.

| $QS_I$ | $QS_{\theta}$ | Indication                          |

|--------|---------------|-------------------------------------|

| 0      | 0             | No operation                        |

| 0      | 1             | First byte of opcode from the queue |

| 1      | 0             | Empty queue                         |

| 1      | 1             | Subsequent byte from the queue      |

# Minimum mode and maximum mode of operation with Timing diagrams

# Minimum mode operation in 8086

#### Minimum mode operation in 8086:

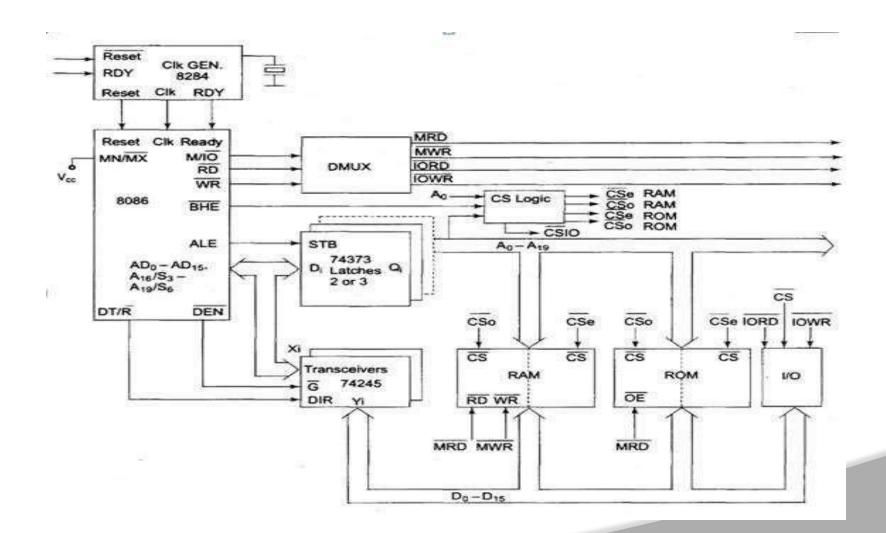

In a minimum mode 8086 system, the microprocessor 8086 is operated

in minimum mode by strapping its MN/MX pin to logic 1.

- In this mode, all the control signals are given out by the microprocessor chip itself. There is a single microprocessor in the minimum mode system.

- The remaining components in the system are latches, transceivers, clock generator, memory and I/O devices. Some type of chip selection logic may be required for selecting memory or I/O devices, depending upon the address map of the system.

- Latches are generally buffered output D-type flip-flops like 74LS373 or 8282. They are used for separating the valid address from the multiplexed address/data signals and are controlled by the ALE signal generated by 8086.

- Transceivers are the bidirectional buffers and sometimes they are called as data amplifiers. They are required to separate the valid data from the time multiplexed address/data signals.

- > They are controlled by two signals namely, DEN and DT/R.

- The DEN signal indicates the direction of data, i.e. from or to the processor. The system contains memory for the monitor and users program storage.

- Usually, EPROM is used for monitor storage, while RAM for users program storage. A system may contain I/O devices.

# Maximum mode operation in 8086

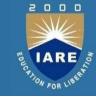

- In the maximum mode, the 8086 is operated by strapping the MN/MX pin to ground.

- In this mode, the processor derives the status signal S2, S1,

S0. Another chip called bus controller derives the control signal using this status information.

- In the maximum mode, there may be more than one microprocessor in the system configuration.

- The components in the system are same as in the minimum mode system.

- The basic function of the bus controller chip IC8288 is to derive control signals like RD and WR (for memory and I/O devices), DEN, DT/R, ALE etc. using the information by the processor on the status lines.

- The bus controller chip hasinput lines S2, S1, S0 and CLK. These inputs to 8288 are driven by CPU.

#### Maximum mode

- It derives the outputs ALE, DEN, DT/R, MRDC, MWTC, AMWC, IORC, IOWC and AIOWC. The AEN, IOB and CEN pins are especially useful for multiprocessor systems.

- AEN and IOB are generally grounded. CEN pin is usually tied to +5V. The significance of the MCE/PDEN output depends upon the status of the IOB pin.

- If IOB is grounded, it acts as master cascade enable to control cascade 8259A, else it acts as peripheral data enable used in the multiple bus configurations.

- INTA pin used to issue two interrupt acknowledge pulses to the interrupt controller or to an interrupting device.

- IORC, IOWC are I/O read command and I/O write command signals respectively.

- These signals enable an IO interface to read or write the data from or to the address port.

- The MRDC, MWTC are memory read command and memory write command signals respectively and may be used as memory read or write signals.

- The MRDC, MWTC are memory read command and memory write command signals respectively and may be used as memory read or write signals.

- All these command signals instructs the memory to accept or send data from or to the bus.

- For both of these write command signals, the advanced signals namely AIOWC and AMWTC are available.

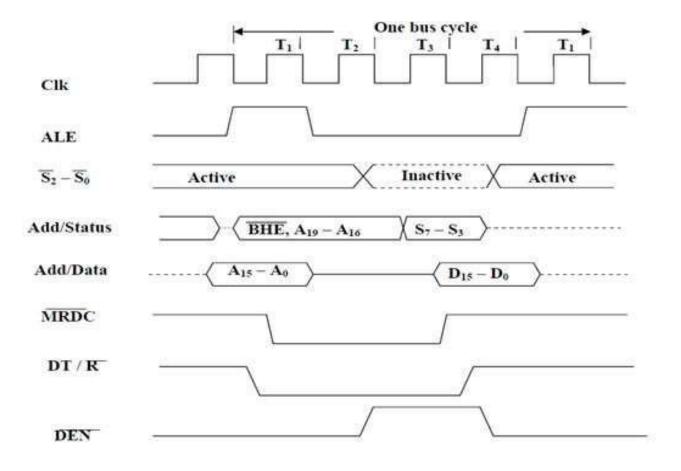

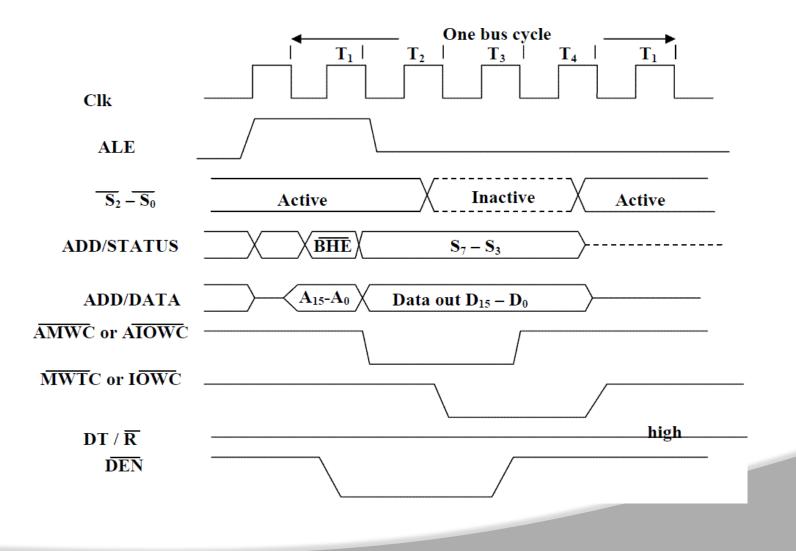

- Here the only difference between in timing diagram between minimum mode and maximum mode is the status signals used and the available control and advanced command signals.

- ➢RO, S1, S2 are set at the beginning of bus cycle.8288 bus controller will output a pulse as on the ALE and apply a required signal to its DT / R pin during T1.

- ➢In T2, 8288 will set DEN=1 thus enabling transceivers, and for an input it will activate MRDC or IORC. These signals are activated until T4. For an output, the AMWC or AIOWC is activated from T2 to T4 and MWTC or IOWC is activated from T3 to T4.

# Timing diagram for minimum mode

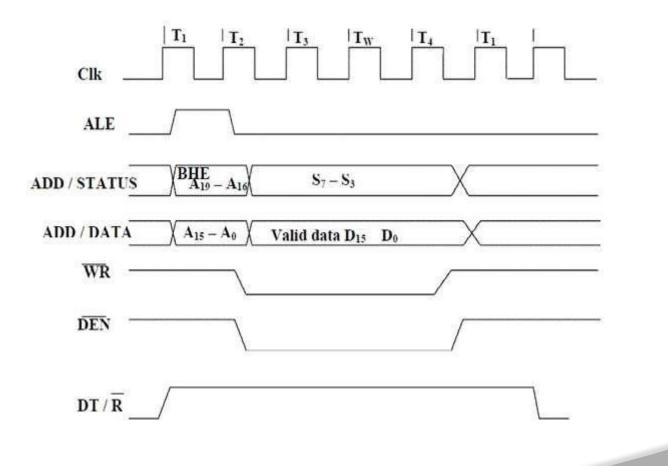

### Write Cycle Timing Diagram for

- The working of the minimum mode configuration system can be better described in terms of the timing diagrams rather than qualitatively describing the operations.

- The opcode fetch and read cycles are similar. Hence the timing diagram can be categorized in two parts, the first is the timing diagram for read cycle and the second is the timing diagram for write cycle.

Bus Request and Bus Grant Timings in Minimum Mode System of 8086

# Timing diagram for maximum mode

## Memory Read Timing Diagram in Maximum Mode of 8086

### Memory Write Timing in Maximum mode of 8086

2 0 0 0

IARE

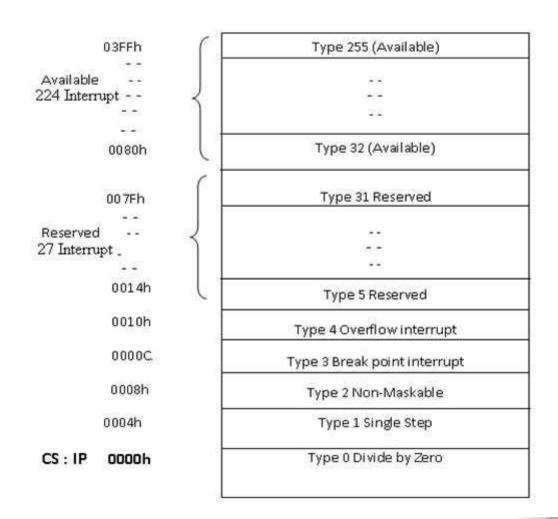

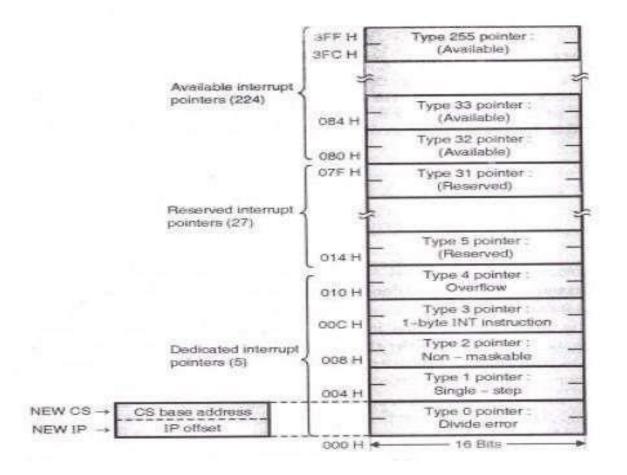

# **Interrupt structure of 8086**

#### **Interrupt structure of 8086**

# Vector interrupt table, interrupt service routines

# Introduction to DOS and BIOS interrupts

### **BIOS INTERRUPT**

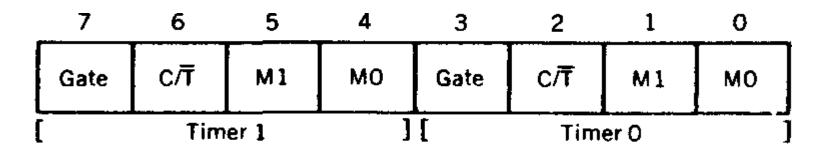

#### **BIOS INTERRUPT**