## PPTS ON ANALOG AND DIGITAL ELECTRONICS (IT)

II B.Tech III semester

**Course code: AECBO5**

Ms. M.Saritha, Assistant Professor Ms. C. Devi Supraja, Assistant Professor

**Institute of Aeronautical Engineering**

# TARE SOLVER AND A POR LIBERT A

### **SYLLABUS**

**Module-1:DIODE AND APPLICATIONS**

**Module-2:BIPOLAR JUNCTION TRANSISTOR (BJT)**

**Module-3:NUMBER SYSTEMS**

**Module-4: MINIMIZATION OF BOOLEAN FUNCTIONS**

**Module-5:SEQUENTIAL CIRCUITS FUNDAMENTALS**

#### **MODULE-I**

#### **DIODE AND APPLICATIONS**

Diode - Static and Dynamic resistances, Equivalent circuit, Load line analysis, Diffusion and Transition Capacitances, Diode Applications: Switch-Switching times. Rectifier - Half Wave Rectifier, Full Wave Rectifier, Bridge Rectifier, Rectifiers with Capacitive Filter

### **CONTENTS**

- ➤ Introduces the PN junction diodes.

- ➤ Analysis of diode characteristics.

- > Equivalent circuits and load line.

- > Diode behaviour as a switch.

- ➤ Diodes in rectifiers.

- ➤ Breakdown mechanisms- Avalanche, Zener.

- >. Rectifiers with Capacitive Filter

#### **MATERIALS**

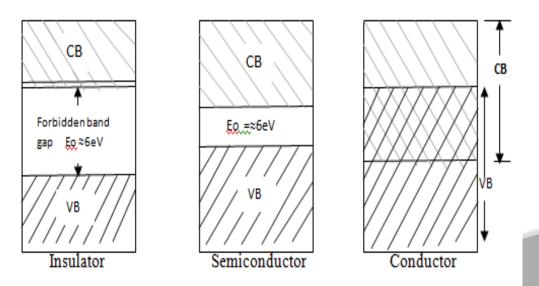

Based on the electrical properties of the materials like conductivity, materials are divided into three types.

- i) Conductors

- ii) Semiconductors

- iii) Insulators

Energy band diagrams for insulator, semiconductor and conductor

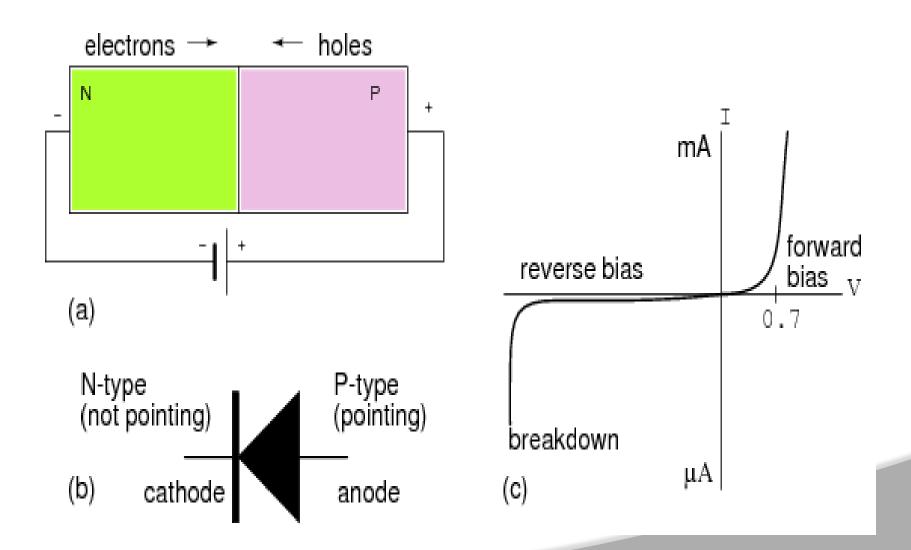

### PN JUNCTION DIODE

### What do you mean by diode?

A PN junctionis a device formed by joining p-type with n-type semiconductors and separated by a thin junction is called PN Junction

### PN JUNCTION DIODE

### THEORY OF PN JUNCTION DIODE

- ➤ The depletion layer contains no free and mobile charge carriers but only

- fixed and immobile ions.

- > Its width depends upon the doping level...

- > Heavily doped......thin depletion layer

- ➤ lightly doped......thick depletion layer

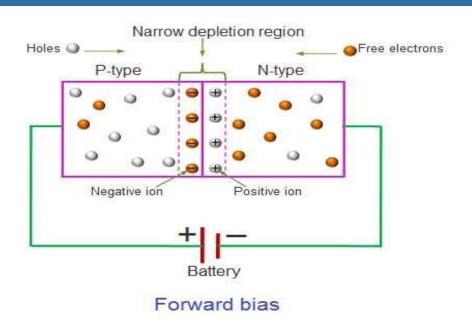

<u>Forward bias mode</u>: positive terminal connected to pregion and negative terminal connected to n region.

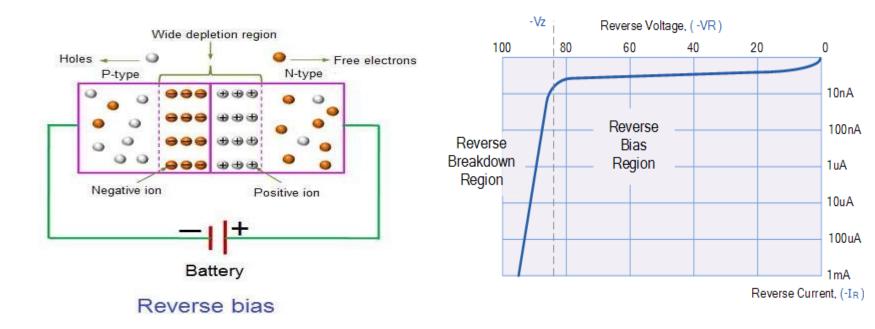

**Reverse bias mode:** negative terminal connected to pregion and positive terminal connected to n region

### PN JUNCTION -FORWARD BIAS

It forces the majority charge carriers to move across the junction decreasing the width of the depletion layer.

### PN JUNCTION –REVERSE BIAS

The free electrons and free holes are depletion layer width increases.

attracted towards the battery, hence

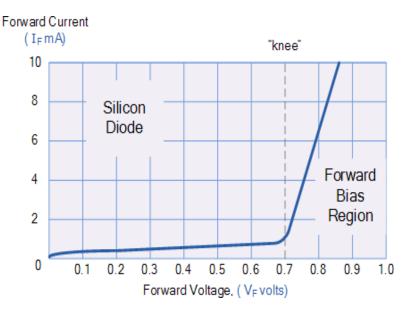

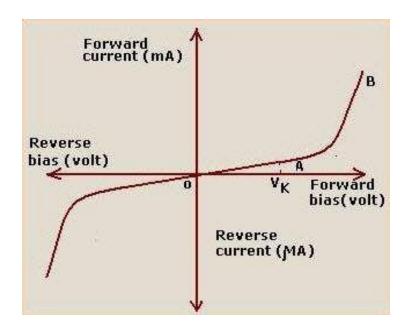

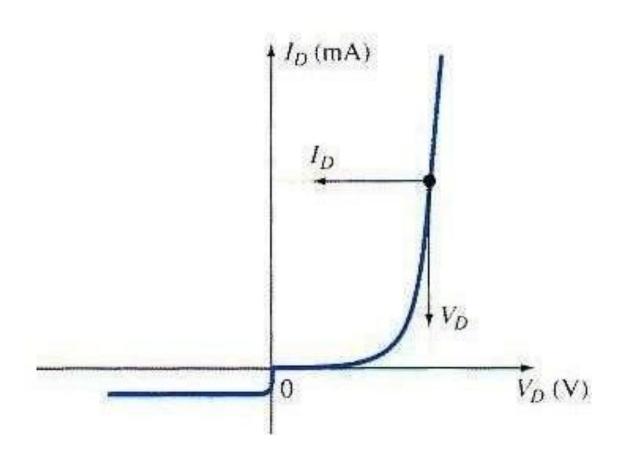

### V-I CHARACTERISTICS OF PN JUNCTION DIODE

V-I characteristics of PN junction diode

### STATIC OR DC RESISTANCE

- > The resistance of a diode at a particular operating point is called the dc or static resistance diode.

- > The resistance of the diode at the operating point can be found simply by finding the corresponding levels of  $V_D$  and  $I_D$ .

- It can be determined using equation

$$R_D = V_D/I_D$$

The lower current through a diode the higher the dc resistance level

### **STATIC OR DC RESISTANCE**

Fig: Static resistance curve

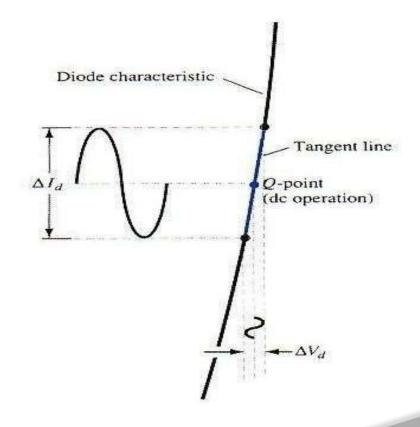

### **DYNAMIC OR AC RESISTANCE**

- Static resistance is using dc input.

If the input is sinusoidal the scenario will change.

- The ac resistance is determined by straight line drawn between the two intersections of the maximum and minimum values of input voltage.

Fig: Dynamic resistance curve

### PN JUNCTION DIODE CHARACTERISTICS

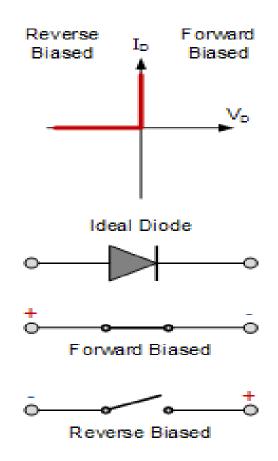

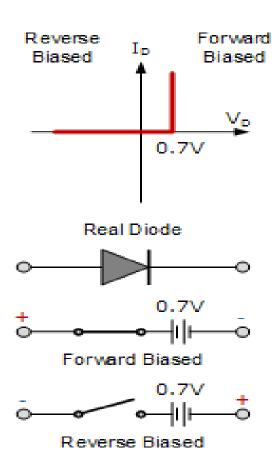

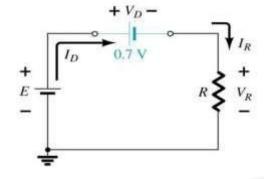

### **DIODE EQUIVALENT CIRCUIT**

When a diode is F.B, we can use the approximate model for the on state

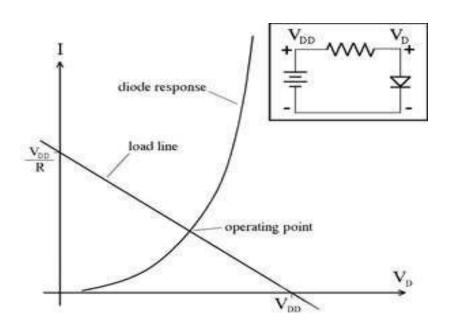

### PN DIODE- LOAD LINE ANALYSIS

A load line is a line drawn on the characteristic curve, a graph of the current vs. voltage in a nonlinear device like a diode.

The curve shows the diode response (I vs  $V_D$ ) while the straight line shows

the behavior of the linear part of the circuit:

$$I=(V_{DD}-V_{D})/R$$

.

The point of intersection gives the actual current and voltage.

### **JUNCTION CAPACITANCE**

In a <u>p-n junction diode</u>, two types of capacitance take place. They are,

- Transition capacitance (C<sub>T</sub>)

- Diffusion capacitance (C<sub>D</sub>)

Transition Capacitance C<sub>T</sub>

The amount of capacitance changed with increase in voltage is called transition capacitance. The transition capacitance is also known as depletion region capacitance, junction capacitance or barrier capacitance.

### TRANSITION CAPACITANCE C<sub>T</sub>

The change of capacitance at the depletion region can be defined as the

change in electric charge per change in voltage.

$$C_T = dQ / dV$$

Where,

C<sub>T</sub>= Transition capacitance

dQ = Change in electric charge

dV = Change in voltage

### DIFFUSION CAPACITANCE (C<sub>D</sub>)

Diffusion capacitance occurs in a forward biased p-n junction diode. Diffusion capacitance is also sometimes referred as storage capacitance. It is denoted as  $C_D$ .

The formula for diffusion capacitance is

$$C_D = dQ / dV$$

### **DIODE APPLICATIONS**

### common applications of diodes are

- **≻**Switches

- **≻** Rectifiers

- **≻**Clipper Circuits

- **≻**Clamping Circuits

- ➤ Reverse Current Protection Circuits

- ➤In Logic Gates

- ➤ Voltage Multipliers

### RECTIFIER

- A circuit that converts ac voltage of main supply into pulsating dc voltage using one or more PN junction diodes is called rectifier.

- ➤ Half Wave Rectifier

- > Full Wave Rectifier

- Bridge Rectifier

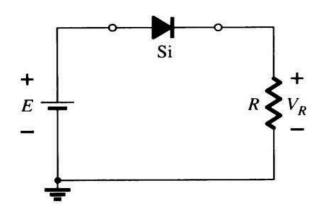

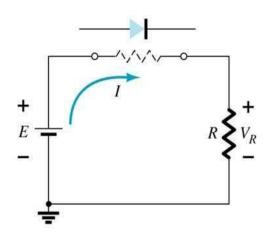

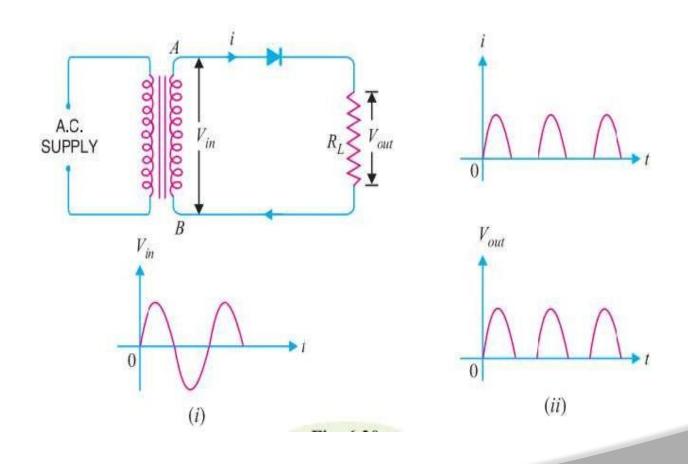

### Half Wave Rectifier

- The process of removing one-half the input signal to establish a dc level is called half-wave rectification.

- ➤In Half wave rectification, the rectifier conducts current during positive

- half cycle of input ac signal only.

- ➤ Negative half cycle is suppressed.

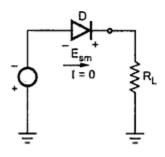

### **Half Wave Rectifier**

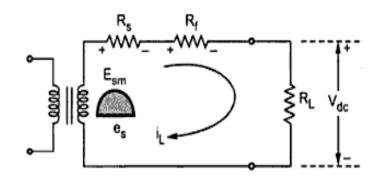

#### Average DC load Current (I<sub>DC</sub>):

Mathematically, current waveform can be described as,

$$i_L = I_m \sin \omega t$$

$$i_L = 0$$

for

$$0 \le \omega t \le \pi$$

for

$$\pi \le \omega t \le 2\pi$$

Im = peak value of load current

$$I_{DC} = \frac{1}{2\pi} \int_{0}^{2\pi} i_{L} d(\omega t) = \frac{1}{2\pi} \int_{0}^{2\pi} I_{m} \sin(\omega t) d(\omega t)$$

$$I_{DC} = \frac{I_m}{\pi} = average value$$

$$I_m = \frac{E_{sm}}{R_f + R_L + R_s}$$

(a) Equivalent circuit

where  $R_s$  = resistance of secondary winding of transformer. If  $R_s$  is not given it should be neglected while calculating  $I_m$ .

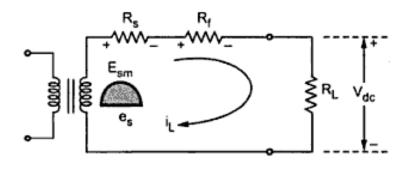

### Average DC voltage (Edc):

$$E_{DC} = I_{DC}R_{L}$$

$$E_{DC} = \frac{I_{m}}{\pi}R_{L}$$

$$= \frac{E_{sm}}{(R_{f} + R_{L} + R_{s})\pi}R_{L}$$

(a) Equivalent circuit

But as  $R_f$  and  $R_s$  are small compared to  $R_L$ ,  $(R_f + R_s)/R_L$  is negligibly small compared to 1. So neglecting it we get,

$$E_{DC} \approx \frac{E_{sm}}{\pi}$$

### RMS Load Current (Irms):

$$I_{RMS} = \sqrt{\frac{1}{2\pi}} \int_{0}^{\pi} (I_{m} \sin \omega t)^{2} d(\omega t)$$

$$I_{RMS} = \frac{I_m}{2}$$

### RMS Load Voltage (Erms):

$$E_{L (RMS)} \approx \frac{E_{sm}}{2}$$

### Peak Inverse Voltage (PIV):

$$PIV = Em$$

Diode must be selected based on the PIV rating the circuit specification.

and

#### DC Power Delivered to the load:

$$P_{DC} = E_{DC} I_{DC} = I_{DC}^2 R_L$$

D.C. Power output =

$$I_{DC}^2 R_L = \left[\frac{I_m}{\pi}\right]^2 R_L = \frac{I_m^2}{\pi^2} R_L$$

$P_{DC} = \frac{I_m^2}{\pi^2} R_L$

### AC input power from transformer secondary:

The power input taken from the secondary of transformer is the power supplied to three resistances namely load resistance  $R_L$ , the diode resistance  $R_f$  and winding resistance  $R_s$ . The a.c. power is given by,

$$P_{AC} = I_{RMS}^{2}[R_{L} + R_{f} + R_{s}]$$

$$I_{RMS} = \frac{I_{m}}{2} \qquad \text{for half wave,}$$

$$P_{AC} = \frac{I_{m}^{2}}{4}[R_{L} + R_{f} + R_{s}]$$

### **Rectifier Efficiency(n):**

$$\eta = \frac{D.C. \text{ output power}}{A.C. \text{ input power}} = \frac{P_{DC}}{P_{AC}}$$

$$\eta = \frac{\frac{l_m^2}{\pi^2} R_L}{\frac{l_m^2}{4} [R_f + R_L + R_s]} = \frac{(4/\pi^2) R_L}{(R_f + R_L + R_s)}$$

;  $\eta = 40.6\%$

Under pest conditions (no diode loss) only 40.0% of the ac input power is converted into dc power.

The rest remains as the ac power in the load

#### Ripple Factor:

Ripple factor

$$\gamma = \frac{R.M.S. \text{ value of a. c. component of output}}{\text{Average or d. c. component of output}}$$

(or)

Ripple factor =

$$\frac{I_{ac}}{I_{DC}}$$

$$\gamma = \sqrt{\left(\frac{I_{RMS}}{I_{DC}}\right)^2 - 1}$$

$$\gamma = \sqrt{\left[\frac{\left(\frac{l_m}{2}\right)}{\left(\frac{l_m}{\pi}\right)}\right]^2 - 1} = \sqrt{\frac{\pi^2}{4} - 1} = \sqrt{1.4674} \qquad \Rightarrow \qquad \qquad \gamma = 1.211$$

This indicates that the ripple content in the output are 1.211 times the dc component.

i.e. 121.1 % of dc component.

#### **Disadvantage of HWR:**

- The ripple factor of half wave rectifier is 1.21, which is quite high.

- The output contains lot of ripples

- ➤ The maximum theoretical efficiency is 40%.

- The practical value will be quite less than this.

- >This indicates that HWR is quite inefficient.

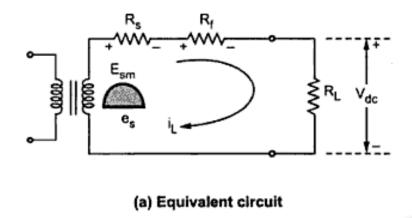

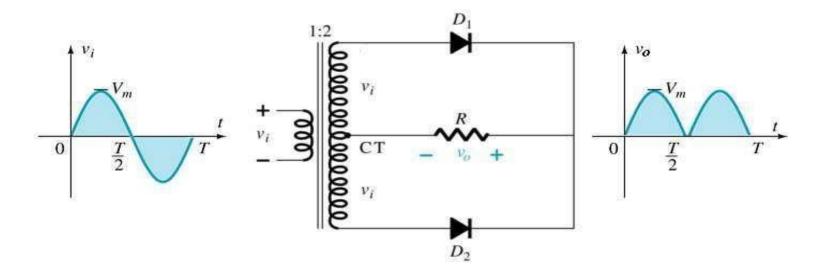

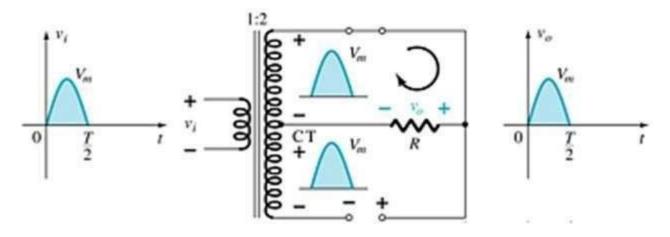

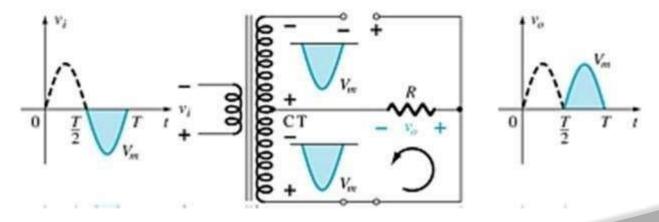

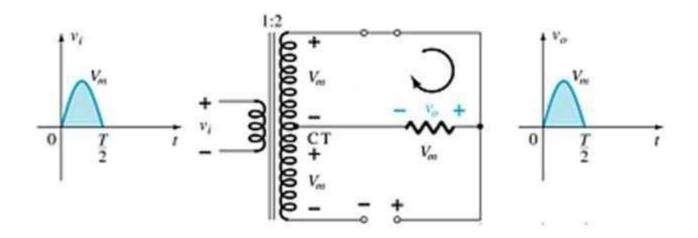

- The full wave rectifier circuit consists of two *power diodes* connected to a single load resistance (R<sub>L</sub>) with each diode taking it in turn to supply current to the load.

- When point A of the transformer is positive with respect to point C, diode  $D_1$  conducts in the forward direction as indicated by the arrows.

- ➤When point B is positive (in the negative half of the cycle) with respect to point C, diode D<sub>2</sub> conducts in the forward direction and the current flowing through resistor R is in the same direction for both half-cycles.

- As the output voltage across the resistor R is the phasor sum of the two waveforms combined, this type of full wave rectifier circuit is also known as a "bi-phase" circuit.

Current Flow during the positive half of the input cycle

Current Flow during the negative half of the input cycle

#### **Average DC current:**

$$I_{av} = I_{DC} = \frac{1}{\pi} \int_{0}^{\pi} i_{L} d(\omega t) = \frac{1}{\pi} \int_{0}^{\pi} I_{m} \sin \omega t d\omega t$$

$$I_{DC} = \frac{2I_m}{\pi}$$

$I_{DC} = \frac{2I_m}{\pi}$  for full wave rectifier

Average (DC): Voltage

$$E_{DC} = I_{DC}R_{L} = \frac{2I_{m}R_{L}}{\pi}$$

Substituting value of I<sub>m</sub>,

$$E_{DC} = \frac{2 E_{sm} R_L}{\pi \left[ R_f + R_s + R_L \right]} = \frac{2 E_{sm}}{\pi \left[ 1 + \frac{R_f + R_s}{R_L} \right]}$$

But as  $R_f$  and  $R_s \ll R_L$  hence  $\frac{R_f + R_s}{R_L} \ll 1$

$$E_{DC} = \frac{2E_{sm}}{\pi}$$

#### RMS Load Current (Irms):

$$I_{RMS} = \sqrt{\frac{1}{\pi} \int_{0}^{\pi} i \frac{1}{L} d(\omega t)} \quad \Rightarrow \quad I_{RMS} = \sqrt{\frac{1}{\pi} \int_{0}^{\pi} [I_{m} \sin \omega t]^{2} d(\omega t)} \quad \Rightarrow \quad \quad I_{RMS} = \frac{I_{m}}{\sqrt{2}}$$

#### **RMS Load Voltage:**

$$E_{L \text{ (RMS)}} = I_{RMS} R_L = \frac{I_m}{\sqrt{2}} R_L$$

#### **DC Output Power:**

D.C. Power output =

$$E_{DC}I_{DC} = I_{DC}^2R_L$$

$$P_{DC} = I_{DC}^2R_L = \left(\frac{2I_m}{\pi}\right)^2R_L$$

$$P_{DC} = \frac{4}{\pi^2}I_m^2R_L$$

### **AC input power (Pac):**

The a.c. power input is given by,

:

$$P_{AC} = I_{RMS}^2(R_f + R_s + R_L) = \left(\frac{I_m}{\sqrt{2}}\right)^2(R_f + R_s + R_L)$$

$$P_{AC} = \frac{I_m^2(R_f + R_s + R_L)}{2}$$

### Rectifier Efficiency $(\eta)$ :

But if R<sub>f</sub> + R<sub>s</sub> << R<sub>L</sub>, neglecting it from denominator

$$\eta = \frac{8 R_L}{\pi^2 (R_L)} = \frac{8}{\pi^2}$$

$$\% \eta_{\text{max}} = \frac{8}{\pi^2} \times 100 = 81.2 \%$$

### Ripple Factor:

Ripple factor =

$$\sqrt{\left[\frac{I_{RMS}}{I_{DC}}\right]^2 - 1}$$

For full wave

$$I_{RMS} = I_m/\sqrt{2}$$

and  $I_{DC} = 2I_m/\pi$

Ripple factor =

$$\sqrt{\left[\frac{I_m/\sqrt{2}}{2I_m/\pi}\right]^2 - 1} = \sqrt{\frac{\pi^2}{8} - 1}$$

Ripple factor =

$$\gamma = 0.48$$

## **Peak Inverse Voltage:**

PIV of diode =

$$2 E_{sm}$$

### **Advantages of Full Wave Rectifier:**

- Efficiency is higher.

- The large dc power output

- The ripple factor is less

## **Disadvantages of Full Wave Rectifier:**

- PIV rating of diode is higher.

- Higher PIV diodes are larger in size and costlier.

- The cost of center tap transformer is high.

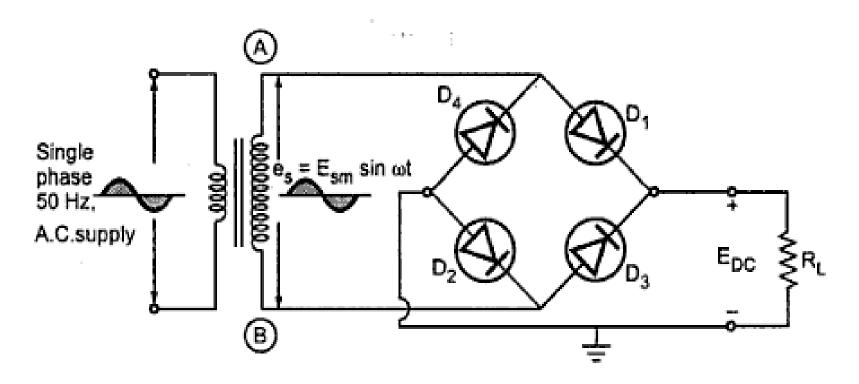

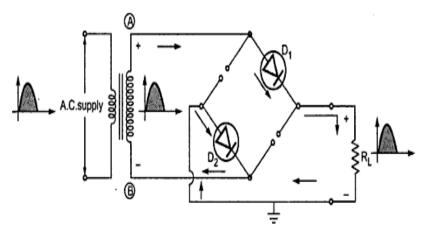

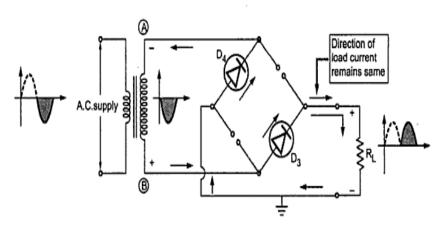

# **BRIDGE RECTIFIER**

### WORKING OF BRIDGE RECTIFIER

Current flow during positive half cycle

During the positive half cycle of secondary voltage, the diodes D1 and D2 are forward-biased, but diodes D3 and D4 do no conduct. The current is through D1, R, D2 and secondary winding.

Current flow during negative half cycle

During the negative half cycle, the diodes D3 and D4 are forward-biased, but diodes D1 and D2 do not conduct. The current is through D3, secondary winding, D4 and R.

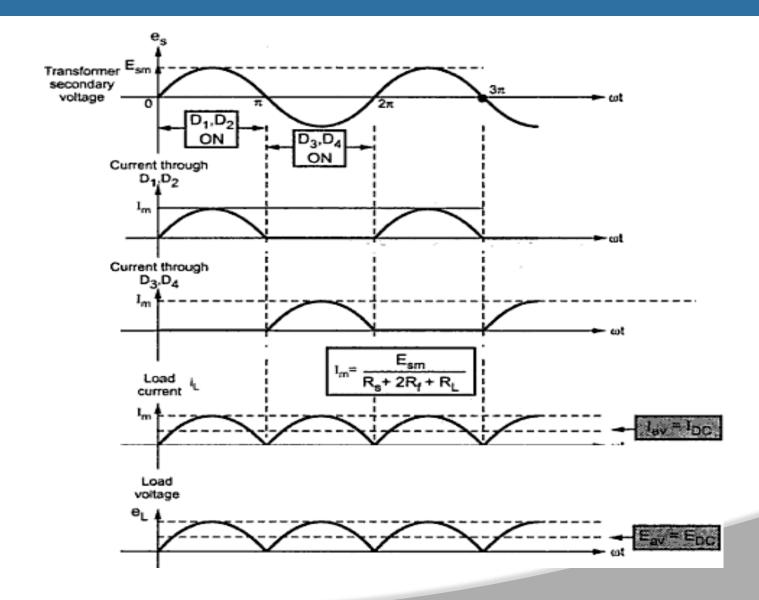

## **BRIDGE RECTIFIER WAVEFORMS**

## **BRIDGE RECTIFIER PARAMETERS**

$$I_{DC} = \frac{2I_m}{\pi}$$

and  $I_{RMS} = \frac{I_m}{\sqrt{2}}$

$$E_{DC} = I_{DC} R_{L} = \frac{2E_{sm}}{\pi}$$

$$P_{DC} = I_{DC}^{2} R_{L} = \frac{4}{\pi^{2}} I_{m}^{2} R_{L}$$

$$P_{AC} = I_{RMS}^{2} (R_{s} + 2R_{f} + R_{L}) = \frac{I_{m}^{2} (2R_{f} + R_{s} + R_{L})}{2}$$

$$\eta = \frac{8R_{L}}{\pi^{2} (R_{s} + 2R_{f} + R_{L})}, \% \eta_{max} = 81.2\%$$

$$\gamma = 0.48$$

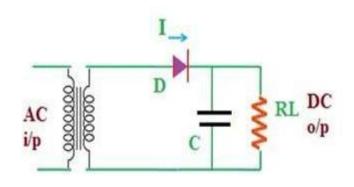

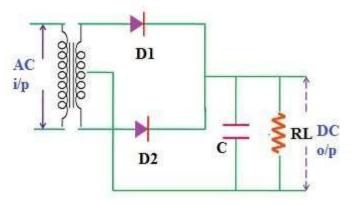

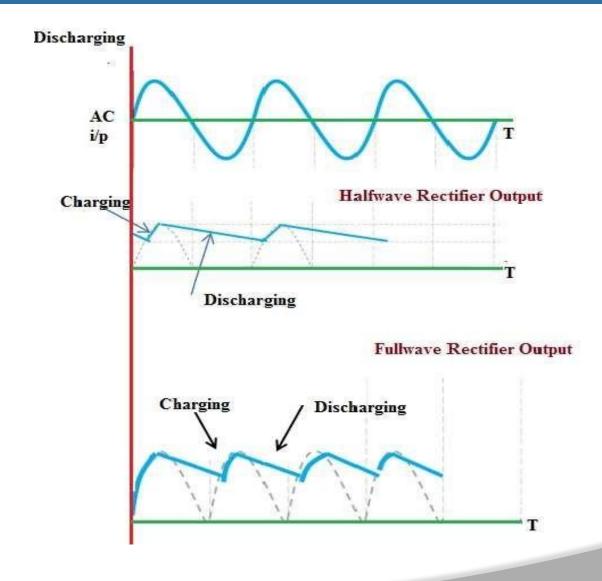

### **RECTIFIERS WITH CAPACITIVE FILTER**

Fig: H/W rectifier with filter

Fig: F/W rectifier with filter

•In full wave rectifier circuit using a capacitor filter, the capacitor C is located across the RL load resistor. The working of this rectifier is almost the same as a half wave rectifier.

## **RECTIFIERS WITH CAPACITIVE FILTER WAVEFORMS**

# MODULE-II BIPOLAR JUNCTION TRANSISTOR

Principle of Operation and characteristics - Common Emitter, Common Base, Common Collector Configurations, Operating point, DC & AC load lines, Transistor Hybrid parameter model, Determination of h- parameters from transistor characteristics, Conversion of h-parameters.

### **CONTENTS**

- >Introduction

- **➤** Common Emitter Configuration

- Common Base Configuration

- ➤ Common Collector Configuration

- ➤ Operating point, DC & AC load lines

- >Transistor Hybrid parameter model

- ➤ Conversion of h-parameters.

## **INTRODUCTION**

Transistor is a device that can be used as either an amplifier or a switch. Transistor is current controlling device.

### INTRODUCTION

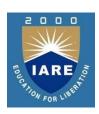

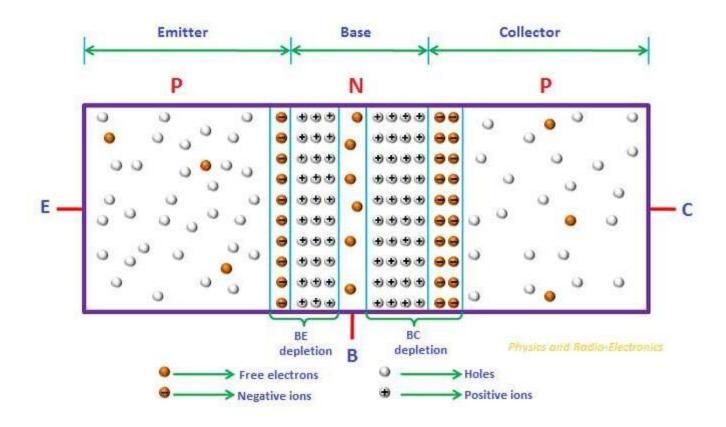

- > The three layers of BJT are called Emitter, Base and Collector

- Base is very thin compared to the other two layers

- ➤ Base is lightly doped. Emitter is heavily doped. Collector is moderately doped

- ➤ NPN Emitter and Collector are made of N-type semiconductors; Base is P-type

- PNP Emitter and Collector are P-type, Base is N-type

- Both types (NPN and PNP) are extensively used, either separately or in the same circuit

- BJT has two junctions Emitter-Base (EB) Junction

- and Collector-Base (CB) Junction

- The device is called "bipolar junction transistor" because current is due to motion of two types of charge carriers free electrons & holes

- Transistor Analogous to two diodes connected back-to-back: EB diode and CB diode

### TRANSISTOR OPERATION

- ➤ Operation of **NPN** transistor is discussed here

- ➤ For normal operation (amplifier application)

- ➤— EB junction should be forward biased

- ➤– CB junction should be reverse biased

- Depletion width at EB junction is narrow (forward biased)

- ➤ Depletion width at CB junction is wide (reverse biased)

- ➤ When EB junction is forward biased, free electrons from emitter region drift towards base region

- Some free electrons combine with holes in the base to form small base current

## **TRANSISTOR OPERATION**

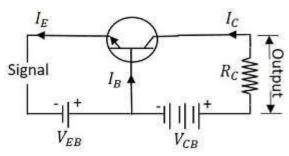

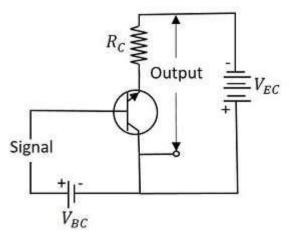

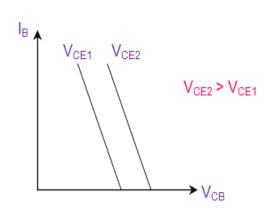

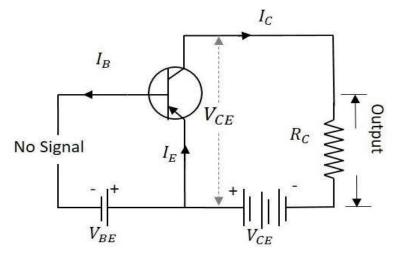

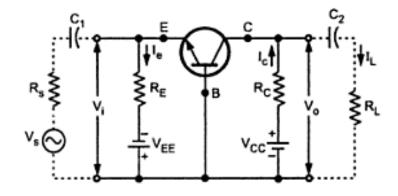

### **Common Base (CB) Configuration of Transistor**

➤ In CB Configuration, the base terminal of the transistor will be common between the input and the output terminals as shown by Fig.4. This configuration offers low input impedance, high output impedance, high resistance gain and high

voltage gain.

Fig.4: NPN Transistor in CB Configuration

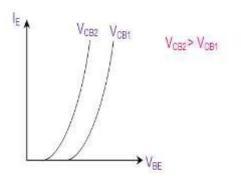

Fig.5: CB Configuration I/P Characteristics

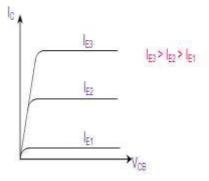

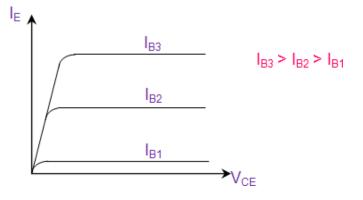

Fig.6: CB Configuration O/P Characteristics

> This leads to the expression for the input resistance as

$$R_{in} = \frac{\Delta V_{BE}}{\Delta I_E} \Big|_{V_{CB} = constant}$$

output resistance can be obtained as

$$R_{out} = \frac{\Delta V_{CB}}{\Delta I_C} \Big|_{I_E = constant}$$

The current gain has a value less than 1 and can expressed as

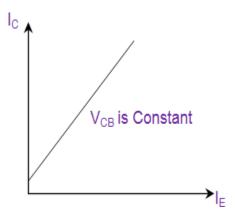

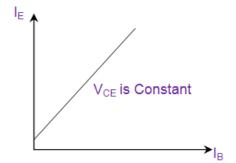

$$\alpha = \frac{\Delta I_C}{\Delta I_E}\Big|_{V_{CB} = constant}$$

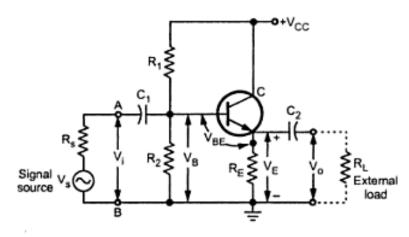

Common Collector (CC) Configuration of Transistor

Fig.7: CB Configuration Current Transfer Characteristics

This offers high input impedance, low output impedance, voltage gain less than

one and a large current gain.

Fig.8: NPN Transistor in CC Configuration

Fig.9: CC Configuration I/P

Characteristics

Fig. 10: CC Configuration O/P Characteristics

Fig.11: CC Configuration Current Transfer Characteristics

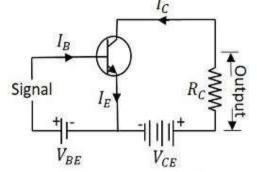

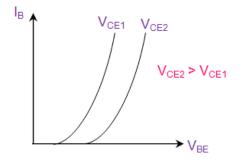

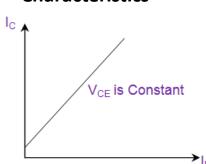

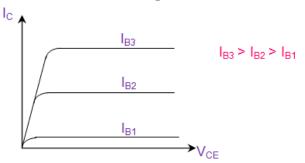

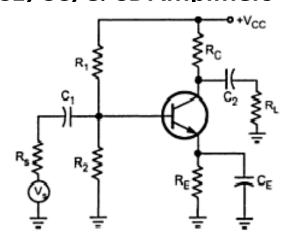

#### **Common Emitter (CE) Configuration of Transistor**

➤In this configuration, the emitter terminal is common between the input and the output terminals as shown by Fig.12. This configuration offers medium input impedance, medium output impedance, medium current gain and

Fig.12 NPN Transistor in CE Configuration

Fig.13: CE Configuration I/P

Characteristics

Fig.14: CE Configuration O/P

Characteristics

Fig.15: CE Configuration Current

Transfer Characteristics

# **COMPARISON OF TRANSISTOR CONFIGURATIONS**

| S. No. | Characteristic    | Common base                     | Common emitter                   | Common collector            |

|--------|-------------------|---------------------------------|----------------------------------|-----------------------------|

| 1.     | Input resistance  | Low (about 100 Ω)               | Low (about 750 Ω)                | Very high (about<br>750 kΩ) |

| 2.     | Output resistance | Very high (about<br>450 kΩ)     | High (about 45 k $\Omega$ )      | Low (about 50 Ω)            |

| 3.     | Voltage gain      | about 150                       | about 500                        | less than 1                 |

| 4.     | Applications      | For high frequency applications | For audio frequency applications | For impedance matching      |

| 5.     | Current gain      | No (less than 1)                | High (β)                         | Appreciable                 |

## DC AND AC LOAD LINE

### **DC Load Line**

$\begin{array}{c|c}

I_{C}(mA) & & & & \\

\hline

V_{CC} & & & & \\

\hline

R_{C} & & & & \\

\hline

& & & & \\$

Fig.17: CE Amplifier circuit with no I/P signal

Fig.18: CE O/P characteristics with DC load line

The value of collector emitter voltage at any given time will be

$$V_{CE} = V_{CC} - I_C R_C$$

- ➤ The fig.18 shows the DC load line.

- To obtain the load line, two points be A and B of the straight line are to be determined.

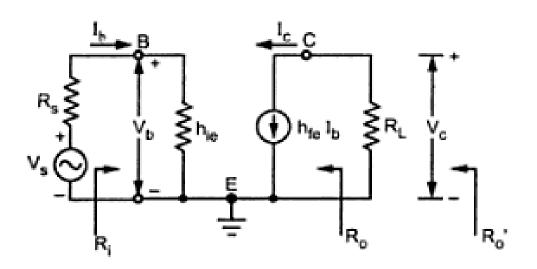

#### CE, CC, & CB Amplifiers

Practical common emitter amplifier circuit

Common collector circuit

Common base circuit

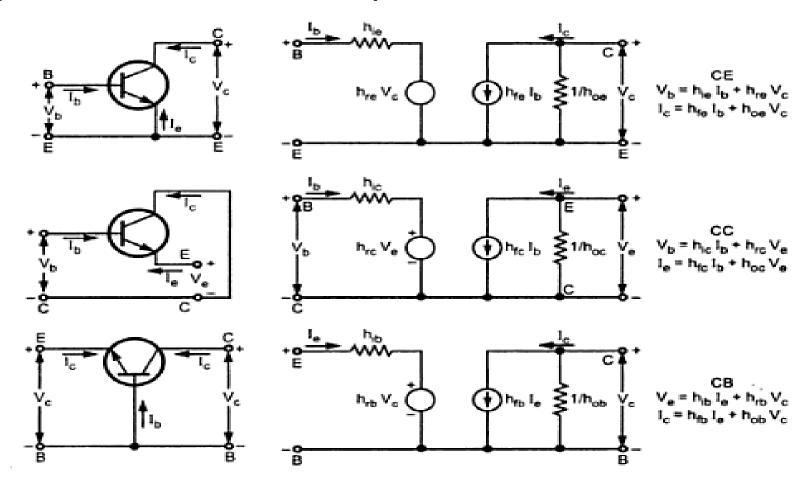

### Hybrid model of CE, CC, & CB Amplifiers

Transistor configurations and their hybrid models

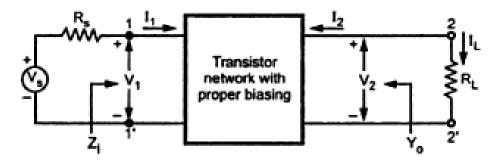

### **Small Signal Analysis Of A Junction Transistor**

#### Basic transistor amplifier

Transistor amplifier in its h-parameter model

### Small signal analysis of transistor amplifier

$$A_{is} = -\frac{h_{f}}{1 + h_{o} R_{L}}$$

$$A_{is} = \frac{A_{i} R_{s}}{Z_{i} + R_{s}}$$

$$Z_{i} = h_{i} + h_{r} A_{i} R_{L} = h_{i} - \frac{h_{f} h_{r}}{h_{o} + Y_{L}}$$

$$A_{v} = \frac{A_{i} R_{L}}{Z_{i}}$$

$$A_{vs} = \frac{A_{v} R_{i}}{Z_{i} + R_{s}} = \frac{A_{i} R_{L}}{Z_{i} + R_{s}} = \frac{A_{is} R_{L}}{R_{s}}$$

$$Y_{o} = h_{o} - \frac{h_{f} h_{r}}{h_{i} + R_{s}} = \frac{1}{Z_{o}}$$

$$A_{P} = A_{V} A_{i} = A_{i}^{2} \frac{R_{L}}{Z_{i}}$$

### Steps for ac analysis of a transistor circuit

- Draw the actual circuit diagram

- Replace Coupling Capacitors & emitter bypass capacitor by short circuit

- $\triangleright$  Replace dc source by a short circuit. In other words, short  $v_{cc}$  and ground lines

- Mark the points B(base), C(collector), E(emitter) on the circuit diagram and locate these points as the start of the equivalent circuit.

- Replace the transistor by its h-parameter model.

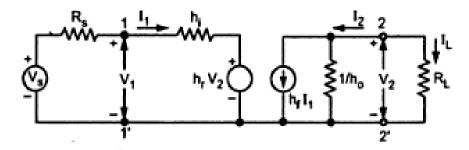

### **Approximate H-Model For CE Amplifier**

Approximate CE model

Current Gain

$$A_i \approx -h_{fe}$$

Input Impedance  $R_i \approx h_{ie}$

Voltage Gain:  $A_v = \frac{A_i R_L}{R_i} = \frac{A_i R_L}{h_{ie}}$

Output Impedance  $Y_o = 0$

$R_o = \frac{1}{Y_o} = \infty$

$R_o' = R_o \parallel R_L = \infty \parallel R_L = R_L$

# MODULE-III NUMBERSYSTEMS

**Number systems:** Complements of Numbers, Codes- Weighted and Non-weighted codes and its Properties, Parity check code and Hamming code. **Boolean Algebra:** Basic Theorems and Properties, Switching Functions-Canonical and Standard Form, Algebraic Simplification, Digital Logic Gates, EX-OR gates, Universal Gates, Multilevel NAND/NOR realizations

### **CONTENTS**

- ➤ Complements of Numbers

- Codes- Weighted and Non-weighted codes and its Properties

- ➤ Parity check code and Hamming code

- ➤ Basic Theorems and Properties

- ➤ Switching Functions- Canonical and Standard Form

- ➤ Algebraic Simplification

- ➤ Digital Logic Gates, EX-OR gates

- ➤ Universal Gates

- ➤ Multilevel NAND/NOR realizations

### **NUMBER SYSTEMS**

### **▶**Binary number system.

A method of representing **numbers** that has 2 as its base and uses only the digits 0 and 1.

Ex:10100010

## **≻**Decimal number system

A number system that uses a notation in which each number is expressed in base 10 by using one of the first nine integers or 0 in each place and letting each place value be a power of 10

Numbers:0,1,2,3,4,5,6,7,8,9

### **NUMBER SYSTEMS**

### **≻Octal number system**

The octal numbering system uses the numerals 0-1-2-3-4-5-6-7.

### > Hexa decimal number system

The hexadecimal numeral system, often shortened to "hex", is a numeral system made up of 16 symbols (base 16) they are 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E.

## **NUMBER BASE CONVERSION**

### **Binary to Decimal Conversion:**

It is by the positional weights method. In this method, each binary digit of the no. is multiplied by its position weight. The product terms are added to obtain the decimal no

#### Example:

### **NUMBER BASE CONVERSION**

#### **Binary to Octal conversion:**

Starting from the binary pt. make groups of 3 bits each, on either side of the binary pt, & replace each 3 bit binary group by the equivalent octaldigit.

#### Example:

$$1011010111_{2} = ?_{8}$$

$$1 011 010 111$$

$$\downarrow \qquad \downarrow \qquad \downarrow$$

$$1 2 2 7$$

$$1011010111_2 = 1327_8$$

## **NUMBER BASE CONVERSION**

### **Binary to Hexadecimal conversion:**

For this make groups of 4 bits each , on either side of the binary pt & replace each 4 bit group by the equivalent hexadecimal digit.

### Example:

$$1010111011_2 = 2BB_{16}$$

### **Decimal to Binary conversion:**

#### Technique

- ➤ Divide by two, keep track of the remainder

- > First remainder is bit 0 (LSB, least-significant bit)

- > Second remainder is bit 1 etc

#### **Decimal to Octal Conversion:**

To convert a mixed decimal no. To a mixed octal no. convert the integer and fraction parts separately.

To convert decimal integer no. to octal, successively divide the given no by 8 till the quotient is 0. The last remainder is the MSD . The remainder read upwards give the equivalent octal integer no.

Toconvert the given decimal fraction to octal, successively multiply the decimal fraction & the subsequent decimal fractions by 8 till the product is 0 or till the required accuracy is the MSD. The integers to the left of the octal pt read downwards give the octal fraction.

# **Example:**

$$1234_{10} = ?_8$$

$$1234_{10} = 2322_8$$

#### **Decimal to Hexadecimal conversion:**

It is successively divide the given decimal no. by 16 till the quotient is zero. The last remainder is the MSB. The remainder read from bottom to top gives the equivalent hexadecimal integer.

Toconvert a decimal fraction to hexadecimal successively multiply the given decimal fraction & subsequent decimal fractions by 16, till the product is zero. Or till the required accuracy is obtained and collect all the integers to the left of decimal pt. The first integer is MSB & the integer read from top to bottom give the hexadecimal fraction known as **the hexadabble method**.

# **Example:**

$$1234_{10} = 4D2_{16}$$

#### **Octal to binary Conversion:**

Convert each octal digit to a 3-bit equivalent binary representation

#### **Octal to decimal Conversion:**

Multiply each digit in the octal no by the weight of its position & add all the product terms Decimal value of the octal no.

$$724_8 = > 4 \times 8^0 = 4$$

$2 \times 8^1 = 16$

$7 \times 8^2 = 448$

$468_{10}$

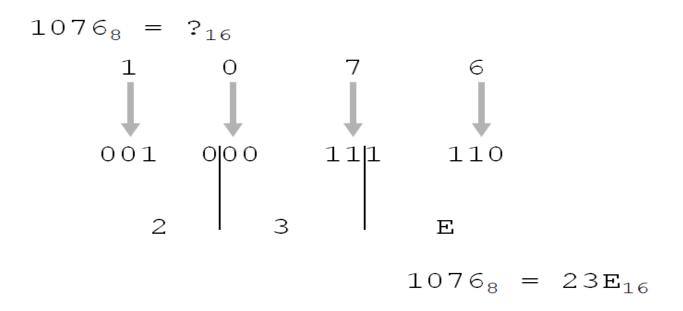

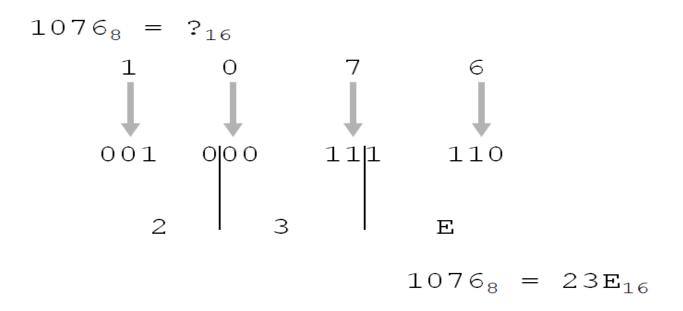

#### Octal to hexadecimal conversion:

The simplest way is to first convert the given octal no. to binary & then the binary no. to hexadecimal.

#### Octal to hexadecimal conversion:

The simplest way is to first convert the given octal no. to binary & then the binary no. to hexadecimal.

## **Hexa decimal to binary Conversion:**

Convert each hexadecimal digit to a 4-bit equivalent binary representation

#### Hexa decimal to decimal Conversion:

Convert each hexadecimal digit to a 4-bit equivalent binary representation

# **BINARYARITHMETIC**

### **Binary Addition:**

Rules: 0+0=0

0+1=1

1+0=1

1+1=10

i.e, 0 with a carry of 1.

# **Binary Subtraction:**

Rules:

0 = 0 = 0

1-1=0

1-0=1

0-1=1

with a borrow of 1

# COMPLEMENTS

### 9's & 10's Complements:

It is the Subtraction of decimal number can be accomplished by the 9's & 10's compliment methods similar to the 1's & 2's compliment methods of binary. The 9's compliment of a decimal number is obtained by subtracting each digit of that decimal number from 9. The 10's compliment of a decimal number is obtained by adding a 1 to its 9's compliment.

# **BINARY CODED DECIMAL**

#### **BCD Addition:**

It is individually adding the corresponding digits of the decimal numbers expressed in 4 bit binary groups starting from the LSD.

If there is no carry & the sum term is not an illegal code, no correction is needed.

If there is a carry out of one group to the next group or if the sum term is an illegal code then  $6_{10}$  (0110) is added to the sum term of that group & the resulting carry is added to the next group.

# **BINARY CODED DECIMAL**

#### **BCD Subtraction:**

Performed by subtracting the digits of each 4 bit group of the subtrahend the digits from the corresponding 4- bit group of the minuend in binary starting from the LSD . if there is no borrow from the next group , then  $6_{10}$  (0110) is subtracted from the difference term of this group.

### Some Common Error Detecting and Correcting Codes

- Parity Code

- Hamming Code

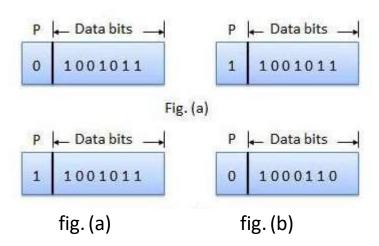

### **Parity Code:**

- A parity bit is an extra bit added to a string of data bits in order to detect any error that might have crept into it while it was being stored or processed and moved from one place to another in a digital system.

- ➤ This simple parity code suffers from two limitations. Firstly, it cannot detect the error if the number of bits having undergone a change is even.

The parity bit can be set to 0 and 1 depending on the type of the parity required.

- For even parity, this bit is set to 1 or 0 such that the no. of "1 bits" in the entire word is even. Shown in fig. (a).

- For odd parity, this bit is set to 1 or 0 such that the no. of "1 bits" In the entire word is odd. Shown in fig. (b).

### **Hamming Code:**

- ➤ An increase in the number of redundant bits added to message bits can enhance the capability of the code to detect and correct errors.

- ➤ If sufficient number of redundant bits arranged such that different error bits produce different error results, then it should be possible not only to detect the error bit but also to identify its location.

- In fact, the addition of redundant bits alters the 'distance' code parameter, which has come to be known as the Hamming distance.

The code word sequence for this code is written as  $P_1P_2D_1P_3D_2D_3D_4$ , with  $P_1$ ,  $P_2$  and  $P_3$  being the parity bits and  $D_1$ ,  $D_2$ ,  $D_3$  and  $D_4$  being the data bits.

## Generation of HammingCode:

|                                 | $P_1$ | $P_2$ | $D_1$ | $P_3$ | $D_2$ | $D_3$ | $D_4$ |

|---------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Data bits (without parity)      |       |       | 0     |       | 1     | 1     | 0     |

| Data bits with parity bit $P_1$ | 1     |       | 0     |       | 1     |       | 0     |

| Data bits with parity bit $P_2$ |       | 1     | 0     |       |       | 1     | 0     |

| Data bits with parity bit $P_3$ |       |       |       | 0     | 1     | 1     | 0     |

| Data bits with parity           | 1     | 1     | 0     | 0     | 1     | 1     | 0     |

### Identity Elements

> a:X+0=X

> b:X•1=X

Commutativity

a: X+Y=Y+X

> b:X•Y=Y•X

Complements

> a: X+X'=1

b: X • X′ = 0

## **OR** operation

| Х | Υ | X+0 | X+Y | Y+X | Χ' | X+X' |

|---|---|-----|-----|-----|----|------|

| 0 | 0 | 0   | 0   | 0   | 1  | 1    |

| 0 | 1 | 0   | 1   | 1   | 1  | 1    |

| 1 | 0 | 1   | 1   | 1   | 0  | 1    |

| 1 | 1 | 1   | 1   | 1   | 0  | 1    |

## **AND** operation

| Χ | Υ | X•1 | X•Y | Y∙X | X' | X•X′ |

|---|---|-----|-----|-----|----|------|

| 0 | 0 | 0   | 0   | 0   | 1  | 0    |

| 0 | 1 | 0   | 0   | 0   | 1  | 0    |

| 1 | 0 | 1   | 0   | 0   | 0  | 0    |

| 1 | 1 | 1   | 1   | 1   | 0  | 0    |

# > Associativity

- $\rightarrow$  a:(X+Y)+Z=X+(Y+Z)

- $\rightarrow$  b:  $(X \bullet Y) \bullet Z = X \bullet (Y \bullet Z)$

| X | Υ | Z | X+Y | (X+Y)+Z | Y+Z | X+(Y+Z) | X•Y | (X•Y)•Z | Y∙Z | X•(Y•Z) |

|---|---|---|-----|---------|-----|---------|-----|---------|-----|---------|

| 0 | 0 | 0 | 0   | 0       | 0   | 0       | 0   | 0       | 0   | 0       |

| 0 | 0 | 1 | 0   | 1       | 1   | 1       | 0   | 0       | 0   | 0       |

| 0 | 1 | 0 | 1   | 1       | 1   | 1       | 0   | 0       | 0   | 0       |

| 0 | 1 | 1 | 1   | 1       | 1   | 1       | 0   | 0       | 1   | 0       |

| 1 | 0 | 0 | 1   | 1       | 0   | 1       | 0   | 0       | 0   | 0       |

| 1 | 0 | 1 | 1   | 1       | 1   | 1       | 0   | 0       | 0   | 0       |

| 1 | 1 | 0 | 1   | 1       | 1   | 1       | 1   | 0       | 0   | 0       |

| 1 | 1 | 1 | 1   | 1       | 1   | 1       | 1   | 1       | 1   | 1       |

# > Distributivity

$$\rightarrow$$

a: X+(Y•Z) = (X+Y)•(X+Z)

$$\rightarrow$$

b:  $X \bullet (Y+Z) = (X \bullet Y) + (X \bullet Z)$

|   |   |   |     |     | (X+Y)• |     | X+    |     |     | X•Y+ |     | Х•    |

|---|---|---|-----|-----|--------|-----|-------|-----|-----|------|-----|-------|

| X | Υ | Z | X+Y | X+Z | (X+Z)  | Y∙Z | (Y•Z) | Х∙Ү | X∙Z | X∙Z  | Y+Z | (Y+Z) |

| 0 | 0 | 0 | 0   | 0   | 0      | 0   | 0     | 0   | 0   | 0    | 0   | 0     |

| 0 | 0 | 1 | 0   | 1   | 0      | 0   | 0     | 0   | 0   | 0    | 1   | 0     |

| 0 | 1 | 0 | 1   | 0   | 0      | 0   | 0     | 0   | 0   | 0    | 1   | 0     |

| 0 | 1 | 1 | 1   | 1   | 1      | 1   | 1     | 0   | 0   | 0    | 1   | 0     |

| 1 | 0 | 0 | 1   | 1   | 1      | 0   | 1     | 0   | 0   | 0    | 0   | 0     |

| 1 | 0 | 1 | 1   | 1   | 1      | 0   | 1     | 0   | 1   | 1    | 1   | 1     |

| 1 | 1 | 0 | 1   | 1   | 1      | 0   | 1     | 1   | 0   | 1    | 1   | 1     |

| 1 | 1 | 1 | 1   | 1   | 1      | 1   | 1     | 1   | 1   | 1    | 1   | 1     |

> Idempotency

$$a:X+X=X$$

> Null elements

> Involution

|   |   | OR  | AND |     |     |     |     |    | _   |

|---|---|-----|-----|-----|-----|-----|-----|----|-----|

| X | Υ | X+Y | X•Y | X+X | X•X | X+1 | X•0 | X' | Χ'' |

| 0 | 0 | 0   | 0   | 0   | 0   | 1   | 0   | 1  | 0   |

| 0 | 1 | 1   | 0   | 0   | 0   | 1   | 0   | 1  | 0   |

| 1 | 0 | 1   | 0   | 1   | 1   | 1   | 0   | 0  | 1   |

| 1 | 1 | 1   | 1   | 1   | 1   | 1   | 0   | 0  | 1   |

# > Absorption

- $a: (X \bullet Y) + (X \bullet Y' \bullet Z) = (X \bullet Y) + (X \bullet Z)$

- $b: (X+Y) \bullet (X+Y'+Z) = (X+Y) \bullet (X+Z)$

|   |       |   |    |    |      | (XY)+  |    | (XY)+ |     | X+Y' | (X+Y)•   |     | (X+Y)• |

|---|-------|---|----|----|------|--------|----|-------|-----|------|----------|-----|--------|

| X | ( Y ) | Z | Y' | XY | XY'Z | (XY'Z) | XZ | (XZ)  | X+Y | +Z   | (X+Y'+Z) | X+Z | (X+Z)  |

| 0 | 0     | 0 | 1  | 0  | 0    | 0      | 0  | 0     | 0   | 1    | 0        | 0   | 0      |

| 0 | 0     | 1 | 1  | 0  | 0    | 0      | 0  | 0     | 0   | 1    | 0        | 1   | 0      |

| 0 | 1     | 0 | 0  | 0  | 0    | 0      | 0  | 0     | 1   | 0    | 0        | 0   | 0      |

| 0 | 1     | 1 | 0  | 0  | 0    | 0      | 0  | 0     | 1   | 1    | 1        | 1   | 1      |

| 1 | 0     | 0 | 1  | 0  | 0    | 0      | 0  | 0     | 1   | 1    | 1        | 1   | 1      |

| 1 | 0     | 1 | 1  | 0  | 1    | 1      | 1  | 1     | 1   | 1    | 1        | 1   | 1      |

| 1 | 1     | 0 | 0  | 1  | 0    | 1      | 0  | 1     | 1   | 1    | 1        | 1   | 1      |

| 1 | 1     | 1 | 0  | 1  | 0    | 1      | 1  | 1     | 1   | 1    | 1        | 1   | 1      |

DeMorgan's theorem (very important!)

#### Generalized DeMorgan's theorem:

• GT8b:

$$(X_1 \bullet X_2 \bullet ... \bullet X_{n-1} \bullet X_n)' = X_1' + X_2' + ... + X_{n-1}' + X_n'$$

#### OR AND

| Ĭ | X | Y | X+Y | X•Y | X' | Y' | (X+Y)' | X'•Y' | (X•Y)' | X'+Y' |

|---|---|---|-----|-----|----|----|--------|-------|--------|-------|

|   | 0 | 0 | 0   | 0   | 1  | 1  | 1      | 1     | 1      | 1     |

|   | 0 | 1 | 1   | 0   | 1  | 0  | 0      | 0     | 1      | 1     |

|   | 1 | 0 | 1   | 0   | 0  | 1  | 0      | 0     | 1      | 1     |

|   | 1 | 1 | 1   | 1   | 0  | 0  | 0      | 0     | 0      | 0     |

#### Consensus Theorem

$$\rightarrow$$

a:  $(X \bullet Y) + (X' \bullet Z) + (Y \bullet Z) = (X \bullet Y) + (X' \bullet Z)$

$$\rightarrow$$

b:  $(X+Y) \bullet (X'+Z) \bullet (Y+Z) = (X+Y) \bullet (X'+Z)$

| x | Υ | Z | X' | XY | X'Z | YZ | (XY)+<br>(X'Z)+<br>(YZ) | (XY)+<br>(X'Z) | X+Y | X'+Z | Y+Z | (X+Y) •<br>(X'+Z) •<br>(Y+Z) | (X+Y)•<br>(X'+Z) |

|---|---|---|----|----|-----|----|-------------------------|----------------|-----|------|-----|------------------------------|------------------|

| 0 | 0 | 0 | 1  | 0  | 0   | 0  | 0                       | 0              | 0   | 1    | 0   | 0                            | 0                |

| 0 | 0 | 1 | 1  | 0  | 1   | 0  | 1                       | 1              | 0   | 1    | 1   | 0                            | 0                |

| 0 | 1 | 0 | 1  | 0  | 0   | 0  | 0                       | 0              | 1   | 1    | 1   | 1                            | 1                |

| 0 | 1 | 1 | 1  | 0  | 1   | 1  | 1                       | 1              | 1   | 1    | 1   | 1                            | 1                |

| 1 | 0 | 0 | 0  | 0  | 0   | 0  | 0                       | 0              | 1   | 0    | 0   | 0                            | 0                |

| 1 | 0 | 1 | 0  | 0  | 0   | 0  | 0                       | 0              | 1   | 1    | 1   | 1                            | 1                |

| 1 | 1 | 0 | 0  | 1  | 0   | 0  | 1                       | 1              | 1   | 0    | 1   | 0                            | 0                |

| 1 | 1 | 1 | 0  | 1  | 0   | 1  | 1                       | 1              | 1   | 1    | 1   | 1                            | 1                |

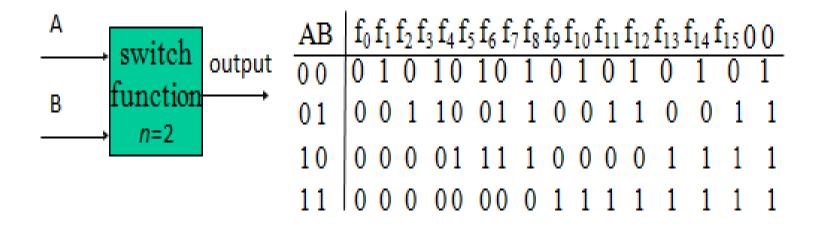

# **SWITCHING FUNCTIONS**

- For *n* variables, there are 2<sup>n</sup> possible combinations of Values from all 0s to all 1s

- ➤ There are 2 possible values for the output of a function of a combination of values of *n* variables i.e. 0 and 1

- $\triangleright$  There are  $2^{2^n}$  different switching functions for n variables

- $\rightarrow$  n=0 (no inputs)  $2^{2n} = 2^{20} = 2^1 = 2$

Output can be either 0 or 1

$$> n=1 \text{ (1 input, A)}$$

$2^{2n}=2^{21}=2^2=4$

Output can be 0, 1, A, or A'

# **SWITCHING FUNCTIONS EXAMPLE**

$$\triangleright$$

n=2 (2 inputs, A and B)

$$2^{2n} = 2^{2^2} = 2^4 = 16$$

$$f_0 = 0$$

$f_1 = A'B' = (A+B)'$

$f_2 = A'B$

$f_3 = A'B' + A'B = A'(B'+B) = A'$

Logical functions are generally expressed in terms of different combinations of logical variables with their true forms as well as the complement forms. Binary logic values obtained by the logical functions and logic variables are in binary form. An arbitrary logic function can be expressed in the following forms.

- Sum of the Products (SOP)

- Product of the Sums (POS)

- Product Term: In Boolean algebra, the logical product of several variables on which a function depends is considered to be a product term. In other words, the AND function is referred to as a product term or standard product.

- > Sum Term: An OR function is referred to as a sum term

- > Sum of Products (SOP): The logical sum of two or more logical productterms is referred to as a sum of products expression

$$Y = AB + BC + AC$$

➤ **Product of Sums (POS):** Similarly, the logical product of two or morelogical sum terms is called a product of sums expression

$$Y = (A + B + C)(\bar{A} + \bar{B} + \bar{C})$$

> Standard form: The standard form of the Boolean function is when it is expressed in sum of the products or product of the sums fashion

$$Y = AB + BC + AC$$

- Nonstandard Form: Boolean functions are also sometimes expressed in nonstandard forms like  $F = (AB + CD)(\bar{A}\bar{B} + \bar{C}\bar{D})$ , which is neither a sum of products form nor a product of sums form.

- ➤ **Minterm**: A product term containing all n variables of the function in either true or complemented form is called the minterm. Each minterm is obtained by an AND operation of the variables in their true form or complemented form.

- Maxterm: A sum term containing all n variables of the function in either true or complemented form is called the Maxterm. Each Maxterm is obtained by an OR operation of the variables in their true form or complemented form.

- ➤ The canonical sum of products form of a logic function can be obtained by using the following procedure:

- Check each term in the given logic function. Retain if it is a minterm, continue to examine the next term in the same manner.

- Examine for the variables that are missing in each product which is not a minterm. If the missing variable in the minterm is X, multiply that minterm with (X+X').

- Multiply all the products and discard the redundant terms.

- Example: Obtain the canonical sum of product form of the following function F(A,B,C) = A + BC

- Solution: F(A,B,C) = A + BC  $= A(B + \bar{B})(C + \bar{C}) + BC(A + \bar{A})$   $= (AB + A\bar{B})(C + \bar{C}) + ABC + \bar{A}BC$   $= ABC + A\bar{B}C + AB\bar{C} + AB\bar{C} + AB\bar{C} + ABC + \bar{A}BC$   $= ABC + A\bar{B}C + AB\bar{C} + AB\bar{C} + ABC = ABC$

- · Hence the canonical sum of the product expression of the given function is

$$F(A,B,C) = ABC + A\overline{B}C + AB\overline{C} + A\overline{B}\overline{C} + \overline{A}BC$$

➤ The product of sums form is a method (or form) of simplifying the Boolean expressions of logic gates. In this POS form, all the variables are ORed, i.e. written as sums to form sum terms. All these sum terms are ANDed (multiplied) together to get the product-of-sum form. This form is exactly opposite to the SOP form. So this can also be said as —Dualof SOP form.

$$(A+B) * (A + B + C) * (C+D)$$

POS form can be obtained by

- Writing an OR term for each input combination, which produces LOW output.

- Writing the input variables if the value is 0, and write the complement of the variable if its value is AND the OR terms to obtain the output function.

### **ALGEBRAIC SIMPLIFICATION**

Minimize the following Boolean expression using Boolean identities –

$$F(A,B,C)=(A+B)(A+C)F(A,B,C)=(A+B)(A+C)$$

#### Solution

Given,

$$F(A,B,C)=(A+B)(A+C)$$

$$F(A,B,C)=A(1+C)+B.A+B.C$$

[Applying distributive Law]

$$F(A,B,C)=(A+1).A+B.C$$

[Applying distributive Law]

So,

$$F(A,B,C)=A+BCF(A,B,C)=A+BC$$

is the minimized form.

# **DIGITAL LOGIC GATES**

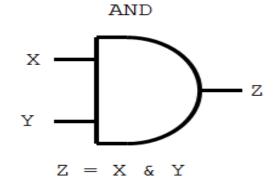

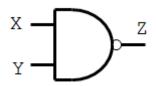

### **AND GATE:**

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

|   |   |   |

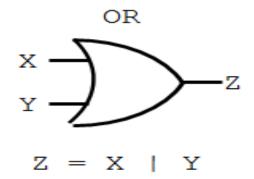

#### **OR GATE:**

$$Z=A+B$$

| Х | Y | Z |

|---|---|---|

| O | 0 | 0 |

| O | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

|   | ı |   |

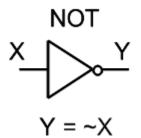

# **DIGITAL LOGIC GATES**

#### **NOT GATE:**

#### **NAND GATE:**

| X | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

|   |   |   |

# **DIGITAL LOGIC GATES**

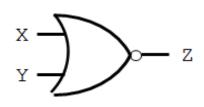

#### **NOR GATE:**

| Χ | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

|   |   |   |

#### **Ex-OR GATE:**

| ХΥ  | Z |

|-----|---|

| 0 0 | 1 |

| 0 1 | O |

| 1 0 | 0 |

| 1 1 | 1 |

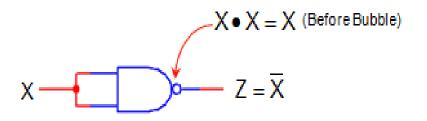

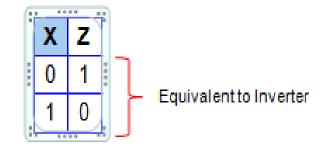

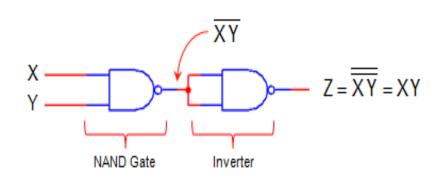

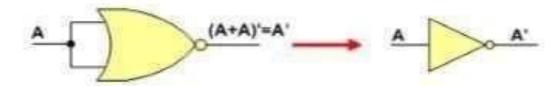

#### NAND Gate as an Inverter Gate

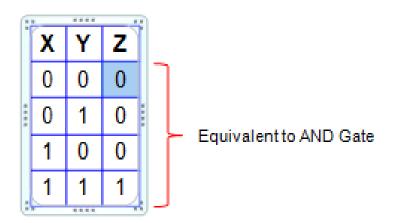

#### NAND Gate as an AND Gate

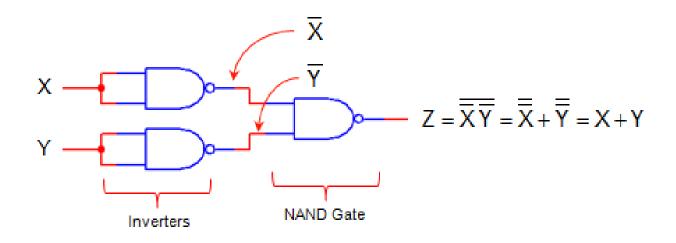

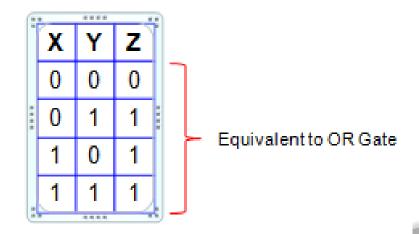

#### NAND Gate as an OR Gate

1. All NOR input pins connect to the input signal A gives an output A'.

2. One NOR input pin is connected to the input signal A while all other input pins are connected to logic 0. The output will be A'.

#### Implementing OR Using only NOR Gates

An OR gate can be replaced by NOR gates as shown in the figure (The OR is replaced by a NOR gate with its output complemented by a NOR gate inverter)

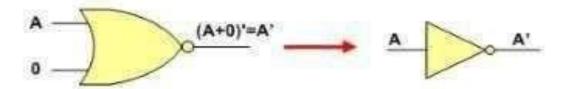

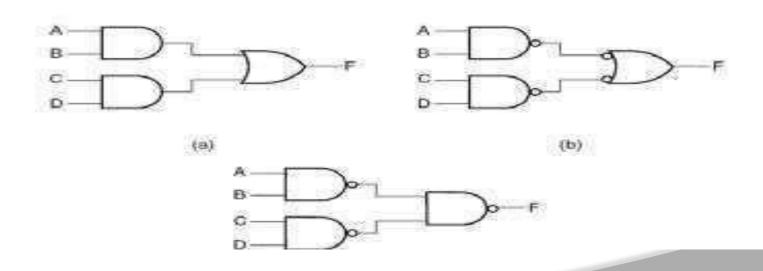

#### **Example 1:** implement the following function F = AB + CD

- The implementation of Boolean functions with NAND gatesrequires that the functions be in sum of products (SOP) form.

- This function can be implemented by three steps.

#### **Example 1:** implement the following function F = AB + CD

- The implementation of Boolean functions with NAND gatesrequires that the functions be in sum of products (SOP) form.

- This function can be implemented by three steps.

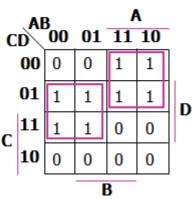

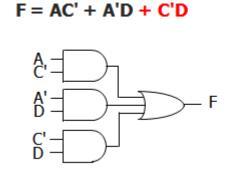

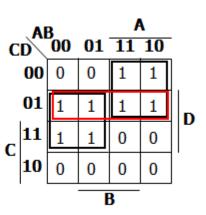

# MODULE-IV MINIMIZATION OF BOOLEAN FUNCTIONS

**Karnaugh Map Method** - Up to five Variables, Don't Care Map Entries, Tabular Method,

**Combinational Logic Circuits:** Adders, Subtractors, comparators, Multiplexers, Demultiplexers, Encoders, Decoders and Code converters, Hazards and Hazard Free Relations.

## **CONTENTS**

- ➤ Up to five Variables,

- ➤ Don't Care Map Entries,

- ➤ Tabular Method,

- > Adders,

- ➤ Subtractors,

- >comparators, Multiplexers, Demultiplexers,

- ➤ Encoders, Decoders and Code converters,

- > Hazards and Hazard Free Relations.

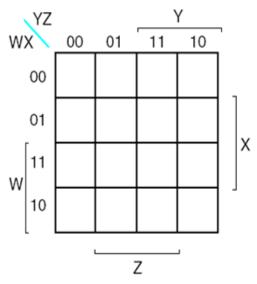

#### **KARANAUGH MAP**

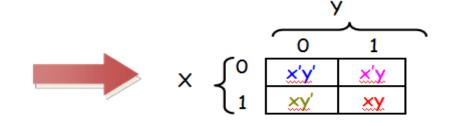

A two-variable function has four possible minterms. We can re- arrange these minterms into a Karnaughmap

| × | у | mįnterm |

|---|---|---------|

| 0 | 0 | x'y'    |

| 0 | 1 | ×'y     |

| 1 | 0 | ×χ'     |

| 1 | 1 | ×χ      |

- Now we can easily see which minterms containcommonliterals

- Minterms on the left and right sides contain y' and y respectively

- Minterms in the top and bottom rows contain x' and x respectively

|     |   | У    |     |  |  |

|-----|---|------|-----|--|--|

|     | • | 0    | 1   |  |  |

| v J | 0 | x'y' | ×'y |  |  |

| ^   | 1 | xy'  | ×y  |  |  |

|   | У  | У   |

|---|----|-----|

| X | ΧY | х'y |

| X | ×  | хy  |

#### **KARANAUGH MAP**

- Make as few rectangles as possible, to minimize the number of products in the final expression.

- Make each rectangle as large as possible, to minimize the number of literals in each term.

- Rectangles can be overlapped, if that makes them larger

- The most difficult step is grouping together all the 1s in the K-map

- Make rectangles around groups of one, two, four or eight1s

- All of the 1s in the map should be included in at least one

- rectangle. Do not include any of the0s

- Each group corresponds to oneproductterm

|   |   |   | \ | У |

|---|---|---|---|---|

|   | 0 | 1 | 0 | 0 |

| X | 0 | 1 | 1 | 1 |

| · |   | Ž |   |   |

#### **3 VARIABLEK-MAP**

- $\triangleright$  Let's consider simplifying f(x,y,z) = xy + y'z + xz

- You should convert the expression into a sum ofmintermsform,

- ➤ The easiest way to do this is to make a truth table forthe function, and then read off theminterms

- You can either write out the literals or use theminterm shorthand

- Here is the truth table and sum of minterms for ourexample:

| × | У | Z | f(x,y,z) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | 0        |

| 0 | 1 | 1 | 0        |

| 1 | 0 | 0 | 0        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | 1        |

| 1 | 1 | 1 | 1        |

$$f(x,y,z) = x'y'z + xy'z + xyz' + xyz' + xyz = m_1 + m_5 + m_6 + m_7$$

## **3 VARIABLEK-MAP**

Maxterms are grouped to find minimal PoS expression yz 01 11 10

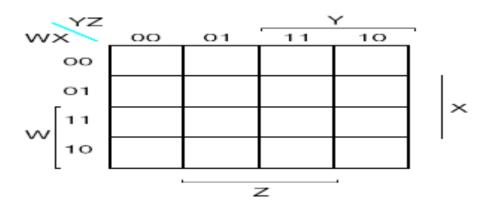

## **4-VARIABLE K-MAP**

- We can do four-variable expressions too!

- The minterms in the third and fourth columns, and inthethird and

- fourth rows, are switchedaround.

- Again, this ensures that adjacent squares have commonliterals

- Grouping minterms is similar to the three-variable case, but:

- You can have rectangular groups of 1, 2, 4, 8 or 16 minterms

- You can wrap around all four sides

# **4-VARIABLE K-MAP**

|    |          |         | ,      | У       |   |

|----|----------|---------|--------|---------|---|

|    | w'x'y'z' | w'x'y'z | w'x'yz | w'x'yz' |   |

|    | w'xy'z'  | w'xy'z  | w'xyz  | w'xyz'  | v |

| W  | wxy'z'   | wxy'z   | wxyz   | wxyz'   |   |

| VV | wx'y'z'  | wx'y'z  | wx'yz  | wx'yz'  |   |

| Z  |          |         | -      |         | - |

|  |   |                        |             | )               | /                      |   |

|--|---|------------------------|-------------|-----------------|------------------------|---|

|  |   | $\mathbf{m}_0$         | $m_1$       | <b>m</b> 3      | m <sub>2</sub>         |   |

|  |   | m <sub>4</sub>         | <b>m</b> 5  | <b>m</b> 7      | <b>m</b> 6             | X |

|  | W | <b>m</b> <sub>12</sub> | <b>m</b> 13 | <b>m</b> 15     | m <sub>14</sub>        |   |

|  |   | m <sub>8</sub>         | <b>m</b> 9  | m <sub>11</sub> | <b>m</b> <sub>10</sub> |   |

|  | , |                        | 7           | 7               |                        |   |

## **DON'T CARE CONDITION**

- You don't always need all 2<sup>n</sup> input combinations in ann-variable function

- If you can guarantee that certain input combinationsnever occur

- If some outputs aren't used in the rest of thecircuit

| × | У | z | f(x,y,z) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | X        |

| 0 | 1 | 1 | 0        |

| 1 | 0 | 0 | 0        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | X        |

| 1 | 1 | 1 | 1        |

➤ We mark don't-care outputs in truth tables and K-maps with Xs.

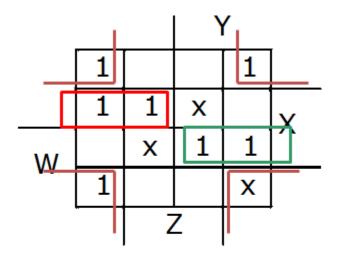

## **DON'T CARE CONDITION**

> Find a MSP for

$$f(w,x,y,z) = \sum m(0,2,4,5,8,14,15), d(w,x,y,z) = \sum m(7,10,13)$$

This notation means that input combinations wxyz = 0111, 1010 and 1101(corresponding to minterms  $m_7$ ,  $m_{10}$  and  $m_{13}$ ) are unused.

|   |   |   | У | , |   |

|---|---|---|---|---|---|

|   | 1 | 0 | 0 | 1 |   |

|   | 1 | 1 | × | 0 | X |

| W | 0 | × | 1 | 1 |   |

|   | 1 | 0 | 0 | × |   |

|   | Z |   |   |   |   |

## DON'T CARE CONDITION

#### Find a MSP for:

$$f(w,x,y,z) = \sum m(0,2,4,5,8,14,15), d(w,x,y,z) = \sum m(7,10,13)$$

$$f(w,x,y,z) = x'z' + w'xy' + wxy$$

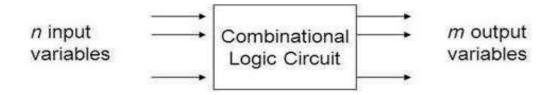

## **COMBINATIONAL CIRCUITS**

- Combinational circuit is a circuit in which we combine the different gates in the circuit, for example encoder, decoder, multiplexer and demultiplexer.

- Some of the characteristics of combinational circuits arefollowing:

- The output of combinational circuit at any instant of time, depends only on the levels present at inputterminals.

- The combinational circuit do not use any memory. The previous state of input does not have any effect on the present state of the circuit.

- A combinational circuit can have an n number of inputs and mnumber of outputs.

## **COMBINATIONAL CIRCUITS**

#### Block diagram:

possible combinations of inputvalues.

- Specific functions : of combinational circuits

- Adders, subtractors, multiplexers, comparators, encoder, Decoder. MSI Circuits and standardcells

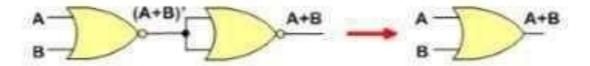

## **ANALYSIS PROCEDURE**

#### **Analysis procedure**

Toobtain the output Boolean functions from a logic diagram, proceed as follows:

- Label all gate outputs that are a function of input variables with arbitrary symbols. Determine the Boolean functions foreachgate output.

- Label the gates that are a function of input variables and previously labeled gates with other arbitrary symbols. Find the Boolean functions for these gates.

- Repeat the process outlined in step 2 until the outputs of the circuit are obtained.

#### **DESIGN PROCEDURE**

#### **Design Procedure**

- ➤ The problem is stated

- ➤ The number of available input variables andrequiredoutput variables is determined.

- > The input and output variables are assigned letter symbols.

- The truth table that defines the required relationship between inputs and outputs is derived.

- > The simplified Boolean function for each output is obtained.

- > The logic diagram is drawn.

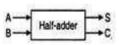

#### **BINARY ADDERS**

#### **ADDERS**

#### Half Adder

A Half Adder is a combinational circuit with two binary inputs (augends and addend bits and two binary outputs (sum and carry bits.) It adds the two inputs (A and B) and produces the sum (S) and the carry (C) bits.

Fig 1:Blockdiagram

| Inp | nputs Output |   | puts |

|-----|--------------|---|------|

| Ā   | В            | s | С    |

| 0   | 0            | 0 | 0    |

| 0   | 1            | 1 | 0    |

| 1   | 0            | 1 | 0    |

| 1   | 1            | 0 | 1    |

Fig 2:Truthtable

#### **BINARYSUBTRACTORS**

#### **Full subtractor**

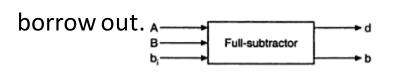

The full subtractor perform subtraction of three input bits: the minuend, subtrahend, and borrow in and generates two output bits difference and

Fig 7:Blockdiagram

| Ir | nput | 5 | Difference Borro |   |

|----|------|---|------------------|---|

| A  | В    | b | d                | ь |

| 0  | 0    | 0 | 0                | 0 |

| 0  | 0    | 1 | 1                | 1 |

| 0  | 1    | 0 | 1                | 1 |

| 0  | 1    | 1 | 0                | 1 |

| 1  | 0    | 0 | 1                | 0 |

| 1  | 0    | 1 | 0                | 0 |

| 1  | 1    | 0 | 0                | 0 |

| 1  | 1    | 1 | 1                | 1 |

|    |      |   |                  |   |

Fig 8: Truthtable

$$d = \overline{ABb}_i + \overline{AB} \overline{b}_i + A\overline{B} \overline{b}_i + ABb_i = A \oplus B \oplus b_i$$

$$b = \overline{ABb}_i + \overline{AB} \overline{b}_i + \overline{ABb}_i + ABb_i = \overline{AB} + (\overline{A \oplus B})b_i$$

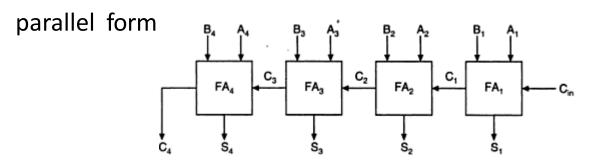

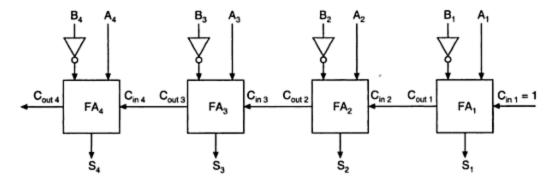

## PARALLEL ADDER AND SUBTRACTOR

A binary parallel adder is a digital circuit that adds two binary numbers in parallel form and produces the arithmetic sum of those numbers in

Fig 9:paralleladder

Fig 10:parallelsubtractor

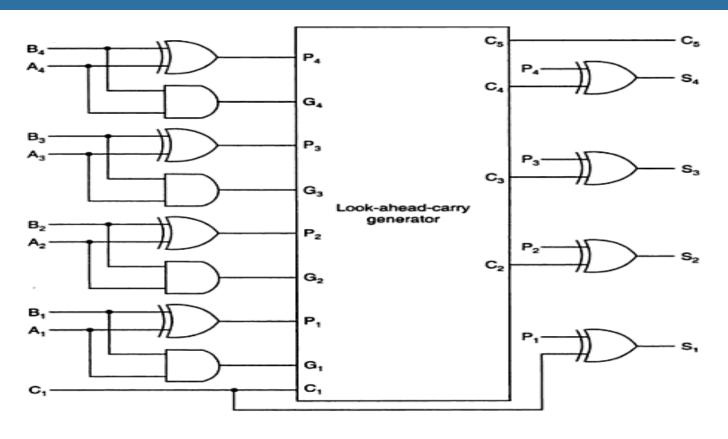

#### **CARRY LOOK-A- HEAD ADDER**

- In parallel-adder, the speed with which an addition can be performed is governed by the time required for the carries to propagate or ripple through all of the stages of the adder.

- The look-ahead carry adder speeds up the process byeliminating this ripple carry delay.

$$S_n = P_n \oplus C_n$$

where  $P_n = A_n \oplus B_n$

$C_{on} = C_{n+1} = G_n + P_n C_n$  where  $G_n = A_n \cdot B_n$

# **CARRY LOOK-A- HEAD ADDER**

Fig:1 blockdiagram

## **BINARY MULTIPLIER**

A binary multiplier is an electronic circuit used in digital electronics, such as a computer, to multiply two binary numbers. It is built using binary adders.

Example: (101 x 011)

Partial products are: 101 >

## **BINARY MULTIPLIER**

- We can also make an  $n \times m$  "block" multiplier and use that to form partial products.

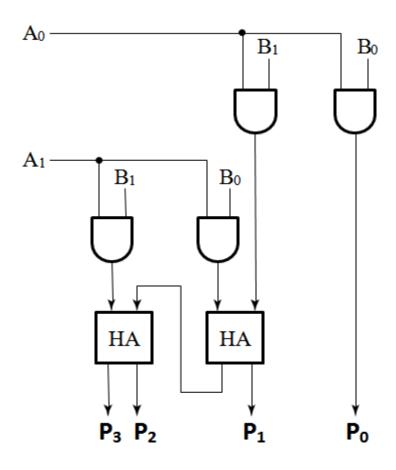

- ➤ Example: 2 × 2 The logic equations for each partial-product binary digit are shownbelow

- ➤ We need to "add" the columns to get the product bits P0,P1, P2, and P3

# **BINARY MULTIPLIER**

Fig 1: 2 x 2 multiplier array

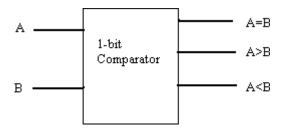

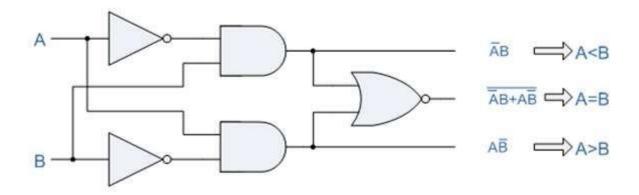

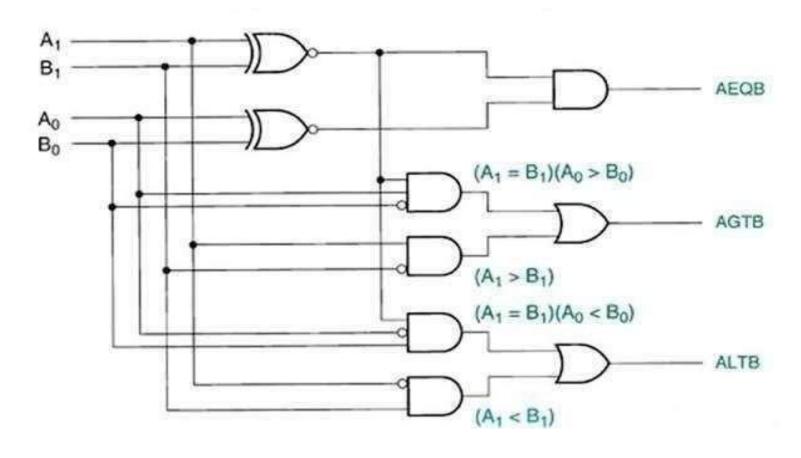

➤ Magnitude comparator takes two numbers as input in binary form and determines whether one number is greater than, less than or equal to the other number.

#### 1-Bit Magnitude Comparator

>A comparator used to compare two bits is called a single bit comparator.

Fig:1 Block diagram

| Inputs |   | Outputs |       |       |  |

|--------|---|---------|-------|-------|--|

| A      | В | A > B   | A = B | A < B |  |

| 0      | 0 | 0       | 1     | 0     |  |

| 0      | 1 | 0       | 0     | 1     |  |

| 1      | 0 | 1       | 0     | 0     |  |

| 1      | 1 | 0       | 1     | 0     |  |

Fig 2:Logic diagram of 1-bit comparator

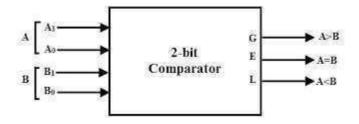

## > 2 Bit magnitude comparator

Fig: 3 Block diagram

| Inputs         |       |                | Outputs        |     |     |                   |

|----------------|-------|----------------|----------------|-----|-----|-------------------|

| $\mathbf{A}_1$ | $A_0$ | B <sub>1</sub> | B <sub>0</sub> | A>B | A=B | A <e< th=""></e<> |

| 0              | 0     | 0              | 0              | 0   | 1   | 0                 |

| 0              | 0     | 0              | 1              | 0   | 0   | 1                 |

| 0              | 0     | 1              | 0              | 0   | 0   | 1                 |

| 0              | 0     | 1              | 1              | 0   | 0   | 1                 |

| 0              | 1     | 0              | 0              | 1   | 0   | 0                 |

| 0              | 1     | 0              | 1              | 0   | 1   | 0                 |

| 0              | 1     | 1              | 0              | 0   | 0   | 1                 |

| 0              | 1     | 1              | 1              | 0   | 0   | 1                 |

| 1              | 0     | 0              | 0              | 1   | 0   | 0                 |

| 1              | 0     | 0              | 1              | 1   | 0   | 0                 |

| 1              | 0     | 1              | 0              | 0   | 1   | 0                 |

| 1              | 0     | 1              | 1              | 0   | 0   | 1                 |

| 1              | 1     | 0              | 0              | 1   | 0   | 0                 |

| 1              | 1     | 0              | 1              | 1   | 0   | 0                 |

| 1              | 1     | 1              | 0              | 1   | 0   | 0                 |

| 1              | 1     | 1              | 1              | 0   | 1   | 0                 |

Fig: 4 Truthtable

Fig 5:Logic diagram of 2-bitcomparator

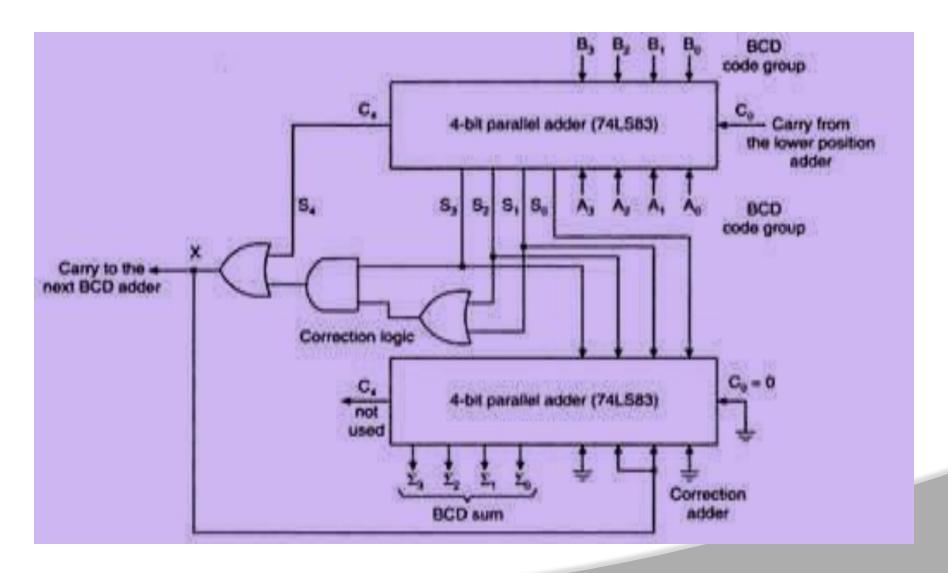

#### **BCD ADDER**

#### **BCD Adder**

- Perform the addition of two decimal digits in BCD, together with an input carry from a previous stage.

- ➤ When the sum is 9 or less, the sum is in proper BCD form and no correction is needed.

- ➤ When the sum of two digits is greater than 9, a correction of 0110 should be added to that sum, to produce the proper BCD result. This will produce a carry to be added to the next decimal position.

# **BCD ADDER**

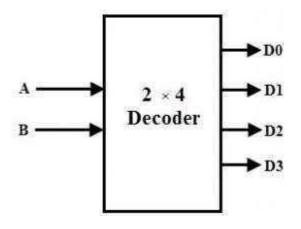

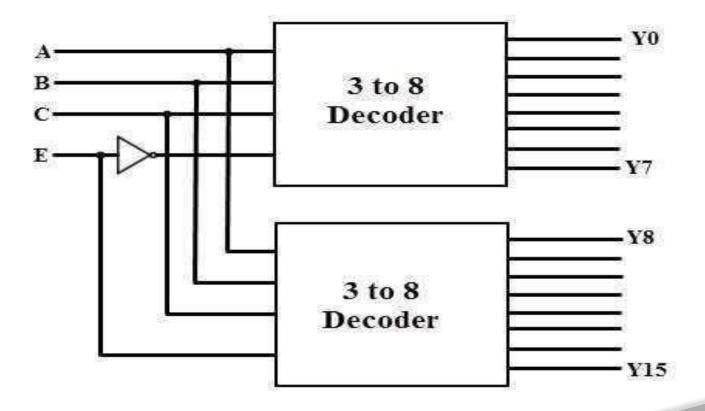

## **DECODER**

- A binary decoder is a combinational logic circuit that converts binary information from the  $\bf n$  coded inputs to a maximum of  $2^n$ unique outputs.

- We have following types of decoders 2x4,3x8,4x16....

#### 2x4 decoder

Fig 1: Blockdiagram

| Inpu | its |    | Ou | tput           |    |

|------|-----|----|----|----------------|----|

| Α    | В   | D. | D, | D <sub>2</sub> | D, |

| 0    | 0   | 1  | 0  | 0              | 0  |

| 0    | 1   | 0  | 1  | 0              | 0  |

| 0    | 1   | 0  | 0  | 1              | 0  |

| 1    | 1   | 0  | 0  | 0              | 1  |

Fig 2:Truth table

# **DECODER**

Higher order decoder implementation using lower order.

Ex:4x16 decoder using 3x8decoders

## **ENCODERS**

- ➤ An Encoder is a combinational circuit that performs the reverse operation of Decoder. It has maximum of 2<sup>n</sup> input lines and 'n' output lines.

- > It will produce a binary code equivalent to the input, which is active High.

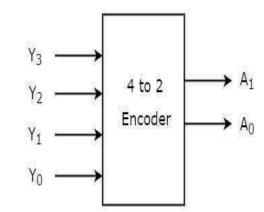

Fig 1:block diagram of 4x2encoder

# **ENCODERS**

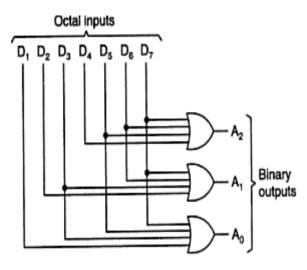

## **Octal to binaryencoder**

| Octal digits   |   | E              |    |                |

|----------------|---|----------------|----|----------------|

|                |   | A <sub>2</sub> | Α, | A <sub>0</sub> |

| Do             | 0 | 0              | 0  | 0              |

| D,             | 1 | 0              | 0  | 1              |

| $D_2$          | 2 | 0              | 1  | 0              |

| $D_3$          | 3 | 0              | 1  | 1              |

| D <sub>4</sub> | 4 | 1              | 0  | 0              |

| $D_5$          | 5 | 1              | 0  | 1              |

| $D_6$          | 6 | 1              | 1  | 0              |

| D <sub>7</sub> | 7 | 1              | 1  | 1              |

Fig 2:Truthtable

Fig 3: Logic diagram

## **ENCODERS**

#### **Priority encoder**

A 4 to 2 priority encoder has four inputs  $Y_3$ ,  $Y_2$ ,  $Y_1$  &  $Y_0$  and two outputs  $A_1$  &  $A_0$ . Here, the input,  $Y_3$  has the highest priority, whereas the input,  $Y_0$  has the lowest priority.

| Inputs     |                |                |    | Outputs               |                       |   |

|------------|----------------|----------------|----|-----------------------|-----------------------|---|

| <b>Y</b> 3 | Y <sub>2</sub> | Y <sub>1</sub> | Υ0 | <b>A</b> <sub>1</sub> | <b>A</b> <sub>0</sub> | v |

| 0          | 0              | 0              | 0  | 0                     | 0                     | 0 |

| 0          | 0              | 0              | 1  | 0                     | 0                     | 1 |

| 0          | 0              | 1              | x  | 0                     | 1                     | 1 |

| 0          | 1              | х              | х  | 1                     | 0                     | 1 |

| 1          | x              | х              | х  | 1                     | 1                     | 1 |

Fig 4:Truthtable

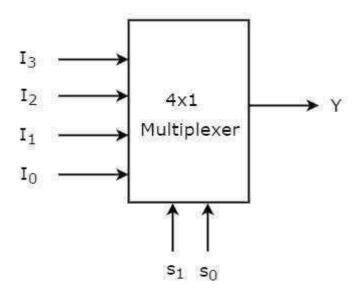

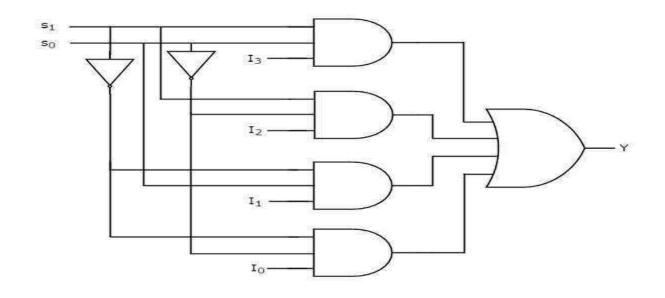

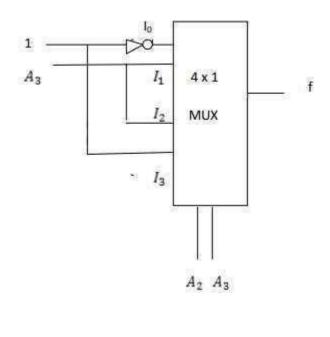

- ➤ Multiplexer is a combinational circuit that has maximum of 2<sup>n</sup> data inputs, 'n' selection lines and single output line. One of these data inputs will be connected to the output based on the values of selection lines.

- ➤ We have different types of multiplexers 2x1,4x1,8x1,16x1,32x1......

Fig 3: Logic diagram

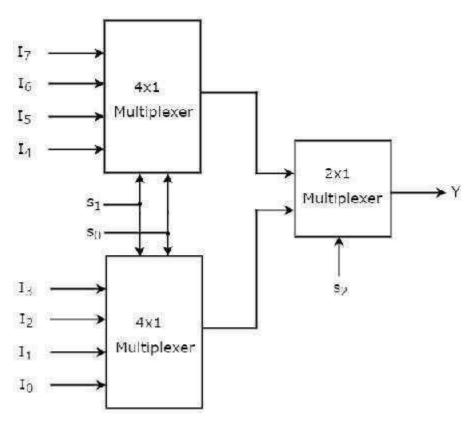

Now let us implement the higher-order Multiplexer using lower-order Multiplexers.

> Ex: 8x1 Multiplexer

Fig 3: 8x1 Multiplexer diagram

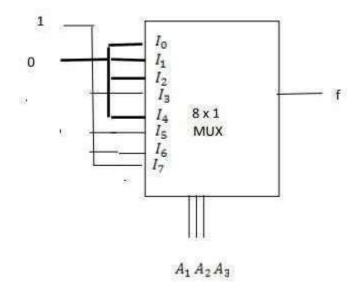

- Implementation of Boolean function usingmultiplexer

- $\triangleright$  f(A1, A2, A3) = Σ(3,5,6,7) implementation using 8x1mux

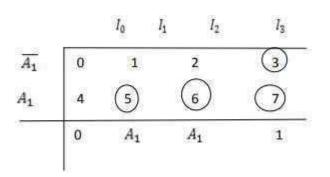

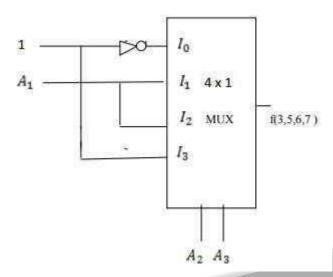

#### $f(A1, A2, A3) = \Sigma(3,5,6,7)$ implementation using 4x1 mux

#### Method:1

| Minterms | $A_1$ | $A_2$ | $A_3$ | f |

|----------|-------|-------|-------|---|

| 0        | 0     | 0     | 0     | 0 |

| 1        | 0     | 0     | 1     | 0 |

| 2        | 0     | 1     | 0     | 0 |

| 3        | 0     | 1     | 1     | 1 |

| 4        | 1     | 0     | 0     | 0 |

| 5        | 1     | 0     | 1     | 1 |

| 6        | 1     | 1     | 0     | 1 |

| 7        | 1     | 1     | 1     | 1 |

#### Method:2

| Minterm | $A_1$ | $A_2$       | $A_3$ | 900 | f                 |       |

|---------|-------|-------------|-------|-----|-------------------|-------|

| 0       | 0     | 0           | 0     | 0   | -                 |       |

| I       | 0     | 0           | Ĩ.    | 0   | f=0               | 10    |

| 2       | 0     | 1           | 0     | 0   | , and the second  |       |

| 3       | 0     | 1           | 1     | 1   | f= A <sub>3</sub> | $I_1$ |

| 4       | 1     | 0           | 0     | 0   | Ö                 |       |

| 5       | 1     | 0           | 1     | 1   | $f = A_3$         | $I_2$ |

| 6       | 1     | o) <b>1</b> | 0     | 1   | X.                |       |

| 7       | 1     | 1           | 10    | 1   | f= 1              | $I_3$ |

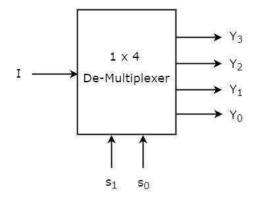

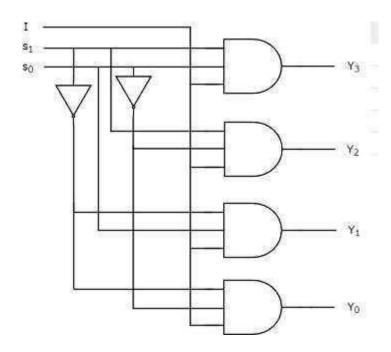

#### **DEMULTIPLEXER**

- A demultiplexer is a device that takes a single input line and routes it to one of several digital output lines.

- A demultiplexer of 2<sup>n</sup> outputs has n select lines, which are used to select which output line to send theinput.

- ➤ We have 1x2,1x4,8x1.... Demultiplexers.

# **DEMULTIPLEXER**

#### **Boolean functions for each outputas**

$$Y_3 = s_1 s_0 I$$

$$Y_2=s_1s_0{'}I$$

$$Y_1 = s_1{}'s_0I$$

$$Y_0={s_1}'{s_0}'I$$

Fig:3 Logicdiagram

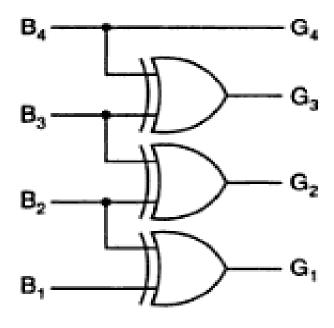

## **CODE CONVERTERS**

A code converter is a logic circuit whose inputs are bit patterns representing numbers (or character) in one code and whose outputs are the corresponding representation in a different code.

#### Design of a 4-bit binary to gray codeconverter

|     | 4-bit I | binary         |    |   |    | 4-bit ( | Gray           |     |

|-----|---------|----------------|----|---|----|---------|----------------|-----|

| B., | Ba      | B <sub>2</sub> | В, | _ | G, | Ga      | G <sub>2</sub> | G,  |

| 0   | 0       | 0              | 0  |   | 0  | 0       | 0              | O   |

| 0   | 0       | 0              | 1  |   | 0  | 0       | 0              | 1   |

| 0   | 0       | 7              | 0  |   | O  | 0       | -1             | -1  |

| 0   | 0       | 1              | 1  |   | 0  | 0       | 1              | 0   |

| 0   | 1       | 0              | 0  |   | 0  | 1       | -1             | 0   |

| 0   | 1       | 0              | 1  |   | O  | 1       | 1              | 1   |

| 0   | 1       | 7              | 0  |   | О  | 1       | O              | 1   |

| 0   | 1       | 1              | 1  |   | O  | 1       | 0              | 0   |

| 1   | 0       | 0              | 0  |   | 1  | 1       | 0              | 0   |

| 1   | 0       | 0              | 1  |   | 1  | 1       | 0              | -18 |

| 1   | 0       | 1              | 0  |   | 1  | 1       | 1              | 1   |

| -1  | 0       | 1              | 1  |   | 1  | -1      | 1              | 0   |

| 1   | 1       | O              | 0  |   | 1  | •       | 1              | 0   |

| 1   | 1       | 0              | 1  |   | 1  | 0       | 1              | 75  |

| 1   | 1       | 1              | 0  |   | 1  | 0       | 0              | 1   |

| _1_ | 1       | 1              |    |   | 1  |         | <u> </u>       |     |

Fig:1 Truthtable

# **CODE CONVERTERS**

Fig: 2 Logicdiagram

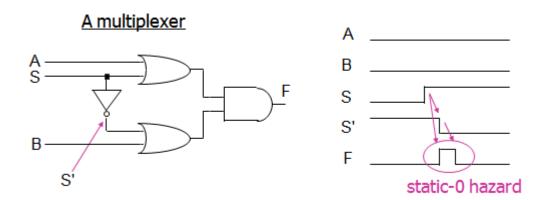

#### **HAZARDS AND GLITCHES**

- > glitch: unwanted output

- > A circuit with the potential for a glitch has a **hazard**.

- > Glitches occur when different pathways have different delays

- Causes circuit noise

- Dangerous if logic makes a decision while output is unstable

- Solutions

- Design hazard-free circuit

- Difficult when logic is multilevel

- Wait until signals are stable

#### **TYPES OF HAZARDS**

- Static 1-hazard

- Output should stay logic 1

- Gate delays cause brief glitch to logic 0

- Static 0-hazard

- Output should stay logic 0

- Gate delays cause brief glitch to logic 1

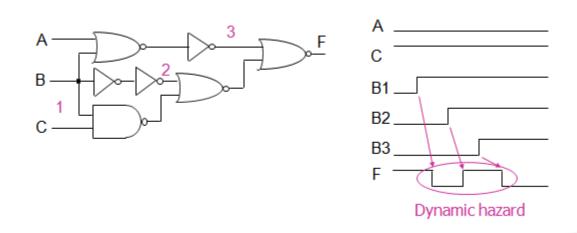

- Dynamic hazards

- Output should toggle cleanly

- Gate delays cause multiple transitions

## **STATIC HAZARDS**

- Often occurs when a literal and its complement momentarily assume the same value

- Through different paths with different delays

- Causes an (ideally) static output to glitch

## **DYNAMIC HAZARDS**

- Often occurs when a literal assumes multiple values

- Through different paths with different delays

- Causes an output to toggle multiple times

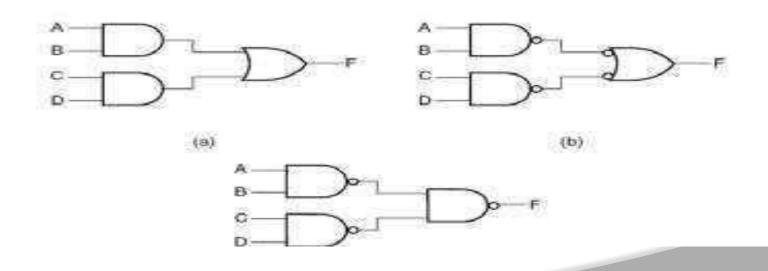

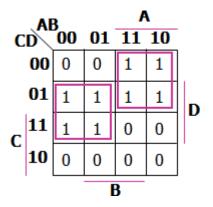

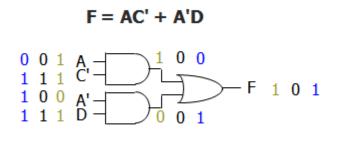

#### **ELIMINATING STATIC HAZARDS**

- Key idea: Glitches happen when a changing input spans separate Kmap encirclements

- Example: 1101 to 0101 change can cause a static-1 glitch

■ ABCD: 1101 → 0101

## **ELIMINATING STATIC HAZARDS**

- Solution: Add redundant K-map encirclements

- Ensure that all single-bit changes are covered by same block

- First eliminate static-1 hazards: Use SOP form

- If need to eliminate static-0 hazards, use POS form

- > Technique only works for 2-level logic

## **ELIMINATING STATIC HAZARDS**

- We can eliminate static hazards in 2-level logic for single-bit changes

- Eliminating static hazards also eliminates dynamic hazards

- Hazards are a difficult problem

- Multiple-bit changes in 2-level logic are hard

- Static hazards in multilevel logic are harder

- Dynamic hazards in multilevel logic are harder yet

# MODULE-V SEQUENTIAL CIRCUITS FUNDAMENTALS

Basic Architectural Distinctions between Combinational and Sequential circuits, SR Latch, Flip Flops: SR, JK, JK Master Slave, D and T Type Flip Flops, Excitation Table of all Flip Flops, Timing and Triggering Consideration, Conversion from one type of Flip-Flop to another.

Registers and Counters: Shift Registers – Left, Right and Bidirectional Shift Registers, Applications of Shift Registers - Design and Operation of Ring and Twisted Ring Counter, Operation of Asynchronous and Synchronous Counters

#### **CONTENTS**

- Combinational and Sequential circuits,

- ➤ SR Latch, Flip Flops: SR, JK, JK Master Slave,

- > D and T Type Flip Flops, Excitation Table of all Flip Flops,

- > Timing and Triggering Consideration,

- ➤ Shift Registers Left, Right and Bidirectional Shift Registers, Operation of Asynchronous and

- ➤ Synchronous Counters.

## **SEQUENTIAL CIRCUITS**

- Gated latch is a basic latch that includesinput gating and a control signal.

- The latch retains its existing state when the control input is equal to 0.

- ➤ Its state may be changed when the control signal is equal to 1.In our discussion we referred to the control input as the clock.

- We consider two types of gated latches:

- Gated SR latch uses the S and R inputs to set the latch to 1

- Gated D latch uses the Dinput to force the latch into a state that has the same logic value as the Dinput.

## **SEQUENTIAL CIRCUITS**

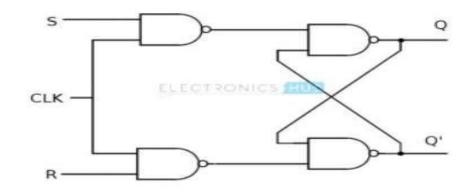

- Basic latch is a feedback connection of two NOR gates or two NAND gates.

- > It can store one bit ofinformation.

- ➤ It can be set to 1 using the S input andreset to 0 using the Rinput.

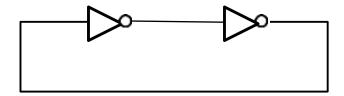

- > A feedback loop with even number of inverters

- $\triangleright$  If A = 0, B = 1 or when A = 1, B =0

- This circuit is not useful due to the lack of a mechanism for changing its state

# **RS LATCH:**

# **D LATCH:**

#### **FLIP FLOPS:**

- A flip-flop is a storage element based onthe gated latch principle.

- It can have its output state changed onlyon the edge of the controlling clock signal.

#### **Types Of Flip-flops:**

- SR flip-flop (Set, Reset)

- T flip-flop (Toggle)

- D flip-flop (Delay)

- > JK flip-flop

#### **FLIP FLOPS:**

- ➤ Edge-triggered flip-flop is affected only by the input values present when the active edge of the clock occurs

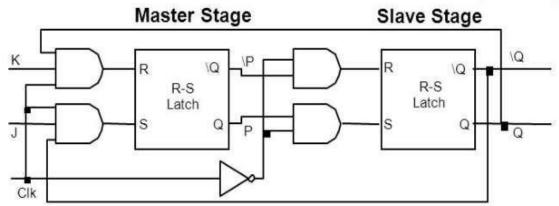

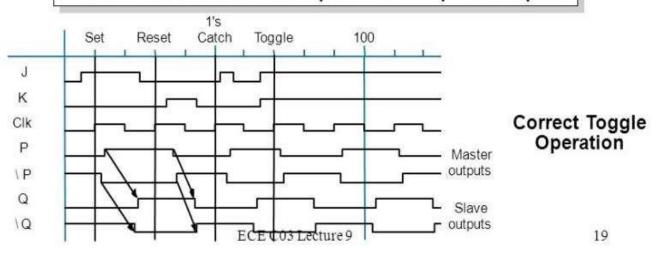

- ➤ Master-slave flip-flop is built with twogated latches

- > The master stage is active during half of the clock cycle, and the slave stage is active during the other half.

- > The output value of the flip-flop changes on the edge of the clock that activates the transfer into the slave stage

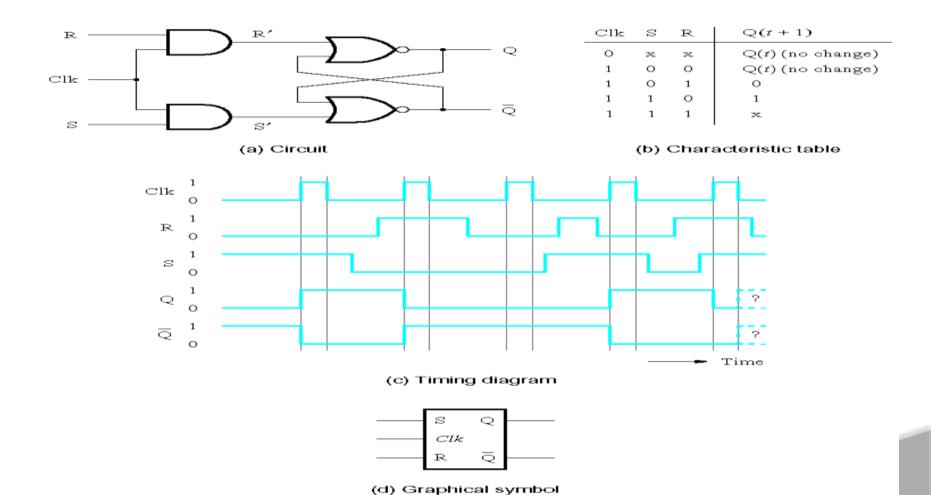

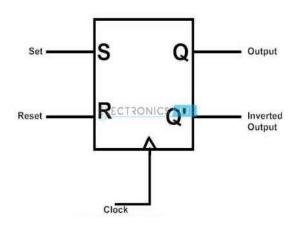

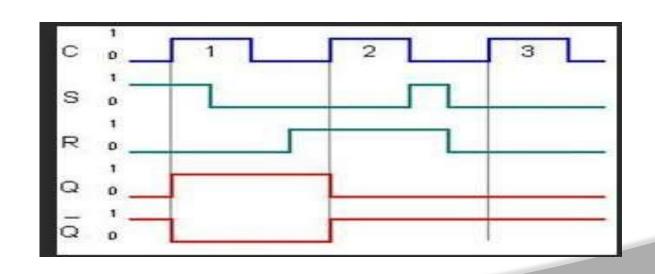

# **SR FLIP FLOP**

| ļ        | INPUTS |   | OUTPU<br>T   | STATE         |

|----------|--------|---|--------------|---------------|

| CLK      | S      | R | Q            |               |

| X        | 0      | 0 | No<br>Change | Previous      |

| <b>A</b> | 0      | 1 | 0            | Reset         |

| •        | 1      | 0 | 1            | Set           |

| <b>†</b> | 1      | 1 | =            | Forbidde<br>n |

# SR FLIPFLOP EXCITATION TABLE & TIMING DIAGRAM

|     |        | SR FLIP-F | LOP   |        |     |

|-----|--------|-----------|-------|--------|-----|

| ı   | Q(t)   | Q(t+1)    | S     | R      |     |

|     | 0      | 0         | 0     | ×      |     |

|     | 0      | 1         | 1     | 0      |     |

|     | 1      | 0         | 0     | 1      |     |

|     | 1      | 1         | ×     | 0      |     |

| EXC | ITATIO | N TABLE C | OF SR | FLIP-F | LOP |

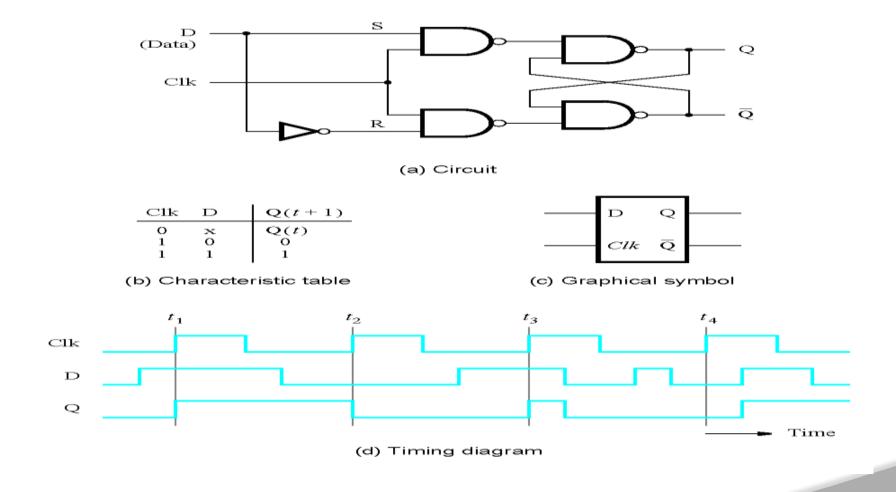

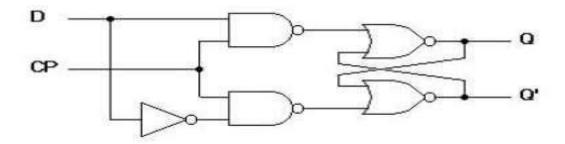

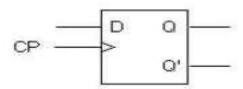

# **D FLIPFLOP**

(a) Logic diagram with NAND gates

(b) Graphical symbol

| Q D | Q(t+1) |

|-----|--------|

| 0 0 | 0      |

| 0 1 | 1      |

| 10  | 0      |

| 1 1 | 1      |

(c) Transition table

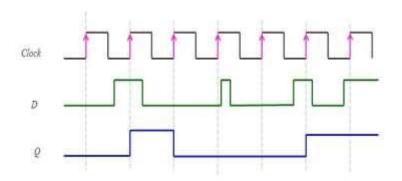

# **D FLIPFLOP EXCITATION TABLE & TIMING DIAGRAM:**

| Present       | Next state  | D |

|---------------|-------------|---|

| state $(Q_n)$ | $(Q_{n+1})$ |   |

| 0             | 0           | 0 |

| 0             | 1           | 1 |

| 1             | 0           | 0 |

| 1             | 1           | 1 |

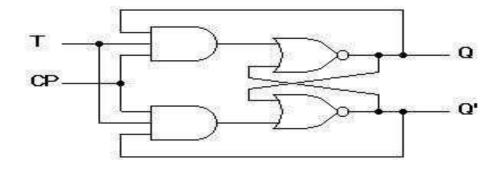

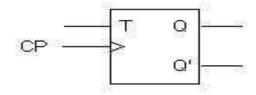

# T FLIPFLOP:

#### (a) Logic diagram

#### (b) Graphical symbol

| QT  | Q(t+1) |

|-----|--------|

| 0 0 | 0      |

| 0 1 | 1      |

| 1 0 | 1      |

| 1-1 | 0      |

#### (c) Transition table

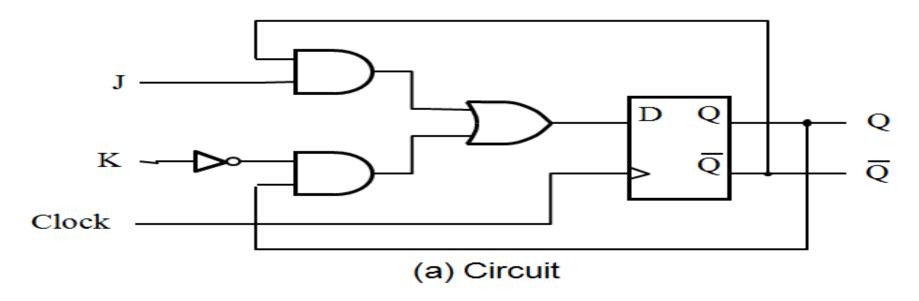

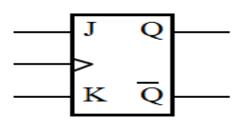

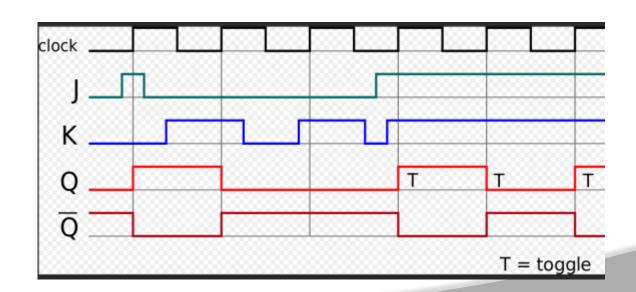

# **JK FLIPFLOP**

| JK  | Q(t+1)            |

|-----|-------------------|

| 0 0 | Q(t)              |

| 0 1 | О                 |

| 1 0 | 1                 |

| 1 1 | $\overline{Q}(t)$ |

(b) Characteristic table (c) Graphical symbol

# JK FLIPFLOP

| Q Output         |               | Inputs         |    |

|------------------|---------------|----------------|----|

| Present<br>State | Next<br>State | J <sub>n</sub> | Kn |

| 0                | 0             | 0              | х  |

| 0                | 1             | 1              | х  |

| 1                | 0             | х              | 1  |

| 1                | 1             | X              | 0  |

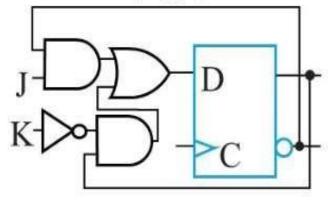

### **MASTER SLAVE JK FLIPFLOP**

Sample inputs while clock high

Sample inputs while clock low

### Uses time to break feedback path from outputs to inputs!

### **CONVERSION OF FLIPFLOP:**

- Draw the block diagram of the target flip flop from the given problem.

- 2. Write truth table for the target flip-flop.

- Write excitation table for the available flipflop.

- Draw k-map for target flip-flop.

- 5. Draw the block diagram.

# JK TO SR FLIPFLOP:

### Characteristic Table —

| S | R | Q(t+1) | Operation |                   |

|---|---|--------|-----------|-------------------|

| 0 | 0 | Q(t)   | No change |                   |

| 0 | 1 | 0      | Reset     | $\longrightarrow$ |

| 1 | 0 | 1      | Set       |                   |

| 1 | 1 | ?      | Undefined |                   |

Characteristic Equation

$$Q(t+1) = J \overline{Q} + \overline{K} Q$$

Excitation Table

| Q(t) | Q(t+1)     | JК  | Operation |

|------|------------|-----|-----------|

| 0    | 0          | 0 X | No change |

| 0    | 1          | 1 X | Set       |

| 1    | ange<br>() | X 1 | Reset     |

| 1    | 1          | X 0 | No Change |

| <b>→</b> J | K | Q(t+1)            | Operation           |

|------------|---|-------------------|---------------------|

| 0          | 0 | Q(t)              | No change           |

| 0          | 1 | 0                 | Reset               |

| 1          | 0 | 1                 | Set                 |

| 1          | 1 | $\overline{Q}(t)$ | Complement (Toggle) |

Louis and Promoder Station Emdementals

# **CHARACTERISTIC EQUATION:**

| Flip-flop | Characteristic Equation    |

|-----------|----------------------------|

| D         | Q(t+1) = D                 |

| T         | $Q(t+1) = T \oplus Q(t)$   |

| SR        | Q(t+1) = S + R' Q(t)       |

| JK        | Q(t+1) = J Q(t)' + K' Q(t) |

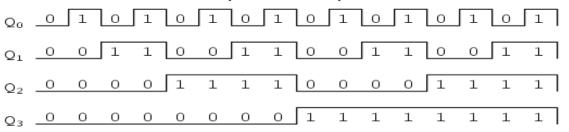

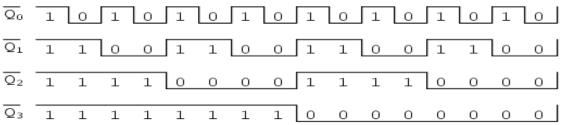

### **COUNTERS:**

- > Counters are a specific type of sequential circuit.

- ➤ Like registers, the state, or the flip-flop values themselves, serves as the "output."

- > The output value increases by one on each clock cycle.

- > After the largest value, theoutput "wraps around" back to 0.

- > Counters can act as simple clocks to keep track of "time."

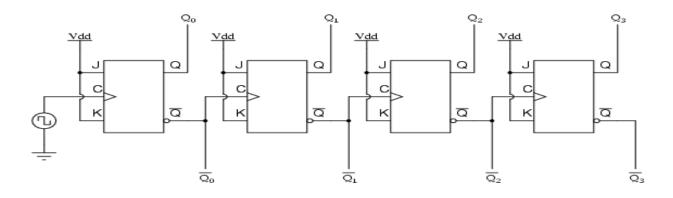

## **ASYNCHRONOUS COUNTERS:**

Asynchronous counter created from two JK flip-flops An asynchronous (ripple) counter is a single d-type flip-flop, with its J (data) input fed from its own inverted output. This circuit can store one bit, and hence can count from zero to one before it overflows (starts over from 0).

# **ASYNCHRONOUS UP/DOWN COUNTERS:**

#### "Up" count sequence

#### "Down" count sequence

### **SYNCHRONOUS COUNTERS:**

The counters which use clock signal to change their transition are called "synchronous counters". this means the synchronous counters depends on their clock input to change state values. in synchronous counters, all flip flops are connected to the same clock signal and all flip flops will trigger at the same time.

### **Types of Counters:**

- 4 bit Binary synchronous UP& DOWN counter

- 4 bit Binary synchronous UP / DOWN counter

- BCD counters

- Ring counters

- > Johnson counters etc.

# **JOHNSON COUNTERS:**

| Jo    | hnso | n counter |    |    |  |

|-------|------|-----------|----|----|--|

| State | Q0   | Q1        | Q2 | Q3 |  |

| 0     | 0    | 0         | 0  | 0  |  |

| 1     | 1    | 0         | 0  | 0  |  |

| 2     | 1    | 1         | 0  | 0  |  |

| 3     | 1    | 1         | 1  | 0  |  |

| 4     | 1    | 1         | 1  | 1  |  |

| 5     | 0    | 1         | 1  | 1  |  |

| 6     | 0    | 0         | 1  | 1  |  |

| 7     | 0    | 0         | 0  | 1  |  |

| 0     | 0    | 0         | 0  | 0  |  |

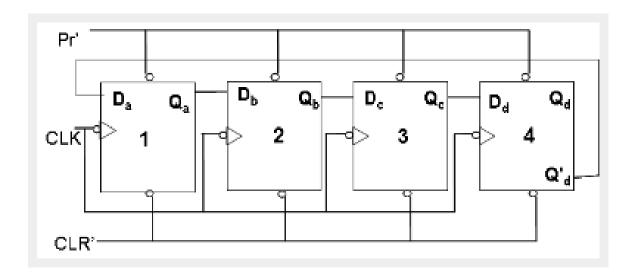

### **SHIFT REGISTER:**

Shift registers, like counters, are a form of sequential logic. Sequential logic, unlike Combinational Logic is not only affected by the present inputs, but also, by the prior history. In other words, sequential logic remembers past events. Basic shift registers are classified by structure according to the

### **Types of Shift Registers:**

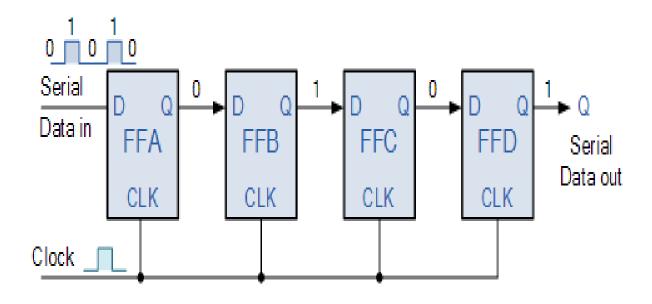

- Serial-in/serial-out

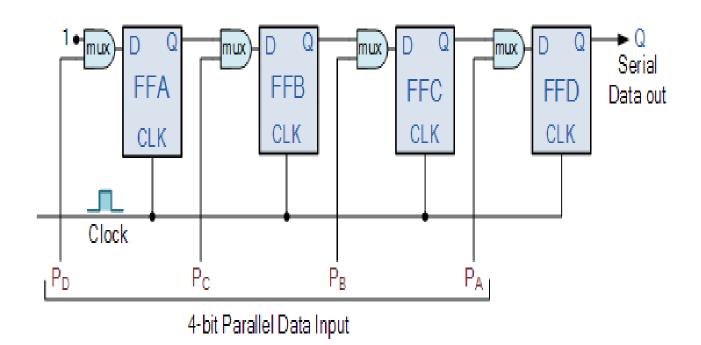

- Parallel-in/serial-out

- Serial-in/parallel-out

- Universal parallel-in/parallel-out

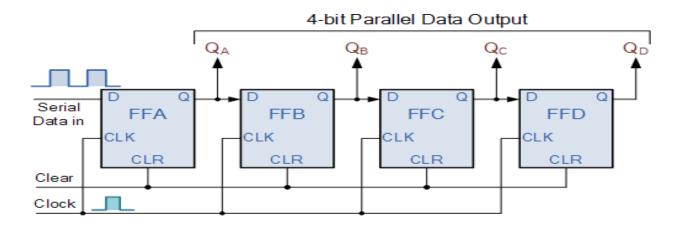

# **SERIAL IN TO PARALLEL OUTPUT:**

| Clock Pulse No | QA | QB | QC | QD |

|----------------|----|----|----|----|

| 0              | 0  | 0  | 0  | 0  |

| 1              | 1  | 0  | 0  | 0  |

| 2              | 0  | 1  | 0  | 0  |

| 3              | 0  | 0  | 1  | 0  |

| 4              | 0  | 0  | 0  | 1  |

| 5              | 0  | 0  | 0  | 0  |

# **SERIAL IN TO SERIAL OUTPUT:**

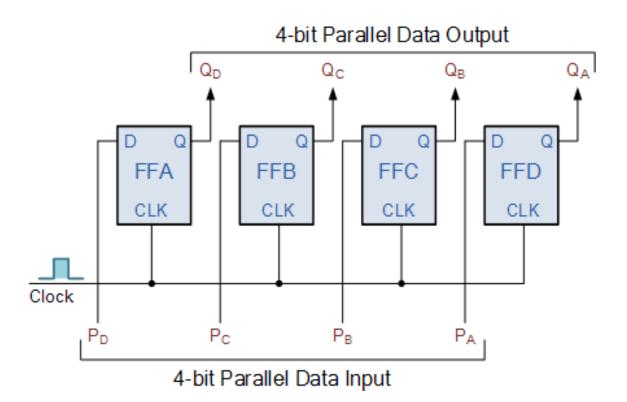

# **PARALLEL IN TO SERIAL OUTPUT:**

# **PARALLEL IN TO PARALLEL OUTPUT:**