## DIGITAL ELECTRONICS (AECB03) III SEMESTER ELECTRICAL AND ELECTRONICS ENGINEERING

PREPARED BY V.BINDU SREE J.SRAVANA

## Unit-I FUNDAMENTALS OF DIGITAL SYSTEMS AND LOGIC FAMILIES

**>**Binary number system.

A method of representing **numbers** that has 2 as its base and uses only the digits 0 and 1.

Ex:10100010

### Decimal number system

A number system that uses a notation in which each number is expressed in base 10 by using one of the first nine integers or 0 in each place and letting each place value be a power of 10

Numbers:0,1,2,3,4,5,6,7,8,9

### >Octal number system

The octal numbering system uses the numerals 0-1-2-3-4-5-6-7.

### Hexa decimal number system

The hexadecimal numeral system, often shortened to "hex", is a numeral system made up of 16 symbols (base 16) they are 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E.

### **Binary to Decimal Conversion:**

It is by the positional weights method . In this method, each binary digit of the no. is multiplied by its position weight . The product terms are added to obtain the decimal no

Example:

$$101011_{2} \implies 1 x 2^{0} = 1$$

$$1 x 2^{1} = 2$$

$$0 x 2^{2} = 0$$

$$1 x 2^{3} = 8$$

$$0 x 2^{4} = 0$$

$$1 x 2^{5} = 32$$

$$43_{10}$$

### **Binary to Octal conversion:**

Starting from the binary pt. make groups of 3 bits each, on either side of the binary pt, & replace each 3 bit binary group by the equivalent octaldigit.

$$1011010111_2 = ?_8$$

Example:

1 011 010 111  $\downarrow \qquad \downarrow \qquad \downarrow \qquad \downarrow$  1 3 2 7

$1011010111_2 = 1327_8$

#### **Binary to Hexadecimal conversion:**

For this make groups of 4 bits each , on either side of the binary pt & replace each 4 bit group by the equivalent hexadecimal digit.

Example:

$1010111011_{2} = ?_{16}$   $10 \ 1011 \ 1011$   $2 \ B \ B$   $1010111011_{2} = 2BB_{16}$

### **Decimal to Binary conversion:**

Technique

> Divide by two, keep track of the remainder

First remainder is bit 0 (LSB, least-significant bit)

$$\sum \mathbf{S}(125_{10} = ?_2) = 2 \boxed{125} \\ 2 \boxed{62} \\ 1 \\ 2 \boxed{31} \\ 0 \\ 2 \boxed{15} \\ 1 \\ 2 \boxed{7} \\ 1 \\ 2 \boxed{3} \\ 1 \\ 2 \boxed{1} \\ 1 \\ 0 \\ 1 \end{bmatrix}$$

$125_{10} = 1111101_2$

# EDUCATION FOR LIBER

### **Decimal to Octal Conversion:**

- To convert a mixed decimal no to a mixed octal no. convert the integer and fraction parts separately.

- •To convert decimal integer no. to octal, successively divide the given no by 8 till the quotient is 0. The last remainder is the MSD

- The remainder read upwards give the equivalent octal integer no.

- •To convert the given decimal fraction to octal, successively multiply the decimal fraction & the subsequent decimal fractions by 8 till the product is 0 or till the required accuracy is the MSD. The integers to the left of the octal pt read downwards give the octal fraction.

**Example:**

# EU PHION FOR LIGHT

### **Decimal to Hexadecimal conversion:**

- •It is successively divide the given decimal no. by 16 till the quotient is zero. The last remainder is the MSB. The remainder read from bottom to top gives the equivalent hexadecimal integer.

- •To convert a decimal fraction to hexadecimal successively multiply the given decimal fraction & subsequent decimal fractions by 16, till the product is zero. Or till the required accuracy is obtained and collect all the integers to the left of decimal pt. The first integer is MSB & the integer read from top to bottom .

#### Example:

$$1234_{10} = ?_{16}$$

$$16 | 1234 \\ 16 | 77 2 \\ 16 | 4 13 = D \\ 0 4$$

$1234_{10} = 4D2_{16}$

### **Octal to binary Conversion:**

Convert each octal digit to a 3-bit equivalent binary representation

$705_8 = ?_2$   $7 \quad 0 \quad 5$   $\downarrow \quad \downarrow \quad \downarrow$  $111 \quad 000 \quad 101$

$705_8 = 111000101_2$

# FOR LIARE NO

### **Octal to decimal Conversion:**

Multiply each digit in the octal no by the weight of its position & add all the product terms Decimal value of the octal no.

$$724_8 \implies 4 \times 8^0 = 4$$

$$2 \times 8^1 = 16$$

$$7 \times 8^2 = 448$$

$$468_{10}$$

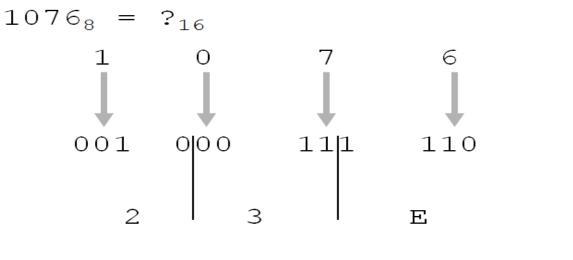

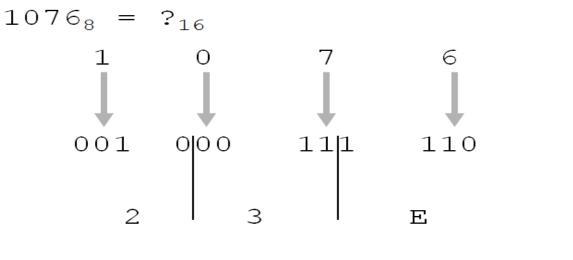

### **Octal to hexadecimal conversion**:

The simplest way is to first convert the given octal no. to binary & then the binary no. to hexadecimal.

$1076_8 = 23E_{16}$

### **Octal to hexadecimal conversion**:

The simplest way is to first convert the given octal no. to binary & then the binary no. to hexadecimal.

$1076_8 = 23E_{16}$

### Hexa decimal to binary Conversion:

Convert each hexadecimal digit to a 4-bit equivalent binary representation

$10AF_{16} = ?_2$   $1 \qquad 0 \qquad A \qquad F$   $\downarrow \qquad \downarrow \qquad \downarrow \qquad \downarrow$  $0001 \ 0000 \ 1010 \ 1111$

$10AF_{16} = 0001000010101111_2$

# EDUCATION FOR LIBER

### Hexa decimal to decimal Conversion:

Convert each hexadecimal digit to a 4-bit equivalent binary representation

$$ABC_{16} \implies C \times 16^{0} = 12 \times 1 = 12$$

B \times 16^{1} = 11 \times 16 = 176

A \times 16^{2} = 10 \times 256 = 2560

2748\_{10}

### Hexa decimal to octal Conversion:

Use binary as an intermediary  $1FOC_{16} = ?_8$   $1FOC_{16} = ?_8$  0|001| 111|1 00|00 1|1001|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|100| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10| 1|10

$1FOC_{16} = 17414_8$

### **Binary Addition:**

Rules: 0+0=0 0+1=1 1+0=1 1+1=10 i.e, 0 with a carry of 1.

### **Binary Subtraction:**

Rules: 0-0=0 1-1=0 1-0=1 0-1=1 with a borrow of 1

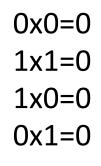

### **Binary multiplication:**

**Rules:**

### **Binary Division:**

### 1's compliment of n number:

It is obtained by simply complimenting each bit of the numbers that is all 1's to 0's and all 0's to 1's Example: 1's complement of 1101001 is 0010110

### 2's compliment of n number:

It is obtained by simply complimenting each bit of the numbers that is all 1's to 0's and all 0's to 1's and add 1 to the value

Example: 2's complement of 1101001 is 0010110

+1= 0010111

9's & 10's Complements:

It is the Subtraction of decimal number can be accomplished by the 9's & 10's compliment methods similar to the 1's & 2's compliment methods of binary. The 9's compliment of a decimal number is obtained by subtracting each digit of that decimal number from 9. The 10's compliment of a decimal number is obtained by adding a 1 to its 9's compliment.

### 1's compliment arithmetic:

In1's complement subtraction, add the 1's complement of the subtrahend to the minuend. If there is a carryout, bring the carry around & add it to the LSB called the end around carry. Look at the sign bit (MSB). If this is a 0, the result is positive & is in true binary. If the MSB is a 1 ( carry or no carry ), the result is negative & is in its is complement form .Take its 1's complement to get the magnitude in binary.

### 2's compliment arithmetic:

The 2's complement system is used to represent negative numbers using modulus arithmetic. The word length of a computer is fixed i.e, if a 4 bit number is added to another 4 bit number the result will be only of 4 bits. Carry if any , from the fourth bit will overflow called the Modulus arithmetic.

# Representation of signed numbers binary arithmetic in computers:

Two ways of representing signed numbers is Sign Magnitude form and Complemented form there are two complimented forms i.e. 1's compliment form and 2's compliment form

#### Weighted Codes:

The weighted codes are those that obey the position weighting principle, which states that the position of each number represent a specific weight. In these codes each decimal digit is represented by a group of four bits.

In weighted codes, each digit is assigned a specific weight according to its position. For example, in 8421/BCD code, 1001 the weights of 1, 1, 0, 1 (from left to right) are 8, 4, 2 and 1 respectively.

Examples:8421,2421 are all weighted codes.

#### Non-weighted codes:

The non-weighted codes are not positionally weighted . In other words codes that are not assigned with any weight to each digit position.

Examples: Excess-3(XS-3) and Gray Codes.

### **BCD Addition:**

It is individually adding the corresponding digits of the decimal numbers expressed in 4 bit binary groups starting from the LSD .

If there is no carry & the sum term is not an illegal code , no correction is needed.

If there is a carry out of one group to the next group or if the sum term is an illegal code then  $6_{10}$  (0110) is added to the sum term of that group & the resulting carry is added to the next group.

### **BCD Subtraction:**

Performed by subtracting the digits of each 4 bit group of the subtrahend the digits from the corresponding 4- bit group of the minuend in binary starting from the LSD . if there is no borrow from the next group , then  $6_{10}$  (0110) is subtracted from the difference term of this group.

**Error – Detecting codes:**

When binary data is transmitted & processed, it is susceptible to noise that can alter or distort its contents. The 1's may get changed to 0's & 0's may get changed to 1's because digital systems must be accurate to the digit, error can pose a problem. Several schemes have been devised to detect the occurrence of a single bit error in a binary word, so that whenever such an error occurs the concerned binary word can be corrected & retransmitted.

- When we talk about digital systems, be it a digital computer or a digital communication set-up, the issue of error detection and correction is of great practical significance.

- Errors creep into the bit stream owing to noise or other impairments during the course of its transmission from the transmitter to the receiver.

- While the addition of redundant bits helps in achieving the goal of making transmission of information from one place to another error free or reliable, it also makes it inefficient.

Some Common Error Detecting and CorrectingCodes

- Parity Code

- Hamming Code

### Parity Code:

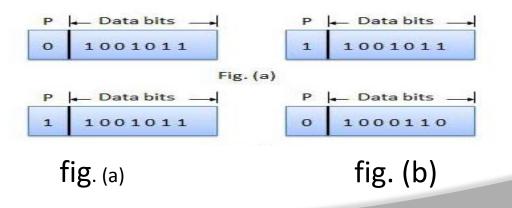

A parity bit is an extra bit added to a string of data bits in order to detect any error that might have crept into it while it was being stored or processed and moved from one place to another in a digital system.

- The parity bit can be set to 0 and 1 depending on the type of the parity required.

- $\succ$  For even parity, this bit is set to 1 or 0 such that the no.

- of "1 bits" in the entire word is even. Shown in fig. (a).

- $\succ$  For odd parity, this bit is set to 1 or 0 such that the no.

- of "1 bits" in the entire word is odd. Shown in fig. (b).

#### Hamming Code:

- An increase in the number of redundant bits added to message bits can enhance the capability of the code to detect and correct errors.

- If sufficient number of redundant bits arranged such that different error bits produce different error results, then it should be possible not only to detect the error bit but also to identify its location.

- In fact, the addition of redundant bits alters the 'distance' code parameter.

- For example, the addition of single-bit parity results in a code with a Hamming distance of at least 2.

- The smallest Hamming distance in the case of a threefold repetition code would be 3.

- Hamming noticed that an increase in distance enhanced the code's ability to detect and correct errors.

- Hamming's code was therefore an attempt at increasing the Hamming distance and at the same time having as high an information throughput rate as possible.

- ➢ The generalized form of code is  $P_1P_2D_1P_3D_2D_3D_4P_4D_5D_6D_7D_8D_9D_{10}D_{11}P_{5....}$ , where P and D respectively represent parity and data bits.

- We can see from the generalized form of the code that all bit positions that are powers of 2 (positions 1, 2, 4, 8, 16 ...) are used as parity bits.All other bit positions (positions 3, 5, 6, 7, 9, 10, 11 ...) are used to encode data.

- Each parity bit is allotted a group of bits from the data bits in the code word, and the value of the parity bit (0 or 1) is used to give it certain parity.

So on. Groups are formed by first checking bits and then alternately skipping and checking bits following the parity bit. Here, is the position of the parity bit; 1 for P<sub>1</sub>, 2 for P<sub>2</sub>, 4 for P<sub>3</sub>, 8 for P<sub>4</sub> and so on.

≻Now, the position of  $P_3$  is at number 4. In order to form the group, we check the first three bits *N*-1=3 and then follow it up by alternately skipping and checking four bits (*N*=4).

- The Hamming code is capable of correcting single-bit errors on messages of any length.

- Although the Hamming code can detect two-bit errors, it cannot give the error locations.

- The number of parity bits required to be transmitted along with the message, however, depends upon the message length.  $(2^n - n) > m$

- The number of parity bits n required to encode m message bits is the smallest integer that satisfies the condition

- The code word sequence for this code is written as  $P_1P_2D_1P_3D_2D_3D_4$ , with  $P_1$ ,  $P_2$  and  $P_3$  being the parity bits and  $D_1$ ,  $D_2$ ,  $D_3$  and  $D_4$  being the data bits.

- Generation of Hamming Code:

|                                 | $P_1$ | $P_2$ | $D_1$ | $P_3$ | $D_2$ | $D_3$ | $D_4$ |

|---------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Data bits (without parity)      |       |       | 0     |       | 1     | 1     | 0     |

| Data bits with parity bit $P_1$ | 1     |       | 0     |       | 1     |       | 0     |

| Data bits with parity bit $P_2$ |       | 1     | 0     |       |       | 1     | 0     |

| Data bits with parity bit $P_3$ |       |       |       | 0     | 1     | 1     | 0     |

| Data bits with parity           | 1     | 1     | 0     | 0     | 1     | 1     | 0     |

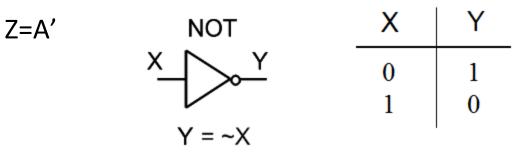

- Binary

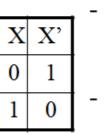

- > A1a: X=0 if X=1

- > A1b: X=1 if X=0

- Complement

- > aka invert, NOT

- > A2a: if X=0, X'=1

- A2b: if X=1, X'=0

- The tick mark ' means complement, invert, or NOT

Other symbolfor \_\_\_\_\_

- complement:  $X' = \overline{X}$

- AND operation

- > A3a:0•0=0

- > A4a:1•1=1

- > A5a:0•1=1•0=0

- The dot means AND

- Other symbol forAND:

X•Y=XY (nosymbol)

- OR Operation

- > A3b:1+1=1

- > A4b:0+0=0

- > A5b: 1+0=0+1=1

- The plus + means OR

| Х | Y | X•Y |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

| Х | Y | X+Y |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

- Variable: Variables are the different symbols in a Boolean expression

- Literal: Each occurrence of a variable or its complement is called a literal

# $\overline{A} + A.B + A.\overline{C} + \overline{A}.B.C$

• **Term**: A term is the expression formed by literals and operations at one level

#### OR operation

- IdentityElements

- > a:X+0=X

- > b:X•1=X

- Commutativity

- > a:X+Y=Y+X

- b:X•Y=Y•X

- Complements

- > a:X+X'=1

- > b:X•X'=0

| Х | Υ | X+0 | X+Y | Y+X | X' | X+X′ |

|---|---|-----|-----|-----|----|------|

| 0 | 0 | 0   | 0   | 0   | 1  | 1    |

| 0 | 1 | 0   | 1   | 1   | 1  | 1    |

| 1 | 0 | 1   | 1   | 1   | 0  | 1    |

| 1 | 1 | 1   | 1   | 1   | 0  | 1    |

#### **AND** operation

| Х | Y | X•1 | X•Y | Y•X | X' | X•X′ |

|---|---|-----|-----|-----|----|------|

| 0 | 0 | 0   | 0   | 0   | 1  | 0    |

| 0 | 1 | 0   | 0   | 0   | 1  | 0    |

| 1 | 0 | 1   | 0   | 0   | 0  | 0    |

| 1 | 1 | 1   | 1   | 1   | 0  | 0    |

- Associativity

- > a:(X+Y)+Z=X+(Y+Z)

- > b:(X●Y)●Z=X●(Y●Z)

| X | Y | Ζ | X+Y | (X+Y)+Z | Y+Z | X+(Y+Z) | X•Y | (X∙Y)∙Z | Y•Z | X•(Y•Z) |

|---|---|---|-----|---------|-----|---------|-----|---------|-----|---------|

| 0 | 0 | 0 | 0   | 0       | 0   | 0       | 0   | 0       | 0   | 0       |

| 0 | 0 | 1 | 0   | 1       | 1   | 1       | 0   | 0       | 0   | 0       |

| 0 | 1 | 0 | 1   | 1       | 1   | 1       | 0   | 0       | 0   | 0       |

| 0 | 1 | 1 | 1   | 1       | 1   | 1       | 0   | 0       | 1   | 0       |

| 1 | 0 | 0 | 1   | 1       | 0   | 1       | 0   | 0       | 0   | 0       |

| 1 | 0 | 1 | 1   | 1       | 1   | 1       | 0   | 0       | 0   | 0       |

| 1 | 1 | 0 | 1   | 1       | 1   | 1       | 1   | 0       | 0   | 0       |

| 1 | 1 | 1 | 1   | 1       | 1   | 1       | 1   | 1       | 1   | 1       |

- Distributivity

- > a:  $X+(Y \bullet Z) = (X+Y) \bullet (X+Z)$

- $b: X \bullet (Y+Z) = (X \bullet Y) + (X \bullet Z)$

|   |   |   |     |     | (X+Y)● |     | Χ+    |     |     | Х∙Ү+ |     | X۰    |

|---|---|---|-----|-----|--------|-----|-------|-----|-----|------|-----|-------|

| X | Y | Ζ | X+Y | X+Z | (X+Z)  | Y•Z | (Y∙Z) | X•Y | X•Z | X•Z  | Y+Z | (Y+Z) |

| 0 | 0 | 0 | 0   | 0   | 0      | 0   | 0     | 0   | 0   | 0    | 0   | 0     |

| 0 | 0 | 1 | 0   | 1   | 0      | 0   | 0     | 0   | 0   | 0    | 1   | 0     |

| 0 | 1 | 0 | 1   | 0   | 0      | 0   | 0     | 0   | 0   | 0    | 1   | 0     |

| 0 | 1 | 1 | 1   | 1   | 1      | 1   | 1     | 0   | 0   | 0    | 1   | 0     |

| 1 | 0 | 0 | 1   | 1   | 1      | 0   | 1     | 0   | 0   | 0    | 0   | 0     |

| 1 | 0 | 1 | 1   | 1   | 1      | 0   | 1     | 0   | 1   | 1    | 1   | 1     |

| 1 | 1 | 0 | 1   | 1   | 1      | 0   | 1     | 1   | 0   | 1    | 1   | 1     |

| 1 | 1 | 1 | 1   | 1   | 1      | 1   | 1     | 1   | 1   | 1    | 1   | 1     |

- Idempotency

- > a:X+X=X

- > b:X•X=X

- Null elements

- > a:X+1=1

- > b:X•0=0

- Involution

- > a:(X')'=X

| - |   |   | OR  | AND |     |     |     |     |    |     |

|---|---|---|-----|-----|-----|-----|-----|-----|----|-----|

| I | Х | Υ | X+Y | X•Y | X+X | X•X | X+1 | X•0 | X' | X'' |

| ſ | 0 | 0 | 0   | 0   | 0   | 0   | 1   | 0   | 1  | 0   |

|   | 0 | 1 | 1   | 0   | 0   | 0   | 1   | 0   | 1  | 0   |

|   | 1 | 0 | 1   | 0   | 1   | 1   | 1   | 0   | 0  | 1   |

|   | 1 | 1 | 1   | 1   | 1   | 1   | 1   | 0   | 0  | 1   |

• Absorption

>a: (X•Y)+(X•Y'•Z)=(X•Y)+(X•Z)

> b: (X+Y)•(X+Y'+Z) =

(X+Y)•(X+Z)

|   |              |   |    |    |      | (XY)+  |    | (XY)+ |     | X+Y' | (X+Y)●   |     | (X+Y)● |

|---|--------------|---|----|----|------|--------|----|-------|-----|------|----------|-----|--------|

| × | <b>( Y</b> ) | Z | Υ' | XY | XY'Z | (XY'Z) | XZ | (XZ)  | X+Y | +Z   | (X+Y'+Z) | X+Z | (X+Z)  |

| 0 | 0            | 0 | 1  | 0  | 0    | 0      | 0  | 0     | 0   | 1    | 0        | 0   | 0      |

| 0 | 0            | 1 | 1  | 0  | 0    | 0      | 0  | 0     | 0   | 1    | 0        | 1   | 0      |

| 0 | 1            | 0 | 0  | 0  | 0    | 0      | 0  | 0     | 1   | 0    | 0        | 0   | 0      |

| 0 | 1            | 1 | 0  | 0  | 0    | 0      | 0  | 0     | 1   | 1    | 1        | 1   | 1      |

| 1 | 0            | 0 | 1  | 0  | 0    | 0      | 0  | 0     | 1   | 1    | 1        | 1   | 1      |

| 1 | 0            | 1 | 1  | 0  | 1    | 1      | 1  | 1     | 1   | 1    | 1        | 1   | 1      |

| 1 | 1            | 0 | 0  | 1  | 0    | 1      | 0  | 1     | 1   | 1    | 1        | 1   | 1      |

| 1 | 1            | 1 | 0  | 1  | 0    | 1      | 1  | 1     | 1   | 1    | 1        | 1   | 1      |

- DeMorgan's theorem (very important!)

- > a: (X+Y)'=\_X' Y'

$X+Y = X \bullet Y$  break (or connect) the bar & change the sign --

> b: (X.Y)'=X'+Y'

X•Y = X+Y break (or connect) the bar & change the sign

Generalized DeMorgan's theorem:

• GT8a:  $(X_1+X_2+...+X_{n-1}+X_n)'=X_1'\bullet X_2'\bullet...\bullet X_{n-1}'\bullet X_n'$

OR AND

| X | Y | X+Y | X•Y | X' | Y' | (X+Y)' | X'•Y' | (X•Y)' | X'+Y' |

|---|---|-----|-----|----|----|--------|-------|--------|-------|

| 0 | 0 | 0   | 0   | 1  | 1  | 1      | 1     | 1      | 1     |

| 0 | 1 | 1   | 0   | 1  | 0  | 0      | 0     | 1      | 1     |

| 1 | 0 | 1   | 0   | 0  | 1  | 0      | 0     | 1      | 1     |

| 1 | 1 | 1   | 1   | 0  | 0  | 0      | 0     | 0      | 0     |

- Consensus Theorem

- > a: (X•Y)+(X'•Z)+(Y•Z) = (X•Y)+(X'•Z) > b: (X+Y)•(X'+Z)•(Y+Z) = (X+Y)•(X'+Z)

|   |   |   |    |    |     |    | (XY)+<br>(X'Z)+ | (XY)+ |     |      |     | (X+Y)●<br>(X'+Z)● | (X+Y)• |

|---|---|---|----|----|-----|----|-----------------|-------|-----|------|-----|-------------------|--------|

| X | Υ | z | X' | XY | x'z | YZ | (YZ)            | (X'Z) | X+Y | X'+Z | Y+Z | (Y+Z)             | (X'+Z) |

| 0 | 0 | 0 | 1  | 0  | 0   | 0  | 0               | 0     | 0   | 1    | 0   | 0                 | 0      |

| 0 | 0 | 1 | 1  | 0  | 1   | 0  | 1               | 1     | 0   | 1    | 1   | 0                 | 0      |

| 0 | 1 | 0 | 1  | 0  | 0   | 0  | 0               | 0     | 1   | 1    | 1   | 1                 | 1      |

| 0 | 1 | 1 | 1  | 0  | 1   | 1  | 1               | 1     | 1   | 1    | 1   | 1                 | 1      |

| 1 | 0 | 0 | 0  | 0  | 0   | 0  | 0               | 0     | 1   | 0    | 0   | 0                 | 0      |

| 1 | 0 | 1 | 0  | 0  | 0   | 0  | 0               | 0     | 1   | 1    | 1   | 1                 | 1      |

| 1 | 1 | 0 | 0  | 1  | 0   | 0  | 1               | 1     | 1   | 0    | 1   | 0                 | 0      |

| 1 | 1 | 1 | 0  | 1  | 0   | 1  | 1               | 1     | 1   | 1    | 1   | 1                 | 1      |

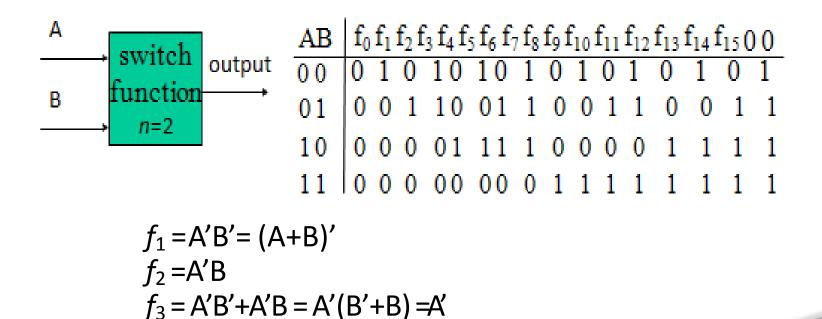

- > For *n* variables, there are  $2^n$  possible combinations of Values from all 0s to all 1s

- There are 2 possible values for the output of a function of a combination of values of *n* variables i.e. 0 and 1

- There are 2<sup>2n</sup> different switching functions for n variables

- > n=0 (no inputs)  $2^{2^n} = 2^{2^0} = 2^1 = 2$

Output can be either 0 or 1

> n=1 (1 input, A)  $2^{2^n} = 2^{2^1} = 2^2 = 4$

Output can be 0, 1, A, or A'

> n=2 (2 inputs, A and B)  $\implies$   $2^{2^n} = 2^{2^2} = 2^4 = 16$

Logical functions are generally expressed in terms of different combinations of logical variables with their true forms as well as the complement forms. Binary logic values obtained by the logical functions and logic variables are in binary form. An arbitrary logic function can be expressed in the following forms.

- Sum of the Products (SOP)

- Product of the Sums (POS)

- FOUCHTION FOR LIBERT

- Product Term: In Boolean algebra, the logical product of several variables on which a function depends is considered to be a product term. In other words, the AND function is referred to as a product term or standard product.

- Sum Term: An OR function is referred to as a sum term

- Sum of Products (SOP): The logical sum of two or more logical Y = AB + BC + ACproductterms is referred to as a sum of products expression

- **Product of Sums (POS):** Similarly, the logical product of two or morelogical sum terms is called a product of sums expression

> Standard form: The standard form of the Boolean function is

when it is expressed in sum of the products or product of the Y = AB + BC + ACsums fashion

- > Nonstandard Form: Boolean functions are also sometimes  $F = (AB + CD)(\overline{AB} + \overline{CD})$ , which is neither a sum of products form nor a product of sums form.

- Minterm: A product term containing all n variables of the function in either true or complemented form is called the minterm. Each minterm is obtained by an AND operation of the variables in their true form or complemented form.

- FOUCHTION FOR LIBERT

- Maxterm: A sum term containing all n variables of the function in either true or complemented form is called the Maxterm.

Each Maxterm is obtained by an OR operation of the variables in their true form or complemented form.

- The canonical sum of products form of a logic function can be obtained by using the following procedure

- Check each term in the given logic function. Retain if it is a minterm, continue to examine the next term in the same manner.

- Multiply all the products and discard the redundant terms.

- EDUCKTION FOR LIBER

- Example: Obtain the canonical sum of product form of the following function F(A, B, C) = A + BC

- Solution:

$$F(A,B,C) = A + BC$$

=  $A(B + \overline{B})(C + \overline{C}) + BC(A + \overline{A})$

=  $(AB + A\overline{B})(C + \overline{C}) + ABC + \overline{ABC}$

=  $ABC + A\overline{B}C + AB\overline{C} + A\overline{B}C + ABC + \overline{ABC}$

$= ABC + A\overline{B}C + AB\overline{C} + A\overline{B}\overline{C} + \overline{A}BC (as ABC + ABC = ABC)$

Hence the canonical sum of the product expression of the given function is

$F(A,B,C) = ABC + A\overline{B}C + AB\overline{C} + A\overline{B}\overline{C} + \overline{A}BC$

The product of sums form is a method (or form) of simplifying the Boolean expressions of logic gates. In this POS form, all the variables are ORed, i.e. written as sums to form sum terms. All these sum terms are ANDed (multiplied) together to get the product-of-sum form. This form is exactly opposite to the SOP form. So this can also be said as —Dualof SOP form .

(A+B) \* (A + B + C) \* (C+D)

POS form can be obtained by

Writing an OR term for each input combination, which produces LOW

Minimize the following Boolean expression using Boolean identities –

- F(A,B,C)=(A+B)(A+C)F(A,B,C)=(A+B)(A+C)Solution

- Given, F(A,B,C)=(A+B)(A+C)

- F (A,B,C)=A.A+A.C+B.A+B.C [Applying distributive Rule] F(A,B,C)=A+A.C+B.A+B.C [Applying Idempotent Law] F(A,B,C)=A(1+C)+B.A+B.C [Applying distributive Law] F(A,B,C)=A+B.A+B.C [Applying dominance

- F(A,B,C)=(A+1).A+B.C [Applying distributive Law]

- F(A,B,C)=1.A+B.C [Applying dominance Law]

- F(A,B,C)=A+B.C [Applying dominance Law]

- So, F(A,B,C)=A+BCF(A,B,C)=A+BC is the minimized form.

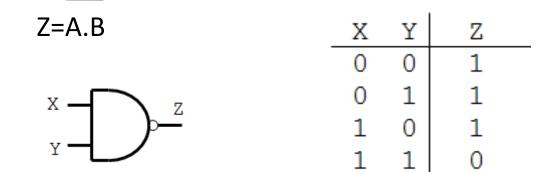

### DIGITAL LOGIC GATES

AND GATE: Z=A.B  $X \longrightarrow Z$   $Y \longrightarrow Z$ Z = X & Y

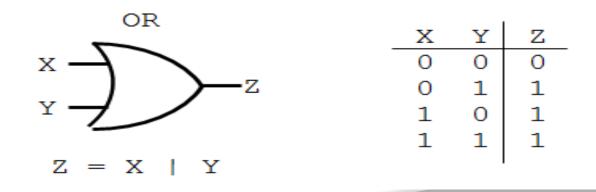

### **OR GATE:**

Z=A+B

Υ

0

1 0

1

Х

0

0 1 1 Z

0

0

0

1

### **DIGITAL LOGIC GATES**

### NOT GATE:

#### NAND GATE:

## DIGITAL LOGIC GATES

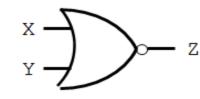

#### NOR GATE:

Z=A+B

| Х | Y | Ζ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

|   |   |   |

### **Ex-OR GATE:**

| ХҮ  | Z |

|-----|---|

| 0 0 | 1 |

| 0 1 | 0 |

| 1 0 | 0 |

| 1 1 | 1 |

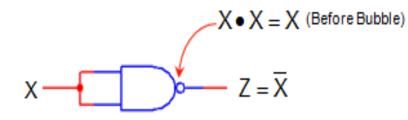

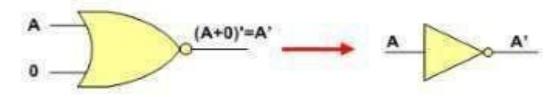

#### NAND Gate as an Inverter Gate

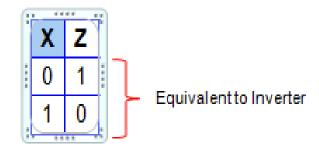

#### NAND Gate as an AND Gate

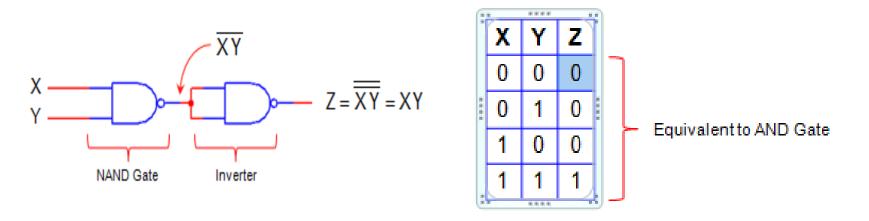

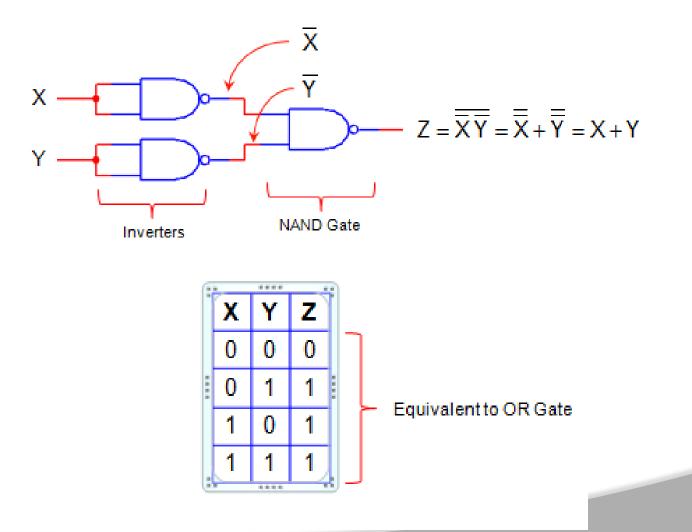

NAND Gate as an OR Gate

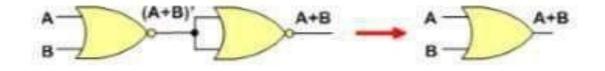

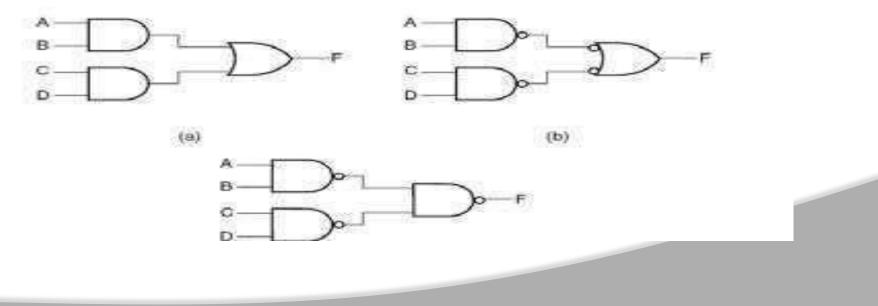

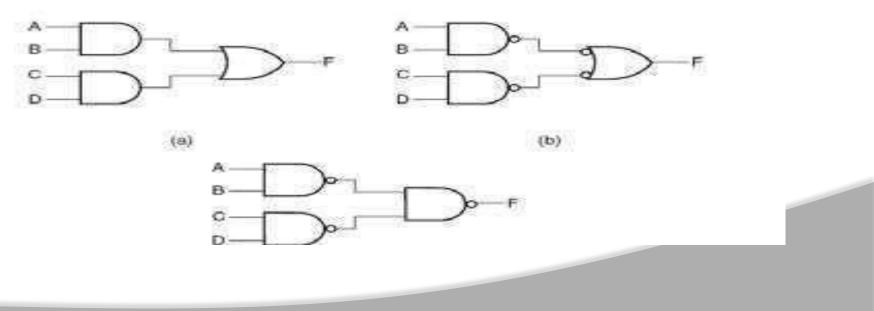

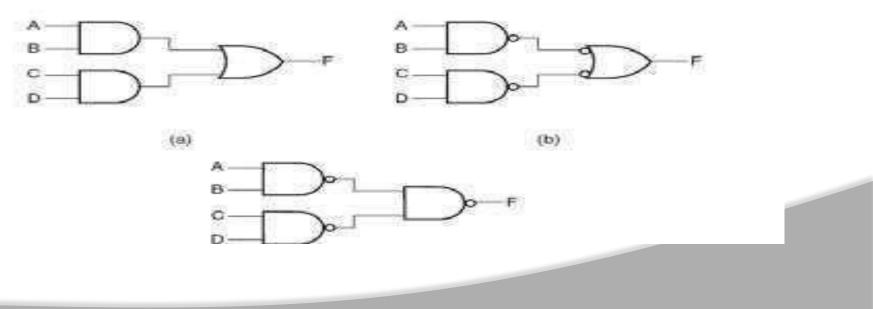

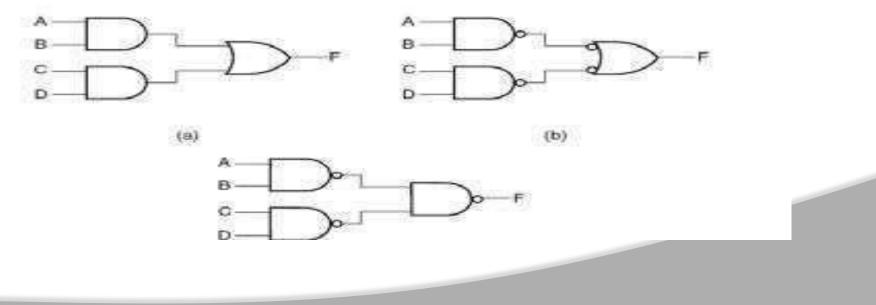

### MULTILEVEL NAND-NOR REALIZATION

EDUCKTION BET

1. All NOR input pins connect to the input signal A gives an output A'.

2. One NOR input pin is connected to the input signal A while all other input pins are connected to logic 0. The output will be A'.

#### **Implementing OR Using only NOR Gates**

An OR gate can be replaced by NOR gates as shown in the figure (The OR is replaced by a NOR gate with its output complemented by a NOR gate inverter)

- The implementation of Boolean functions with NAND gates requires that the functions be in sum of products (SOP) form.

- This function can be implemented by three steps.

0 0 0

The implementation of Boolean functions with NAND gates requires that the functions be in sum of products (SOP) form.

0 0 0

The implementation of Boolean functions with NAND gates requires that the functions be in sum of products (SOP) form.

0 0 0

- The implementation of Boolean functions with NAND gates requires that the functions be in sum of products (SOP) form.

- This function can be implemented by three steps.

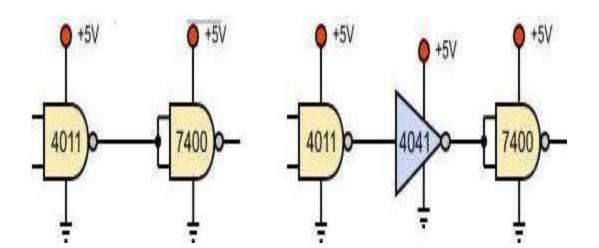

#### **CMOS DRIVING TTL AND CMOS DRIVING TTL**

#### Interfacing a CMOS to a TTL under 5Volts power supply

# **Unit-II** COMBINATIONAL DIGITAL CIRCUITS

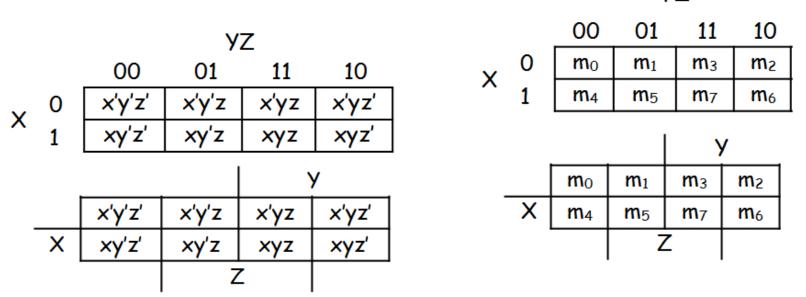

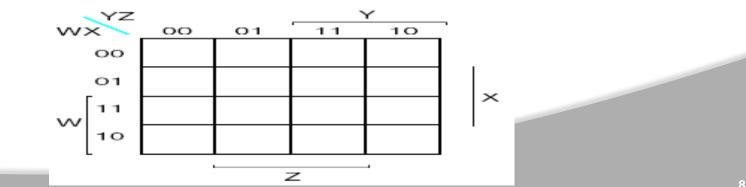

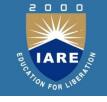

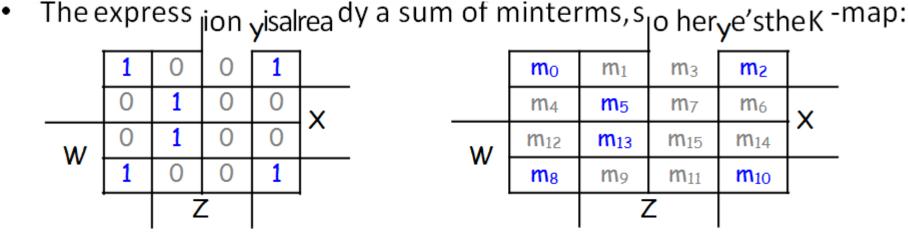

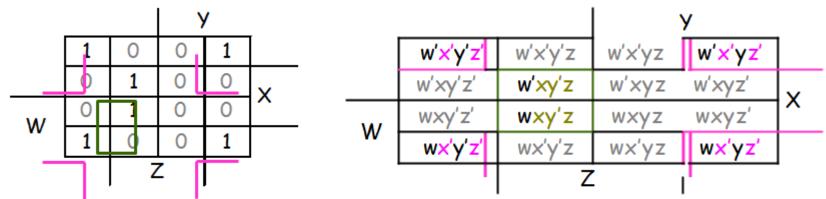

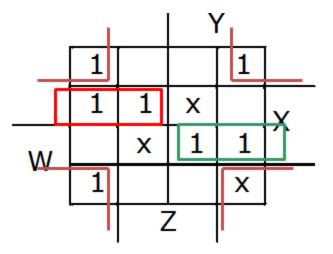

## KARANAUGHMAP

- •Boolean algebra helps us simplify expressions and circuits

- •Karnaugh Map: A graphical technique for simplifying aBooleanexpression into eitherform:

- -minimal sum of products(MSP)

- -minimal product of sums(MPS)

- Goal of the simplification.

- -There are a minimal number of product/sumterms

- -Each term has a minimal number ofliterals

### KARANAUGH MAP

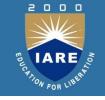

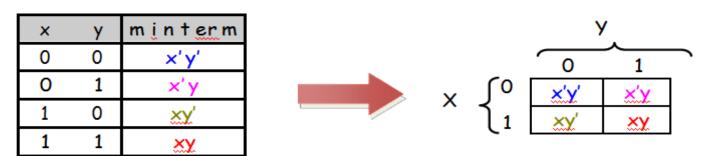

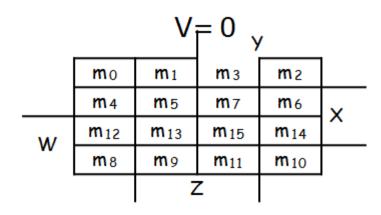

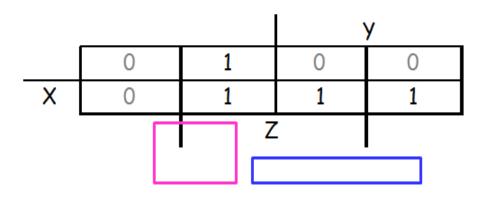

A two-variable function has four possible minterms. We can re- arrange these minterms into a Karnaugh map

- Now we can easily see which minterms contain commonliterals

- Minterms on the left and right sides contain y' and y respectively

Х

#### KARANAUGH MAP

- Make as few rectangles as possible, to minimize the number of products in the final expression.

- Make each rectangle as large as possible, to minimize the number of literals in each term.

- Rectangles can be overlapped, if that makes them larger

- The most difficult step is grouping together all the 1s in the Kmap

- Make rectangles around groups of one, two, four or eight 1s

- All of the 1s in the map should beincluded inat least one rectangle. Do not include any of the 0s

- Each group corresponds to one product term

• Maxterms are grouped to find minimal PoS expression yz 00 01 11 10x x + y + z x + y + z' x + y' + z'

|   |         |         |          | x+y'+z  |

|---|---------|---------|----------|---------|

| 1 | x' +y+z | x'+y+z' | x'+y'+z' | x'+y'+z |

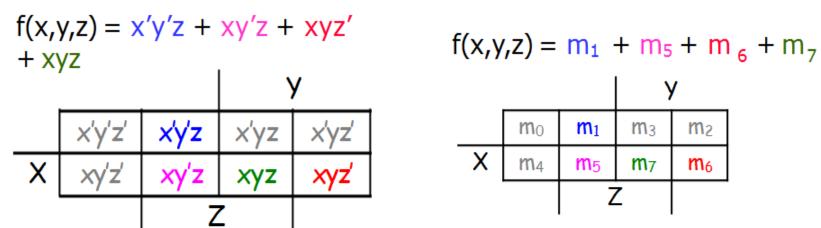

- Let's consider simplifying f(x,y,z) = xy + y'z + xz

- You should convert the expression into a sum of mintermsform,

- The easiest way to do this is to make a truth table for the function, and then read off the minterms

- You can either write out the literals or use the minterm shorthand

- Here is the truth table and sum of minterms for our

|   |   |   | -        |

|---|---|---|----------|

| × | Y | z | f(x,y,z) |

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | 0        |

| 0 | 1 | 1 | 0        |

| 1 | 0 | 0 | 0        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | 1        |

| 1 | 1 | 1 | 1        |

$$f(x,y,z) = x'y'z + xy'z + xyz' + xyz = m_1 + m_5 + m_6 + m_7$$

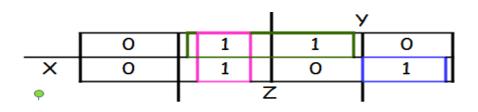

• For a three-variable expression with inputs x, y, z, the arrangement of

#### YΖ

- Here is the filled in K-map, with all groups shown

- The magenta and green groups overlap, which makes each of them as

- large as possible

- Minterm m<sub>6</sub> is in a group all by its lonesome

• The final MSP here is x'z + y'z + xyz'

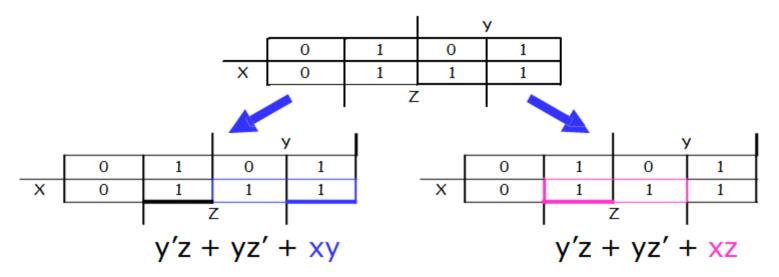

There may not necessarily be a *unique* MSP. The K-map below yields

two

valid and equivalent MSPs, because there are two possible waysto

Remember that overlapping groups is possible, as shown above

Maxterms are grouped to find minimal PoS expression

00

01

11

10

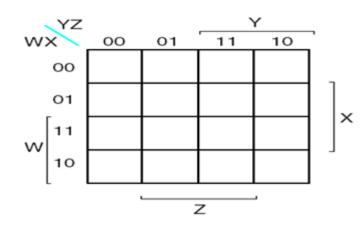

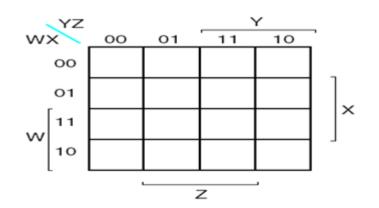

- We can do four-variable expressions too!

- The minterms in the third and fourth columns, and in thethird

- and

- fourth rows, are switchedaround.

- Again, this ensures that adjacent squares have common literals

- Grouping minterms is similar to the three-variable case, but:

- You can have rectangular groups of 1, 2, 4, 8 or 16 minterms

- You can wrap around all four sides

81

We can make the following groups, resulting in the MSP x'z' + xy'z

Example: Simplify  $m_0 + m_2 + m_5 + m_8 + m_{10} + m_{13}$

•

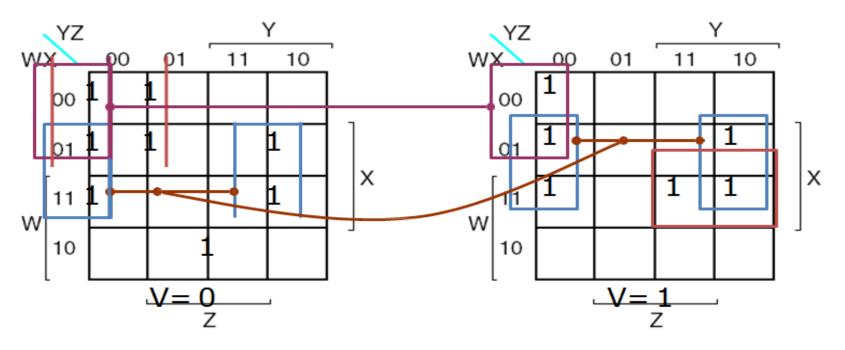

$$F(W,X,Y,Z) = \prod M(0,1,2,4,5)$$

•  $V(W,X,Y,Z) = \prod M(0,1,2,4,5)$

•  $V(W,X,Y,Z) = \prod M(0,1,2,5)$

•  $V(W,X,Y,Z) = \prod M(0,1$

|    |                 |                 | V= 1        | Y               |   |

|----|-----------------|-----------------|-------------|-----------------|---|

|    | m <u>16</u>     | m <sub>17</sub> | <b>m</b> 19 | m <sub>8</sub>  |   |

|    | m <sub>20</sub> | m <sub>21</sub> | m₂₃         | m <sub>22</sub> | v |

| W  | m₂8             | m <sub>29</sub> | $m_{B1}$    | m <sub>30</sub> | ^ |

| vv | m₂₄             | m <sub>2₅</sub> | m₂7         | m <sub>26</sub> |   |

|    |                 | Z               | 2           |                 |   |

• In our example, we can write f(x,y,z) in two equivalent ways

• In either case, the resulting K-map is shownbelow

$\begin{array}{ll} f = XZ' \\ \Sigma m(4,6,12,14,20,22,28,30) \\ + V'W'Y' & \Sigma m(0,1,4,5) \\ + W'Y'Z' & \Sigma m(0,4,16,20) \\ + VWXY & \Sigma m(30,31) \\ + V'WX'YZ & m11 \end{array}$

## DON'T CARE CONDITION

- You don't always need all 2<sup>n</sup> input combinations in annvariable function

- If you can guarantee that certain input combinations never

occur

If some outputs aren't used in the rest of the circuit

| × | У | z | f(x,y,z) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | X        |

| 0 | 1 | 1 | 0        |

| 1 | 0 | 0 | 0        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | X        |

| 1 | 1 | 1 | 1        |

We mark don't-care outputs in truth tables and K-maps with Xs.

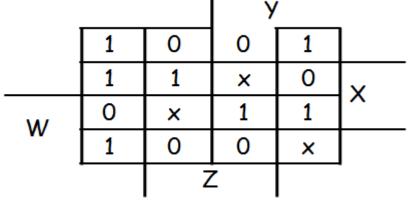

• Find a MSP for

f(w,x,y,z) = 🖻 m(0,2,4,5,8,14,15), d(w,x,y,z) = 🖻 m(7,10,13)

This notation means that input combinations wxyz = 0111, 1010 and 1101(corresponding to minterms  $m_7$ ,  $m_{10}$  and  $m_{13}$ ) are unused.

## DON'T CARE CONDITION

• Find a MSP for:

f(w,x,y,z) = 🖻m(0,2,4,5,8,14,15), d(w,x,y,z) = 🖻m(7,10,13)

f(w,x,y,z) = x'z' + w'xy' + wxy

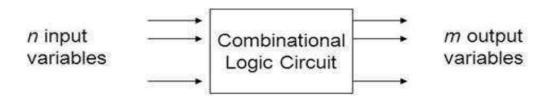

## COMBINATIONAL CIRCUITS

Combinational circuit is a circuit in which we combine the different gates in the circuit, for example encoder, decoder, multiplexer and demultiplexer.

Some of the characteristics of combinational circuits are:

The output of combinational circuit at any instant of time, depends

only on the levels present at inputterminals.

• The combinational circuit do not use any memory. The previous state

of input does not have any effect on the present state of the circuit.

A combinational circuit can have an n number of inputs and m number of outputs.

## COMBINATIONAL CIRCUITS

• Block diagram:

possible combinations of input values.

- Specific functions : of combinational circuits

- Adders, subtractors, multiplexers, comparators, encoder, Decoder. MSI Circuits and standard cells

#### **Analysis procedure**

To obtain the output Boolean functions from a logic diagram, proceed as follows:

- Label all gate outputs that are a function of input variables with arbitrary symbols. Determine the Boolean functions for eachgate output.

- Label the gates that are a function of input variables and previously labeled gates with other arbitrary symbols. Find the Boolean functions for these gates.

- 3. Repeat the process outlined in step 2 until the outputs of the circuit are obtained.

## **DESIGN PROCEDURE**

# EUCHTION FOR LIBERT

#### **Design Procedure**

- 1. The problem is stated

- 2.The number of available input variables and required output variables is determined.

- 3. The input and output variables are assigned letter symbols.

- 4.The truth table that defines the required relationship between inputs

- and outputs is derived.

- 5.The simplified Boolean function for each output is obtained.6.The logic diagram is drawn.

#### **ADDERS**

#### Half Adder

A Half Adder is a combinational circuit with two binary inputs (augends and addend bits and two binary outputs (sum and carry bits.) It adds the two inputs (A and B) and produces the sum (S) and the carry (C) bits.

Fig 1:Block diagram

| Inp | Inputs |   | Outputs |  |  |

|-----|--------|---|---------|--|--|

| A   | в      | S | С       |  |  |

| 0   | 0      | 0 | 0       |  |  |

| 0   | 1      | 1 | 0       |  |  |

| 1   | 0      | 1 | 0       |  |  |

| 1   | 1      | 0 | 1       |  |  |

Fig 2:Truth table

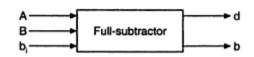

#### **Full subtractor**

The full subtractor perform subtraction of three input bits: the minuend , subtrahend , and borrow in and generates two output bits difference and borrow out.

Fig 7:Block diagram

| Inputs |   | nputs Difference |   | Borrow |

|--------|---|------------------|---|--------|

| Ā      | в | b,               | d | b      |

| 0      | 0 | 0                | 0 | 0      |

| 0      | 0 | 1                | 1 | 1      |

| 0      | 1 | 0                | 1 | 1      |

| 0      | 1 | 1                | 0 | 1      |

| 1      | 0 | 0                | 1 | 0      |

| 1      | 0 | 1                | 0 | 0      |

| 1      | 1 | 0                | 0 | 0      |

| 1      | 1 | 1                | 1 | 1      |

Fig 8: Truth table

$$d = \overline{A}\overline{B}b_{i} + \overline{A}B\overline{b}_{i} + A\overline{B}\overline{b}_{i} + ABb_{i} = A \oplus B \oplus b_{i}$$

$$b = \overline{A}\overline{B}b_{i} + \overline{A}B\overline{b}_{i} + \overline{A}Bb_{i} + ABb_{i} = \overline{A}B + (\overline{A \oplus B})b_{i}$$

EUCHTON FOR LIBER

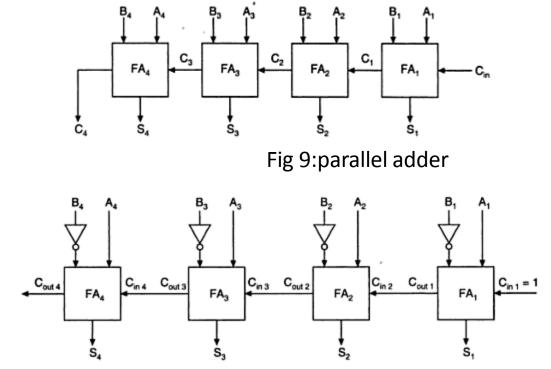

A binary parallel adder is a digital circuit that adds two binary numbers in parallel form and produces the arithmetic sum of those numbers in parallel form

Fig 10:parallel subtractor

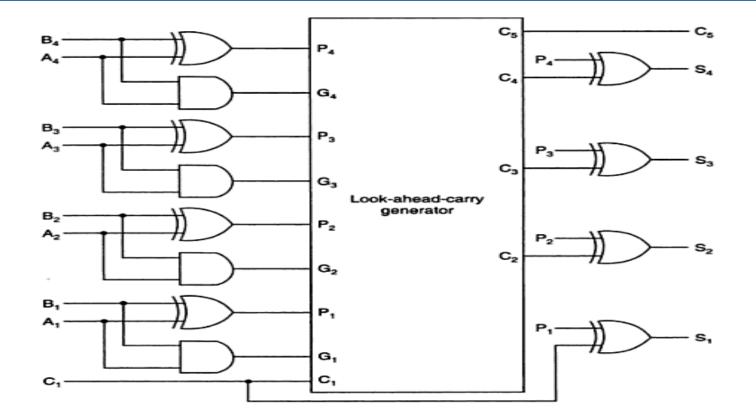

## **CARRY LOOK-A- HEAD ADDER**

- In parallel-adder, the speed with which an addition can be performed is governed by the time required for the carries to propagate or ripple through all of the stages of the adder.

- The look-ahead carry adder speeds up the process by eliminating this ripple carry delay.

$$S_n = P_n \oplus C_n \text{ where } P_n = A_n \oplus B_n$$

$$C_{on} = C_{n+1} = G_n + P_n C_n \text{ where } G_n = A_n \cdot B_n$$

## **CARRY LOOK-A- HEAD ADDER**

Fig:1 block diagram

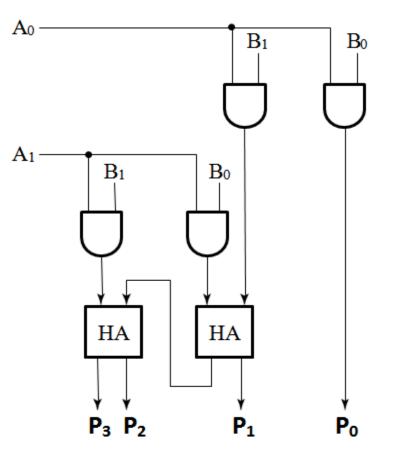

A binary multiplier is an electronic circuit used in digital electronics, such as a computer, to multiply two binary numbers. It is built using binary adders.

Example: (101 x 011)

Partial products are: 101 × 1, 101 × 1, and 101 × 0

|   |   |   | 1 | 0 | 1 |   |

|---|---|---|---|---|---|---|

|   |   | × | 0 | 1 | 1 | _ |

|   |   |   | 1 | 0 | 1 |   |

|   |   | 1 | 0 | 1 |   |   |

|   | 0 | 0 | 0 |   |   | _ |

| D | 0 | 1 | 1 | 1 | 1 | • |

- We can also make an n × m "block" multiplier and use that to form partial products.

- Example: 2 × 2 The logic equations for each partial-product binary digit are shown below

- We need to "add" the columns to get the product bits P0, P1, P2, and P3.

#### **BINARY MULTIPLIER**

Fig 1: 2 x 2 multiplier array

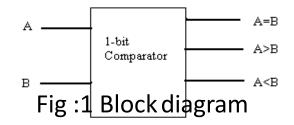

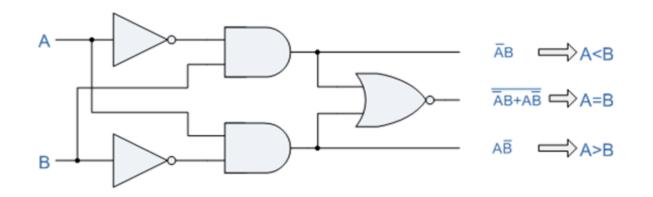

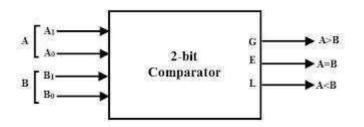

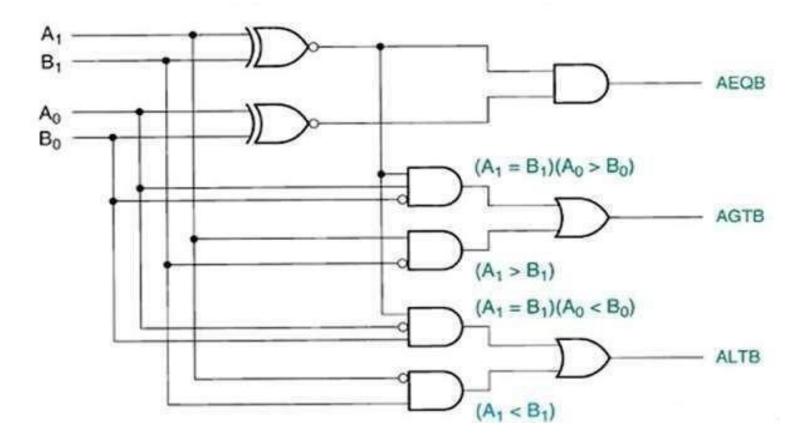

Magnitude comparator takes two numbers as input in binary form and determines whether one number is greater than, less than or equal to the other number.

1-Bit Magnitude Comparator

A comparator used to compare two bits is called a single bit comparator.

#### MAGNITUDE COMPARATOR

| Inp | uts |       | Outputs |       |  |

|-----|-----|-------|---------|-------|--|

| A   | В   | A > B | A = B   | A < B |  |

| 0   | 0   | 0     | 1       | 0     |  |

| 0   | 1   | 0     | 0       | 1     |  |

| 1   | 0   | 1     | 0       | 0     |  |

| 1   | 1   | 0     | 1       | 0     |  |

Fig 2:Logic diagram of 1-bit comparator

## MAGNITUDE COMPARATOR

• 2 Bit magnitude comparator

Fig :3 Block diagram

|                | Inp            | outs           |                |     | Outputs |                   |

|----------------|----------------|----------------|----------------|-----|---------|-------------------|

| A <sub>1</sub> | A <sub>0</sub> | B <sub>1</sub> | B <sub>0</sub> | A>B | A=B     | A <b< th=""></b<> |

| 0              | 0              | 0              | 0              | 0   | 1       | 0                 |

| 0              | 0              | 0              | 1              | 0   | 0       | 1                 |

| 0              | 0              | 1              | 0              | 0   | 0       | 1                 |

| 0              | 0              | 1              | 1              | 0   | 0       | 1                 |

| 0              | 1              | 0              | 0              | 1   | 0       | 0                 |

| 0              | 1              | 0              | 1              | 0   | 1       | 0                 |

| 0              | 1              | 1              | 0              | 0   | 0       | 1                 |

| 0              | 1              | 1              | 1              | 0   | 0       | 1                 |

| 1              | 0              | 0              | 0              | 1   | 0       | 0                 |

| 1              | 0              | 0              | 1              | 1   | 0       | 0                 |

| 1              | 0              | 1              | 0              | 0   | 1       | 0                 |

| 1              | 0              | 1              | 1              | 0   | 0       | 1                 |

| 1              | 1              | 0              | 0              | 1   | 0       | 0                 |

| 1              | 1              | 0              | 1              | 1   | 0       | 0                 |

| 1              | 1              | 1              | 0              | 1   | 0       | 0                 |

| 1              | 1              | 1              | 1              | 0   | 1       | 0                 |

Fig:4 Truthtable

## MAGNITUDE COMPARATOR

Fig 5:Logic diagram of 2-bit comparator

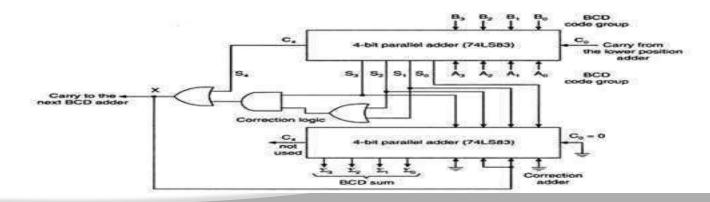

#### **BCD ADDER**

#### **BCD Adder**

- Perform the addition of two decimal digits in BCD, together with an input carry from a previous stage.

- When the sum is 9 or less, the sum is in proper BCD form and no correction is needed.

- When the sum of two digits is greater than 9, a correction of 0110 should be added to that sum, to produce the proper BCD result. This will produce a carry to be added to the next decimal position.

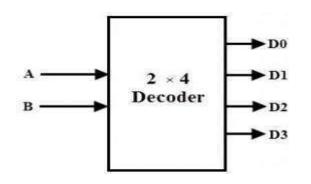

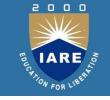

- A binary decoder is a combinational logic circuit that converts binary information from the n coded inputs to a maximum of 2<sup>n</sup>unique outputs.

- We have following types of decoders 2x4,3x8,4x16....

2x4 decoder

Inputs Output D. D. D. D. A В 0 1 0 0 0 0 1 0 1 0 0 0 1 0 0 0 1 0 1 1 0 0 0 1

Fig 1: Block diagram

Fig 2:Truthtable

Higher order decoder implementation using lower order. Ex:4x16 decoder using 3x8decoders

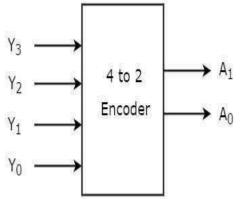

# **ENCODERS**

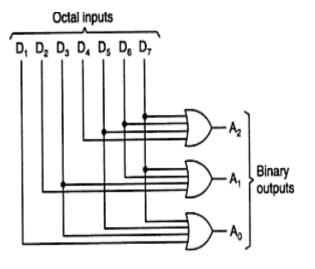

- An Encoder is a combinational circuit that performs the reverse operation of Decoder. It has maximum of 2<sup>n</sup> input lines and 'n' output lines.

- It will produce a binary code equivalent to the input, which is active High.

Fig 1:block diagram of 4x2encoder

# **ENCODERS**

## Octal to binary encoder

| Octal digits   |   | E              | Binary | ,              |

|----------------|---|----------------|--------|----------------|

|                |   | A <sub>2</sub> | Α,     | A <sub>0</sub> |

| Do             | 0 | 0              | 0      | 0              |

| D              | 1 | 0              | 0      | 1              |

| $D_2$          | 2 | 0              | 1      | 0              |

| $D_3$          | 3 | 0              | 1      | 1              |

| D4             | 4 | 1              | 0      | 0              |

| D <sub>5</sub> | 5 | 1              | 0      | 1              |

| D <sub>6</sub> | 6 | 1              | 1      | 0              |

| D7             | 7 | 1              | 1      | 1              |

Fig 2:Truth table

Fig 3: Logic diagram

# **ENCODERS**

## **Priority encoder**

A 4 to 2 priority encoder has four inputs  $Y_3$ ,  $Y_2$ ,  $Y_1 \& Y_0$  and two outputs  $A_1 \& A_0$ . Here, the input,  $Y_3$  has the highest priority, whereas the input,  $Y_0$  has the lowest priority.

| Inputs         |                |    |                | Outputs |                |   |

|----------------|----------------|----|----------------|---------|----------------|---|

| Y <sub>3</sub> | Y <sub>2</sub> | Y1 | Y <sub>0</sub> | A1      | A <sub>0</sub> | v |

| 0              | 0              | 0  | 0              | 0       | 0              | 0 |

| 0              | 0              | 0  | 1              | 0       | 0              | 1 |

| 0              | 0              | 1  | х              | 0       | 1              | 1 |

| 0              | 1              | x  | x              | 1       | 0              | 1 |

| 1              | x              | x  | x              | 1       | 1              | 1 |

Fig 4:Truth table

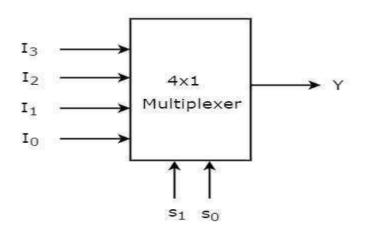

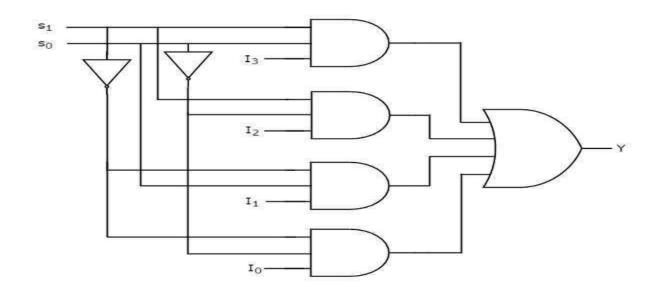

- Multiplexer is a combinational circuit that has maximum of 2<sup>n</sup> data inputs, 'n' selection lines and single output line. One of these data inputs will be connected to the output based on the values of selection lines.

- We have different types of multiplexers 2x1,4x1,8x1,16x1,32x1.....

| Selection             | Selection Lines |                |  |

|-----------------------|-----------------|----------------|--|

| <b>s</b> <sub>1</sub> | SO              | Ŷ              |  |

| 0                     | 0               | I <sub>0</sub> |  |

| 0                     | 1               | lı             |  |

| 1                     | 0               | Iz             |  |

| 1                     | 1               | IJ             |  |

Fig 2: Truthtable

Fig 1: Block diagram

Fig 3: Logic diagram

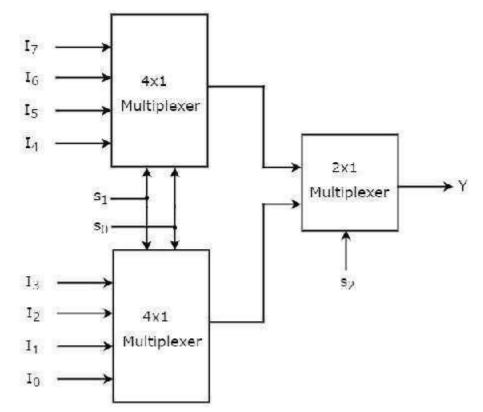

• Now, let us implement the higher-order Multiplexer using lower-order Multiplexers.

• Ex: 8x1 Multiplexer

Fig 3: 8x1 Multiplexer diagram

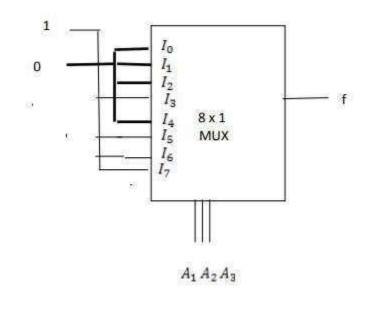

- Implementation of Boolean function usingmultiplexer

- $f(A1, A2, A3) = \Sigma(3, 5, 6, 7)$  implementation using 8x1 mux

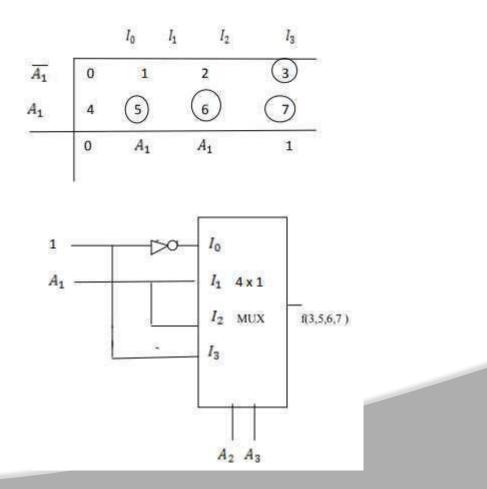

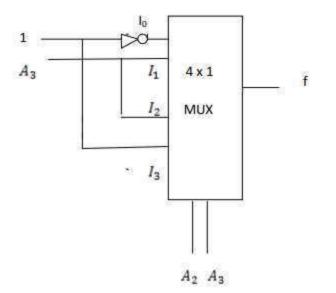

# $f(A1, A2, A3) = \Sigma(3,5,6,7)$ implementation using 4x1 muxMethod:1

| Minterms | <i>A</i> <sub>1</sub> | <i>A</i> <sub>2</sub> | A <sub>3</sub> | f |

|----------|-----------------------|-----------------------|----------------|---|

| 0        | 0                     | 0                     | 0              | 0 |

| 1        | 0                     | 0                     | 1              | 0 |

| 2        | 0                     | 1                     | 0              | 0 |

| 3        | 0                     | 1                     | 1              | 1 |

| 4        | 1                     | 0                     | 0              | 0 |

| 5        | 1                     | 0                     | 1              | 1 |

| 6        | 1                     | 1                     | 0              | 1 |

| 7        | 1                     | 1                     | 1              | 1 |

## Method:2

| Minterm | A1 | A <sub>2</sub> | A3 | 1 | f                 |                       |

|---------|----|----------------|----|---|-------------------|-----------------------|

| 0       | 0  | 0              | 0  | 0 | ł.                |                       |

| 1       | 0  | 0              | 1  | 0 | f= 0              | I <sub>0</sub>        |

| 2       | 0  | 1              | 0  | 0 |                   |                       |

| 3       | 0  | 1              | 1  | 1 | $f = A_3$         | <i>I</i> <sub>1</sub> |

| 4       | 1  | 0              | 0  | 0 | ž                 |                       |

| 5       | 1  | 0              | 1  | 1 | f= A <sub>3</sub> | $I_2$                 |

| 6       | 1  | 1              | 0  | 1 | 3                 | -                     |

| 7       | 1  | I              | 1  | 1 | f= 1              | $I_3$                 |

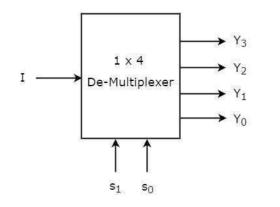

# DEMULTIPLEXER

- A demultiplexer is a device that takes a single input line and routes it to one of several digital output lines.

- A demultiplexer of 2<sup>n</sup> outputs has n select lines, which are used to select which output line to send the input.

- We have 1x2,1x4,8x1.... Demultiplexers.

| Selectio   | Selection Inputs |                | Out            | Outputs    |    |

|------------|------------------|----------------|----------------|------------|----|

| <b>S</b> 1 | S <sub>0</sub>   | Y <sub>3</sub> | Y <sub>2</sub> | <b>Y</b> 1 | YO |

| 0          | 0                | 0              | 0              | 0          | 1  |

| 0          | 1                | 0              | D              | I          | 0  |

| 1          | 0                | 0              | I              | 0          | 0  |

| 1          | 1                | I              | 0              | 0          | 0  |

Fig:1 Block diagram

Fig: 2 Truth table

# DEMULTIPLEXER

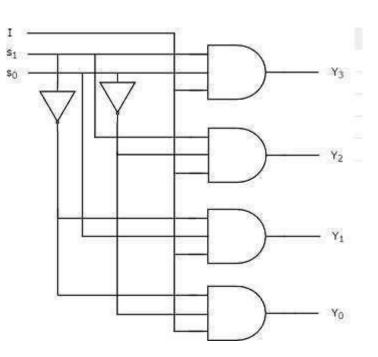

## Boolean functions for each output as

$egin{aligned} Y_3 &= s_1 s_0 I \ Y_2 &= s_1 s_0' I \ Y_1 &= s_1' s_0 I \ Y_0 &= s_1' s_0' I \end{aligned}$

Fig:3 Logic diagram

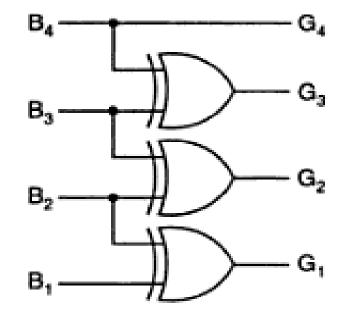

A code converter is a logic circuit whose inputs are bit patterns representing numbers (or character) in one code and whose outputs are the corresponding representation in a different code.

Design of a 4-bit binary to gray code converter

|                | 4-bit I        | binary         | ,                     |    | 4-bit ( | Gray           |    |

|----------------|----------------|----------------|-----------------------|----|---------|----------------|----|

| B <sub>4</sub> | B <sub>3</sub> | B <sub>2</sub> | <b>B</b> <sub>1</sub> | G4 | G3      | G <sub>2</sub> | G, |

| 0              | 0              | 0              | 0                     | 0  | 0       | 0              | 0  |

| 0              | 0              | 0              | 1                     | 0  | 0       | 0              | 1  |

| 0              | 0              | 1              | 0                     | 0  | 0       | 1              | 1  |

| 0              | 0              | 1              | 1                     | 0  | 0       | 1              | 0  |

| 0              | 1              | 0              | 0                     | 0  | 1       | 1              | 0  |

| 0              | 1              | 0              | 1                     | 0  | 1       | 1              | 1  |

| 0              | 1              | 1              | 0                     | 0  | 1       | 0              | 1  |

| 0              | 1              | 1              | 1                     | 0  | 1       | 0              | 0  |

| 1              | 0              | 0              | 0                     | 1  | 1       | 0              | 0  |

| 1              | 0              | 0              | 1                     | 1  | 1       | 0              | 1  |

| 1              | 0              | 1              | 0                     | 1  | 1       | 1              | 1  |

| 1              | 0              | 1              | 1                     | 1  | 1       | 1              | 0  |

| 1              | 1              | 0              | 0                     | 1  | 0       | 1              | 0  |

| 1              | 1              | 0              | 1                     | 1  | 0       | 1              | 1  |

| 1              | 1              | 1              | 0                     | 1  | 0       | 0              | 1  |

| 1              | 1              | 1              | 1                     | 1  | 0       | 0              | 0  |

Fig :1 Truthtable

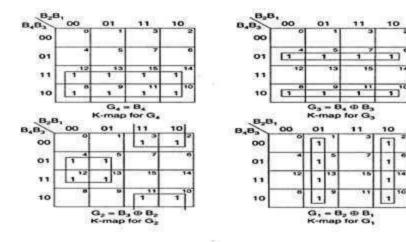

# **CODE CONVERTERS**

## K-map simplification

$$\begin{array}{ll} G_4 = \Sigma m(8,\,9,\,10,\,11,\,12,\,13,\,14,\,15) & G_4 = B_4 \\ G_3 = \Sigma m(4,\,5,\,6,\,7,\,8,\,9,\,10,\,11) & G_3 = \overline{B}_4 B_3 + B_4 \overline{B}_3 = B_4 \oplus B_3 \\ G_2 = \Sigma m(2,\,3,\,4,\,5,\,10,\,11,\,12,\,13) & G_2 = \overline{B}_3 B_2 + B_3 \overline{B}_2 = B_3 \oplus B_2 \\ G_1 = \Sigma m(1,\,2,\,5,\,6,\,9,\,10,\,13,\,14) & G_1 = \overline{B}_2 B_1 + B_2 \overline{B}_1 = B_2 \oplus B_1 \end{array}$$

# **CODE CONVERTERS**

Fig: 2 Logic diagram

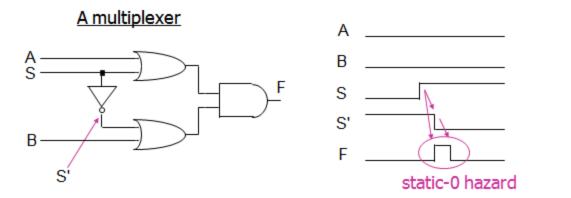

# **HAZARDS AND GLITCHES**

- **glitch**: unwanted output

- A circuit with the potential for a glitch has a **hazard**.

- Glitches occur when different pathways have different delays

- Causes circuit noise

- Dangerous if logic makes a decision while output is unstable

Solutions

- Design hazard-free circuits

- Difficult when logic is multilevel

- Wait until signals are stable

# **TYPES OF HAZARDS**

- Static 1-hazard

- Output should stay logic 1

- Gate delays cause brief glitch to logic 0

- Static 0-hazard

- Output should stay logic 0

- Gate delays cause brief glitch to logic 11

0

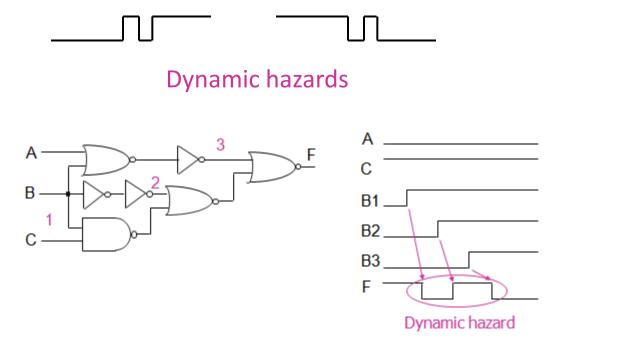

- Dynamic hazards

- Output should toggle cleanly

- Gate delays cause multiple transitions

# **STATIC HAZARDS**

- Often occurs when a literal and its complement momentarily assume the same value

- Through different paths with different delays

- Causes an (ideally) static output to *glitch*

# **DYNAMIC HAZARDS**

- Often occurs when a literal assumes multiple values

- Through different paths with different delays

- Causes an output to toggle multiple times

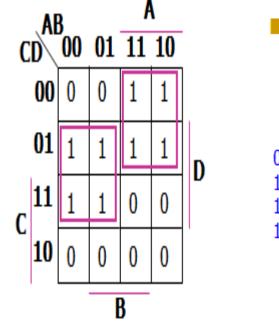

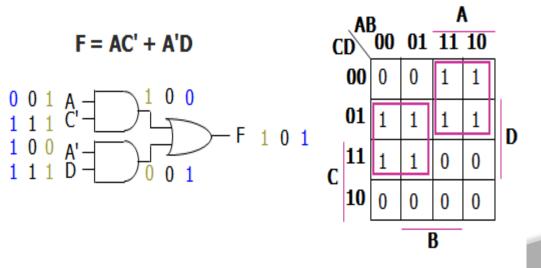

# **ELIMINATING STATIC HAZARDS**

- Key idea: Glitches happen when a changing input spans separate K-map encirclements

- Example: 1101 to 0101 change can cause a static-1 glitch

■ ABCD: 1101 → 0101

2 0 0 0

# **ELIMINATING STATIC HAZARDS**

- Solution: Add redundant K-map encirclements

- Ensure that all single-bit changes are covered by same block

- First eliminate static-1 hazards: Use SOP form

- If need to eliminate static-0 hazards, use POS form

- Technique only works for 2-level logic

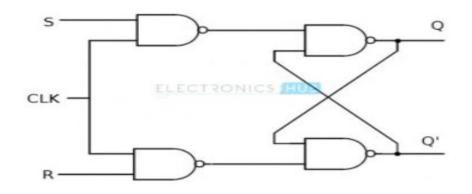

# **Unit-III** SEQUENTIAL CIRCUITS AND SYSTEMS

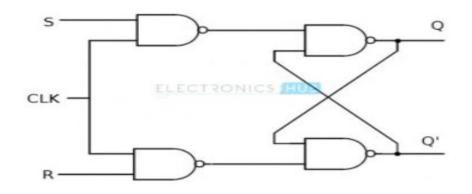

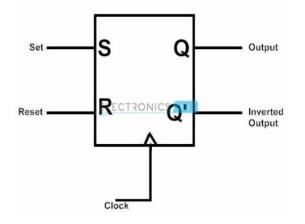

Gated latch is a basic latch that includes input gating and a control signal.

- The latch retains its existing state when the control input is equal to 0.

- Its state may be changed when the control signal is equal to 1.In our discussion we referred to the control input as the clock.

- We consider two types of gated latches:

- Gated SR latch uses the S and R inputs to set the latch to 1

- Gated D latch uses the D input to force the latch into a state that has the same logic value as the Dinput.

# **SEQUENTIAL CIRCUITS**

- Basic latch is a feedback connection of two NOR gates or two NAND gates.

- It can store one bit of information.

- It can be set to 1 using the S input andreset to 0 using the R input.

- > A feedback loop with even number of inverters

> If A = 0, B = 1 or when A = 1, B = 0

This circuit is not useful due to the lack ofa mechanism for changing its state **RS LATCH:**

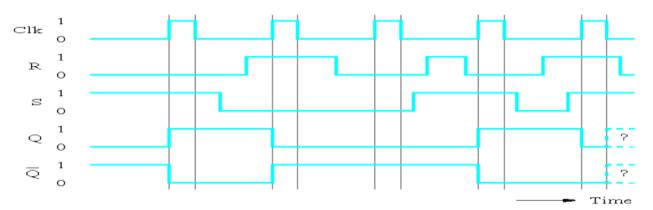

| Clk | S | R | Q(t+1)           |

|-----|---|---|------------------|

| 0   | × | × | Q(t) (no change) |

| 1   | 0 | 0 | Q(t) (no change) |

| 1   | 0 | 1 | 0                |

| 1   | 1 | 0 | 1                |

| 1   | 1 | 1 | ×                |

|     |   |   |                  |

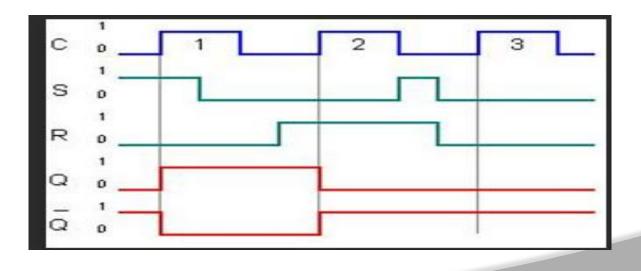

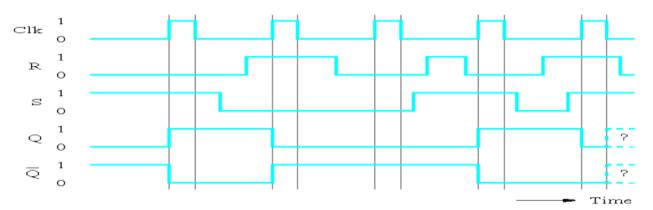

### (b) Characteristic table

### (c) Timing diagram

(d) Graphical symbol

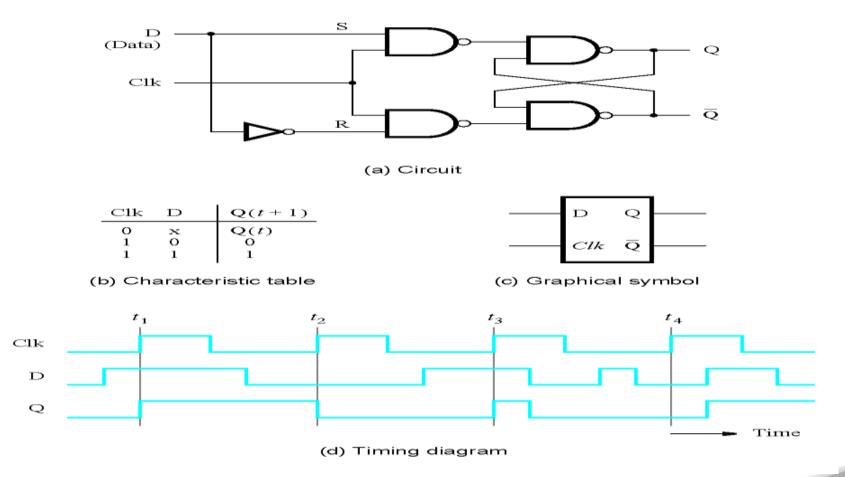

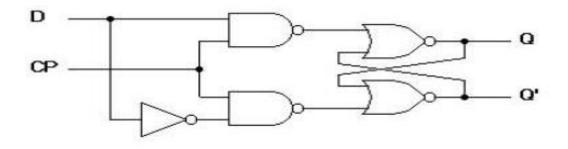

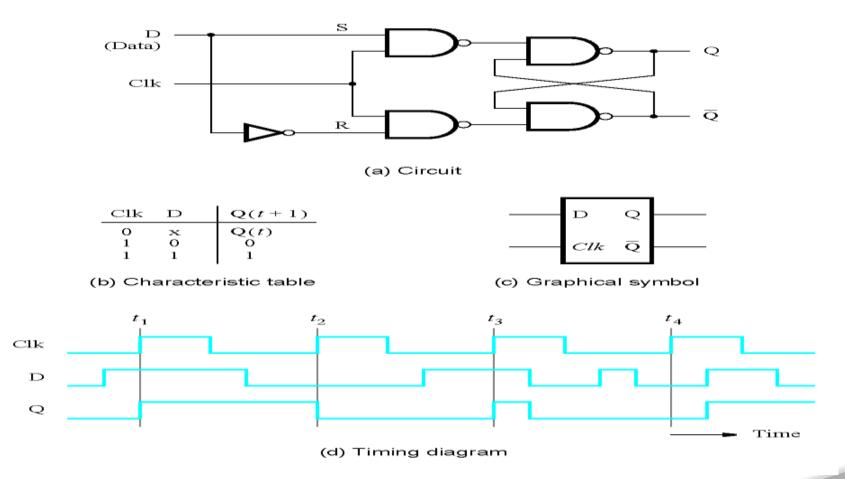

**D LATCH:**

- A flip-flop is a storage element based on the gated latch principle.

- It can have its output state changed onlyon the edge of the controlling clocksignal.

- Types Of Flip-flops:

- SR flip-flop (Set, Reset)

- T flip-flop (Toggle)

- D flip-flop (Delay)

- JK flip-flop

- Edge-triggered flip-flop is affected only by the input values present when the active edge of the clock occurs

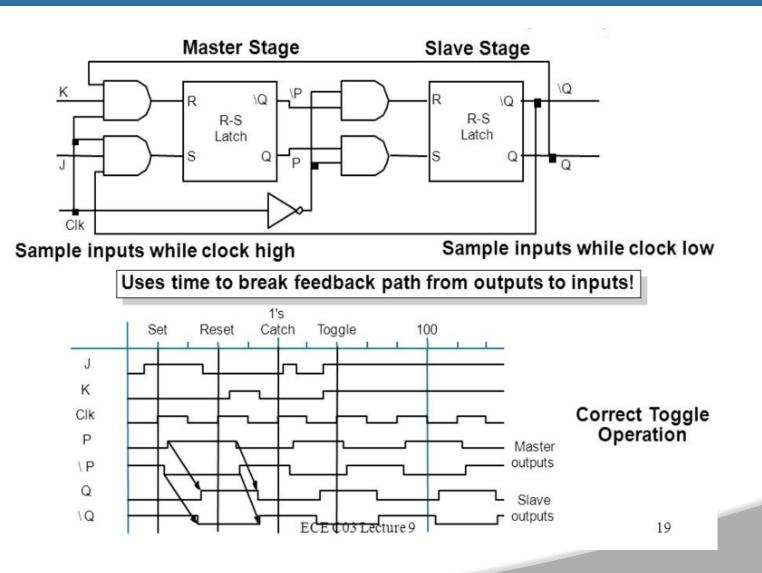

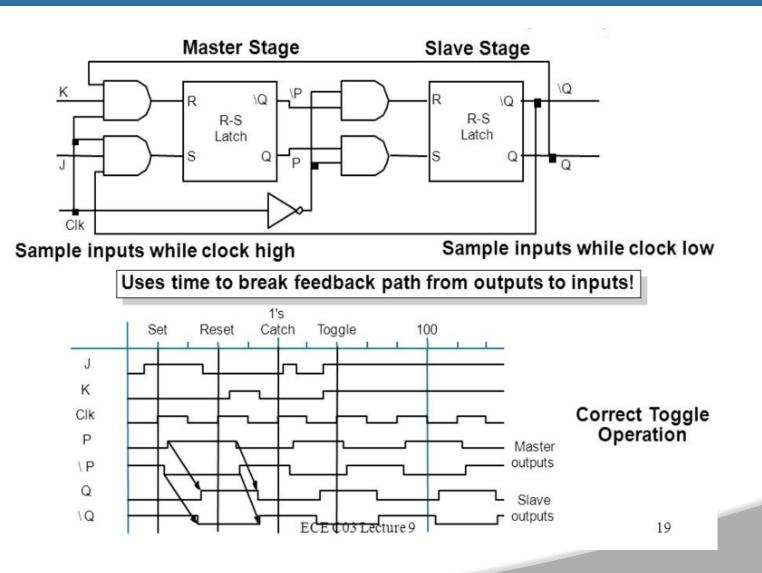

- Master-slave flip-flop is built with two gated

latches

- The master stage is active during half of the clock cycle, and the slave stage is active during the other half.

- The output value of the flip-flop changes on the edge of the clock that activates the transfer into the slave stage

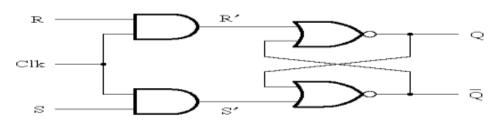

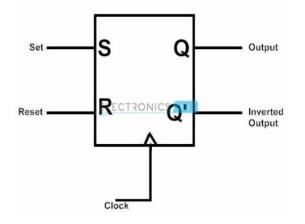

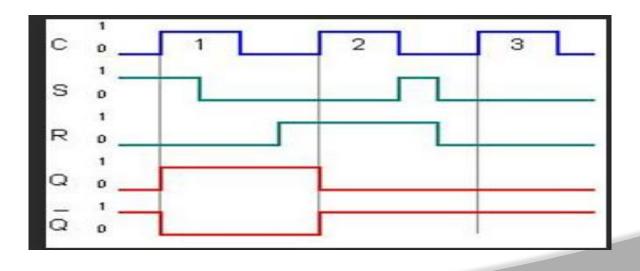

# SR Flip flop

|          | INPUTS |   | OUTPU        | STATE         |

|----------|--------|---|--------------|---------------|

| CLK      | S      | R | Q            |               |

| Х        | 0      | 0 | No<br>Change | Previous      |

| <b>↑</b> | 0      | 1 | 0            | Reset         |

| <b>•</b> | 1      | 0 | 1            | Set           |

| Ť        | 1      | 1 | -            | Forbidde<br>n |

# SR FLIPFLOP Excitation Table & Timing Diagram

|     |      | SR FLIP-F | LOP   |        |     |

|-----|------|-----------|-------|--------|-----|

|     | Q(t) | Q(t+1)    | S     | R      |     |

|     | 0    | 0         | 0     | х      |     |

|     | ο    | 1         | 1     | Ο      |     |

|     | 1    | Ο         | Ο     | 1      |     |

|     | 1    | 1         | ×     | Ο      |     |

| EXC |      | N TABLE C | DF SR | FLIP-F | LOP |

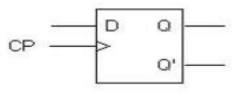

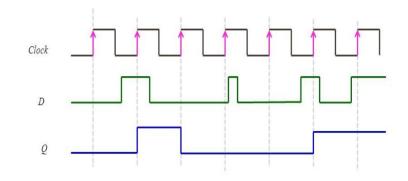

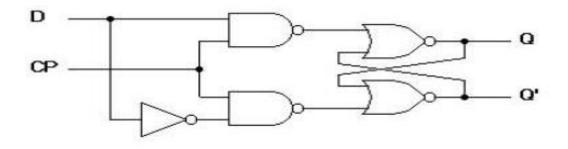

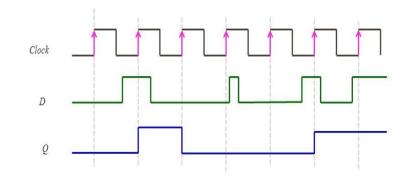

# D FLIPFLOP:

(a) Logic diagram with NAND gates

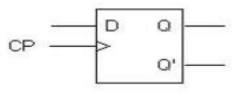

(b) Graphical symbol

| QD  | Q(t+1) |

|-----|--------|

| 0 0 | 0      |

| 0 1 | 1      |

| 10  | 0      |

| 11  | 1      |

(c) Transition table

# D FLIPFLOP Excitation Table & Timing Diagram:

| Present<br>state $(Q_n)$ | Next state $(Q_{n+1})$ | D |

|--------------------------|------------------------|---|

| 0                        | 0                      | 0 |

| 0                        | 1                      | 1 |

| 1                        | 0                      | 0 |

| 1                        | 1                      | 1 |

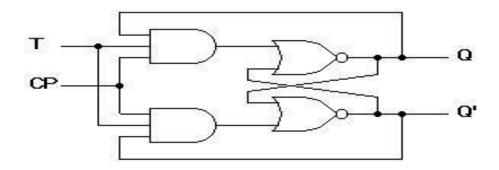

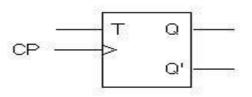

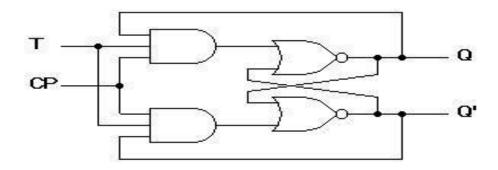

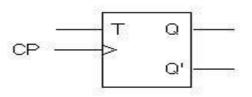

# T FLIPFLOP :

(a) Logic diagram

(b) Graphical symbol

| QT  | Q(t+1) |

|-----|--------|

| 0 0 | 0      |

| 01  | 1      |

| 10  | 1      |

| 11  | 0      |

(c) Transition table

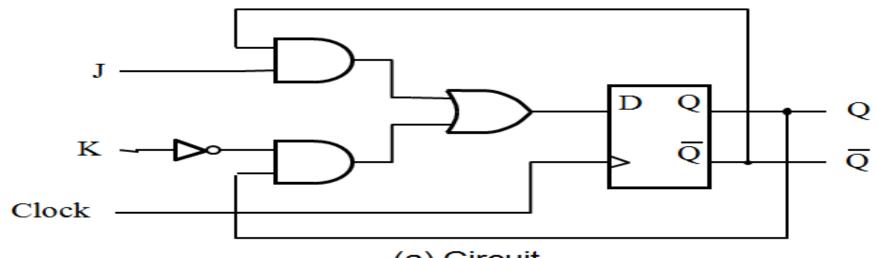

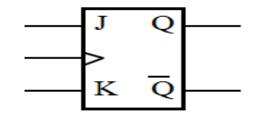

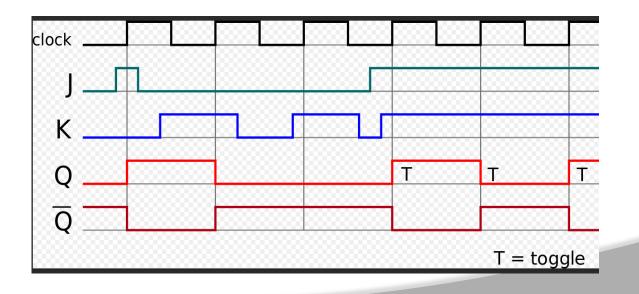

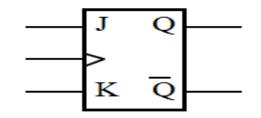

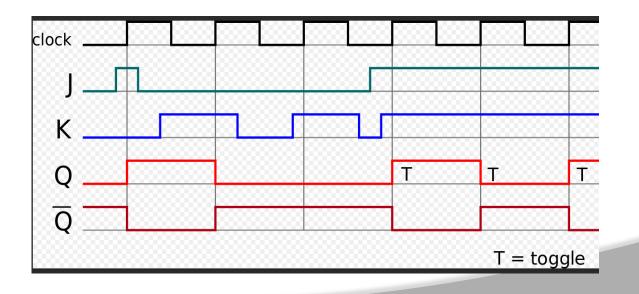

**JK FLIPFLOP**

(a) Circuit

| ЈК  | Q(t+1)            |

|-----|-------------------|

| 0 0 | Q(t)              |

| 0 1 | 0                 |

| 1 0 | 1                 |

| 1 1 | $\overline{Q}(t)$ |

(b) Characteristic table (c) Graphical symbol

# **JK FLIPFLOP**

| Q Output         |               | Inputs         |    |

|------------------|---------------|----------------|----|

| Present<br>State | Next<br>State | J <sub>n</sub> | Kn |

| 0                | 0             | 0              | x  |

| 0                | 1             | 1              | x  |

| 1                | 0             | x              | 1  |

| 1                | 1             | x              | 0  |

# **Master Slave JK FLIPFLOP**

- 1. Draw the block diagram of the target flip flop from the given problem.

- 2. Write truth table for the target flip-flop.

- Write excitation table for the available flipflop.

- 4. Draw k-map for target flip-flop.

- 5. Draw the block diagram.

# Jk to SR FLIPFLOP:

| S             | R   | Q(t+1)                            | Ope               | eration                           | →J  | K        | Q(t+1)            | Operation             |

|---------------|-----|-----------------------------------|-------------------|-----------------------------------|-----|----------|-------------------|-----------------------|

| 0             | 0   | Q(t)                              | No                | change                            | 0   | 0        | Q(t)              | No change             |

| 0             | 1   | 0                                 | Rese              | et                                | → 0 | 1        | 0                 | Reset                 |

| 1             | 0   | 1                                 | Set               |                                   | 1   | 0        | 1                 | Set                   |

| 1             | 1   | ?                                 | Und               | efined                            | 1   | 1        | $\overline{Q}(t)$ | Complement            |

| C             | ha  | racteri                           | istic             | Equation                          |     | Г        |                   | (Toggle)              |

|               |     |                                   |                   |                                   |     |          |                   |                       |

|               |     | Q(t+                              | 1) = .            | $J \overline{Q} + \overline{K} Q$ |     | L        | $\Box$            |                       |

| E             | kci | Q(t+<br>tation                    |                   |                                   |     | J-       | Dj                | D                     |

| E2<br>Q(1     |     | tation                            | Tab               |                                   |     | J-<br>K- | Dj<br>Def         |                       |

|               |     | tation                            | Tab<br>J K        | ole                               |     | J-<br>K- |                   | $\sum D$<br>$\sum -C$ |

| 2(1<br>0<br>0 | )   | <b>tation</b><br>Q(t+1)<br>0<br>1 | Tab<br>J K        | Operation                         |     | J-<br>K- |                   | → D<br>→ C            |

| 2(1<br>0<br>0 | )   | tation<br>Q(t+1)                  | Tab<br>J K<br>0 X | Operation<br>No change            |     | J-<br>K- |                   | $\sum D$<br>$\sum -C$ |

| Flip-flop | Characteristic Equation    |

|-----------|----------------------------|

| D         | Q(t+1) = D                 |

| Т         | $Q(t{+}1) = T \oplus Q(t)$ |

| SR        | Q(t+1) = S + R' Q(t)       |

| JK        | Q(t+1) = J Q(t)' + K' Q(t) |

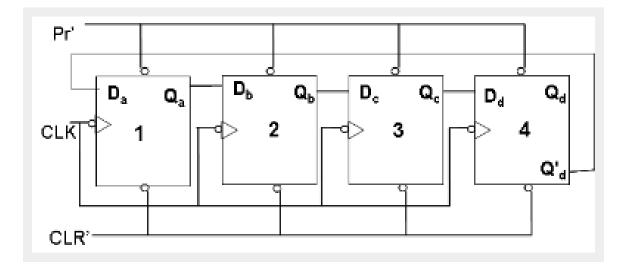

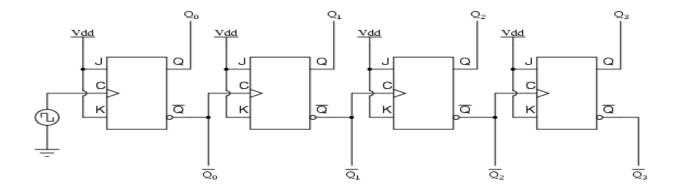

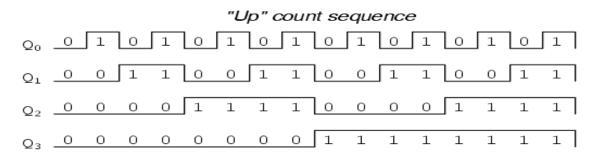

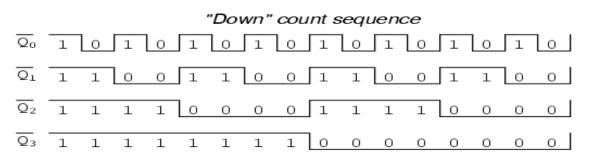

#### **Counters:**

- > Counters are a specific type of sequential circuit.

- Like registers, the state, or the flip-flop values themselves, serves as the "output."

- > The output value increases by one on each clock cycle.

- > After the largest value, the output "wraps around" back to 0.

- > Counters can act as simple clocks to keep track of "time."

- You may need to record how many times something has happened.

- How many bits have been sent or received?

- How many steps have been performed in some computation?

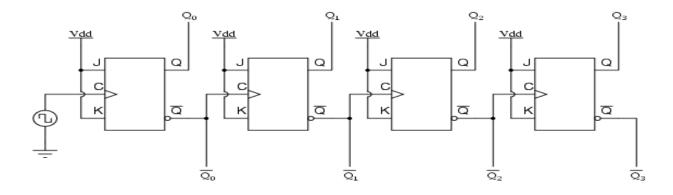

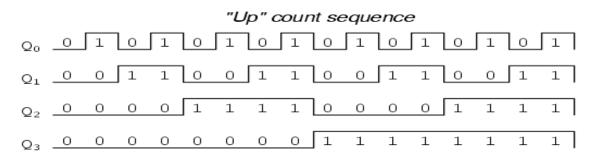

Asynchronous counter created from two JK flip-flops An asynchronous (ripple) counter is a single d-type flip-flop, with its J (data) input fed from its own inverted output. This circuit can store one bit, and hence can count from zero to one before it overflows (starts over from 0).

# **Asynchronous Up/Down Counters:**

The counters which use clock signal to change their transition are called "Synchronous counters". This means the synchronous counters depends on their clock input to change state values. In synchronous counters, all flip flops are connected to the same clock signal and all flip flops will trigger at the same time.

### Types of Counters:

- Binary counters

- 4 bit synchronous UP counter

- 4 bit synchronous DOWN counter

- 4 bit synchronous UP / DOWN counter

- Loadable counters

- BCD counters

- Ring counters

- > Johnson counters etc.

#### **Johnson Counters:**

| Johnson counter |    |           |    |    |  |

|-----------------|----|-----------|----|----|--|

| State           | Q0 | <b>Q1</b> | Q2 | Q3 |  |

| 0               | 0  | 0         | 0  | 0  |  |

| 1               | 1  | 0         | 0  | 0  |  |

| 2               | 1  | 1         | 0  | 0  |  |

| 3               | 1  | 1         | 1  | 0  |  |

| 4               | 1  | 1         | 1  | 1  |  |

| 5               | 0  | 1         | 1  | 1  |  |

| 6               | 0  | 0         | 1  | 1  |  |

| 7               | 0  | 0         | 0  | 1  |  |

| 0               | 0  | 0         | 0  | 0  |  |

#### **Ring Counters:**

| Straight ring counter |    |    |    |    |  |

|-----------------------|----|----|----|----|--|

| State                 | QO | Q1 | Q2 | Q3 |  |

| 0                     | 1  | 0  | 0  | 0  |  |

| 1                     | 0  | 1  | 0  | 0  |  |

| 2                     | 0  | 0  | 1  | 0  |  |

| 3                     | 0  | 0  | 0  | 1  |  |

| 0                     | 1  | 0  | 0  | 0  |  |

| 1                     | 0  | 1  | 0  | 0  |  |

| 2                     | 0  | 0  | 1  | 0  |  |

| 3                     | 0  | 0  | 0  | 1  |  |

| 0                     | 1  | 0  | 0  | 0  |  |

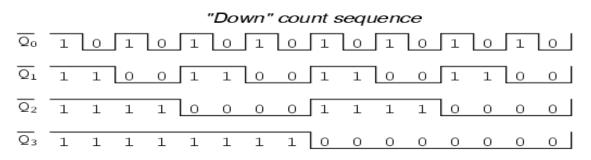

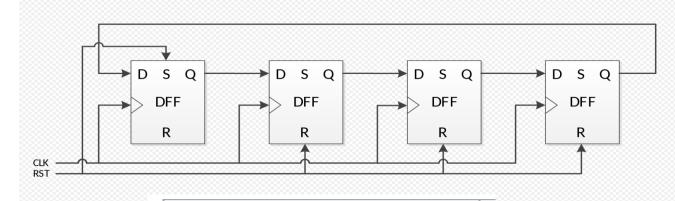

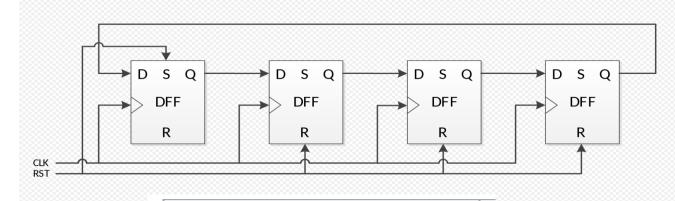

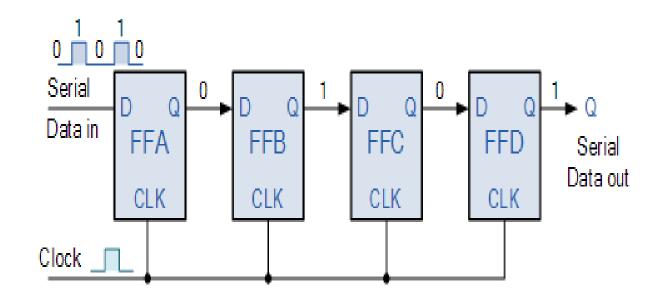

Shift registers, like counters, are a form of sequential logic. Sequential logic, unlike Combinational Logic is not only affected by the present inputs, but also, by the prior history. In other words, sequential logic remembers past events.

### Types of Shift Registers:

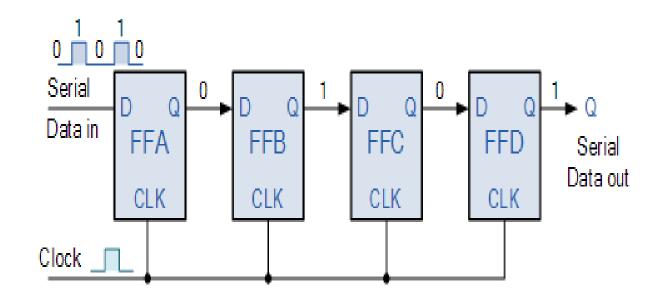

- Serial-in/serial-out

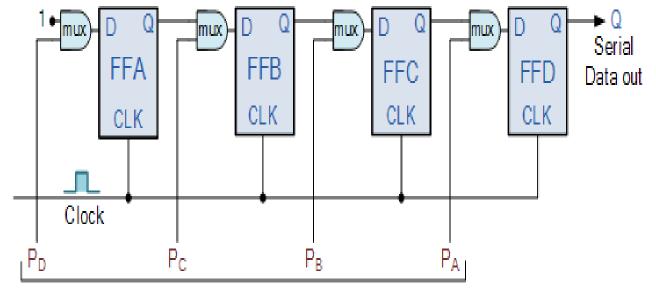

- Parallel-in/serial-out

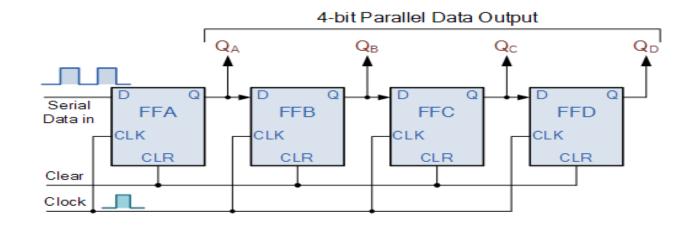

- Serial-in/parallel-out

- Universal parallel-in/parallel-out

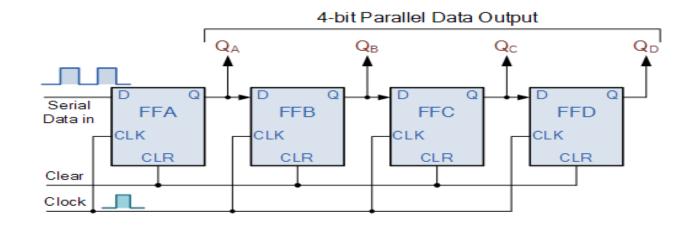

## Serial in to Parallel Output:

| Clock Pulse No | QA | QB | QC | QD |

|----------------|----|----|----|----|

| 0              | 0  | 0  | ο  | 0  |

| 1              | 1  | 0  | 0  | 0  |

| 2              | 0  | 1  | 0  | 0  |

| 3              | о  | о  | 1  | 0  |

| 4              | 0  | 0  | 0  | 1  |

| 5              | о  | 0  | 0  | 0  |

#### Serial in to Serial Output:

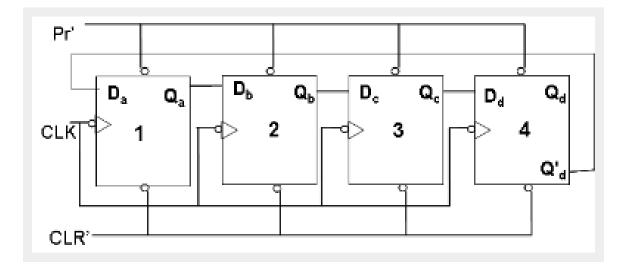

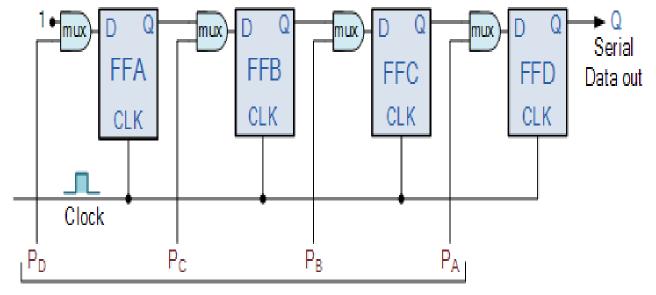

### **Parallel in to Serial Output:**

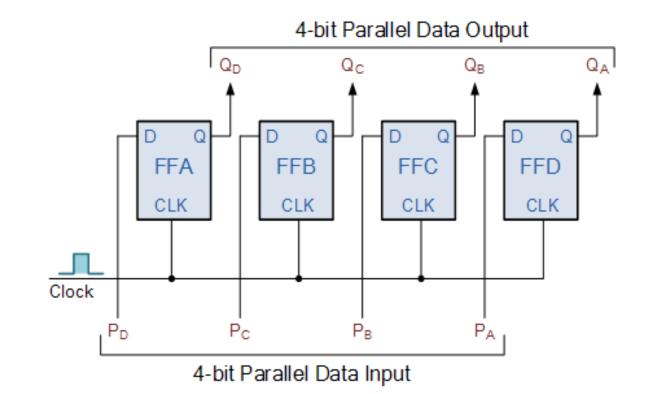

4-bit Parallel Data Input

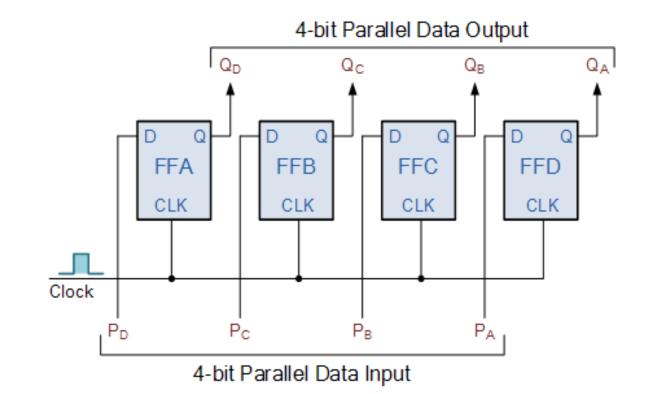

# **Parallel in to Parallel Output:**

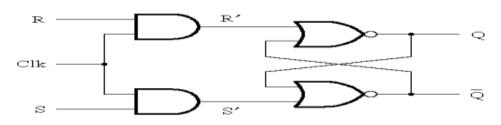

**RS LATCH:**

(a) Circuit

| Clk | S | R | Q(t+1)           |

|-----|---|---|------------------|

| 0   | × | × | Q(1) (no change) |

| 1   | 0 | 0 | Q(t) (no change) |

| 1   | 0 | 1 | 0                |

| 1   | 1 | 0 | 1                |

| 1   | 1 | 1 | ×                |

|     |   |   |                  |

#### (b) Characteristic table

#### (c) Timing diagram

(d) Graphical symbol

**D LATCH:**

- A flip-flop is a storage element based on the gated latch principle.

- It can have its output state changed onlyon the edge of the controlling clocksignal.

- Types Of Flip-flops:

- SR flip-flop (Set, Reset)

- T flip-flop (Toggle)

- D flip-flop (Delay)

- JK flip-flop

- Edge-triggered flip-flop is affected only by the input values present when the active edge of the clock occurs

- Master-slave flip-flop is built with two gated

- latches

- The master stage is active during half of the clock cycle, and the slave stage is active during the other half.

- The output value of the flip-flop changes on the edge of the clock that activates the transfer into the slave stage

# SR Flip flop

|          | INPUTS | OUTPU | STATE        |               |

|----------|--------|-------|--------------|---------------|

| CLK      | S      | R     | Q            |               |

| Х        | 0      | 0     | No<br>Change | Previous      |

| <b>↑</b> | 0      | 1     | 0            | Reset         |

| <b>•</b> | 1      | 0     | 1            | Set           |

| ŕ        | 1      | 1     | -            | Forbidde<br>n |

# SR FLIPFLOP Excitation Table & Timing Diagram

|     |      | SR FLIP-F | LOP |        |     |

|-----|------|-----------|-----|--------|-----|

|     | Q(t) | Q(t+1)    | S   | R      |     |

|     | 0    | 0         | Ο   | ×      |     |

|     | ο    | 1         | 1   | ο      |     |

|     | 1    | Ο         | Ο   | 1      |     |

|     | 1    | 1         | ×   | ο      |     |

| FXC |      | N TABLE C |     | FLIP-F | IOP |

#### D FLIPFLOP:

(a) Logic diagram with NAND gates

(b) Graphical symbol

| QD  | Q(t+1) |

|-----|--------|

| 0 0 | 0      |

| 0 1 | 1      |

| 10  | 0      |

| 11  | 1      |

(c) Transition table

# D FLIPFLOP Excitation Table & Timing Diagram:

| Present       | Next state  | D |

|---------------|-------------|---|

| state $(Q_n)$ | $(Q_{n+1})$ |   |

| 0             | 0           | 0 |

| 0             | 1           | 1 |

| 1             | 0           | 0 |

| 1             | 1           | 1 |

#### T FLIPFLOP :

(a) Logic diagram

(b) Graphical symbol

| QT  | Q(t+1) |

|-----|--------|

| 0 0 | 0      |

| 01  | 1      |

| 10  | 1      |

| 11  | 0      |

(c) Transition table

**JK FLIPFLOP**

(a) Circuit

| JK  | Q(t+1)            |

|-----|-------------------|

| 0 0 | Q(t)              |

| 0 1 | 0                 |

| 1 0 | 1                 |

| 1 1 | $\overline{Q}(t)$ |

(b) Characteristic table (c) Graphical symbol

# JK FLIPFLOP

| Q Out            | Inputs        |                |    |

|------------------|---------------|----------------|----|

| Present<br>State | Next<br>State | J <sub>n</sub> | Kn |

| 0                | 0             | 0              | x  |

| 0                | 1             | 1              | x  |

| 1                | 0             | x              | 1  |

| 1                | 1             | x              | 0  |

### **Master Slave JK FLIPFLOP**

# Jk to SR FLIPFLOP:

| S             | R   | Q(t+1)                            | Ope               | eration                           | → J | K        | Q(t+1)            | Operation            |

|---------------|-----|-----------------------------------|-------------------|-----------------------------------|-----|----------|-------------------|----------------------|

| 0             | 0   | Q(t)                              | No                | change                            | 0   | 0        | Q(t)              | No change            |

| 0             | 1   | 0                                 | Rese              | et —                              | → 0 | 1        | 0                 | Reset                |

| 1             | 0   | 1                                 | Set               |                                   | 1   | 0        | 1                 | Set                  |

| 1             | 1   | ?                                 | Und               | efined                            | 1   | 1        | $\overline{Q}(t)$ | Complement           |

| C             | ha  | racteri                           | istic             | Equation                          |     | Г        |                   | (Toggle)             |

|               |     |                                   |                   |                                   |     |          |                   |                      |

|               |     | Q(t+                              | 1) = .            | $J \overline{Q} + \overline{K} Q$ |     |          |                   |                      |

| E             | kci | Q(t+<br>tation                    |                   |                                   |     | J-       | Dj                | D                    |

| E2<br>Q(1     |     | tation                            | Tab               |                                   |     | J-<br>K- | Dj<br>Dr          |                      |

|               |     | tation                            | Tab<br>J K        | ole                               |     | J-<br>K- |                   | → D<br>→ C           |

| 2(1<br>0<br>0 | )   | <b>tation</b><br>Q(t+1)<br>0<br>1 | Tab<br>J K        | Operation                         |     | J-<br>K- |                   | → D<br>→ C           |

| 2(1<br>0<br>0 | )   | tation<br>Q(t+1)                  | Tab<br>J K<br>0 X | Operation<br>No change            |     | J-<br>K- |                   | $\sum D$<br>$\sum C$ |

| Flip-flop | Characteristic Equation    |

|-----------|----------------------------|

| D         | Q(t+1) = D                 |

| Т         | $Q(t{+}1) = T \oplus Q(t)$ |

| SR        | Q(t+1) = S + R' Q(t)       |

| JK        | Q(t+1) = J Q(t)' + K' Q(t) |

# **Asynchronous Up/Down Counters:**

#### **Johnson Counters:**

| Johnson counter |    |           |    |    |  |  |  |

|-----------------|----|-----------|----|----|--|--|--|

| State           | Q0 | <b>Q1</b> | Q2 | Q3 |  |  |  |

| 0               | 0  | 0         | 0  | 0  |  |  |  |

| 1               | 1  | 0         | 0  | 0  |  |  |  |

| 2               | 1  | 1         | 0  | 0  |  |  |  |

| 3               | 1  | 1         | 1  | 0  |  |  |  |

| 4               | 1  | 1         | 1  | 1  |  |  |  |

| 5               | 0  | 1         | 1  | 1  |  |  |  |

| 6               | 0  | 0         | 1  | 1  |  |  |  |

| 7               | 0  | 0         | 0  | 1  |  |  |  |

| 0               | 0  | 0         | 0  | 0  |  |  |  |

#### **Ring Counters:**

| Straight ring counter |    |    |    |    |  |  |  |

|-----------------------|----|----|----|----|--|--|--|

| State                 | QO | Q1 | Q2 | Q3 |  |  |  |

| 0                     | 1  | 0  | 0  | 0  |  |  |  |

| 1                     | 0  | 1  | 0  | 0  |  |  |  |

| 2                     | 0  | 0  | 1  | 0  |  |  |  |

| 3                     | 0  | 0  | 0  | 1  |  |  |  |

| 0                     | 1  | 0  | 0  | 0  |  |  |  |

| 1                     | 0  | 1  | 0  | 0  |  |  |  |

| 2                     | 0  | 0  | 1  | 0  |  |  |  |

| 3                     | 0  | 0  | 0  | 1  |  |  |  |

| 0                     | 1  | 0  | 0  | 0  |  |  |  |

### Serial in to Parallel Output:

| Clock Pulse No | QA | QB | QC | QD |

|----------------|----|----|----|----|

| 0              | ο  | 0  | 0  | 0  |

| 1              | 1  | 0  | 0  | 0  |

| 2              | 0  | 1  | 0  | 0  |

| 3              | о  | 0  | 1  | 0  |

| 4              | о  | 0  | 0  | 1  |

| 5              | о  | 0  | 0  | 0  |

#### Serial in to Serial Output:

### **Parallel in to Serial Output:**

4-bit Parallel Data Input

# **Parallel in to Parallel Output:**

# **Unit-IV** A/D AND D/A CONVERTERS

#### Introduction:

- ➤ In electronics a digital to analog converter is a system that converts a digital signal into analog signal.

- An analog to digital converter is a system that converts a analog signal into digital signal.

# Data Converters:

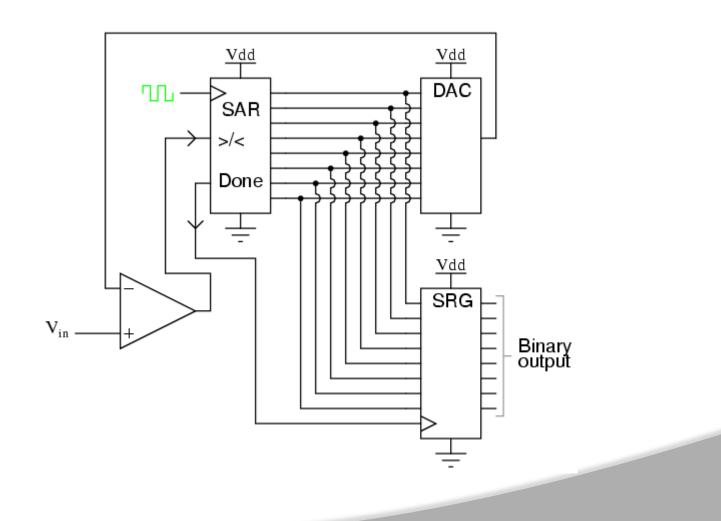

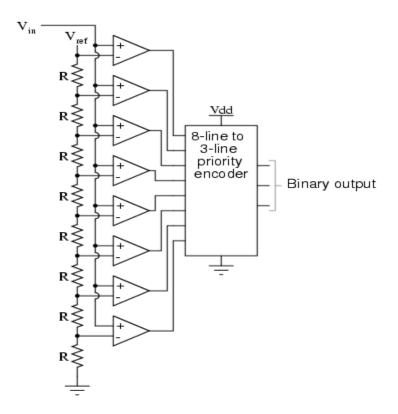

- Classification of ADCs

- Direct type ADC.

- Integrating type ADC

- Direct type ADCs

- Flash (comparator) type converter

- Counter type converter

- Tracking or servo converter.

- Successive approximation type converter

#### Integrating type converters:

An ADC converter that perform conversion in an indirect manner by first changing the analog I/P signal to a linear function of time or frequency and then to a digital code is known as integrating type A/D converter.

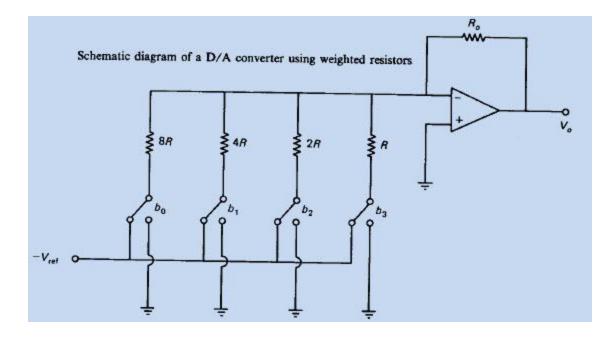

# **DAC TECHNIQUES:**

- Weighted resistor DAC

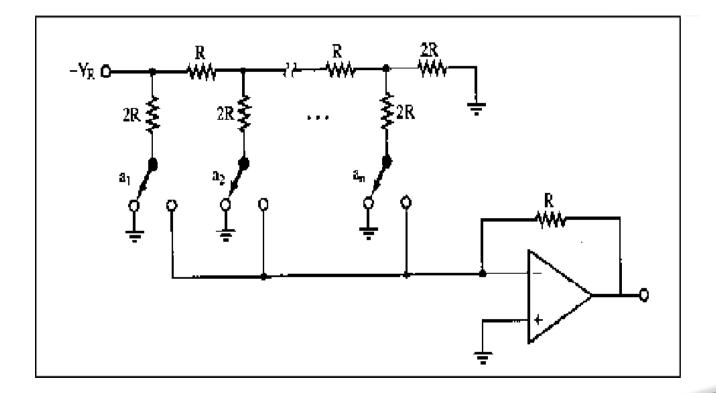

- ➢ R-2R ladder DAC

- Inverted R-2R ladder DAC

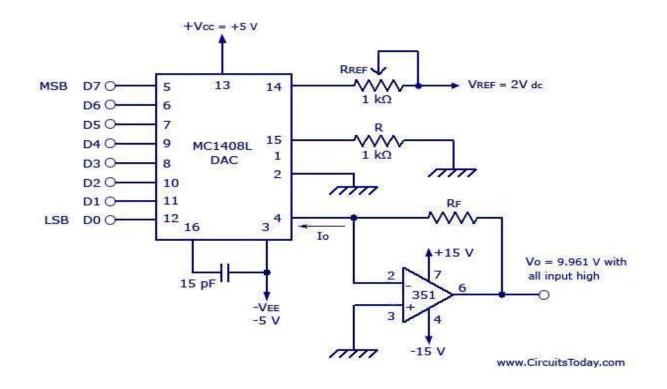

- ➢ IC 1408 DAC

**DAC TECHNIQUES:**

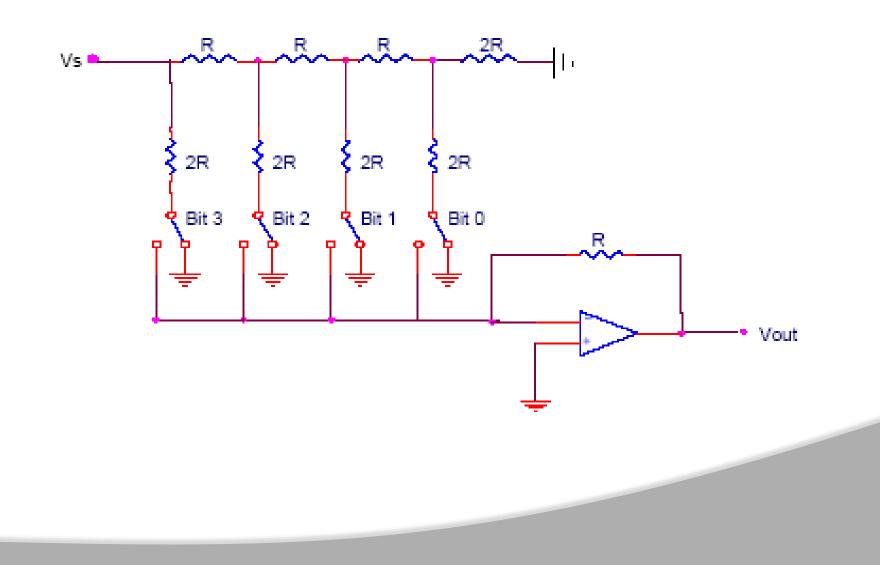

# Weighted Resistor DAC

**DAC TECHNIQUES:**

#### Inverted R-2R DAC

## **INVERTED R-2R DAC:**

IC 1408 DAC

MC1408 D/A Converter With Current Output

# **INVERTED R-2R DAC:**

### IC 1408 DAC Specifications:

- Resolution

- Non-linearity or Linearity Error

- Gain error and Offset Error

- Settling Time

# **INVERTED R-2R DAC:**

#### IC 1408 DAC Applications:

- Microcomputer interfacing

- CRT Graphics Generation

- Programmable Power Supplies

- Digitally controlled gain circuits

- Digital Filters

2 0 0 0

#### **DAC characteristics:**

- Resolution

- Reference Voltage

- Speed

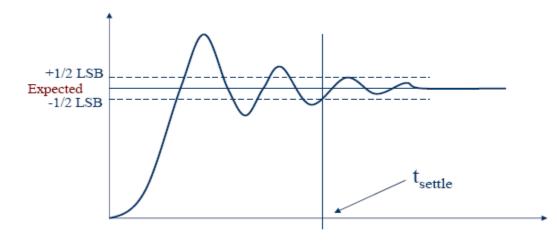

- Settling Time

- ➤ Linearity

#### **Resolution:**

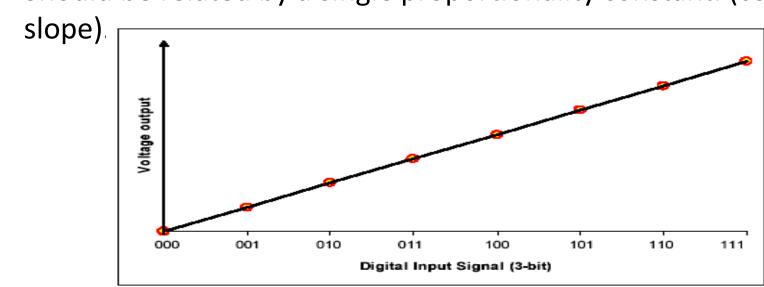

- > The change in output voltage for a change of the LSB.

- Related to the size of the binary representation of the voltage. (8bit)

- Higher resolution results in smaller steps between voltage values

#### **Reference Voltage:**

> Multiplier DAC

-Reference voltage is a constant set by the manufacturer

> Non-Multiplier DAC

-Reference voltage is variable