## INSTITUTE OF AERONAUTICAL ENGINEERING

(Autonomous) Dundigal, Hyderabad - 500 043

## Lab Manual:

# DIGITAL SYSTEM DESIGN LABORATORY (AECC06)

Prepared by

Ms S. Sushma (IARE10513)

ELECTRONICS AND COMMUNICATION ENGINEERING INSTITUTE OF AERONAUTICAL ENGINEERING

December 7, 2021

# Contents

| C | Content                                              |  |      |  |  |  |  |  |

|---|------------------------------------------------------|--|------|--|--|--|--|--|

| 1 |                                                      |  | 1    |  |  |  |  |  |

|   | 1.1 Introduction                                     |  |      |  |  |  |  |  |

|   | 1.1.1 Student Responsibilities                       |  |      |  |  |  |  |  |

|   | 1.1.2 Laboratory Teaching Assistant Responsibilities |  |      |  |  |  |  |  |

|   | 1.1.3 Faculty Coordinator Responsibilities           |  |      |  |  |  |  |  |

|   | 1.1.4 Lab Policy and Grading                         |  |      |  |  |  |  |  |

|   | 1.1.5 Course Goals and Objectives                    |  |      |  |  |  |  |  |

|   | 1.2 Use of Laboratory Instruments                    |  |      |  |  |  |  |  |

|   | 1.2.1 Instrument Protection Rules                    |  |      |  |  |  |  |  |

|   | 1.3 Data Recording and Reports                       |  |      |  |  |  |  |  |

|   | 1.3.1 The Laboratory Worksheets                      |  |      |  |  |  |  |  |

|   | 1.3.2 The Lab Report                                 |  | . 5  |  |  |  |  |  |

| 2 | LAB-1 ORIENTATION                                    |  | 7    |  |  |  |  |  |

|   | 2.1 Introduction                                     |  | . 7  |  |  |  |  |  |

|   | 2.2 Objective                                        |  | . 7  |  |  |  |  |  |

|   | 2.3 Prelab Preparation:                              |  | . 7  |  |  |  |  |  |

|   | 2.4 Equipment needed                                 |  | . 7  |  |  |  |  |  |

|   | 2.5 Procedure                                        |  | . 7  |  |  |  |  |  |

| 3 | LAB-2 REALIZATION OF A BOOLEAN FUNCTION              |  | 8    |  |  |  |  |  |

|   | 3.1 Introduction                                     |  | . 8  |  |  |  |  |  |

|   | 3.2 Objective                                        |  | . 8  |  |  |  |  |  |

|   | 3.3 Prelab                                           |  | . 8  |  |  |  |  |  |

|   | 3.4 Equipment needed                                 |  | . 8  |  |  |  |  |  |

|   | 3.5 Back ground                                      |  | . 8  |  |  |  |  |  |

|   | 3.6 Procedure                                        |  | . 8  |  |  |  |  |  |

|   | 3.7 VHDL Program                                     |  | . 9  |  |  |  |  |  |

|   | 3.8 Probing Further Experiments                      |  | . 10 |  |  |  |  |  |

| 4 | Lab 3 – DESIGN OF DECODER AND ENCODER                |  | 11   |  |  |  |  |  |

|   | 4.1 Introduction                                     |  | . 11 |  |  |  |  |  |

|   | 4.2 Objective                                        |  |      |  |  |  |  |  |

|   | 4.3 Prelab Preparation:                              |  |      |  |  |  |  |  |

|   | 4.4 Equipment needed                                 |  |      |  |  |  |  |  |

|   | 4.5 Background                                       |  |      |  |  |  |  |  |

|   | 4.6 Procedure                                        |  |      |  |  |  |  |  |

|   | 4.7 VHDL Program                                     |  |      |  |  |  |  |  |

|   | 4.8 Further Probing Experiments                      |  |      |  |  |  |  |  |

| _ | Lab 4 – DESIGN OF MULTIPLEXER AND DEMULTIPLEXER      |  | 16   |  |  |  |  |  |

|    | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8 | Introduction Objective Prelab Preparation: Equipment needed Background Procedure VHDL Program Further Probing Experiments | 16<br>16<br>16<br>16<br>16<br>18<br>18 |

|----|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 6  | Lab                                                  | 5 – DESIGN OF CODE CONVERTERS                                                                                             | 20                                     |

|    | 6.1                                                  | Introduction                                                                                                              | 20                                     |

|    | 6.2                                                  | Objective                                                                                                                 | 20                                     |

|    | 6.3                                                  | Prelab Preparation:                                                                                                       | 20                                     |

|    | 6.4                                                  | Equipment needed                                                                                                          | 20                                     |

|    | 6.5                                                  | Background                                                                                                                | 20                                     |

|    | 6.6                                                  | Procedure                                                                                                                 | 21                                     |

|    | 6.7                                                  | VHDL Program                                                                                                              |                                        |

|    | 6.8                                                  | Further Probing Experiments                                                                                               | 22                                     |

| 7  | LAI                                                  | B-6 FULL ADDER AND FULL SUBTRACTOR DESIGN MODELING                                                                        | 23                                     |

|    | 7.1                                                  | Introduction                                                                                                              | 23                                     |

|    | 7.2                                                  | Objective                                                                                                                 | 23                                     |

|    | 7.3                                                  | Prelab Preparation:                                                                                                       | 23                                     |

|    | 7.4                                                  | Equipment needed                                                                                                          | 23                                     |

|    | 7.5                                                  | Background                                                                                                                | 23                                     |

|    | 7.6                                                  | Procedure                                                                                                                 |                                        |

|    | 7.7                                                  | VHDL Program                                                                                                              |                                        |

|    | 7.8                                                  | Probing Further Experiments                                                                                               | 27                                     |

| 8  | LAI                                                  | B-7 DESIGN OF 8-BIT ARITHMETIC LOGIC UNIT                                                                                 | 28                                     |

|    | 8.1                                                  | Introduction                                                                                                              |                                        |

|    | 8.2                                                  | Objective                                                                                                                 |                                        |

|    | 8.3                                                  | Prelab                                                                                                                    |                                        |

|    | 8.4                                                  | Equipment needed                                                                                                          | 28                                     |

|    | 8.5                                                  | Back ground                                                                                                               | 28                                     |

|    | 8.6<br>8.7                                           | Procedure                                                                                                                 | 30                                     |

|    | 8.8                                                  | Probing Further Experiments                                                                                               | 31                                     |

| _  |                                                      |                                                                                                                           |                                        |

| 9  |                                                      | B-8 HDL MODEL FOR FLIP FLOPS                                                                                              | 32                                     |

|    | 9.1<br>9.2                                           | Introduction                                                                                                              | $\frac{32}{32}$                        |

|    | 9.2                                                  | Objective                                                                                                                 | $\frac{32}{32}$                        |

|    | 9.3                                                  | Equipment needed                                                                                                          | $\frac{32}{32}$                        |

|    | 9.5                                                  | Back ground                                                                                                               | $\frac{32}{32}$                        |

|    | 9.6                                                  | Procedure                                                                                                                 | $\frac{32}{33}$                        |

|    | 9.7                                                  | VHDL Program                                                                                                              | 33                                     |

|    | 9.8                                                  | Probing Further Experiments                                                                                               | 35                                     |

| 10 |                                                      |                                                                                                                           |                                        |

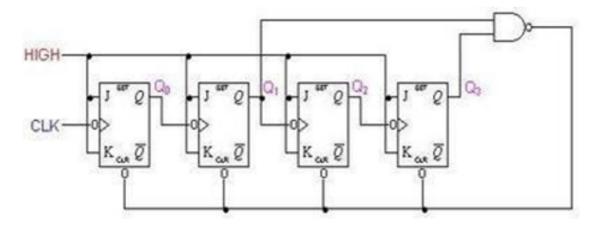

|    | T. A T                                               | R-9 DESIGN OF COUNTERS                                                                                                    | 34                                     |

| 10 |                                                      | B-9 DESIGN OF COUNTERS Introduction                                                                                       | <b>36</b>                              |

|           | 10.3 Prelab                                                                                                                                                                                                                                                                                                                                                                                                       | 36                                                                                                 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|           | 10.4 Equipment needed                                                                                                                                                                                                                                                                                                                                                                                             | 36                                                                                                 |

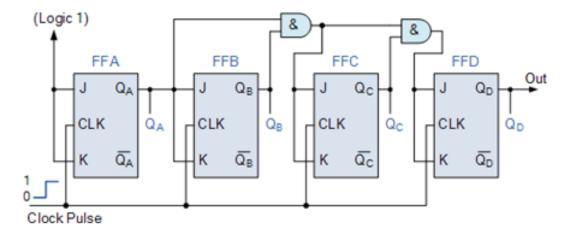

|           | 10.5 Back ground                                                                                                                                                                                                                                                                                                                                                                                                  | 36                                                                                                 |

|           | 10.6 Procedure                                                                                                                                                                                                                                                                                                                                                                                                    | 38                                                                                                 |

|           | 10.7 VHDL Program                                                                                                                                                                                                                                                                                                                                                                                                 | 36                                                                                                 |

|           | 10.8 Probing Further Experiments                                                                                                                                                                                                                                                                                                                                                                                  | 41                                                                                                 |

| 11        | LAB-10 HDL CODE FOR UNIVERSAL SHIFT REGISTER                                                                                                                                                                                                                                                                                                                                                                      | 42                                                                                                 |

|           | 11.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                 | 42                                                                                                 |

|           | 11.2 Objective                                                                                                                                                                                                                                                                                                                                                                                                    | 42                                                                                                 |

|           | 11.3 Prelab                                                                                                                                                                                                                                                                                                                                                                                                       | 42                                                                                                 |

|           | 11.4 Equipment needed                                                                                                                                                                                                                                                                                                                                                                                             | 42                                                                                                 |

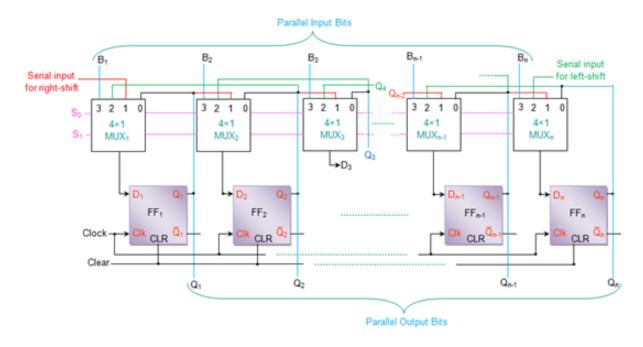

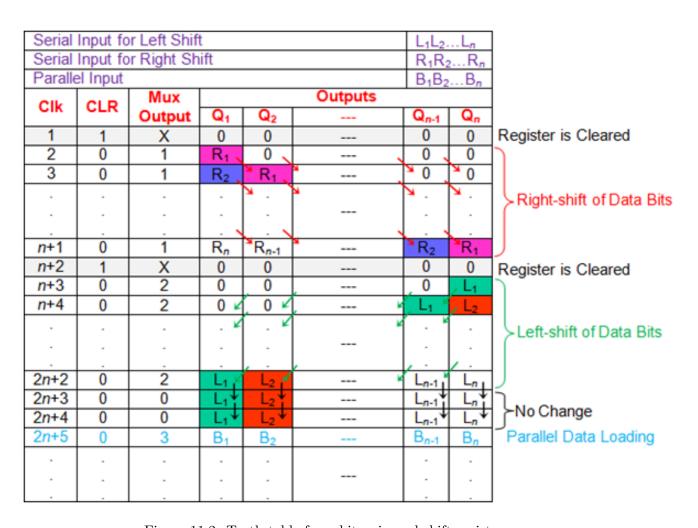

|           | 11.5 Back ground                                                                                                                                                                                                                                                                                                                                                                                                  | 42                                                                                                 |

|           | 11.6 Procedure                                                                                                                                                                                                                                                                                                                                                                                                    | 45                                                                                                 |

|           | 11.7 VHDL Program                                                                                                                                                                                                                                                                                                                                                                                                 | 45                                                                                                 |

|           | 11.8 Probing Further Experiments                                                                                                                                                                                                                                                                                                                                                                                  | 47                                                                                                 |

| <b>12</b> | Lab 11 – HDL CODE FOR CARRY LOOK AHEAD ADDER                                                                                                                                                                                                                                                                                                                                                                      | 48                                                                                                 |

|           | 12.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                 | 48                                                                                                 |

|           | 12.2 Objective                                                                                                                                                                                                                                                                                                                                                                                                    | 48                                                                                                 |

|           | 12.3 Prelab Preparation:                                                                                                                                                                                                                                                                                                                                                                                          | 48                                                                                                 |

|           | 12.4 Equipment needed                                                                                                                                                                                                                                                                                                                                                                                             | 48                                                                                                 |

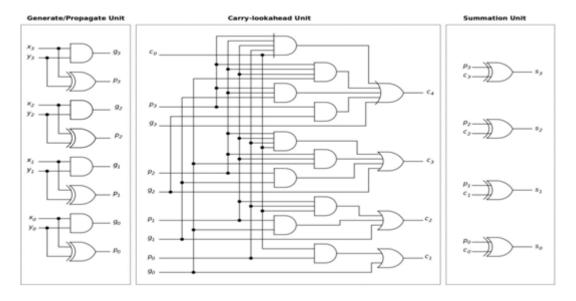

|           | 12.5 Background                                                                                                                                                                                                                                                                                                                                                                                                   | 48                                                                                                 |

|           | 12.6 Procedure                                                                                                                                                                                                                                                                                                                                                                                                    | 50                                                                                                 |

|           | 12.7 VHDL Program                                                                                                                                                                                                                                                                                                                                                                                                 | 50                                                                                                 |

|           | 12.8 Further Probing Experiments                                                                                                                                                                                                                                                                                                                                                                                  | 52                                                                                                 |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                   | 02                                                                                                 |

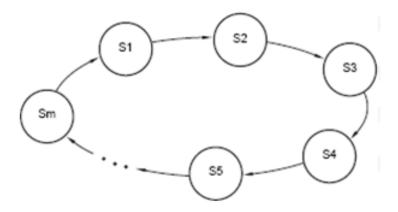

| 13        | LAB-12 HDL CODE TO DETECT A SEQUENCE                                                                                                                                                                                                                                                                                                                                                                              | 53                                                                                                 |

| 13        |                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                    |

| 13        | LAB-12 HDL CODE TO DETECT A SEQUENCE                                                                                                                                                                                                                                                                                                                                                                              | 53                                                                                                 |

| 13        | LAB-12 HDL CODE TO DETECT A SEQUENCE 13.1 Introduction                                                                                                                                                                                                                                                                                                                                                            | <b>53</b> 53 53                                                                                    |

| 13        | LAB-12 HDL CODE TO DETECT A SEQUENCE  13.1 Introduction                                                                                                                                                                                                                                                                                                                                                           | 53<br>53<br>53<br>53                                                                               |

| 13        | LAB-12 HDL CODE TO DETECT A SEQUENCE  13.1 Introduction                                                                                                                                                                                                                                                                                                                                                           | 53<br>53<br>53<br>53<br>53                                                                         |

| 13        | LAB-12 HDL CODE TO DETECT A SEQUENCE  13.1 Introduction                                                                                                                                                                                                                                                                                                                                                           | 53<br>53<br>53<br>53<br>53<br>55                                                                   |

| 13        | LAB-12 HDL CODE TO DETECT A SEQUENCE  13.1 Introduction                                                                                                                                                                                                                                                                                                                                                           | 53<br>53<br>53<br>53<br>53<br>55<br>55                                                             |

| 13        | LAB-12 HDL CODE TO DETECT A SEQUENCE  13.1 Introduction                                                                                                                                                                                                                                                                                                                                                           | 53<br>53<br>53<br>53<br>53<br>55                                                                   |

|           | LAB-12 HDL CODE TO DETECT A SEQUENCE  13.1 Introduction                                                                                                                                                                                                                                                                                                                                                           | 53<br>53<br>53<br>53<br>53<br>55<br>55                                                             |

|           | LAB-12 HDL CODE TO DETECT A SEQUENCE  13.1 Introduction 13.2 Objective 13.3 Prelab Preparation: 13.4 Equipment needed 13.5 Background 13.6 Procedure 13.7 VHDL Program 13.8 Probing Further Experiments                                                                                                                                                                                                           | 53<br>53<br>53<br>53<br>55<br>55<br>55<br>57                                                       |

|           | LAB-12 HDL CODE TO DETECT A SEQUENCE  13.1 Introduction  13.2 Objective  13.3 Prelab Preparation:  13.4 Equipment needed  13.5 Background  13.6 Procedure  13.7 VHDL Program  13.8 Probing Further Experiments  Lab 13 - HDL CODE TO DETECT A SEQUENCE  14.1 Introduction  14.2 Objective                                                                                                                         | 53<br>53<br>53<br>53<br>55<br>55<br>57<br>58<br>58                                                 |

|           | LAB-12 HDL CODE TO DETECT A SEQUENCE  13.1 Introduction 13.2 Objective 13.3 Prelab Preparation: 13.4 Equipment needed 13.5 Background 13.6 Procedure 13.7 VHDL Program 13.8 Probing Further Experiments  Lab 13 - HDL CODE TO DETECT A SEQUENCE 14.1 Introduction 14.2 Objective 14.3 Prelab Preparation:                                                                                                         | 53<br>53<br>53<br>53<br>55<br>55<br>57<br>58<br>58<br>58                                           |

|           | LAB-12 HDL CODE TO DETECT A SEQUENCE  13.1 Introduction 13.2 Objective 13.3 Prelab Preparation: 13.4 Equipment needed 13.5 Background 13.6 Procedure 13.7 VHDL Program 13.8 Probing Further Experiments  Lab 13 - HDL CODE TO DETECT A SEQUENCE 14.1 Introduction 14.2 Objective 14.3 Prelab Preparation: 14.4 Equipment needed                                                                                   | 53<br>53<br>53<br>53<br>53<br>55<br>55<br>56<br>57<br>58<br>58<br>58<br>58                         |

|           | LAB-12 HDL CODE TO DETECT A SEQUENCE  13.1 Introduction 13.2 Objective 13.3 Prelab Preparation: 13.4 Equipment needed 13.5 Background 13.6 Procedure 13.7 VHDL Program 13.8 Probing Further Experiments  Lab 13 - HDL CODE TO DETECT A SEQUENCE 14.1 Introduction 14.2 Objective 14.3 Prelab Preparation: 14.4 Equipment needed 14.5 Background                                                                   | 53<br>53<br>53<br>53<br>53<br>55<br>55<br>57<br>58<br>58<br>58<br>58<br>58                         |

|           | LAB-12 HDL CODE TO DETECT A SEQUENCE  13.1 Introduction 13.2 Objective 13.3 Prelab Preparation: 13.4 Equipment needed 13.5 Background 13.6 Procedure 13.7 VHDL Program 13.8 Probing Further Experiments  Lab 13 - HDL CODE TO DETECT A SEQUENCE 14.1 Introduction 14.2 Objective 14.3 Prelab Preparation: 14.4 Equipment needed 14.5 Background 14.6 Procedure                                                    | 53<br>53<br>53<br>53<br>53<br>55<br>55<br>57<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58 |

|           | LAB-12 HDL CODE TO DETECT A SEQUENCE  13.1 Introduction 13.2 Objective 13.3 Prelab Preparation: 13.4 Equipment needed 13.5 Background 13.6 Procedure 13.7 VHDL Program 13.8 Probing Further Experiments  Lab 13 - HDL CODE TO DETECT A SEQUENCE 14.1 Introduction 14.2 Objective 14.3 Prelab Preparation: 14.4 Equipment needed 14.5 Background 14.6 Procedure 14.7 VHDL Program                                  | 53<br>53<br>53<br>53<br>53<br>55<br>55<br>57<br>58<br>58<br>58<br>58<br>58<br>60<br>60             |

|           | LAB-12 HDL CODE TO DETECT A SEQUENCE  13.1 Introduction 13.2 Objective 13.3 Prelab Preparation: 13.4 Equipment needed 13.5 Background 13.6 Procedure 13.7 VHDL Program 13.8 Probing Further Experiments  Lab 13 - HDL CODE TO DETECT A SEQUENCE 14.1 Introduction 14.2 Objective 14.3 Prelab Preparation: 14.4 Equipment needed 14.5 Background 14.6 Procedure                                                    | 53<br>53<br>53<br>53<br>53<br>55<br>55<br>57<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58 |

| 14        | LAB-12 HDL CODE TO DETECT A SEQUENCE  13.1 Introduction 13.2 Objective 13.3 Prelab Preparation: 13.4 Equipment needed 13.5 Background 13.6 Procedure 13.7 VHDL Program 13.8 Probing Further Experiments  Lab 13 - HDL CODE TO DETECT A SEQUENCE 14.1 Introduction 14.2 Objective 14.3 Prelab Preparation: 14.4 Equipment needed 14.5 Background 14.6 Procedure 14.7 VHDL Program                                  | 53<br>53<br>53<br>53<br>53<br>55<br>55<br>57<br>58<br>58<br>58<br>58<br>58<br>60<br>60             |

| 14<br>A   | LAB-12 HDL CODE TO DETECT A SEQUENCE  13.1 Introduction 13.2 Objective 13.3 Prelab Preparation: 13.4 Equipment needed 13.5 Background 13.6 Procedure 13.7 VHDL Program 13.8 Probing Further Experiments  Lab 13 - HDL CODE TO DETECT A SEQUENCE 14.1 Introduction 14.2 Objective 14.3 Prelab Preparation: 14.4 Equipment needed 14.5 Background 14.6 Procedure 14.7 VHDL Program 14.8 Further Probing Experiments | 53<br>53<br>53<br>53<br>53<br>55<br>55<br>57<br>58<br>58<br>58<br>58<br>58<br>60<br>60<br>62       |

## **Course Information**

#### 1.1 Introduction

This course is intended to enhance the learning experience of the student in topics encountered in AECB10. In this lab, students are expected to gain experience in using the basics for design of high-speed ALUs, control and timing circuitry, and asynchronous systems; hands-on system prototyping with HDLs for FPGA devices; current hardware topics related to computer design using modern design methodologies and CAD tools; and principles of system design for testability. How the student performs in the lab depends on his/her preparation, participation, and teamwork. Each team member must participate in all aspects of the lab to insure a thorough understanding of the equipment and concepts. The student, lab teaching assistant, and faculty coordinator all have certain responsibilities toward successful completion of the lab's goals and objectives.

#### 1.1.1 Student Responsibilities

The student is expected to be prepared for each lab. Lab preparation includes reading the lab experiment and related textbook material. If you have questions or problems with the preparation, contact your Laboratory teaching Faculty (LTF), but in a timely manner. Do not wait until an hour or two before the lab and then expect the LTF to be immediately available.

A large portion of the student's grade is determined in the comprehensive final exam, resulting in a requirement of understanding the concepts and procedure of each lab experiment for the successful completion of the lab class. The student should remain alert and use common sense while performing a lab experiment. They are also responsible for keeping a professional and accurate record of the lab experiments in the lab manual wherever tables are provided. Students should report any errors in the lab manual to the teaching Faculty.

The student responsibilities are:

- 1. Students are required to attend all labs.

- 2. Students should work individually while performing lab experiments.

- 3. Students have to bring the lab worksheet whenever they come for lab work.

- 4. Should take only the lab worksheet, calculator (if needed) and a pen or pencil to the work area.

- 5. Should learn the prelab questions. Read through the lab experiment to familiarize themselves with the basics of embedded C and 8051 Trainer board.

- 6. Should utilize 3 hour's time properly to perform the experiment and to verify the results. Do the experiments, draw the graphs if required and take the signature from the faculty.

- 7. If the experiment is not completed in the stipulated time, the pending work has to be carried out in the leisure hours or extended hours.

- 8. For practical subjects there shall be a continuous evaluation during the semester for 30 sessional marks and 70 end examination marks.

- 9. Out of 30 internal marks, 20 marks shall be awarded for day-to-day work and 10 marks to be awarded by conducting an internal laboratory test.

#### 1.1.2 Laboratory Teaching Assistant Responsibilities

The LTF shall be completely familiar with each lab prior to class. The LTF shall provide the students with a syllabus and safety review during the first class. The LTF is responsible for ensuring that all the necessary equipment and/or preparations for the lab are available and in working condition. Lab experiments should be checked in advance to make sure everything is in working order. The LTF should fully answer any questions posed by the students and supervise the students performing the lab experiments. The LTF is expected to award the marks in the lab worksheets in a fair and timely manner. The marks awarded lab worksheets should uploaded in student portal at the same day.

#### 1.1.3 Faculty Coordinator Responsibilities

The faculty coordinator should ensure that the laboratory is properly equipped, i.e., that the teaching assistants receive any equipment necessary to perform the experiments. The coordinator is responsible for supervising the teaching assistants and resolving any questions or problems that are identified by the teaching assistants or the students. The coordinator may supervise the format of the final exam for the lab. They are also responsible for making any necessary corrections to this manual and ensuring that it is continually updated and available.

#### 1.1.4 Lab Policy and Grading

The student should understand the following policy:

**ATTENDANCE:** Attendance is mandatory for all lab hours as per the academic regulations.

#### LAB RECORD's: The student must:

- 1. Thoroughly read the prelab of corresponding experiment before entering to the lab.

- 2. Come with full preparation of corresponding lab experiment, after reaching the lab you should write the worksheet without seeing the lab manual.

- 3. Write the all the tabular columns and related calculations after completion of experiment.

- 4. Take the lab work sheet correction before leaving the lab.

#### **GRADING POLICY:**

- 1. The every week lab worksheet is evaluated for 20 Marks.

- 2. The 20 Marks are sub dived to 5 parts. i.e. preparation, algorithm/circuit design, program / procedure, execution and Viva. Each part is assigned for 4 marks.

- 3. Based the student performance the lab, the faculty grade the marks out of 20 marks in each lab.

- 4. Finally, the faculty grade the marks for day to day evaluation by making the average of conducted laboratory sessions.

- 5. 10 marks are evaluated from the lab internal exam.

**PRE-REQUISTES AND CO-REQUISTIES:** The lab course is to be taken during the same semester as AEC111, but receives a separate grade.

#### 1.1.5 Course Goals and Objectives

The Embedded Systems Laboratory is designed to provide the student with the knowledge to use basic input/output devices and techniques with proficiency. These techniques are designed to complement the concepts introduced in AEC016. In addition, the student should learn how to record experimental results effectively and present these results in a lab worksheet.

More explicitly, the class objectives are:

- To gain proficiency in the usage of Keil IDE Tool.

- To enhance understanding the theory of embedded systems concepts including:

- Operating systems basics,

- Task scheduling

- Embedded software development tools,

- Multiprocessing and multitasking,

- Task communication/synchronization issues,

- Advance processors.

- To develop communication skills through:

- Maintenance of succinct but complete laboratory notebooks as permanent, written descriptions of procedures, results, and analyses.

- Verbal interchanges with the laboratory instructor and other students.

- Preparation of succinct but complete laboratory reports.

- To compare theoretical predictions with experimental results and to determine the source of any apparent errors.

## 1.2 Use of Laboratory Instruments

One of the major goals of this lab is to familiarize the student with the interfacing of various input/output (I/O) devices with the 8051 microcontroller. Some understanding of the lab instruments is necessary to avoid personal or equipment damage. By understanding the device's purpose and following a few simple rules, costly mistakes can be avoided. Most of the instrumentation used in this laboratory is implemented through the interfacing modules, Personal computer, and Cathode ray oscilloscope.

In general, all devices have physical limits. These limits are specified by the device manufacturer and are referred to as the device rating. The ratings are usually expressed in terms of voltage limits, current limits, or power limits. It is up to the engineer to make sure that in device operation, these ratings (limit values) are not exceeded. The following rules provide a guideline for instrument protection.

#### 1.2.1 Instrument Protection Rules

- 1. Setup Keil µVision 4.0 or above software in personal computer.

- 2. Be sure the Keil µVision 4.0 or above is installed properly.

- 3. To initiate the programming you must create a project using the Keil µVision IDE.

- 4. Selecting the type of device you are working with.

- 5. Adding C files to your project.

- 6. Compiling and building the C project using Keil μVision IDE.

- 7. Generating the hex file using Keil µVision IDE.

- 8. Burning the hex code into 8051 microcontroller using flash magic.

## 1.3 Data Recording and Reports

#### 1.3.1 The Laboratory Worksheets

Students must record their experimental values in the provided tables in this laboratory manual and reproduce them in the lab worksheets. Worksheets are integral to recording the methodology and results of an experiment. In engineering practice, the laboratory worksheet serves as an invaluable reference to the technique used in the lab and is essential when trying to duplicate a result or write a report. Therefore, it is important to learn to keep accurate data. Make plots of data and sketches when these are appropriate in the recording and analysis of observations. Note that the data collected will be an accurate and permanent record of the data obtained during the experiment and the analysis of the results. You will need this record when you are ready to prepare a lab worksheet.

#### 1.3.2 The Lab Report

Reports are the primary means of communicating your experience and conclusions to other professionals. In this course you will use the lab report to inform your LTA about what you did and what you have learned from the experience. Engineering results are meaningless unless they can be communicated to others. You will be directed by your LTA to prepare a lab report on a few selected lab experiments during the semester.

Your laboratory report should be clear and concise. The lab report shall be typed on a word processor. As a guide, use the format on the next page. Use tables, diagrams, sketches, and plots, as necessary to show what you did, what was observed, and what conclusions you can draw from this. Even though you will work with one or more lab partners, your report will be the result of your individual effort in order to provide you with practice in technical communication.

#### Formatting and Style

- The lab report shall be hand written in a lab worksheet.

- The first line of each paragraph should have a left indent.

- All the tables should have titles and should be numbered. Tables should be labeled numerically as Table 1, Table 2, etc. Table captions appear above the table.

- Graphs should be presented as figures. All the figures should have titles and should be numbered. Figure captions appear below the figure. Graphs should have labeled axes and clearly show the scales and units of the axes.

- All the figures and tables must be centered on the page.

- Do not place screenshots of your lab worksheet.

## Order of Lab Report Components

**COVER PAGE:** Cover page must include lab name and number, your name, and the date the lab was performed.

**OBJECTIVE:** Clearly state the experiment objective in your own words.

**Prelab:** Indicate the required knowledge for performing the concerned experiment.

**EQUIPMENT USED:** Indicate which equipment was used in performing the experiment.

**BACKGROUND:** Give the brief information about corresponding lab experiment.

**PROCEDURE:** Describe the experimental set up and procedure to perform the experiment.

**RESULT:** After completion of experiment, provide a summary of what was learned from this

part of the laboratory experiment.

**PROBING FURTHER EXPERIMENTS:** Questions pertaining to this lab must be answered at the end of laboratory report.

## LAB-1 ORIENTATION

#### 2.1 Introduction

In the first lab period, the students should become familiar with the location of equipment and components in the lab, the course requirements, and the teaching instructor. Students should also make sure that they have all of the co-requisites and pre-requisites for the course at this time.

## 2.2 Objective

To familiarize the students with the lab facilities, equipment, standard operating procedures, lab safety, and the course requirements.

## 2.3 Prelab Preparation:

Read Appendix B and Appendix C of this manual, paying particular attention to the methods of using measurement instruments. Prior to coming to lab class, complete Part 0 of the Procedure.

# 2.4 Equipment needed

Xilinx software.

Personal computer.

#### 2.5 Procedure

- 1. During the first laboratory period, the instructor will provide the students with a general idea of what is expected from them in this course. Each student will receive a copy of the syllabus, stating the instructor's contact information. In addition, the instructor will review the safety concepts of the course.

- 2. During this period, the instructor will briefly review the equipment which will be used throughout the semester. The location of instruments, equipment, and components (e.g. resistors, capacitors, connecting wiring) will be indicated. The guidelines for instrument use will be reviewed.

#### LAB-2 REALIZATION OF A BOOLEAN FUNCTION

#### 3.1 Introduction

A multi variable Boolean function can be implemented through VHDL in two ways. First one is using primitive gates and the second one is using assign statements.

## 3.2 Objective

By the end of this lab, the student should learn how to Design and simulate the HDL code to realize three and four variable Boolean functions.

#### 3.3 Prelab

Read Appendix B and Appendix C of this manual, paying particular attention to the methods of using measurement instruments. Prior to coming to lab class, complete Part 0 of the Procedure.

## 3.4 Equipment needed

Xilinx software.

Personal computer.

## 3.5 Back ground

A multi variable Boolean function can be implemented through VHDL in two ways. First one is using primitive gates and the second one is using assign statements.

Gate primitives are predefined in VHDL, which are ready to use. They are instantiated like modules. There are two classes of gate primitives: Multiple input gate primitives and Single input gate primitives. Multiple input gate primitives include and, nand, or, nor, xor, and xnor. These can have multiple inputs and a single output. Single input gate primitives include not, buf, notif1, bufif1, notif0, and bufif0. These have a single input and one or more outputs.

Assign statements are used to define signal values as Boolean expressions. In the example: out = AS' + BS, out is defined by the function AS' + BS, but must be written in VHDL using the AND operator ("&"), OR operator ("|"), the XOR operator (" $\oplus$ ") and the NOT operator (" $\sim$ ").

#### 3.6 Procedure

Part (0) After answering the following questions, review the laboratory exercise procedures and plan how you will use the experience gained in these calculations to find the values sought.

- 1. Create a module with required number of variables and mention it's input/output.

- 2. Write the description of given Boolean function using operators or by using the built in primitive gates.

- 3. Create another module referred as test bench to verify the functionality.

- 4. Follow the steps required to simulate the design and compare the obtained output with the corresponding truth table

## 3.7 VHDL Program

```

// logic gates

library ieee;

use ieee.std_logic_1164.all;

entity vhdl3_1a is port(a,b:in std_logic; x:out std_logic);

end vhdl3_1a;

architecture behavior of vhdl3_1a is

begin

x \le a \text{ xor } b;

end behavior;

library ieee;

use ieee.std_logic_1164.all;

entity vhdl3_1a is port(a,b:in std_logic; x:out std_logic);

end vhdl3<sub>1</sub>a;

architecture behavior of vhdl3_1a is

begin

x \le a and b;

end behavior;

library ieee;

use ieee.std_logic_1164.all;

entity vhdl3_1a is port(a,b:in std_logic; x:out std_logic);

end vhdl3_1a;

architecture behavior of vhdl3_1a is

begin

x \le a or b;

end behavior;

library ieee;

use ieee.std_logic_1164.all;

entity vhdl3_1a is port(a,b:in std_logic;x:out std_logic);

end vhdl3_1a;

architecture behavior of vhdl3_1a is

begin

x \le a \text{ nand } b;

end behavior;

```

```

library ieee;

use ieee.std_logic_1164.all;

entity vhdl3_1a is port(a, b:in std_logic;x:out std_logic);

end vhdl3_1a;

architecture behavior of vhdl3_1a is

begin

x \le a \text{ nor } b;

end behavior;

library ieee;

use ieee.std_logic_1164.all;

entity vhdl3_1a is port(a,b:in std_logic;x:out std_logic);

end vhdl3_1a;

architecture behavior of vhdl3_1a is

begin

x \le a \quad xnor \quad b;

end behavior;

library ieee;

use ieee.std_logic_1164.all;

entity vhdl3_1a is port(a :in std_logic;x:out std_logic);

end vhdl3<sub>-</sub>1a;

architecture behavior of vhdl3_1a is

begin

x \le not a;

end behavior;

```

## 3.8 Probing Further Experiments

- Q1. What is the difference between main module and test bench module?.

- Q2. What are the different tools available for simulation.

- Q3. What is meant by universal gate? List them.

## Lab 3 – DESIGN OF DECODER AND ENCODER

#### 4.1 Introduction

Encoder circuit basically converts the applied information signal into a coded digital bit stream. Decoder performs reverse operation and recovers the original information signal from the coded bits.

## 4.2 Objective

To design and simulate the HDL code for the following combinational circuits

- 1. 3 to 8 Decoder

- 2. 8 to 3 Encoder (With priority and without priority)

## 4.3 Prelab Preparation:

Read Appendix B and Appendix C of this manual, paying particular attention to the methods of using measurement instruments. Prior to coming to lab class, complete Part 0 of the Procedure.

# 4.4 Equipment needed

Xilinx software.

Personal computer.

# 4.5 Background

#### Program logic for Decoder

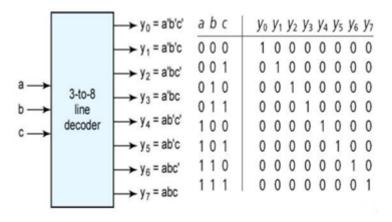

A decoder is a multiple-input, multiple-output logic circuit which converts coded inputs into coded outputs, where the input and output codes are different. The input code generally has fewer bits than the output code. Each input code word produces a different output code word, i.e., there is one-to-one mapping from input code words into output code words. This one-to-one mapping can be expressed in a truth table. The most common decoder circuit is an n-to-2n decoder or binary decoder. Such a decoder has an n-bit binary input code and a 1-out-of-2n output code. A binary decoder is used when you need to activate exactly one of 2noutputs based on an n-bit input value. Figure 4.1 shows the general structure of the 3 to 8 decoder circuit and its truth table.

Figure 4.1: General Structure of 3 to 8 Decoder and its truth table

#### Program logic for Encoder

An encoder has M input and N output lines. Out of M input lines only one is activated at a time and produces equivalent code on output N lines. If a device output code has fewer bits than the input code has, the device is usually called an encoder. Example Octal-to-Binary take 8 inputs and provides 3 outputs. For an 8- to-3 binary encoder with inputs D0-D7 the logic expressions of the outputs XYZ are obtained by using the Table.

$$X = D4 + D5 + D6 + D7 Y = D2 + D3 + D6 + D7 Z = D1 + D3 + D5 + D7$$

| INPUTS    |    |    |           |           |               |    |    | OUTPUTS |   |              |

|-----------|----|----|-----------|-----------|---------------|----|----|---------|---|--------------|

| <b>D7</b> | D6 | D5 | <b>D4</b> | <b>D3</b> | $\mathbf{D2}$ | D1 | D0 | X       | Y | $\mathbf{Z}$ |

| 0         | 0  | 0  | 0         | 0         | 0             | 0  | 1  | 0       | 0 | 0            |

| 0         | 0  | 0  | 0         | 0         | 0             | 1  | 0  | 0       | 0 | 1            |

| 0         | 0  | 0  | 0         | 0         | 1             | 0  | 0  | 0       | 1 | 0            |

| 0         | 0  | 0  | 0         | 1         | 0             | 0  | 0  | 0       | 1 | 1            |

| 0         | 0  | 0  | 1         | 0         | 0             | 0  | 0  | 1       | 0 | 0            |

| 0         | 0  | 1  | 0         | 0         | 0             | 0  | 0  | 1       | 0 | 1            |

| 0         | 1  | 0  | 0         | 0         | 0             | 0  | 0  | 1       | 1 | 0            |

| 1         | 0  | 0  | 0         | 0         | 0             | 0  | 0  | 1       | 1 | 1            |

Table 4.1: Truth Table for 8-3 Encoder with D7-D0 inputs

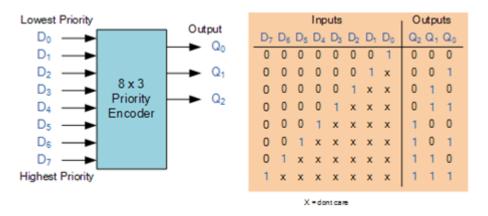

One of the main disadvantages of standard digital encoders is that they can generate the wrong output code when there is more than one input present at logic level "1". The Priority Encoder solves the problems mentioned above by allocating a priority level to each input. The priority encoders output corresponds to the currently active input which has the highest priority. So when an input with a higher priority is present, all other inputs with a lower priority will be ignored. The priority encoder comes in many different forms with an example of an 8- input priority encoder along with its truth table shown in Figure 4.2

Figure 4.2: General Structure of 3 to 8 Decoder and its truth table

Decoder or encoder can be designed using HDL through its truth table in two ways: one is using gate level modeling and another is by behavioral model.

#### 4.6 Procedure

Part (0) After answering the following questions, review the laboratory exercise procedures and plan how you will use the experience gained in these calculations to find the values sought.

- 1. Create a module with required number of variables and mention it's input/output.

- 2. Write the description of given Boolean function using operators or by using the built in primitive gates.

- 3. Create another module referred as test bench to verify the functionality.

- 4. Follow the steps required to simulate the design and compare the obtained output with the corresponding truth table.

## 4.7 VHDL Program

```

// 8 to 3 Encoder without priority

entity encoder is

Port ( A:in std_logic_vector(7 downto 0);

B:out std_logic_vector(2 downto 0));

end encoder;

architecture Behavioral of encoder is

begin

process(A)

begin

if A="100000000" then B<="000";

elsif A="010000000" then B<="001";

elsif A="001000000" then B<="010";

elsif A="000100000" then B<="011";

elsif A="000010000" then B<="100";

elsif A="00001000" then B<="100";

elsif A="000001000" then B<="101";</pre>

```

```

elsif A="00000010" then B<="110";

elsif A="00000001" then B<="111";

else B<="ZZZ";

end if;

end process;

end Behavioral;

// 3 to 8 decoder

entity decoder is

Port (A:in std_logic_vector(2 downto 0);

B: out std_logic_vector(7 downto 0));

end decoder;

architecture Behavioral of decoder is

begin

process (A)

begin

if A="000" then B<="00000001";

elsif A="001" then B<="00000010";

elsif A="010" then B<="00000100";

elsif A="011" then B<="00001000";

elsif A="100" then B<="00010000";

elsif A="101" then B<="00100000";

elsif A="110" then B<="01000000";

elsif A="111" then B<="100000000";

else B<="11111111";

end if;

end process;

end Behavioral;

```

# 4.8 Further Probing Experiments

- Q1. Create a VHDL module named h6to64 that represents a 6-to-64 binary decoder. Use the treelike structure in which the 6-to-64 decoder is built using nine instances of the 3 to 8 decoder.

- Q2. What is the difference between the following two lines of VHDL code? #5 a = b; a = #5 b;

- Q3. Construct a 4x16 decoder using two 3x8 decoder and additional logic. Show the schematic diagram neatly.

## Lab 4 – DESIGN OF MULTIPLEXER AND DEMULTIPLEXER

#### 5.1 Introduction

A Multiplexer is a circuit that accept many inputs but gives only one output. A Demultiplexer functions exactly in the reverse way of a multiplexer i.e., a demultiplexer accepts only one input and gives many outputs.

## 5.2 Objective

To write HDL codes for an 8X1 multiplexer and 1X8 demultiplexer and verify its functionality

## 5.3 Prelab Preparation:

Read Appendix B and Appendix C of this manual, paying particular attention to the methods of using measurement instruments. Prior to coming to lab class, complete Part 0 of the Procedure.

## 5.4 Equipment needed

Xilinx software.

Personal computer.

# 5.5 Background

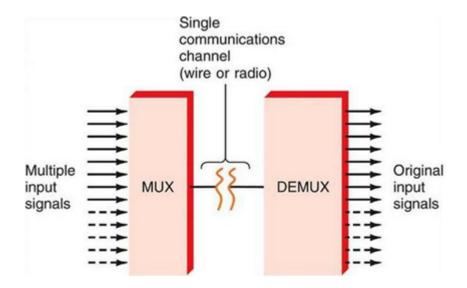

In the large-scale-digital systems, a single line is required to carry on two or more digital signals – and, of course! At a time, one signal can be placed on the one line. But, what is required is a device that will allow us to select; and, the signal we wish to place on a common line, such a circuit is referred to as multiplexer.

The function of a multiplexer is to select the input of any 'n' input lines and feed that to one output line. The function of a de-multiplexer is to inverse the function of the multiplexer and the shortcut forms of the multiplexer. The de-multiplexers are mux and demux. Some multiplexers perform both multiplexing and de-multiplexing operations. The main function of the multiplexer is that it combines input signals, allows data compression, and shares a single transmission channel.

Figure 5.1: Multiplexer and De-multiplexer

The output value of a 8x1 multiplexer can be represented using the equation (4.1)

Y S2 S1 S0 Io S2 S1S0 I1 S2S1 S0 I2 S2S1S0 I3 S2 S1 S0 I4 S2 S1S0 I5 S2S1 S0 I6 S2S1S0 I7 . . . (4.1)

For the combination of selection input, the data line is connected to the output line. The 8x1 multiplexer requires 8 AND gates, one OR gate and 3 selection lines. As an input, the combination of selection inputs are giving to the AND gate with the corresponding input data lines.

In a similar fashion, all the AND gates are given connection. In this 8x1 multiplexer, for any selection line input, one AND gate gives a value of 1 and the remaining all AND gates give 0. And, finally, by using OR gate, all the AND gates are added; and, this will be equal to the selected value.

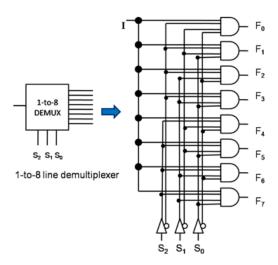

The demultiplexer is also called as data distributors as it requires one input, 3 selected lines and 8 outputs. De-multiplexer takes one single input data line, and then switches it to any one of the output line. 1-to-8 demultiplexer circuit diagram is shown below; it uses 8 AND gates for achieving the operation. The input bit is considered as data D and it is transmitted to the output lines.

Figure 5.2: Demultiplexer circuit diagram

#### 5.6 Procedure

Part (0) After answering the following questions, review the laboratory exercise procedures and plan how you will use the experience gained in these calculations to find the values sought.

- 1. Create a module with required number of variables and mention it's input/output.

- 2. Write the description of given Boolean function using operators or by using the built in primitive gates.

- 3. Create another module referred as test bench to verify the functionality.

- 4. Follow the steps required to simulate the design and compare the obtained output with the corresponding truth table.

## 5.7 VHDL Program

```

// 8:1 multiplexer library ieee;

use ieee.std_logic_1164.all;

entity mux8_1 is

port(din:in std_logic_vector(7 downto 0); sel:in std_logic_vector(2 downto

end mux8_1;

architecture beh123 of mux8_1 is

begin

process (din, sel)

begin

case sel is

when "000" => dout <= din(0);

when "001" => dout <= din (1);

when "010" => dout <= din(2);

when "011" => dout <= din (3);

when "100" = > dout < = din(4);

when "101" => dout <= din(5);

when "110" => dout <= din(6);

when "111" => dout <= din (7);

when others=>

dout \le z';

end case;

end process;

end beh123;

//1:8 Demultiplexer

architectural behavioral of dmux1 is

begin

y(0) \le f when s = 000 else '0';

y(1) \le f when s = 001 else '0';

y(2) \le f when s = 010 else '0';

y(3) \le f when s = 011 else '0';

y(4) \le f when s = 100 else '0';

y(5) \le f when s = 101 else '0';

```

```

y(6) \le f when s = "110" else '0'; y(7) \le f when s = "111" else '0'; end behavioral; demultiplexer:

```

# 5.8 Further Probing Experiments

Q1. Implement the function  $f(A,B,C) = \sum m(0,1,3,5,7)$  by using multiplexer.

Q2. Write code for 1x4 Multiplexer using different coding methods.

Q3. Design an OR gate from 2:1 MUX.

#### Lab 5 – DESIGN OF CODE CONVERTERS

#### 6.1 Introduction

Gray codes are widely used to prevent spurious output from electromechanical switches and to facilitate error correction in digital communications such as digital terrestrial television and some cable TV systems.

## 6.2 Objective

To Design and simulate the HDL code for the following combinational circuits

- a. 4 Bit binary to gray code converter

- b. 4 Bit gray to binary code converter

- c. Comparator

## 6.3 Prelab Preparation:

Read Appendix B and Appendix C of this manual, paying particular attention to the methods of using measurement instruments. Prior to coming to lab class, complete Part 0 of the Procedure.

## 6.4 Equipment needed

Xilinx software.

Personal computer.

## 6.5 Background

#### Binary to gray code converter logic

This conversion method strongly follows the EX-OR gate operation between binary bits. The steps to perform binary to grey code conversion are given bellow.

- a. To convert binary to grey code, bring down the most significant digit of the given binary number, because, the first digit or most significant digit of the grey code number is same as the binary number.

- b. To obtain the successive grey coded bits to produce the equivalent grey coded number for the given binary, add the first bit or the most significant digit of binary to the second one and write down the result next to the first bit of grey code, add the second binary bit to third one and write down the result next to the second bit of grey code, follow this operation until the last binary bit and write down the results based on EX-OR logic to produce the equivalent grey

coded binary.

#### Gray to binary code converter logic

This conversion method also follows the EX-OR gate operation between gray & binary bits. The steps to perform gray code to binary conversion are given below.

- a. To convert grey code to binary, bring down the most significant digit of the given gray code number, because, the first digit or the most significant digit of the gray code number is same as the binary number.

- b. To obtain the successive second binary bit, perform the EX-OR operation between the first bit or most significant digit of binary to the second bit of the given gray code.

- c. To obtain the successive third binary bit, perform the EX-OR operation between the second bit or most significant digit of binary to the third MSD (most significant digit) of grey code and so on for the next successive binary bits conversion to find the equivalent.

#### 6.6 Procedure

Part (0) After answering the following questions, review the laboratory exercise procedures and plan how you will use the experience gained in these calculations to find the values sought.

- 1. Create a module with required number of variables and mention it's input/output.

- 2. Write the description of given Boolean function using operators or by using the built in primitive gates.

- 3. Create another module referred as test bench to verify the functionality.

- 4. Follow the steps required to simulate the design and compare the obtained output with the corresponding truth table.

## 6.7 VHDL Program

```

// binary to gray code converter

entity btog is

Port (b: in STD_LOGIC_VECTOR (3 downto 0);

g : out STDLOGIC_VECTOR (3 downto 0));

end btog;

architecture Dataflow of btog is

begin

g(3) \le b(3);

g(2) <= b(3) \text{ xor } b(2);

g(1) <= b(2) \text{ xor } b(1);

g(0) \le b(1) \text{ xor } b(0);

end Dataflow

//gray to binary converter

entity gtob is

Port (g: in STD_LOGIC_VECTOR (3 downto 0);

b: inout STD_LOGIC_VECTOR (3 downto 0));

```

```

end gtob; architecture Behavioral of gtob is begin b(3) <= g(3); \\ b(2) <= b(3) xor g(2); \\ b(1) <= b(2) xor g(1); \\ b(0) <= b(1) xor g(0); \\ end Behavioral;

```

# 6.8 Further Probing Experiments

Q1. Design BCD to Excess-3 code converter.

Q2. Design a BCD to seven segment code converter.

Q3. Design octal to binary code converter.

# LAB-6 FULL ADDER AND FULL SUBTRACTOR DESIGN MODELING

#### 7.1 Introduction

A combinational logic circuit that performs the addition of two single bits is called Half Adder. A combinational logic circuit that performs the addition of three single bits is called Full Adder. A full subtractor is a combinational circuit that performs subtraction of two bits, one is minuend and other is subtrahend, taking into account borrow of the previous adjacent lower minuend bit.

## 7.2 Objective

To write a HDL code to describe the functions of a full Adder and subtractor.

## 7.3 Prelab Preparation:

Read Appendix B and Appendix C of this manual, paying particular attention to the methods of using measurement instruments. Prior to coming to lab class, complete Part 0 of the Procedure.

## 7.4 Equipment needed

Xilinx software.

Personal computer.

# 7.5 Background

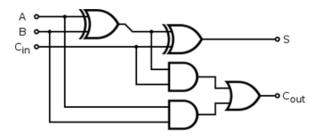

A full adder consists of 3 inputs and 2 outputs. Fig 5.1 shows truth table of full adder. Use "assign" keyword to represent design in dataflow style. The output signal expressions can be obtained from the truth table using K-maps.

Figure 7.1: Logic diagram for 1-bit full adder

Table 7.1: Truth table for 1-bit full adder

| Inj | puts | 3   | Outputs |      |  |

|-----|------|-----|---------|------|--|

| A   | В    | Cin | Sum     | Cout |  |

| 0   | 0    | 0   | 0       | 0    |  |

| 0   | 0    | 1   | 1       | 0    |  |

| 0   | 1    | 0   | 1       | 0    |  |

| 0   | 1    | 1   | 0       | 1    |  |

| 1   | 0    | 0   | 1       | 0    |  |

| 1   | 0    | 1   | 0       | 1    |  |

| 1   | 1    | 0   | 0       | 1    |  |

| 1   | 1    | 1   | 1       | 1    |  |

This is not practical to perform subtraction only between two single bit binary numbers. Instead binary numbers are always multibits. The subtraction of two binary numbers is performed bit by bit from right (LSB) to left (MSB). During subtraction of same significant bit of minuend and subtrahend, there may be one borrow bit along with difference bit. This borrow bit (either 0 or 1) is to be added to the next higher significant bit of minuend and then next corresponding bit of subtrahend to be subtracted from this. It will continue up to MSB. The combinational logic circuit performs this operation is called full subtractor. Hence, full subs tractor is similar to half subs tractor but inputs in full subs tractor are three instead of two.

Two inputs are for the minuend and subtrahend bits and third input is for borrowed which comes from previous bits subtraction. The outputs of full adder are similar to that of half adder, these are difference (D) and borrow (b).

The combination of minuend bit (A), subtrahend bit (B) and input borrow (bi) and their respective differences (D) and output borrows (b) are represented in a truth table 7.2. The output signal expressions can be obtained from the truth table using K-maps.

Table 7.2: Truth table for 1-bit subtractor adder

|   |   | Inputs        | Outputs    |            |  |  |

|---|---|---------------|------------|------------|--|--|

| A | В | C (Borrow in) | Difference | Borrow out |  |  |

| 0 | 0 | 0             | 0          | 0          |  |  |

| 0 | 0 | 1             | 1          | 1          |  |  |

| 0 | 1 | 0             | 1          | 1          |  |  |

| 0 | 1 | 1             | 0          | 1          |  |  |

| 1 | 0 | 0             | 1          | 0          |  |  |

| 1 | 0 | 1             | 0          | 0          |  |  |

| 1 | 1 | 0             | 0          | 0          |  |  |

| 1 | 1 | 1             | 1          | 1          |  |  |

#### 7.6 Procedure

Part (0) After answering the following questions, review the laboratory exercise procedures and plan how you will use the experience gained in these calculations to find the values sought.

- 1. Create a module with required number of variables and mention it's input/output.

- 2. Write the description of given Boolean function using operators or by using the built in primitive gates.

- 3. Create another module referred as test bench to verify the functionality.

- 4. Follow the steps required to simulate the design and compare the obtained output with the corresponding truth table

## 7.7 VHDL Program

```

// full adder VHDL Program using Dataflow Modelling:

entity FULLADDER is

Port (A, B, C_in: in std_logic;

S, C_out: out std_logic);

end FULLADDER;

architecture Behavioral of FULLADDER is

begin

S \le (A \text{ xor } B) \text{ xor } C_{in};

C_{\text{out}} \leq (A \text{ and } B) \text{ or } (C_{\text{in}} \text{ and } (A \text{ xor } B));

end Behavioral;

// full adder VHDL Program using Behavioral Modelling:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD.LOGIC.UNSIGNED.ALL;

entity FULLADDER_BEHAVIORAL_SOURCE is

Port (A: in

STD_LOGIC_VECTOR (2 downto 0);

STDLOGIC_VECTOR (1 downto 0));

y : out

end FULLADDER_BEHAVIORAL_SOURCE;

architecture Behavioral of FULLADDER.BEHAVIORAL.SOURCE is

Begin

process (A)

begin

if (A = "001" \text{ or } A = "010" \text{ or } A = "100" \text{ or } A = "111") then

y(1) <= '1';

else

y(1) < = '0';

end if;

if (A = "011" \text{ or } A = "101" \text{ or } A = "110" \text{ or } A = "111") then

y(0) <= '1';

else y(0) <= '0';

end if;

end process;

end Behavioral

// VHDL code for full adder using the structural method using two half a

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

```

```

entity HA is

Port (A,B: in

STD_LOGIC;

S,C: out STD_LOGIC);

end HA;

architecture dataflow of HA is

begin

S \leq A XOR B:

C \leq A AND B;

end dataflow;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STDLOGIC_UNSIGNED.ALL;

entity ORGATE is

Port (X,Y: in STD_LOGIC;

Z : out STD_LOGIC);

end ORGATE; architecture dataflow of ORGATE is

begin

Z \leq X OR Y;

end dataflow;

library IEEE; use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity FAdder is

Port (FA, FB, FC: in STDLOGIC;

FS, FCA: out STDLOGIC);

end FAdder;

architecture structural of FAdder is

component HA is

Port (A,B: in STD_LOGIC;

S,C: out STDLOGIC);

end component;

component ORGATE is

Port (X,Y: in STDLOGIC;

Z: out STD_LOGIC);

end component;

SIGNAL S0, S1, S2: STD_LOGIC;

U1:HA PORT MAP(A=>FA, B=>FB, S=>S0, C=>S1);

U2:HA PORT MAP(A=>S0, B=>FC, S=>FS, C=>S2);

U3:ORGATE PORT MAP(X=>S2, Y=>S1, Z=>FCA);

end structural;

//full subtractor using dataflow

entity FULLSUBTRACTOR is

Port (A,B,C:in std_logic;

D, B_out:out std_logic);

end FULLSUBTRACTOR;

architecture Behavioral of FULLSUBTRACTOR is

```

```

begin

Process(A,B,C)

begin

D \le A \text{ xor } B \text{ xor } C;

B_{\text{out}} \leq = ((\text{not A}) \text{ and B}) \text{ or } (C \text{ and } (A \text{ xnor B}));

end Process;

end Behavioral;

//full subtractor using Behavioral Modelling

architecture Behavioral of FULLSUBTRACTOR_BEHAVIORAL_SOURCE is

Begin

process (A)

begin

if (A = "001" \text{ or } A = "010" \text{ or } A = "111") then

Y \le "11";

elsif (A = "011") then

Y \le "01";

elsif (A = "100") then

Y \le "10";

else Y \le "00";

end if;

end process;

end Behavioral;

```

# 7.8 Probing Further Experiments

- Q1. Write the sum and carry expression for 1-bit full adder.

- Q2. Write the difference and barrow out expressions for 1-bit subtractor

- Q3. Design a 4-bit ripple carry adder using full adders.

#### LAB-7 DESIGN OF 8-BIT ARITHMETIC LOGIC UNIT

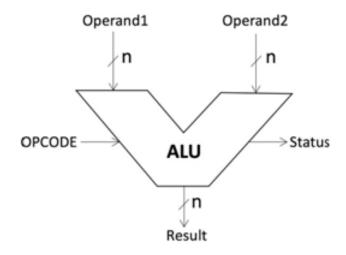

#### 8.1 Introduction

An arithmetic logic unit (ALU) is at the heart of a modern microprocessor, and the adder cell is the elementary unit of an ALU.

## 8.2 Objective

An arithmetic logic unit (ALU) is at the heart of a modern microprocessor, and the adder cell is the elementary unit of an ALU.

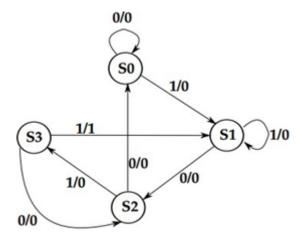

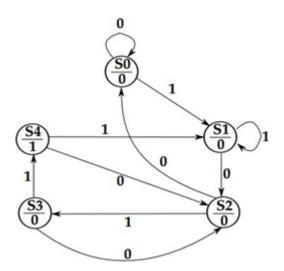

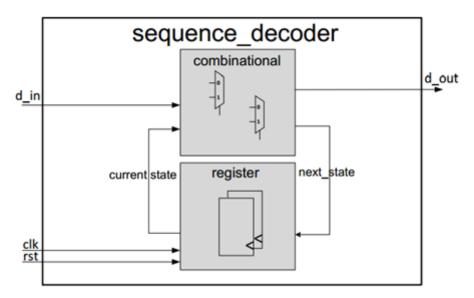

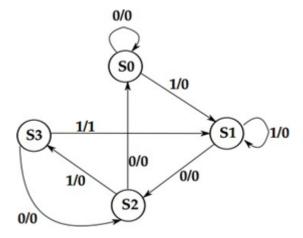

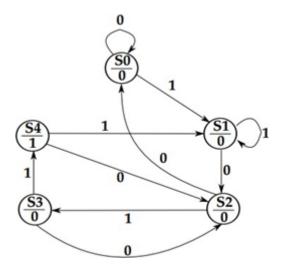

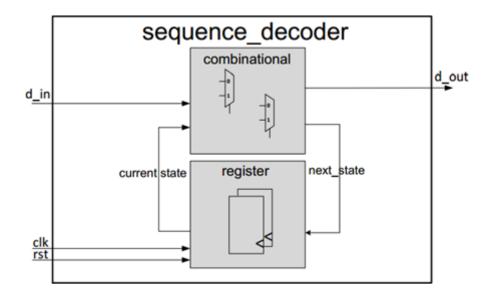

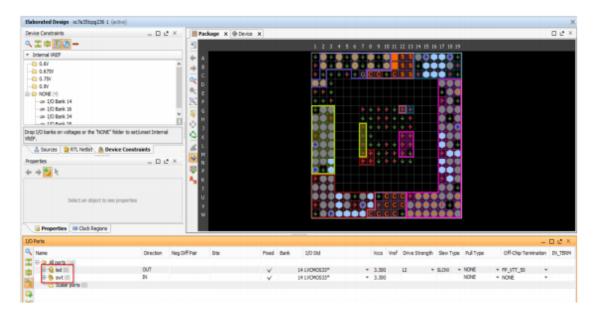

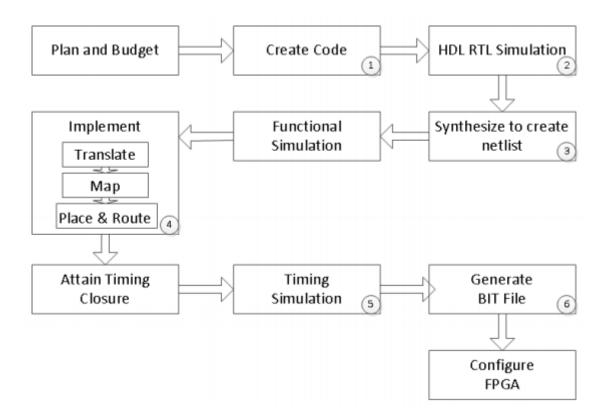

#### 8.3 Prelab