# Lab Manual:

# MICROPROCESSORS AND MICROCONTROLLERS(AECB26)

Prepared by

Ms B.Lakshmi Prasanna(IARE10706)

Electronics and Communication Engineering Institute of Aeronautical Engineering April 7, 2022

# Contents

| Co       | onter | ıt                                           | iv             |

|----------|-------|----------------------------------------------|----------------|

| 1        | INT   | TRODUCTION                                   | 1              |

|          | 1.1   | Introduction                                 | 1              |

|          |       | 1.1.1 Student Responsibilities               | 1              |

|          |       | 1.1.2 Laboratory Assistant Responsibilities  | 2              |

|          |       | 1.1.3 Laboratory Faculty Responsibilities    | 2              |

|          |       | 1.1.4 Course Coordinator Responsibilities    | 2              |

|          | 1.2   | Lab Policy and Grading                       | 2              |

|          | 1.3   | Course Goals and Objectives                  | 3              |

|          | 1.4   | Use of Laboratory Instruments                | 3              |

|          |       | 1.4.1 Instrument Protection Rules            | 3              |

|          | 1.5   | Data Recording and Reports                   | 4              |

|          |       | 1.5.1 The Laboratory Worksheets              | 4              |

|          |       | 1.5.2 The Laboratory Files/Reports           | 4              |

|          |       | 1.5.3 Formatting and Style                   | 4              |

|          |       | 1.5.4 Order of Lab Report Components         | 4              |

| <b>2</b> | LAI   | B-1 Design a Program Using WIN862            | 6              |

|          | 2.1   | Introduction                                 | 6              |

|          | 2.2   | Objective                                    | 6              |

|          |       | 2.2.1 Educational                            | 6              |

|          |       | 2.2.2 Experimental                           | 6              |

|          | 2.3   | Prelab Preparation:                          | 6              |

|          | 2.4   | Equipment needed                             | $\overline{7}$ |

|          | 2.5   | Background                                   | $\overline{7}$ |

|          | 2.6   | Safety Precautions                           | 10             |

|          | 2.7   | Procedure                                    | 10             |

|          | 2.8   | Probing Further Experiments                  | 14             |

| 3        | LAI   | B-2 16 bit arithmetic and logical operations | 15             |

|          | 3.1   | Introduction                                 | 15             |

|          | 3.2   | Objective                                    | 15             |

|          |       | 3.2.1 Educational                            | 15             |

|          |       | 3.2.2 Experimental                           | 15             |

|          | 3.3   | Prelab Preparation:                          | 15             |

|          | 3.4   | Equipment needed                             | 16             |

|          | 3.5   | Background                                   | 16             |

|          | 3.6   | Safety Precautions:                          | 17             |

|          | 3.7   | Procedure                                    | 17             |

|          | 3.8   | Probing Further Experiments                  | 21             |

|          |       |                                              |                |

4 LAB-3 Multibyte Addition and Subraction

|          | 4.1 | Introduction                                                                                                                                  |

|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|

|          | 4.2 | Objective                                                                                                                                     |

|          |     | 4.2.1 Educational                                                                                                                             |

|          |     | 4.2.2 Experimental                                                                                                                            |

|          | 4.3 | Prelab Preparation: 22                                                                                                                        |

|          | 4.4 | Equipment needed                                                                                                                              |

|          | 4.5 | Background                                                                                                                                    |

|          | 4.6 | Safety Precautions                                                                                                                            |

|          | 4.7 | Procedure                                                                                                                                     |

|          | 4.8 | Probing Further Experiments 27                                                                                                                |

| <b>5</b> | LAI | 3-4 Programs to Sort Numbers   29                                                                                                             |

|          | 5.1 | Introduction                                                                                                                                  |

|          | 5.2 | Objective                                                                                                                                     |

|          |     | 5.2.1 Educational $\ldots \ldots 29$                                    |

|          |     | 5.2.2 Experimental $\ldots \ldots 29$                                          |

|          | 5.3 | Prelab Preparation:                                                                                                                           |

|          | 5.4 | Equipment needed                                                                                                                              |

|          | 5.5 | Background 30                                                                                                                                 |

|          | 5.6 | Safety Precautions                                                                                                                            |

|          | 5.7 | Procedure                                                                                                                                     |

|          | 5.8 | Probing Further Experiments                                                                                                                   |

| 6        | LAI | 3-5 Programs for String Manipulations operations 36                                                                                           |

|          | 6.1 | Introduction                                                                                                                                  |

|          | 6.2 | Objective                                                                                                                                     |

|          |     | $6.2.1  \text{Educational} \dots \dots$ |

|          |     | $6.2.2  \text{Experimental}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                 |

|          | 6.3 | Prelab Preparation:                                                                                                                           |

|          | 6.4 | Equipment needed                                                                                                                              |

|          | 6.5 | Background 37                                                                                                                                 |

|          | 6.6 | Safety Precautions                                                                                                                            |

|          | 6.7 | Procedure                                                                                                                                     |

|          | 6.8 | Probing Further Experiments 44                                                                                                                |

| 7        | LAI | <b>3-6</b> Code Conversions 45                                                                                                                |

|          | 7.1 | Introduction                                                                                                                                  |

|          | 7.2 | Objective                                                                                                                                     |

|          |     | 7.2.1 Educational $\ldots \ldots 4$                                     |

|          |     | 7.2.2 Experimental $\ldots \ldots 4$                                    |

|          | 7.3 | Prelab Preparation:                                                                                                                           |

|          | 7.4 | Equipment needed                                                                                                                              |

|          | 7.5 | Background                                                                                                                                    |

|          | 7.6 | Safety Precautions                                                                                                                            |

|          | 7.7 | Procedure                                                                                                                                     |

|          | 7.8 | Probing Further Experiments                                                                                                                   |

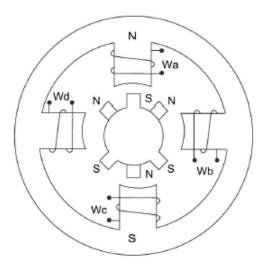

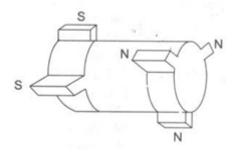

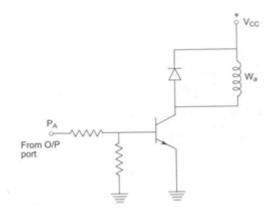

| 8        | LAI | 3-7 Interfacing Stepper Motor to 8086 microprocessor 53                                                                                       |

|          | 8.1 | Introduction                                                                                                                                  |

|          | 8.2 | Objective                                                                                                                                     |

|          |     | 8.2.1 Educational                                                                                                                             |

|          |     | 8.2.2 Experimental                                                                                                                            |

|    | 8.3  | Prelab Preparation:                                                  |

|----|------|----------------------------------------------------------------------|

|    | 8.4  | Equipment needed                                                     |

|    | 8.5  | Background                                                           |

|    | 8.6  | Safety Precautions                                                   |

|    | 8.7  | Procedure                                                            |

|    | 8.8  | Probing Further Experiments                                          |

|    | 0.0  |                                                                      |

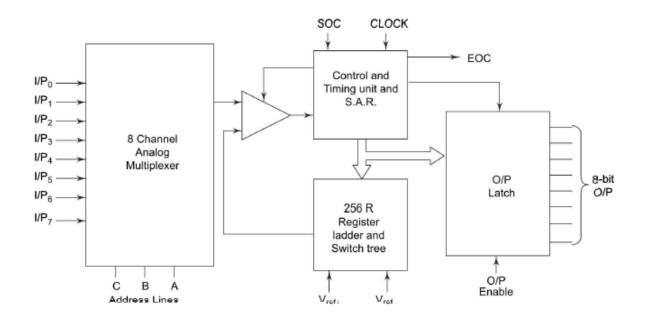

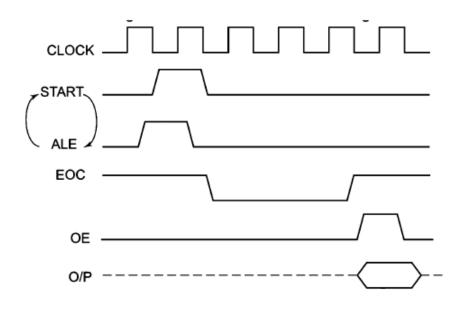

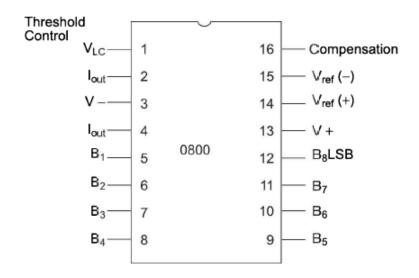

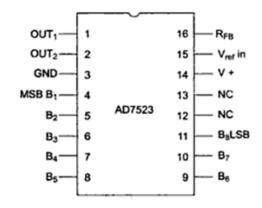

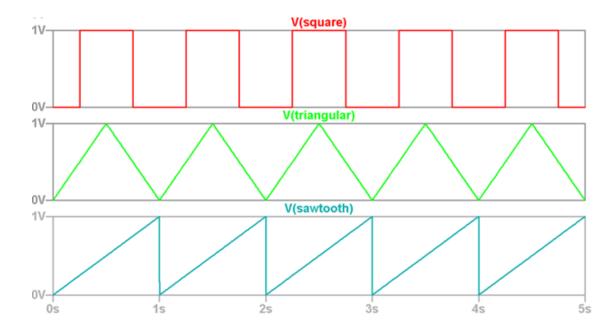

| 9  | LAI  | <b>3-8</b> Interfacing ADC and DAC Devices to 8086 microprocessor 59 |

|    | 9.1  | Introduction                                                         |

|    | 9.2  | Objective                                                            |

|    |      | 9.2.1 Educational                                                    |

|    |      | 9.2.2 Experimental                                                   |

|    | 9.3  | Prelab Preparation:                                                  |

|    | 9.4  | Equipment needed                                                     |

|    | 9.5  | Background                                                           |

|    | 9.6  | Safety Precautions                                                   |

|    | 9.7  | Procedure                                                            |

|    | 9.8  | Probing Further Experiments                                          |

|    | 0.0  |                                                                      |

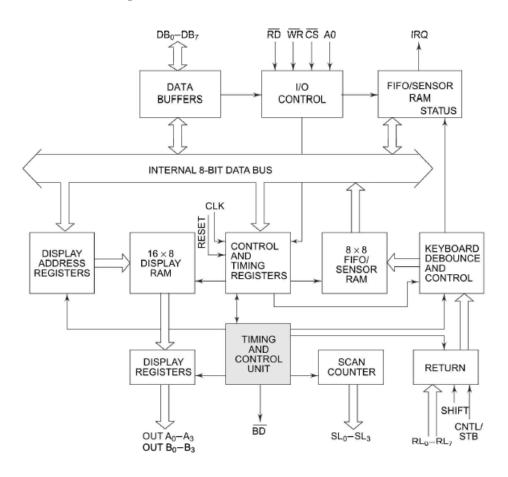

| 10 | LAI  | 3-9 Interfacing Keyboard to 8086 Microprocessor 70                   |

|    | 10.1 | Introduction                                                         |

|    | 10.2 | Objective                                                            |

|    |      | 10.2.1 Educational                                                   |

|    |      | 10.2.2 Experimental                                                  |

|    | 10.3 | Prelab Preparation:                                                  |

|    |      | Equipment needed                                                     |

|    |      | Background                                                           |

|    |      | Safety Precautions                                                   |

|    |      | Procedure                                                            |

|    |      | Probing Further Experiments                                          |

|    | 10.0 |                                                                      |

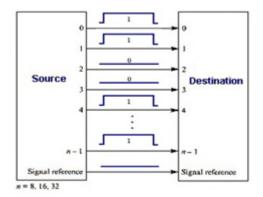

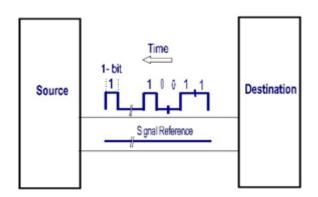

| 11 | LAI  | 3-10 Serial and Parallel Communication 78                            |

|    | 11.1 | Introduction                                                         |

|    | 11.2 | Objective                                                            |

|    |      | 11.2.1 Educational                                                   |

|    |      | 11.2.2 Experimental $\ldots$ 78                                      |

|    | 11.3 | Prelab Preparation:                                                  |

|    |      | Equipment needed                                                     |

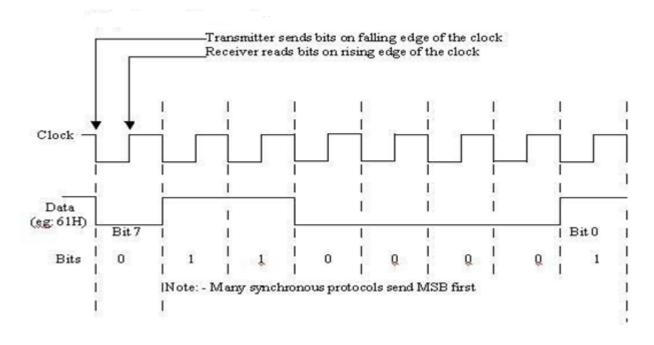

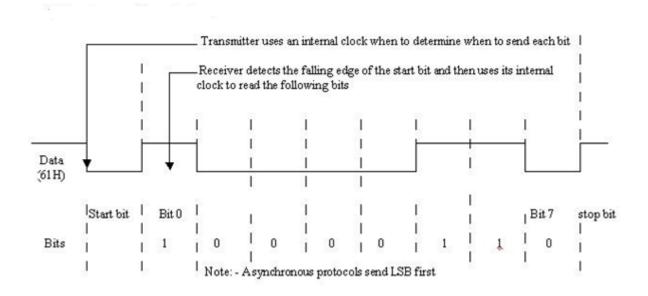

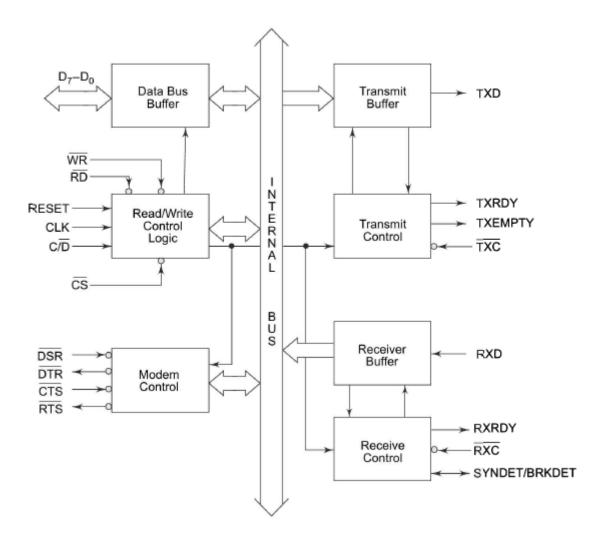

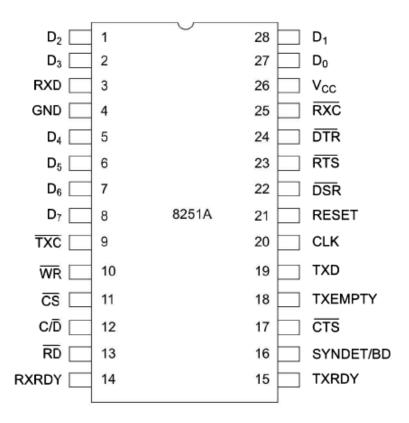

|    |      | Background                                                           |

|    |      | Safety Precautions                                                   |

|    |      | Procedure                                                            |

|    |      | Probing Further Experiments                                          |

|    | 11.0 |                                                                      |

| 12 | LAI  | 3-11 Interfacing traffic light controller and tone generator 94      |

|    | 12.1 | Introduction                                                         |

|    |      | Objective                                                            |

|    |      | 12.2.1 Educational                                                   |

|    |      | 12.2.2 Experimental                                                  |

|    | 12.3 | Prelab Preparation:                                                  |

|    |      | Equipment needed                                                     |

|    |      | Background                                                           |

|    |      | Safety Precautions                                                   |

|    | ±2.0 | , Survey 1 10000000000                                               |

|        | 12.7 Procedure                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                           |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 13     | LAB-12 Arithmetic And Logical operations using 8051 Microcontroller         13.1 Introduction         13.2 Objective         13.2.1 Educational         13.2.2 Experimental         13.3 Prelab Preparation:         13.4 Equipment needed         13.5 Background                                                                                                                                                                       | 100<br>100<br>100<br>100<br>100                                           |

|        | 13.6 Safety Precautions13.7 Procedure13.8 Further Probing Experiments                                                                                                                                                                                                                                                                                                                                                                    | $\begin{array}{c} 104 \\ 105 \end{array}$                                 |

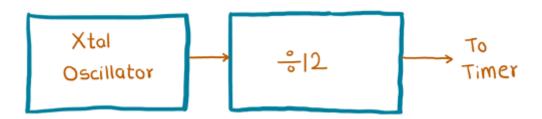

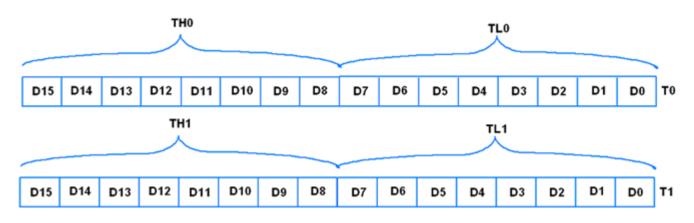

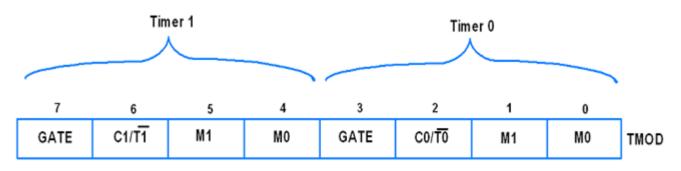

|        | LAB-13 Timer/Counter         14.1 Introduction         14.2 Objective         14.2.1 Educational         14.2.2 Experimental         14.3 Prelab Preparation:         14.4 Equipment needed         14.5 Background         14.6 Safety Precautions         14.7 Procedure         14.8 Further Probing Experiments         14.8 Further Probing Experiments         15.1 Introduction         15.2 Objective         15.2.1 Educational | 109<br>109<br>109<br>110<br>110<br>113<br>114<br>114<br><b>116</b><br>116 |

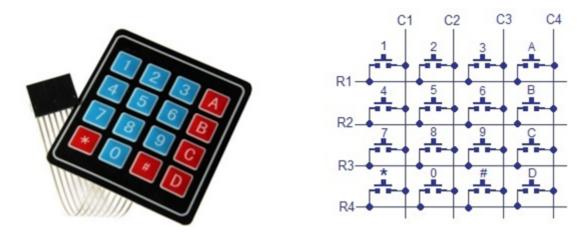

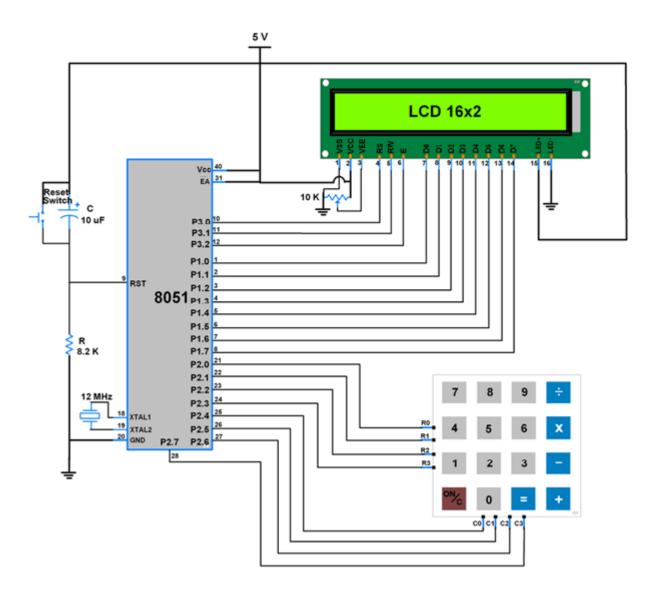

|        | 15.2.1 Educational                                                                                                                                                                                                                                                                                                                                                                                                                       | 116<br>116<br>117<br>117<br>118<br>119                                    |

| _      | Appendix A :Instruction set of 8086 Microprocessor                                                                                                                                                                                                                                                                                                                                                                                       | 121                                                                       |

| B<br>C | Appendix B :Instruction set of 8051 microcontroller<br>Appendix C :Addressing Modes of 8086 microprocessor                                                                                                                                                                                                                                                                                                                               | 132<br>137                                                                |

| D      | Appendix D :Addressing modes of 8051 Microcontroller:                                                                                                                                                                                                                                                                                                                                                                                    | 141                                                                       |

## INTRODUCTION

## 1.1 Introduction

The purpose of this lab is to teach the basics of Intel 8086 and 8051 assembly language. Assembly language is important because it is the principal link between the software world and the hardware world of CPU design. Assembly language is the lowest-level, human-readable programming medium we can use to express complete application programs. Assembly language gives full access to the programmable features of the hardware, so a good understanding of it will provide valuable insight into the fundamentals of CPU design, the operation of the data path, and program execution.

For understanding assembly language. First, compilers translate high-level languages into assembly language, so compiler writers must understand assembly. Operating systems also include critical components written in assembly. Furthermore, embedded and mobile device programming often require knowledge of assembly language. As these technologies become more and more important to the overall performance of computer systems, knowledge of the computer at the assembly-language level will prove to be a valuable asset. Even if you spend your entire career programming in high-level languages, a basic understanding of assembly language concepts will give you an insight into your work that will in turn make you more valuable as an electronics, electrical or computer engineer. This Lab will provide an environment for you to gain hands-on experience with the tools and concepts used in the Microprocessor and microcontroller course.

#### 1.1.1 Student Responsibilities

- 1. Students are required to attend all labs.

- 2. Students should work individually in the hardware and software laboratories

- 3. Students have to follow dress code whenever they come for lab work.

- 4. Should take only the Worksheet, calculator (if needed) and a pen or pencil to the work area.

- 5. Should learn the prelab questions. Read through the lab experiment to familiarize themselves with the components and assembly sequence.

- 6. Should utilize 3 hour's time properly to perform the experiment and to record the readings. Do the calculations, draw the graphs and take signature from the instructor.

- 7. If the experiment is not completed in the stipulated time, the pending work has to be carried out in the leisure hours or extended hours.

- 8. Should submit the completed worksheets according to the deadlines set up by the faculty.

## 1.1.2 Laboratory Assistant Responsibilities

The lab assistant shall be completely familiar with each lab prior to class. The lab assistant shall provide the students with a syllabus and safety review during the first class. The syllabus shall include the lab assistant office hours, telephone number, and the name of the faculty coordinator. The lab assistant is responsible for ensuring that all the necessary equipment and/or preparations for the lab are available and in working condition. Lab experiments should be checked in advance to make sure everything is in working order. The lab assistant should fully answer any questions posed by the students and supervise the students performing the lab experiments.

## 1.1.3 Laboratory Faculty Responsibilities

The faculty should ensure that the laboratory is properly equipped, i.e., that the lab assistants receive any equipment necessary to perform the experiments. The faculty is responsible for resolving any questions or problems that are identified by the lab assistants or the students. The faculty may supervise the format of the final exam for the lab. They are also responsible for making any necessary corrections to this manual and ensuring that it is continually updated and available. Faculty is expected to allot marks for worksheets in a fair and timely manner. The worksheets should be returned to the students in the next lab period following submission. The lab assistant should report any errors in the lab manual to the faculty.

## 1.1.4 Course Coordinator Responsibilities

The course coordinator is responsible fo making any necessary corrections in Course Description and lab manual. He/She has to ensure that it is continually updated and available to the students in the CMS learning Portal.

# 1.2 Lab Policy and Grading

The student should understand the following policy: **ATTENDANCE:** Attendance is mandatory as per the academic regulations.

LAB RECORD's: The student must:

- 1. Write the work sheets for the allotted experiment and keep them ready before the beginning of eachlab.

- 2. Keep all work in preparation of and obtained during lab.

- 3. Perform the experiment and record the observations in the worksheets.

- 4. Analyze the results and get the work sheets evaluated by the Faculty.

- 5. Upload the evaluated reports online from CMS LOGIN within the stipulated time.

### Grading Policy:

The final grade of this course is awarded using the criterion detailed in the academic regulations. A large portion of the student's grade is determined in the comprehensive final exam of the Laboratory course (SEE PRACTICALS), resulting in a requirement of understanding the concepts and procedure of each lab experiment for successful completion of the lab course.

#### **Pre-Requistes and Co-Requisties:**

Co-Requisites for this lab is microprocessor and microcontroller course and pre-requisites are digital system design course. Students are required to have completed both the courses with better grade in each. Students are also assumed to have completed a programming class and be familiar with the use of a computer-based word processor. Note that the instructor reserves the right to alter any part of this information at their discretion. Any changes will be announced in class and distributed in writing to the students prior to the changes taking effect.

## 1.3 Course Goals and Objectives

This laboratory course will facilitates the students to program 8086 microprocessor and 8051 microcontroller. Win862 software will be used for writing and debugging assembly language programs. The course includes performing arithmetic and logical operations, string manipulations, code conversions and interfacing of I/O devices to processor/controller. The hands-on experience acquired by the student's during the course makes them to carry out processor/controller based projects and extend their knowledge on the latest trends and technologies in the field of embedded system.

More explicitly, the class objectives are:

- 1. Assembly language programming skills ranging from simple arithmetic operations to interfacing real time systems.

- 2. The usage of software tools to design, debug and test microprocessor/microcontroller based projects using assembly language programming

- 3. The design of microcomputer and microcontroller based real-time applications in the fields of communication systems, home based automation systems, automobiles and unmanned applications.

## 1.4 Use of Laboratory Instruments

One of the major goals of this lab is to familiarize the student about 8086 microprocessor, 8051 microcontroller, peripheral devices and assembly language programming. Interfacing can be done between 8086 microprocessor/8051 microcontroller and peripherals like stepper motor, ADC, DAC, Tone generator, traffic light etc and perform specific task by writing assembly language program. Serial communication cable RS232 is connected between PC and ESA86/88 trainer board. In general, all devices have physical limits. These limits are specified by the device manufacturer and are referred to as the device rating. The ratings are usually expressed in terms of voltage limits, current limits, or power limits. It is up to the engineer to make sure that in device operation, these ratings (limit values) are not exceeded. The following rules provide a guideline for instrument protection.

The following rules provide a guideline for instrument protection.

#### 1.4.1 Instrument Protection Rules

- 1. Properly connect the 8086 microprocessor/8051 microcontroller kit with power supply terminals.

- 2. Switch on the power supply after checking connection

- 3. While connecting cables/bus to the devices take care of pins

- 4. Handle the Trainer kit carefully.

- 5. Switch of Trainer kit after completing the experiment.

## 1.5 Data Recording and Reports

#### 1.5.1 The Laboratory Worksheets

Students must record their experimental values in the provided tables in this laboratory manual and reproduce them in the lab worksheets. Worksheets are integral to recording the methodology and results of an experiment. Make plots of data and sketches when these are appropriate in the recording and analysis of observations. Note that the data collected will be an accurate and permanent record of the data obtained during the experiment and the analysis of the results.

#### 1.5.2 The Laboratory Files/Reports

Reports are the primary means of communicating your experience and conclusions to other professionals. In this course you will use the lab report to inform your LTF about what you did and what you have learned from the experience. Engineering results are meaningless unless they can be communicated to others. You will be directed by your LTF to prepare a lab report on a few selected lab experiments during the semester.

#### 1.5.3 Formatting and Style

- 1. The lab report shall be hand written in a lab worksheet.

- 2. The first line of each paragraph should have a left indent.

- 3. All the tables should have titles and should be numbered. Tables should be labelled numerically as Table 1, Table 2, etc. Table captions appear above the table.

- 4. Graphs should be presented as figures. All the figures should have titles and should be numbered. Figure captions appear below the figure. Graphs should have labeled axes and clearly show the scales and units of the axes.

- 5. All the figures and tables must be centered on the page.

- 6. Do not place screenshots of your lab worksheet.

#### 1.5.4 Order of Lab Report Components

- 1. Cover Page Cover page must include lab name and number, your name and the date the lab was performed.

- 2. Objective Clearly state the experiment objective in your own words.

- 3. Equipment Used Indicate which equipment was used in performing the experiment.

For each part of the Lab:

- 1. Write the lab's part number and title.

- 2. Firstly, describe the problem that you studied in this part, give an introduction of the theory, and explain why you did this experiment. Do not lift the text from the lab manual; use your own words.

- 3. Secondly, describe the experimental setup and procedures. Do not follow the lab manual in listing out individual pieces of equipment and assembly instructions. That is not relevant information in a lab report! Instead, explain the program. Your description should take the form of a narrative, and include information not present in the manual, such as descriptions of what happened during intermediate steps of the experiment.

- 4. Thirdly, explain your findings. This is the most important part of your report, because here, you show that you understand the experiment beyond the simple level of completing it. Explain (compare expected results with those obtained). Analyse (analyze experimental error). Interpret (explain your results in terms of theoretical issues and relate to your experimental objectives). All the results should be presented even if there is any inconsistency with the theory.

- 5. Finally, provide a summary of what was learned from this part of the laboratory experiment. If the results seem unexpected or unreliable, discuss them and give possible explanations.

**Conclusions -** The conclusion section should provide a take-home message summing up what has been learned from the experiment:

- 1. Briefly restate the purpose of the experiment (the question it was seeking to answer)

- 2. Identify the main findings (answer to the research question)

- 3. Note the main limitations that are relevant to the interpretation of the results

- 4. Summarize what the experiment has contributed to your understanding of the problem.

**Probing Further Experiments -** Questions pertaining to this lab must be answered at end of laboratory report

# LAB-1 Design a Program Using WIN862

## 2.1 Introduction

Assembly language is the most basic programming language available for any processor. With assembly language, a programmer works only with operations implemented directly on the physical CPU. assembly language is the most powerful computer programming language available, and it gives programmers the insight required to write effective code in high-level languages. Windows Driver For ESA 86/88-2 Trainer (WIN862) is used for programming, execution and debugging. The Intel 8086 is a 16-bit microprocessor that is intended to be used as the CPU in a microcomputer. The term 16-bit means that its arithmetic logic unit, its internal registers, and most of its instructions are designed to work with 16-bit binary words.

# 2.2 Objective

#### 2.2.1 Educational

- 1. Learn about Architecture and operation of 8086 microprocessor.

- 2. Understand instruction set and addressing modes of 8086 microprocessor.

- 3. Learn to perform basic operations MOV, ADD, SUB, MUL and DIV.

#### 2.2.2 Experimental

- 1. To perform arithmetical and logical operations with 8 bit data using registers.

- 2. To use Windows Driver for ESA 86/88-2 Trainer (WIN862) for programming, execution and debugging.

- 3. Observe and analyze the output in registers.

## 2.3 Prelab Preparation:

#### Reading

1. Read register organization, Instruction set, addressing modes of 8086 microprocessor.

#### Written

1. Prior coming to the lab complete part0 of the procedure.

# 2.4 Equipment needed

| S.No | Device              | Range / Rating | Quantity (in No's) |

|------|---------------------|----------------|--------------------|

| 1    | 8086 microprocessor |                | 1                  |

|      | kit/Win 862 with PC |                |                    |

| 2    | Keyboard            |                | 1                  |

| 3    | RS-232              |                | 1                  |

## 2.5 Background

#### Features of the ESA -86/88 Microprocessor Trainer:

- 1. 8086 CPU operating at 8 MHz MAX mode.

- 2. Provision for on-board 8087 (NDP) coprocessor.

- 3. Provision for 256 KB of EPROM and 128 KB of RAM onboard

- 4. Battery backup facility for RAM.

- 5. 48 programmable I/O lines using two 8255's

- 6. Timer1 and Timer2 signals are brought out to header pins

- 7. Priority Interrupt Controller (PIC) for eight input using 8259A

- 8. In standal one mode using on board keypad or with PC compatible system through its  $\operatorname{RS-232}$  interface

- 9. Display is 8 seven segment LED

- 10. Designed and engineered to integrate user's application specific interface conveniently at a minimum cost.

- 11. Powerful and user-friendly keyboard / serial monitor, support in development of application programs.

- 12. Software support for development of programs on Computer, the RS-232C interface cable connecting to computer from the kit facilitates transfer of files between the trainer kit and computer for development and debugging purposes.

- 13. High quality reliable PCB with solder mask on both sides and clear legend prints with maximum details provided for the user.

#### Specifications:

- 1. CPU: Intel 8086 operating at 8 MHz in MAX mode.

- 2. Memory: Total 1MB of memory is in the Kit provided.

- 3. EPROM: 4 JEDEC compatible sockets for EPROM

- 4. RAM: 4 JEDEC compatible sockets for RAM

- 5. Parallel I/O:48 I/O lines using two 8255

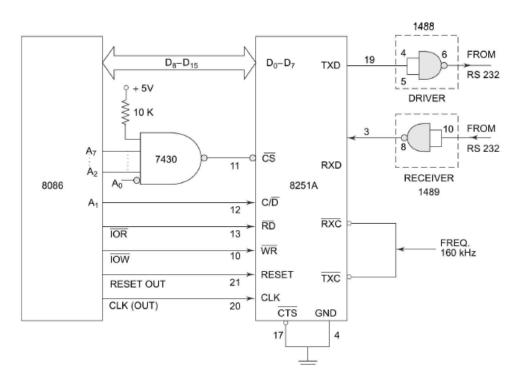

- 6. Serial I/O:One RS-232C compatible interface Using UART 8251A

7. **Timer:** Three 16 bit counter / timers 8253A Counter 1 is used for serial I/O Baud rate generation.

Figure 2.1: ESA86/88 trainer board

- 8. **PIC:** Programmable Interrupt controller using 8253A provides interrupts Vectors for 8 jumpers selectable Internal /External sources.

- 9. Keyboard: keyboard on to the trainer.

- 10. **Display:** 8 seven segment displays

- 11. NIM: Provision for connecting NMI to a key switch

- 12. INTR: Programmable Interrupt controller using 8259A provides Interrupt vectors for 8 jumpers selectable Internal/ External Sources.

- 13. **CPU Bus:** All address, data and control lines are TTL compatible and are terminated in berg strip header.

- 14. **Parallel I/O:**All signals are TTL compatible and Terminated in berg strip header For PPI expansion.

- 15. Serial I/O:Serial port signals are terminated in Standard 9-pin "D type connector.

- 16. Monitor Software:128KB of serial / Keyboard monitor with Powerful commands to enter verify and Debug user programs, including onboard Assemble and disassemble commands.

- 17. **Computer Interface**This can be interfaced to host computer System through the main serial port, also Facilitates uploading, downloading of Intel Hex files between computer and the trainer.

- 18. Power requirements:+5V DC with 1300 mA current rating (Max).

- 19. **Operating Configuration:** Two different modes of operation trainer are possible. They are (i) Serial operation (ii) Keypad operation The first configuration requires a computer system with an RS-232C port, can be used as the controlling device. When a computer system is interfaced to trainer, the driver program must be resident in the computer system. The second mode of operation is achieved through Onboard KEYBOARD / DISPLAY. In this mode, the trainer kit interacts with the user through a computer keyboard and 16x2 LCD Display. This configuration eliminates the need for a computer and offers a convenient way for using the trainer as a stand alone system.

#### **Registers:**

AX:Accumulator register consists of two 8-bit registers AL and AH, which can be combined together and used as a 16-bit register AX. AL in this case contains the low order byte of the word, and AH contains the high-order byte. Accumulator can be used for I/O operations and string manipulation.

BX:Base register consists of two 8-bit registers BL and BH, which can be combined together and used as a 16-bit register BX. BL in this case contains the low-order byte of the word, and BH contains the high-order byte. BX register usually contains a data pointer used for based, based indexed or register indirect addressing.

#### Addressing modes:

Immediate addressing mode: In this type of addressing, immediate data is a part of instruction, and appears in the form of successive byte or bytes. Example: MOV AX, 0005H. In the above example, 0005H is the immediate data. The immediate data may be 8- bit or 16-bit in size. **Instruction set:**

MOV instruction: It is a general purpose instruction to transfer byte or word from register to register, memory to register, register to memory or with immediate addressing. General Format : MOV destination, source Here the source and destination needs to be of the same size, that is both 8 bit or both 16 bit. MOV instruction does not affect any flags.

#### ADD instruction

Add instruction is used to add the current contents of destination with that of source and store the result in destination. Here we can use register and/or memory locations. AF, CF, OF, PF, SF, and ZF flags are affected General Format: ADD Destination, Source

#### SUB instruction

SUB instruction is used to subtract the current contents of destination with that of source and store the result in destination. Here we can use register and/or memory locations. AF, CF, OF, PF, SF, and ZF flags are affected General Format: SUB Destination, Source

#### MUL instruction

This instruction multiplies an unsigned byte or Word by the contents of AL. The Unsigned byte or word may be in any one of the general purpose registers or memory locations. In case of 32-bit results the most significant word of the result will be stored in DX, while the least significant of the result is stored in AX. The flags are modified depending on the result.

#### DIV instruction

It divides an unsigned word or double word by a 16-bit or 8-bit operand. The dividend must be in AX for 16-bit operation and divisor must be specified using any one of the addressing modes except immediate. The result will be in AL(quotient) while AH will contain the remainder. If the result is too big to fit in AL, type0(divide by zero) and an interrupt is generated. In case of double word dividend (32-bit), the higher word should be in DX and lower word should be in AX. The divisor must be specified using any one of the addressing modes except immediate. The quotient will be in AX and the remainder will be in DX.

#### 2.6 Safety Precautions

- 1. Properly connect the 8086 microprocessor kit with power supply terminals.

- 2. Switch on the power supply after checking connections

- 3. Handle the Trainer kit carefully.

## 2.7 Procedure

#### (i)Execution procedure for 8086 (for registers):

- 1. Switch On Power Supply

- 2. Check if DIP switches board is in serial or keyboard mode (Serial mode = 1 on, Board mode = 4 On)

- 3. Press Reset

- 4. Press "EB" (Examine Byte)

- 5. Enter Starting Memory location (Ex: 2000)

- 6. Press next button, Enter OP-Code value

- 7. Then press next button Enter 2nd memory location and op code

- 8. Enter up to n values **Execution:**

- 9. Press Exec. Button

- 10. Press Go enter starting memory location

- 11. Press Exec.

- 12. Press ER (Examine Register)

- 13. Press AX (Now see the result in Ax)

#### (ii)Execution procedure for 8086 (for memory locations):

- 1. Switch On Power Supply

- 2. Check if DIP switches board is in serial or keyboard mode (Serial mode = 1 on, Board mode = 4 On)

- 3. Press Reset

- 4. Press "EB" (Examine Byte)

- 5. Enter Starting Memory location (Ex: 2000)

- 6. Press next button, Enter OP-Code value

- 7. Then press next button Enter 2nd memory location and op code

- 8. Enter up to n values **Execution**:

- 9. Press Exec. Button

- 10. Press Go enter starting memory location

- 11. Press Exec.

- 12. Press EB give input memory location and input values

- 13. Press Exec.

- 14. Press Go Give starting memory location

- 15. Press Exec.

- 16. Press Go Now observe the results in memory location

#### (iii)WIN862 Software procedure(for Registers):

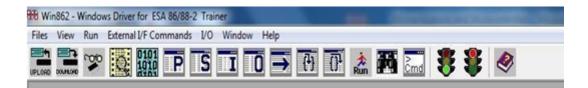

1. Open Win862 icon on desktop and opened Window

Figure 2.2: Win862 icon

| Hit Hi | Win862 - Windows Driver for ESA 86/88-2 Trainer      |     |                |         |  |  |       |  |

|--------|------------------------------------------------------|-----|----------------|---------|--|--|-------|--|

| Files  | Files View Run External I/F Commands I/O Window Help |     |                |         |  |  |       |  |

| UPLORD |                                                      | 100 | 0101<br>1910 P | S I O → |  |  | 🍍 🛢 🤌 |  |

Figure 2.3: win862 opened window

2. Click on Assembler and give starting address (0000:4000), then press enter button

Figure 2.4: Assembler icon

Figure 2.5: Assembler Window

3. Then write 1st Instruction then press enter button.

- 4. Then write 2nd Instruction then press enter button.

- 5. Then write up to nth Instruction then press enter button and close the Assembler window.

- 6. Now click on Dis Assembler and give starting address (Like 0000:4000) then press enter button.

Figure 2.6: Disassembler Window

- 7. Click on Set PC then give starting address then press Enter button.

- 8. Click on Run (check whether program is executed or not)

- 9. Click on view registers

Figure 2.7: view registers

#### (iv)WIN862 Software procedure(for Memory locations):

- 1. Open Win862 icon on desktop.

- 2. Click on Assembler and give starting address (Like 0000:4000) then press Enter button.

- 3. Then write 1st Instruction then press enter button.

- 4. Then write 2nd Instruction then press enter button.

- 5. Then write up to nth Instruction then press enter button and close the Assembler window.

- 6. Now click on Dis Assembler and give starting address (Like 0000:4000) then press enter button.

- 7. Click on Set PC then give starting address then press Enter button.

- 8. Click on Run (check whether program is executed or not)

- 9. Click on view memory

- 10. Now enter input address

- 11. Click on Modify and Give desired input values

- 12. Click on Set PC. Enter initial address and press Dis-Assembler

- 13. Click on Run (check whether program is executed or not)

14. Now observe the result in view memory.

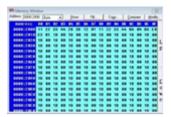

Figure 2.8: view memory

- 15. Click on view memory and enter destination address then press enter button

- 16. Now observe the result.

| ann (1000.3   | 00 | žyna – |    |   | - 24 | -  | L   | 19. |     | 0  | φ.  |    | Ç. |   |    | t an |

|---------------|----|--------|----|---|------|----|-----|-----|-----|----|-----|----|----|---|----|------|

| Address.      |    | ŧ٩.    |    | - |      |    |     |     |     |    |     |    |    |   |    |      |

|               |    | 32     | 88 | - | 28   | 28 | 42  | -   | 44  | 39 | 39  | 44 |    | - |    |      |

|               |    | 85     | -  |   | -    | -  | -   | -   | 18  |    | 18  |    | 18 |   | 18 |      |

|               | -  |        | -  | - | -    | -  | -   | -   | -   | -  | 18  | -  | 18 | - | 18 |      |

|               | -  |        | -  | - | -    | -  | -   | -   | -   |    | -18 | -  | 18 |   | -  |      |

|               | -  |        | 18 | - | -    | -  | -   | -   | 18  | -  | 18  |    | 18 |   | 18 |      |

|               | -  |        | -  | - | -    |    | -   | -   | -   | -  | -   |    | 18 |   | -  |      |

|               | -  |        | -  | - | -    |    | -18 | -   | 18  | -  | 18  |    | 18 |   | 18 |      |

|               | -  |        | -  | - | -    | -  | -   | -   | -   | -  | -   | -  | 18 |   | 10 |      |

|               | -  |        | -  | - | -    | -  | -   | -   | -18 |    | 18  |    | 18 |   | 18 |      |

|               |    |        | -  | - | -    |    | -   | -   | -   | -  | -   |    | 18 |   | 18 |      |

|               | -  |        | -  |   | -    |    | -   | -   | -   |    | -   |    | 18 |   | -  |      |

|               | -  |        |    |   | -    |    | -   | -   | 18  | -  | 18  |    | 18 |   | 18 |      |

| CONTRACTOR OF | -  |        | -  | - | -    | -  | -   | -   | -   | -  | -   | -  | 18 |   | -  |      |

|               | -  |        | -  | - | -    |    | -   | -   | -   | -  | 18  |    | 18 |   | 18 |      |

|               |    |        |    | - | -    | _  | -   | -   | -   | -  | -   |    | -  |   | -  |      |

Figure 2.9: memory window

#### Programs: 8-bit arithmetic operations

1. Addition:

| MEMORY<br>LOCATION | OP-CODE | LABLE | MNEMONIC<br>OPERAND | COMMENTS |

|--------------------|---------|-------|---------------------|----------|

|                    |         |       | MOV AL,43           |          |

|                    |         |       | MOV BL,11           |          |

|                    |         |       | ADD AL,BL           |          |

|                    |         |       | INT 3               |          |

#### **Observation Table:**

| Inp      | out  | Output   |      |  |  |  |  |

|----------|------|----------|------|--|--|--|--|

| Register | Data | Register | Data |  |  |  |  |

| AL       | 43   | AL       |      |  |  |  |  |

| BL       | 11   |          |      |  |  |  |  |

#### 2. Subtraction:

| MEMORY<br>LOCATION | OP-CODE | LABLE | MNEMONIC<br>OPERAND | COMMENTS |

|--------------------|---------|-------|---------------------|----------|

|                    |         |       | MOV AL,43           |          |

|                    |         |       | MOV BL,11           |          |

|                    |         |       | SUB AL,BL           |          |

|                    |         |       | INT 03              |          |

#### **Observation Table:**

| Inj      | out  | Output   |      |  |  |  |

|----------|------|----------|------|--|--|--|

| Register | Data | Register | Data |  |  |  |

| AL       | 43   | AL       |      |  |  |  |

| BL       | 11   |          |      |  |  |  |

#### 3. Multiplication:

| MEMORY<br>LOCATION | OP-CODE | LABEL | MNEMONIC<br>OPERAND | COMMENTS |

|--------------------|---------|-------|---------------------|----------|

|                    |         |       | MOV AL,43           |          |

|                    |         |       | MOV BL,11           |          |

|                    |         |       | MUL BL              |          |

|                    |         |       | INT 3               |          |

#### **Observation Table:**

| In       | put  | Outp     | out  |

|----------|------|----------|------|

| Register | Data | Register | Data |

| AL       | 43   | AX       |      |

| BL       | 11   |          |      |

#### 4. Division:

| MEMORY<br>LOCATION | OP-CODE | LABEL | MNEMONIC<br>OPERAND | COMMENTS |

|--------------------|---------|-------|---------------------|----------|

|                    |         |       | MOV AL,10           |          |

|                    |         |       | MOV BL,02           |          |

|                    |         |       | DIV BL              |          |

|                    |         |       | INT 3               |          |

#### **Observation Table:**

| Inț      | out  | Outp     | out  |

|----------|------|----------|------|

| Register | Data | Register | Data |

| AL       | 10   | AL       |      |

| BL       | 02   | AH       |      |

## 2.8 Probing Further Experiments

- 1. Specify the registers used to hold quotient and remainder to perform unsigned division operation, consider 16-bit dividend and 8-bit divisor.

- 2. What is the procedure to change a single line in disassembler.

- 3. Which flag will be enabled during division error.

# LAB-2 16 bit arithmetic and logical operations

## 3.1 Introduction

The assembly language programs for performing arithmetic and logical operations are composed by using mnemonics, various addressing modes, instructions and registers of microprocessor. The 8086 microprocessor is used to execute the instructions of assembly language program one by one. The results stored in destination registers are compared against theoretical values obtained. Arithmetic operations includes Addition, Subtraction, Multiplication, Division and logical Operations includes AND, OR, XOR.

## 3.2 Objective

#### 3.2.1 Educational

- 1. Learn about the architecture of 8086 microprocessor.

- 2. Learn about Flag manipulation instructions and how they are set and reset in assembly operations.

- 3. Learn what registers are, why they are important and how to use them

- 4. Discover direct and immediate addressing and how they are used in assembly programming

- 5. Discover how to jump to labeled parts of code based on flags

#### 3.2.2 Experimental

- 1. Write an assembly language program to perform 16-bit arithmetic operations.

- 2. Write an assembly language program to perform 16-bit logical operations.

- 3. Observe and analyze the output in registers.

## 3.3 Prelab Preparation:

#### Reading

1. Read register organization, Instruction set, addressing modes of 8086 microprocessor.

#### Written

1. Prior coming to the lab complete part0 of the procedure.

# 3.4 Equipment needed

| S.No | Device               | Range / Rating | Quantity (in No's) |

|------|----------------------|----------------|--------------------|

| 1    | 8086 microprocessor  |                | 1                  |

|      | kit/Win862 with $PC$ |                |                    |

| 2    | Keyboard             |                | 1                  |

| 3    | RS-232               |                | 1                  |

# 3.5 Background

#### **Registers:**

AX:Accumulator register consists of two 8-bit registers AL and AH, which can be combined together and used as a 16-bit register AX. AL in this case contains the low order byte of the word, and AH contains the high-order byte. Accumulator can be used for I/O operations and string manipulation. BX:Base register consists of two 8-bit registers BL and BH, which can be combined together and used as a 16-bit register BX. BL in this case contains the low-order byte of the word, and BH contains the high-order byte. BX register usually contains a data pointer used for based, based indexed or register indirect addressing.

CX:Count register consists of two 8-bit registers CL and CH, which can be combined together and used as a 16-bit register CX. When combined, CL register contains the low order byte of the word, and CH contains the high-order byte. Count register can be used in Loop, shift/rotate instructions and as a counter in string manipulation

DX:Data register consists of two 8-bit registers DL and DH, which can be combined together and used as a 16-bit register DX. When combined, DL register contains the low order byte of the word, and DH contains the high-order byte. Data register can be used as a port number in I/O operations. In integer 32-bit multiply and divide instruction the DX register contains high-order word of the initial or resulting number.

#### Addressing modes:

#### Immediate addressing mode:

In this type of addressing, immediate data is a part of instruction, and appears in the form of successive byte or bytes. Example: MOV AX, 0005H. In the above example, 0005H is the immediate data. The immediate data may be 8- bit or 16-bit in size.

#### Instruction set:

#### MOV instruction:

It is a general purpose instruction to transfer byte or word from register to register, memory to register, register to memory or with immediate addressing. General Format : MOV destination, source Here the source and destination needs to be of the same size, that is both 8 bit or both 16 bit. MOV instruction does not affect any flags.

ADD instruction:

Add instruction is used to add the current contents of destination with that of source and store the result in destination. Here we can use register and/or memory locations. AF, CF, OF, PF, SF, and ZF flags are affected General Format: ADD Destination, Source

#### SUB instruction

SUB instruction is used to subtract the current contents of destination with that of source and store the result in destination. Here we can use register and/or memory locations. AF, CF, OF, PF, SF, and ZF flags are affected General Format: SUB Destination, Source

#### MUL instruction:

This instruction multiplies an unsigned byte or Word by the contents of AL. The Unsigned byte or word may be in any one of the general purpose registers or memory locations. In case of 32-bit results the most significant word of the result will be stored in DX, while the least significant of the result is stored in AX. The flags are modified depending on the result.

DIV instruction:

It divides an unsigned word or double word by a 16-bit or 8-bit operand. The dividend must be in AX for 16-bit operation and divisor must be specified using any one of the addressing modes except immediate. The result will be in AL(quotient) while AH will contain the remainder. If the result is too big to fit in AL, type0(divide by zero) and an interrupt is generated. In case of double word dividend (32-bit), the higher word should be in DX and lower word should be in AX. The divisor must be specified using any one of the addressing modes except immediate. The quotient will be in AX and the remainder will be in DX.

AND instruction:

This instruction logically ANDs each bit of the source byte/word with the corresponding bit in the destination and stores the result in destination. The source can be an immediate number, register or memory location, register can be a register or memory location. The CF and OF flags are both made zero, PF, ZF, SF are affected by the operation and AF is undefined. General Format: AND Destination, Source

OR instruction:

This instruction logically ORs each bit of the source byte/word with the corresponding bit in the destination and stores the result in destination. The source can be an immediate number, register or memory location, register can be a register or memory location. The CF and OF flags are both made zero, PF, ZF, SF are affected by the operation and AF is undefined. General Format: OR Destination, Source

XOR instruction:

The XOR operation is again carried out in a similar way to the AND and OR operation. The constraints on the operands are also similar. The XOR operation gives a high output, when the 2 input bits are dissimilar. Otherwise, the output is zero. General Format: XOR Destination, Source

INT 03 instruction:

The INT 3 instruction generates a special one byte opcode (CC) that is intended for calling the debug exception handler. (This one byte form is valuable because it can be used to replace the first byte of any instruction with a breakpoint, including other one byte instructions, without over-writing other code).

General Format: INT 03

## **3.6** Safety Precautions:

- 1. Properly connect the 8086 microprocessor kit with power supply terminals.

- 2. Switch on the power supply after checking connections

- 3. Handle the Trainer kit carefully.

## 3.7 Procedure

#### WIN862 Software procedure(for Registers):

1. Open Win862 icon on desktop and opened Window

Figure 3.1: Win862 icon

Figure 3.2: win862 opened window

2. Click on Assembler and give starting address (0000:4000), then press enter button

Figure 3.3: Assembler icon

Figure 3.4: Assembler Window

- 3. Then write 1st Instruction then press enter button.

- 4. Then write 2nd Instruction then press enter button.

- 5. Then write up to nth Instruction then press enter button and close the Assembler window.

- 6. Now click on Dis Assembler and give starting address (Like 0000:4000) then press enter button.

Figure 3.5: Disassembler Window

- 7. Click on Set PC then give starting address then press Enter button.

- 8. Click on Run (check whether program is executed or not)

- 9. Click on view registers

Figure 3.6: view registers

# Programs: 16 Bit arithmetic and logical operations using WIN862 software and 8086 microprocessor.

Arithmetic Operations:

#### 1. Addition:

| MEMORY<br>LOCATION | OP-CODE | LABLE | MNEMONIC<br>OPERAND | COMMENTS |

|--------------------|---------|-------|---------------------|----------|

|                    |         |       | MOV AX,4343         |          |

|                    |         |       | MOV BX,1111         |          |

|                    |         |       | ADD AX,BX           |          |

|                    |         |       | INT 3               |          |

#### **Observation Table:**

| Inp      | out  | Outp     | out  |

|----------|------|----------|------|

| Register | Data | Register | Data |

| AX       | 4343 | AX       |      |

| BX       | 1111 |          |      |

#### 2. Subtraction:

| MEMORY<br>LOCATION | OP-CODE | LABLE | MNEMONIC<br>OPERAND | COMMENTS |

|--------------------|---------|-------|---------------------|----------|

|                    |         |       | MOV AX,4343         |          |

|                    |         |       | MOV BX,1111         |          |

|                    |         |       | SUB AX,BX           |          |

|                    |         |       | INT 03              |          |

#### **Observation Table:**

| In       | put  | Outp     | out  |

|----------|------|----------|------|

| Register | Data | Register | Data |

| AX       | 4343 | AX       |      |

| BX       | 1111 |          |      |

## 3. Multiplication:

| MEMORY<br>LOCATION | OP-CODE | LABEL | MNEMONIC<br>OPERAND | COMMENTS |

|--------------------|---------|-------|---------------------|----------|

|                    |         |       | MOV AX,4343         |          |

|                    |         |       | MOV BX,1111         |          |

|                    |         |       | MUL BX              |          |

|                    |         |       | INT 3               |          |

#### **Observation Table:**

| Inț      | out  | Outp     | out  |

|----------|------|----------|------|

| Register | Data | Register | Data |

| AX       | 4343 | AX       |      |

| BX       | 1111 | DX       |      |

#### 4. Division:

| MEMORY<br>LOCATION | OP-CODE | LABEL | MNEMONIC<br>OPERAND | COMMENTS |

|--------------------|---------|-------|---------------------|----------|

|                    |         |       | MOV AX,0080         |          |

|                    |         |       | MOV BX,0008         |          |

|                    |         |       | DIV BX              |          |

|                    |         |       | INT 3               |          |

## **Observation Table:**

| Ing      | out           | Output |      |  |  |

|----------|---------------|--------|------|--|--|

| Register | Register Data |        | Data |  |  |

| AX       | 4343          | AX     |      |  |  |

| BX       | 1111          | DX     |      |  |  |

# Logical Operations :

## 1. AND:

| MEMORY<br>LOCATION | OP-CODE | LABLE | MNEMONIC<br>OPERAND        | COMMENTS |

|--------------------|---------|-------|----------------------------|----------|

|                    |         |       | MOV AX,4343<br>MOV BX,1111 |          |

|                    |         |       | AND AX,BX                  |          |

|                    |         |       | INT 3                      |          |

## **Observation Table:**

| Ing      | out  | Output   |      |  |

|----------|------|----------|------|--|

| Register | Data | Register | Data |  |

| AX       | 4343 | AX       |      |  |

| BX       | 1111 |          |      |  |

## 2. **OR:**

| MEMORY<br>LOCATION | OP-CODE | LABLE | MNEMONIC<br>OPERAND                             | COMMENTS |

|--------------------|---------|-------|-------------------------------------------------|----------|

|                    |         |       | MOV AX,4343<br>MOV BX,1111<br>OR AX,BX<br>INT 3 |          |

## **Observation Table:**

| Inț      | out  | Output   |      |  |  |

|----------|------|----------|------|--|--|

| Register | Data | Register | Data |  |  |

| AX       | 4343 | AX       |      |  |  |

| BX       | 1111 |          |      |  |  |

#### 3. XOR:

| MEMORY<br>LOCATION | OP-CODE | LABLE | MNEMONIC<br>OPERAND                              | COMMENTS |

|--------------------|---------|-------|--------------------------------------------------|----------|

|                    |         |       | MOV AX,4343<br>MOV BX,1111<br>XOR AX,BX<br>INT 3 |          |

### **Observation Table:**

| Ing      | out  | Output   |      |  |  |

|----------|------|----------|------|--|--|

| Register | Data | Register | Data |  |  |

| AX       | 4343 | AX       |      |  |  |

| BX       | 1111 |          |      |  |  |

# 3.8 Probing Further Experiments

- 1. Specify the registers used to hold double word dividend and 16-bit divisor to perform unsigned division operation, and also for quotient and remainder after division.

- 2. To perform logical operations like NAND, NOR which instructions should be used from the instruction set of 8086 microprocessor.

- 3. How to write a program to add the contents of memory location 2000H:0500H to the contents of 3000H:0600H and store the result in 5000H:0700H. Use data segment register initialization instructions.

# LAB-3 Multibyte Addition and Subraction

## 4.1 Introduction

The multibyte data can be added either byte by byte or word by word. The number of bytes in the data can be used for the number of additions. One of the register is used to account for the final carry. Similarly the multibyte data can be Subtracted either byte by byte or word by word. The number of bytes in the data can be used for the number of subtractions. One of the register is used to account for the final borrow. To perform multibyte addition or subtraction we require three address pointers. Two pointers for input data and one pointer for output data.

## 4.2 Objective

#### 4.2.1 Educational

- 1. Learn about the architecture of 8086 microprocessor.

- 2. Learn about Flags and how they are set and reset in assembly operations.

- 3. Learn what registers are, why they are important and how to use them

- 4. Discover register indirect, Indexed addressing and how they are used in assembly programming

- 5. Discover how to jump to labeled parts of code based on flags.

#### 4.2.2 Experimental

- 1. Write an assembly language program to perform multibyte addition.

- 2. Write an assembly language program to perform multibyte subtraction.

- 3. Observe and analyze the outputs using registers and memory locations.

## 4.3 Prelab Preparation:

#### Reading

1. Read register organization, Instruction set, addressing modes of 8086 microprocessor.

#### Written

1. Prior coming to the lab complete part0 of the procedure.

# 4.4 Equipment needed

| S.No | Device               | Range / Rating | Quantity (in No's) |

|------|----------------------|----------------|--------------------|

| 1    | 8086 microprocessor  |                | 1                  |

|      | kit/Win862 with $PC$ |                |                    |

| 2    | Keyboard             |                | 1                  |

| 3    | RS-232               |                | 1                  |

# 4.5 Background

#### **Registers:**

AX:Accumulator register consists of two 8-bit registers AL and AH, which can be combined together and used as a 16-bit register AX. AL in this case contains the low order byte of the word, and AH contains the high-order byte. Accumulator can be used for I/O operations and string manipulation.

BX:Base register consists of two 8-bit registers BL and BH, which can be combined together and used as a 16-bit register BX. BL in this case contains the low-order byte of the word, and BH contains the high-order byte. BX register usually contains a data pointer used for based, based indexed or register indirect addressing.

CX:Count register consists of two 8-bit registers CL and CH, which can be combined together and used as a 16-bit register CX. When combined, CL register contains the low order byte of the word, and CH contains the high-order byte. Count register can be used in Loop, shift/rotate instructions and as a counter in string manipulation

SI:Source Index (SI) is a 16-bit register. SI is used for indexed, based indexed and register indirect addressing, as well as a source data addresses in string manipulation instructions are used in conjunction with the DS register to point the data locations in the data segment.

DI:Destination Index (DI) is a 16-bit register is used in conjunction with the ES register for string operations. DI is used for indexed, based indexed and register indirect addressing, as well as a destination data addresses in string manipulation instructions. In short, Destination Index and SI Source Index registers are used to hold address.

#### Addressing modes:

Immediate addressing mode:

In this type of addressing, immediate data is a part of instruction, and appears in the form of successive byte or bytes.

Example: MOV AX, 0005H. In the above example, 0005H is the immediate data. The immediate data may be 8- bit or 16-bit in size.

Register indirect addressing mode:

Sometimes, the address of the memory location which contains data or operands is determined in an indirect way, using the offset registers. The mode of addressing is known as register indirect mode. In this addressing mode, the offset address of data is in either BX or SI or DI Register. The default segment is either DS or ES.

Example: MOV AX, [BX].

Indexed addressing mode:

In this addressing mode, offset of the operand is stored one of the index registers. DS and ES are the default segments for index registers SI and DI respectively.

Example: MOV AX, [SI] Here, data is available at an offset address stored in SI in DS.

#### Instruction set:

MOV instruction:

It is a general purpose instruction to transfer byte or word from register to register, memory to register, register to memory or with immediate addressing. General Format : MOV destination, source Here the source and destination needs to be of the same size, that is both 8 bit or both

16 bit.MOV instruction does not affect any flags.

ADD instruction:

Add instruction is used to add the current contents of destination with that of source and store the result in destination. Here we can use register and/or memory locations. AF, CF, OF, PF, SF, and ZF flags are affected

General Format: ADD Destination, Source

SUB instruction

SUB instruction is used to subtract the current contents of destination with that of source and store the result in destination. Here we can use register and/or memory locations. AF, CF, OF, PF, SF, and ZF flags are affected General Format: SUB Destination, Source

INC and DEC instructions

INC and DEC instructions are used to increment and decrement the content of the specified destination by one. AF, CF, OF, PF, SF, and ZF flags are affected.

JNZ instruction:

The jnz (or jne) instruction is a conditional jump that follows a test. It jumps to the specified location if the Zero Flag (ZF) is cleared (0). jnz is commonly used to explicitly test for something not being equal to zero General Format: JNZ location

INT 03 instruction:

The INT 3 instruction generates a special one byte opcode (CC) that is intended for calling the debug exception handler. (This one byte form is valuable because it can be used to replace the first byte of any instruction with a breakpoint, including other one byte instructions, without over-writing other code).

General Format: INT 03

## 4.6 Safety Precautions

- 1. Properly connect the 8086 microprocessor kit with power supply terminals.

- 2. Switch on the power supply after checking connections

- 3. Handle the Trainer kit carefully.

# 4.7 Procedure

#### WIN862 Software procedure(for memory locations):

1. Open Win862 icon on desktop ) and opened Window

Figure 4.1: Win862 icon

Figure 4.2: win862 opened window

2. Click on Assembler and give starting address (0000:4000), then press enter button

Figure 4.3: Assembler icon

Figure 4.4: Assembler Window

- 3. Then write 1st Instruction then press enter button.

- 4. Then write 2nd Instruction then press enter button.

- 5. Then write up to nth Instruction then press enter button and close the Assembler window.

- 6. Now click on Dis Assembler and give starting address (Like 0000:4000) then press enter button.

Figure 4.5: Disassembler Window

- 7. Click on Set PC then give starting address then press Enter button.

- 8. Click on Run (check whether program is executed or not)

- 9. Click on view memory

- 10. Now enter input address

- 11. Click on Modify and Give desired input values

- 12. Click on Set PC. Enter initial address and press Dis-Assembler

- 13. Click on Run (check whether program is executed or not)

14. Now observe the result in view memory.

Figure 4.6: view memory

15. Click on view memory and enter destination address then press enter button

16. Now observe the result.

| -     | 100.3 | 00 | \$100 |    |   | - 24 | -  | L   | 19. |    | 0  | φ. |    | Çm | - |    |   |   |

|-------|-------|----|-------|----|---|------|----|-----|-----|----|----|----|----|----|---|----|---|---|

| ***   |       |    | - 11  |    | - |      |    |     |     |    |    |    |    |    |   |    |   |   |

|       | 1888  |    | 32    | 88 | - | 28   | 28 | 42  | -   | 44 | 39 | 39 | 44 |    |   |    |   |   |

|       |       | -  | 85    | -  |   | -    | -  | -   | -   | 18 |    | 18 |    | 18 |   | 18 |   |   |

|       | 1816  | -  |       | -  | - | -    | -  | -   | -   | -  | -  | 18 | -  | 18 |   | 18 |   |   |

|       | 1494  |    |       | -  | - | -    |    | -   | -   | -  | -  | -  |    | 18 |   | -  |   |   |

|       |       | -  |       | 18 | - | -    | -  | -   | -   | 18 | -  | 18 |    | 18 |   | 18 |   |   |

|       | 388.8 |    |       | 10 | - | -    | -  | -   | -   | -  |    | -  |    | 18 |   | -  |   |   |

|       | 1010  | -  |       | -  | - | -    |    | -18 | -   | 18 | -  | 18 | -  | 18 |   | 18 |   |   |

|       | 1878  |    | -     | 10 | - |      | -  | -   | -   | -  | -  | -  |    | 18 |   | 18 |   |   |

|       |       | -  |       | -  |   | -    |    | -   | -   | -  |    | 18 |    | 18 |   | 18 |   |   |

|       | 1899  |    |       | 18 | - | -    | -  | -   | -   | -  | -  | 18 | -  | 18 |   | 18 |   |   |

|       | 2000  |    |       | -  |   | -    |    | -   | -   | -  |    | -  |    | -  |   | -  |   |   |

|       |       | -  |       | -  |   | -    |    | -   | -   | -  | -  | 18 | -  | 18 |   | 18 |   |   |

|       | 180   |    |       | -  |   | -    | -  | -   |     | -  | -  | -  |    | 18 |   | -  |   | ł |

|       | 1000  | -  |       | -  |   | -    |    | -   | -   | 18 | -  | 18 | -  | 18 |   | 18 |   |   |

|       | 181   |    |       | -  | - |      |    | -   | -   | -  | -  | 18 | -  | 18 |   | 18 |   |   |

| 10.10 | 100   | -  | -     | -  | - | -    | -  |     | -   | -  | -  | -  | -  | -  | - | -  | - |   |

Figure 4.7: memory window

Programs: Multibyte Addition and Subtraction using WIN862 software and 8086 microprocessor.

| MEMORY<br>LOCATION | OP-CODE | LABLE | MNEMONIC<br>OPERAND | COMMENTS |

|--------------------|---------|-------|---------------------|----------|

|                    |         |       | MOV AX,0000         |          |

|                    |         |       | MOV SI, 2000        |          |

|                    |         |       | MOV DI, 3000        |          |

|                    |         |       | MOV BX, 2008        |          |

|                    |         |       | MOV CL, 04          |          |

|                    |         | UP:   | MOV AL, [SI]        |          |

|                    |         |       | ADD AL, [BX]        |          |

|                    |         |       | MOV [DI], AL        |          |

|                    |         |       | INC SI              |          |

|                    |         |       | INC BX              |          |

|                    |         |       | INC DI              |          |

|                    |         |       | DEC CL              |          |

|                    |         |       | JNZ UP              |          |

|                    |         |       | INT 3               |          |

1. Multibyte Addition:

#### Observation Table:

|                    | Iı   | Output             |      |                    |      |

|--------------------|------|--------------------|------|--------------------|------|

| MEMORY<br>LOCATION | Data | MEMORY<br>LOCATION | Data | MEMORY<br>LOCATION | Data |

| 2000               |      | 2008               |      | 3000               |      |

| 2001               |      | 2009               |      | 3001               |      |

| 2002               |      | 200A               |      | 3002               |      |

| 2003               |      | 200B               |      | 3003               |      |

### 2. Multibyte Subtraction:

| MEMORY<br>LOCATION | OP-CODE | LABLE | MNEMONIC<br>OPERAND | COMMENTS |

|--------------------|---------|-------|---------------------|----------|

|                    |         |       | MOV AX,0000         |          |

|                    |         |       | MOV SI, 2000        |          |

|                    |         |       | MOV DI, 3000        |          |

|                    |         |       | MOV BX, 2008        |          |