## **LECTURE NOTES**

ON

## MICROCONTROLLER & DIGITAL SIGNAL PROCESSING-R16

**B.Tech VI semester**

Ms. J.SRAVANA

(Assistant professor)

ELECRTONICS AND COMMUNICATION ENGINEERING

## INSTITUTE OF AERONAUTICAL ENGINEERING (Autonomous)

(Autonomous)DUNDIGAL, HYDERABAD - 50004

# MODULE – I

ala kaleka ka

# **MICROPROCESSORS AND**

# **MICROCONTROLLER**

## UNIT-1

## **Microprocessor and Microcontroller**

## **8086 Microprocessor**

#### Introduction to 8085 Microprocessor:

#### The Salient Features of 8085 Microprocessor:

- 8085 is an 8 bit microprocessor, manufactured with N-MOS technology.

- It has 16-bit address bus and hence can address up to  $2^{16} = 65536$  bytes (64KB) memory locations through A<sub>0</sub>-A<sub>15</sub>.

- The first 8 lines of address bus and 8 lines of data bus are multiplexed AD<sub>0</sub> AD<sub>7</sub>.

Data bus is a group of 8 lines D<sub>0</sub> D<sub>7</sub>.

- It supports external interrupt request.8085 consists of 16 bit program counter (PC) and stack pointer (SP).

- Six 8-bit general purpose register arranged in pairs: BC, DE, HL.

- It requires a signal +5V power supply and can operate at 3 MHz, 5 MHz and 6 MHz Serial in/Serial out Port.

- It is enclosed with 40 pins DIP (Dual in line package).

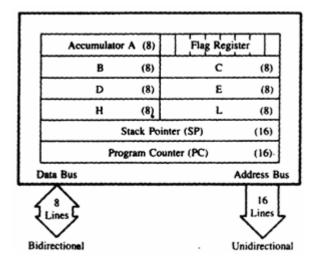

### **Internal Architecture of 8085:**

Architecture of 8085

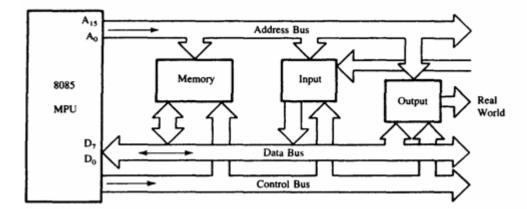

#### 8085 Bus Structure:

#### Address Bus:

- The address bus is a group of 16 lines generally identified as A0 to A15.

- The address bus is unidirectional: bits flow in one direction-from the MPU to peripheral devices.

- The MPU uses the address bus to perform the first function: identifying a peripheral or a memory location.

## **Data Bus:**

- The data bus is a group of eight lines used for data flow.

- These lines are bi-directional data flow in both directions between the MPU and memory and peripheral devices.

- The MPU uses the data bus to perform the second function: transferring binary information.

- The eight data lines enable the MPU to manipulate 8-bit data ranging from 00 to FF (28 = 256 numbers).

- The largest number that can appear on the data bus is 11111111.

## **Control Bus:**

- The control bus carries synchronization signals and providing timing signals.

- The MPU generates specific control signals for every operation it performs. These signals are used to identify a device type with which the MPU wants to communicate.

#### **Registers of 8085:**

- The 8085 have six general-purpose registers to store 8-bit data during program execution.

- These registers are identified as B, C, D, E, H, and L.

- They can be combined as register pairs-BC, DE, and HL-to perform some 16-bit operations.

## Accumulator (A):

- The accumulator is an 8-bit register that is part of the arithmetic/logic unit (ALU).

- This register is used to store 8-bit data and to perform arithmetic and logical operations.

- The result of an operation is stored in the accumulator.

### Flags:

- The ALU includes five flip-flops that are set or reset according to the result of an operation.

- The microprocessor uses the flags for testing the data conditions.

- They are Zero (Z), Carry (CY), Sign (S), Parity (P), and Auxiliary Carry (AC) flags. The most commonly used flags are Sign, Zero, and Carry.

The bit position for the flags in flag register is,

| D <sub>7</sub> | $D_6$ | Ds | $D_4$ | D3 | $D_2$ | D1 | D <sub>0</sub> |

|----------------|-------|----|-------|----|-------|----|----------------|

| S              | Z     |    | AC    |    | Р     |    | СҮ             |

#### 1. Sign Flag (S):

After execution of any arithmetic and logical operation, if D7 of the result is 1, the sign flag is set. Otherwise it is reset.

D7 is reserved for indicating the sign; the remaining is the magnitude of number.

If D7 is 1, the number will be viewed as negative number. If D7 is 0, the number will be viewed as positive number.

#### 2. Zero Flag (z):

If the result of arithmetic and logical operation is zero, then zero flag is set otherwise it is reset.

#### 3. Auxiliary Carry Flag (AC):

If D3 generates any carry when doing any arithmetic and logical operation, this flag is set. Otherwise it is reset.

#### 4. Parity Flag (P):

If the result of arithmetic and logical operation contains even number of 1's then this flag will be set and if it is odd number of 1's it will be reset.

#### 5. Carry Flag (CY):

If any arithmetic and logical operation result any carry then carry flag is set otherwise it is reset.

#### Arithmetic and Logic Unit (ALU):

- It is used to perform the arithmetic operations like addition, subtraction, multiplication, division, increment and decrement and logical operations like AND, OR and EX-OR.

- It receives the data from accumulator and registers.

- According to the result it set or reset the flags.

#### **Program Counter (PC):**

- This 16-bit register sequencing the execution of instructions.

- It is a memory pointer. Memory locations have 16-bit addresses, and that is why this is a 16-bit register.

- The function of the program counter is to point to the memory address of the next instruction to be executed.

- When an opcode is being fetched, the program counter is incremented by one to point to the next memory location.

## Stack Pointer (SP):

- The stack pointer is also a 16-bit register used as a memory pointer.

- It points to a memory location in R/W memory, called the stack.

- The beginning of the stack is defined by loading a 16-bit address in the stack pointer (register).

Temporary Register: It is used to hold the data during the arithmetic and logical operations.

**Instruction Register:** When an instruction is fetched from the memory, it is loaded in the instruction register.

**Instruction Decoder:** It gets the instruction from the instruction register and decodes the instruction. It identifies the instruction to be performed.

Serial I/O Control: It has two control signals named SID and SOD for serial data transmission.

## **Timing and Control unit:**

- It has three control signals ALE, RD (Active low) and WR (Active low) and three status signals IO/M(Active low), S0 and S1.

- ALE is used for provide control signal to synchronize the components of microprocessor and timing for instruction to perform the operation.

- RD (Active low) and WR (Active low) are used to indicate whether the operation is reading the data from memory or writing the data into memory respectively.

- IO/M(Active low) is used to indicate whether the operation is belongs to the memory or peripherals.

- If,

| IO/M(Active<br>Low) | <b>S1</b> | S2 | Data Bus Status(Output) |

|---------------------|-----------|----|-------------------------|

| 0                   | 0         | 0  | Halt                    |

| 0                   | 0         | 1  | Memory WRITE            |

| 0                   | 1         | 0  | Memory READ             |

| 1                   | 0         | 1  | IO WRITE                |

| 1                   | 1         | 0  | IO READ                 |

| 0                   | 1         | 1  | Opcode fetch            |

| 1                   | 1         | 1  | Interrupt ackno wiedge  |

#### **Interrupt Control Unit:**

• It receives hardware interrupt signals and sends an acknowledgement for receiving the interrupt signal.

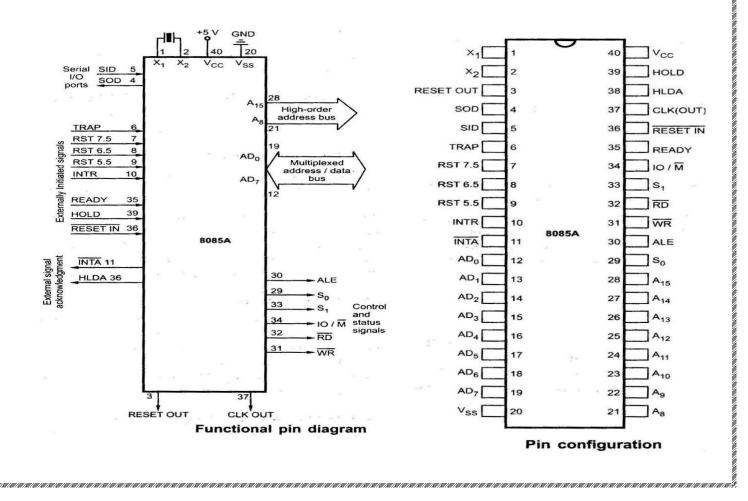

## Pin Diagram and Pin Description Of 8085

8085 is a 40 pin IC, DIP package. The signals from the pins can be grouped as follows

- 1. Power supply and clock signals

- 2. Address bus

- 3. Data bus

- 4. Control and status signals

- 5. Interrupts and externally initiated signals

- 6.

- 7. Serial I/O ports

## 1. Power supply and clock frequency signals

- Vcc + 5 volt power supply

- Vss Ground

- X1, X2: Crystal or R/C network or LC network connections to set the frequency of internal clock generator.

- The frequency is internally divided by two. Since the basic operating timing frequency is 3 MHz, a 6 MHz crystal is connected externally.

- CLK (output)-Clock Output is used as the system clock for peripheral and devices interfaced with the microprocessor.

## 2. Address Bus:

- A8 A15 (output; 3-state)

- It carries the most significant 8 bits of the memory address or the 8 bits of the I/O address;

## 3. Multiplexed Address / Data Bus:

- AD0 AD7 (input/output; 3-state)

- These multiplexed set of lines used to carry the lower order 8 bit address as well as data bus.

- During the opcode fetch operation, in the first clock cycle, the lines deliver the lower order address A0 A7.

- In the subsequent IO / memory, read / write clock cycle the lines are used as data bus.

- The CPU may read or write out data through these lines.

## 4. Control and Status signals:

- ALE (output) Address Latch Enable.

- This signal helps to capture the lower order address presented on the multiplexed address / data bus.

- RD (output 3-state, active low) Read memory or IO device.

- This indicates that the selected memory location or I/O device is to be read and that the data bus is ready for accepting data from the memory or I/O device.

- WR (output 3-state, active low) Write memory or IO device.

- This indicates that the data on the data bus is to be written into the selected memory location or I/O device.

- IO/M (output) Select memory or an IO device.

- This status signal indicates that the read / write operation relates to whether the memory or I/O device.

- It goes high to indicate an I/O operation.

- It goes low for memory operations.

## 5. Status Signals:

• It is used to know the type of current operation of the microprocessor.

| IO/M(Active<br>Low) | <b>S1</b> | S2 | Data Bus Status (Output) |

|---------------------|-----------|----|--------------------------|

| 0                   | 0         | 0  | Halt                     |

| 0                   | 0         | 1  | Memory WRITE             |

| 0                   | 1         | 0  | MemoryREAD               |

| 1                   | 0         | 1  | IO WRITE                 |

| 1                   | 1         | 0  | IOREAD                   |

| 0                   | 1         | 1  | Opcode fetch             |

| 1                   | 1         | 1  | Interrupt acknowledge    |

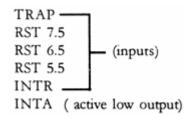

## 6. Interrupts and externally initiated operations:

- They are the signals initiated by an external device to request the microprocessor to do a particular task or work.

- There are five hardware interrupts called,

• On receipt of an interrupt, the microprocessor acknowledges the interrupt by the active low INTA (Interrupt Acknowledge) signal.

## Reset In (input, active low)

- This signal is used to reset the microprocessor.

- The program counter inside the microprocessor is set to zero.

- The buses are tri-stated.

## **Reset Out (Output)**

- It indicates CPU is being reset.

- Used to reset all the connected devices when the microprocessor is reset

## 7. Direct Memory Access (DMA):

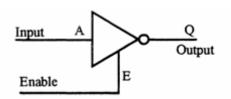

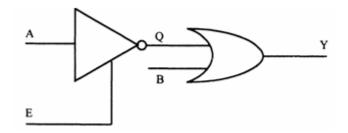

Tri state devices:

. . . . . . . . . . . . . . . . . . . .

- 3 output states are high & low states and additionally a high impedance state.

- When enable E is high the gate is enabled and the output Q can be 1 or 0 (if A is 0, Q is 1, otherwise Q is 0). However, when E is low the gate is disabled and the output Q enters into a high impedance state.

| Е       | Α | Q | State             |

|---------|---|---|-------------------|

| 1(high) | 0 | 1 | High              |

| 1       | 1 | 0 | Low               |

| 0(1ow)  | 0 | 0 | High<br>impedance |

| 0       | 1 | 0 | High<br>impedance |

- For both high and low states, the output Q draws a current from the input of the OR gate.

- When E is low, Q enters a high impedance state; high impedance means it is electrically isolated from the OR gate's input, though it is physically connected. Therefore, it does not draw any current from the OR gate's input.

- When 2 or more devices are connected to a common bus, to prevent the devices from interfering with each other, the tristate gates are used to disconnect all devices except the one that is communicating at a given instant.

- The CPU controls the data transfer operation between memory and I/O device. Direct Memory Access operation is used for large volume data transfer between memory and an I/O device directly.

- The CPU is disabled by tri-stating its buses and the transfer is effected directly by external control circuits.

- HOLD signal is generated by the DMA controller circuit. On receipt of this signal, the microprocessor acknowledges the request by sending out HLDA signal and leaves out the

control of the buses. After the HLDA signal the DMA controller starts the direct transfer of data.

## **READY** (input)

- Memory and I/O devices will have slower response compared to microprocessors.

- Before completing the present job such a slow peripheral may not be able to handle further data or control signal from CPU.

- The processor sets the READY signal after completing the present job to access the data.

- The microprocessor enters into WAIT state while the READY pin is disabled.

## 8. Single Bit Serial I/O ports:

- SID (input) Serial input data line

- SOD (output) Serial output data line

- These signals are used for serial communication

## **Overview or Features of 8086**

- It is a 16-bit Microprocessor (μp). It's ALU, internal registers works with 16bit binary word.

- 8086 has a 20 bit address bus can access up to  $2^{20}=1$  MB memory locations.

- 8086 has a 16bit data bus. It can read or write data to a memory/port either 16bits or 8 bit at a time.

- It can support up to 64K I/O ports.

- It provides 14, 16 -bit registers.

- Frequency range of 8086 is 6-10 MHz

- It has multiplexed address and data bus AD0- AD15 and A16 A19.

- It requires single phase clock with 33% duty cycle to provide internal timing.

- It can prefetch upto 6 instruction bytes from memory and queues them in order to speed up instruction execution.

- It requires +5V power supply.

- A 40 pin dual in line package.

- 8086 is designed to operate in two modes, Minimum mode and Maximum mode.

- The minimum mode is selected by applying logic 1 to the MN / MX# input pin. This is a single microprocessor configuration.

- The maximum mode is selected by applying logic 0 to the MN / MX# input pin. This is a multi micro processors configuration.

#### **Register Organization of 8086**

#### **General purpose registers**

The 8086 microprocessor has a total of fourteen registers that are accessible to the programmer. It is divided into four groups. They are:

- Four General purpose registers

- Four Index/Pointer registers

- Four Segment registers

- Two Other registers

General purpose registers:

## General Purpose Registers

|             |    | 12 0 |         |

|-------------|----|------|---------|

| Accumulator | AX |      | Multip  |

| Base        | BX |      | Pointer |

| Count       | CX |      | Count   |

| Data        | DX |      | Multip  |

Multiply, divide, I/O Pointer to base addresss (data) Count for loops, shifts Multiply, divide, I/O

Accumulator register consists of two 8-bit registers AL and AH, which can be combined together and used as a 16-bit register AX. AL in this case contains the low order byte of the word, and AH contains the high-order byte. Accumulator can be used for I/O operations and string manipulation.

Base register consists of two 8-bit registers BL and BH, which can be combined together and used as a 16-bit register BX. BL in this case contains the low-order byte of the word, and BH contains the high-order byte. BX register usually contains a data pointer used for based, based indexed or register indirect addressing. Count register consists of two 8-bit registers CL and CH, which can be combined together and used as a 16-bit register CX. When combined, CL register contains the low order byte of the word, and CH contains the high-order byte. Count register can be used in Loop, shift/rotate instructions and as a counter in string manipulation

Data register consists of two 8-bit registers DL and DH, which can be combined together and used as a 16-bit register DX. When combined, DL register contains the low order byte of the word, and DH contains the high-order byte. Data register can be used as a port number in I/O operations. In integer 32-bit multiply and divide instruction the DX register contains high-order word of the initial or resulting number.

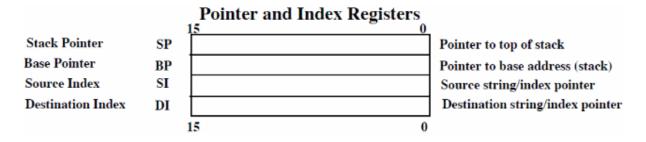

#### **Index or Pointer Registers**

These registers can also be called as Special Purpose registers.

Stack Pointer (SP) is a 16-bit register pointing to program stack, i.e. it is used to hold the address of the top of stack. The stack is maintained as a LIFO with its bottom at the start of the stack segment (specified by the SS segment register). Unlike the SP register, the BP can be used to specify the offset of other program segments.

Base Pointer (BP) is a 16-bit register pointing to data in stack segment. It is usually used by subroutines to locate variables that were passed on the stack by a calling program. BP register is usually used for based, based indexed or register indirect addressing.

Source Index (SI) is a 16-bit register. SI is used for indexed, based indexed and register indirect addressing, as well as a source data address in string manipulation instructions. Used in conjunction with the DS register to point to data locations in the data segment.

Destination Index (DI) is a 16-bit register. Used in conjunction with the ES register in string operations. DI is used for indexed, based indexed and register indirect addressing, as well as a destination data address in string manipulation instructions. In short, Destination Index and SI Source Index registers are used to hold address.

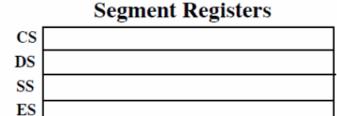

#### Segment Registers

Most of the registers contain data/instruction offsets within 64 KB memory segment. There are four different 64 KB segments for instructions, stack, data and extra data. To specify where in 1 MB of processor memory these 4 segments are located the processor uses four segment registers.

> Code Segment Data Segment Stack Segment Extra Segment

**Other registers of 8086**

Code segment (CS) is a 16-bit register containing address of 64 KB segment with processor instructions. The processor uses CS segment for all accesses to instructions referenced by instruction pointer (IP) register. CS register cannot be changed directly. The CS register is automatically updated during far jump, far call and far return instructions.

Stack segment (SS) is a 16-bit register containing address of 64KB segment with program stack. By default, the processor assumes that all data referenced by the stack pointer (SP) and base pointer (BP) registers is located in the stack segment. SS register can be changed directly using POP instruction.

Data segment (DS) is a 16-bit register containing address of 64KB segment with program data. By default, the processor assumes that all data referenced by general registers (AX, BX, CX, DX) and index register (SI, DI) is located in the data segment. DS register can be changed directly using POP and LDS instructions.

Extra segment (ES) used to hold the starting address of Extra segment. Extra segment is provided for programs that need to access a second data segment. Segment registers cannot be used in arithmetic operations.

# Other Registers Flags Flags Instruction Pointer IP

**Instruction Pointer (IP)** is a 16-bit register. This is a crucially important register which is used to control which instruction the CPU executes. The IP, or program counter, is used to store the memory location of the next instruction to be executed. The CPU checks the program counter to ascertain which instruction to carry out next. It then updates the program counter to point to the next instruction. Thus the program counter will always point to the next instruction to be executed.

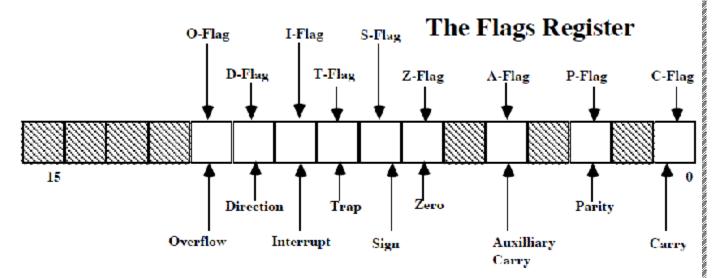

**Flag Register** contains a group of status bits called flags that indicate the status of the CPU or the result of arithmetic operations. There are two types of flags:

The status flags which reflect the result of executing an instruction. The programmer cannot set/reset these flags directly.

The control flags enable or disable certain CPU operations. The programmer can set/reset these bits to control the CPU's operation.

Nine individual bits of the status register are used as control flags (3 of them) and status flags (6ofthem).Theremaining7arenotused.A flag can only take on the values 0 and 1. We say a flag is set if it has the value 1.The statusflags are used to record specific characteristics of arithmetic and of logical instructions.

Control Flags: There are three control flags

1. The Direction Flag (D): Affects the direction of moving data blocks by such instructions as MOVS, CMPS and SCAS. The flag values are 0 = up and 1 = down and can be set/reset by the STD (set D) and CLD (clear D) instructions.

2. The Interrupt Flag (I): Dictates whether or not system interrupts can occur. Interrupts are actions initiated by hardware block such as input devices that will interrupt the normal execution

of programs. The flag values are 0 = disable interrupts or 1 = enable interrupts and can be manipulated by the CLI (clear I) and STI (set I) instructions.

3. The Trap Flag (T): Determines whether or not the CPU is halted after the execution of each instruction. When this flag is set (i.e. = 1), the programmer can single step through his program to debug any errors. When this flag = 0 this feature is off. This flag can be set by the INT 3 instruction.

Status Flags: There are six status flags

1. The Carry Flag (C): This flag is set when the result of an unsigned arithmetic operation is too large to fit in the destination register. This happens when there is an end carry in an addition operation or there an end borrows in a subtraction operation. A value of 1 = carry and 0 = no carry.

2. The Overflow Flag (O): This flag is set when the result of a signed arithmetic operation is too large to fit in the destination register (i.e. when an overflow occurs). Overflow can occur when adding two numbers with the same sign (i.e. both positive or both negative). A value of 1 = overflow and 0 = no overflow.

3. The Sign Flag (S): This flag is set when the result of an arithmetic or logic operation is negative. This flag is a copy of the MSB of the result (i.e. the sign bit). A value of 1 means negative and 0 = positive.

4. **The Zero Flag (Z):** This flag is set when the result of an arithmetic or logic operation is equal to zero. A value of 1 means the result is zero and a value of 0 means the result is not zero.

5. The Auxiliary Carry Flag (A): This flag is set when an operation causes a carry from bit 3 to bit 4 (or a borrow from bit 4 to bit 3) of an operand. A value of 1 = carry and 0 = no carry.

6. The Parity Flag (P): This flags reflects the number of 1s in the result of an operation. If the number of 1s is even its value = 1 and if the number of 1s is odd then its value = 0.

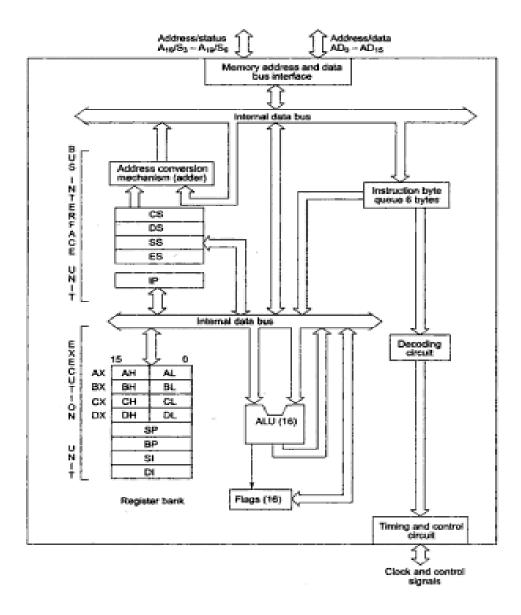

#### Architecture of 8086 or Functional Block diagram of 8086

- 8086 has two blocks Bus Interface Unit (BIU) and Execution Unit (EU).

- The BIU performs all bus operations such as instruction fetching, reading and writing operands for memory and calculating the addresses of the memory operands. The instruction bytes are transferred to the instruction queue.

• EU executes instructions from the instruction system byte queue.

• Both units operate asynchronously to give the 8086 an overlapping instruction fetch and execution mechanism which is called as Pipelining. This results in efficient use of the system bus and system performance.

- BIU contains Instruction queue, Segment registers, Instruction pointer, Address adder.

- EU contains Control circuitry, Instruction decoder, ALU, Pointer and Index register, Flag register.

### **Explanation of Architecture of 8086**

## **Bus Interface Unit:**

- It provides a full 16 bit bidirectional data bus and 20 bit address bus.

- The bus interface unit is responsible for performing all external bus operations.

- Specifically it has the following functions:

- Instruction fetch Instruction queuing, Operand fetch and storage, Address relocation and Bus control.

- The BIU uses a mechanism known as an instruction stream queue to implement pipeline architecture.

- This queue permits prefetch of up to six bytes of instruction code. When ever the queue of the BIU is not full, it has room for at least two more bytes and at the same time the EU is not requesting it to read or write operands from memory, the BIU is free to look ahead in the program by prefetching the next sequential instruction.

- These prefetching instructions are held in its FIFO queue. With its 16 bit data bus, the BIU fetches two instruction bytes in a single memory cycle.

- After a byte is loaded at the input end of the queue, it automatically shifts up through the FIFO to the empty location nearest the output.

- The EU accesses the queue from the output end. It reads one instruction byte after the other from the output of the queue. If the queue is full and the EU is not requesting access to operand in memory.

- These intervals of no bus activity, which may occur between bus cycles are known as Idle state.

- If the BIU is already in the process of fetching an instruction when the EU request it to read or write operands from memory or I/O, the BIU first completes the instruction fetch bus cycle before initiating the operand read / write cycle.

- The BIU also contains a dedicated adder which is used to generate the 20bit physical address that is output on the address bus. This address is formed by adding an appended 16 bit segment address and a 16 bit offset address.

- For example: The physical address of the next instruction to be fetched is formed by combining the current contents of the code segment CS register and the current contents of the instruction pointer IP register.

- The BIU is also responsible for generating bus control signals such as those for memory read or write and I/O read or write.

## **Execution Unit**

- The Execution unit is responsible for decoding and executing all instructions.

- The EU extracts instructions from the top of the queue in the BIU, decodes them, generates operands if necessary, passes them to the BIU and requests it to perform the read or write bus cycles to memory or I/O and perform the operation specified by the instruction on the operands.

- During the execution of the instruction, the EU tests the status and control flags and updates them based on the results of executing the instruction.

- If the queue is empty, the EU waits for the next instruction byte to be fetched and shifted to top of the queue.

- When the EU executes a branch or jump instruction, it transfers control to a location corresponding to another set of sequential instructions.

- Whenever this happens, the BIU automatically resets the queue and then begins to fetch instructions from this new location to refill the queue.

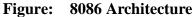

## **General Bus Operation**

- The 8086 has a combined address and data bus commonly referred as a time multiplexed address and data bus.

- The main reason behind multiplexing address and data over the same pins is the maximum utilization of processor pins and it facilitates the use of 40 pin standard DIP package.

- The bus can be demultiplexed using a few latches and transceivers, when ever required.

- Basically, all the processor bus cycles consist of at least four clock cycles. These are referred to as T1, T2, T3, and T4. The address is transmitted by the processor during T1. It is present on the bus only for one cycle.

- The negative edge of this ALE pulse is used to separate the address and the data or status information. In maximum mode, the status lines S0, S1 and S2 are used to indicate the type of operation.

- Status bits S3 to S7 are multiplexed with higher order address bits and the BHE signal. Address is valid during T1 while status bits S3 to S7 are valid during T2 through T4.

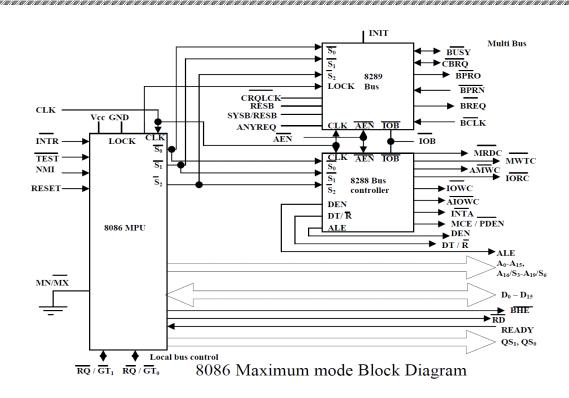

### Maximum mode

- In the maximum mode, the 8086 is operated by strapping the MN/MX pin to ground.

- In this mode, the processor derives the status signal S2, S1, S0. Another chip called bus controller derives the control signal using this status information.

- In the maximum mode, there may be more than one microprocessor in the system configuration.

## Minimum mode

- In a minimum mode 8086 system, the microprocessor 8086 is operated in minimum mode by strapping its MN/MX pin to logic 1.

- In this mode, all the control signals are given out by the microprocessor chip itself.

• There is a single microprocessor in the minimum mode system.

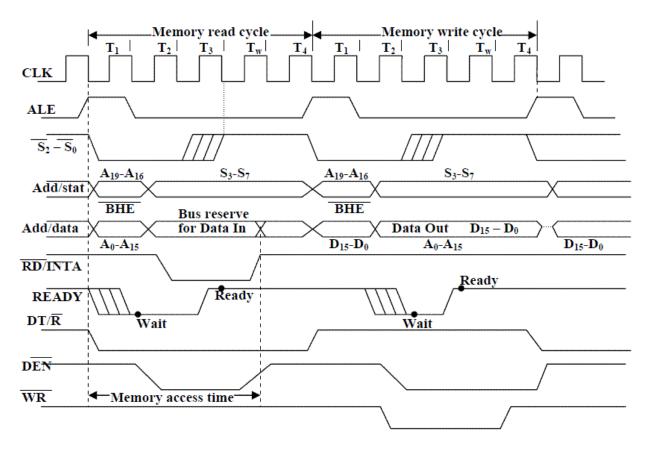

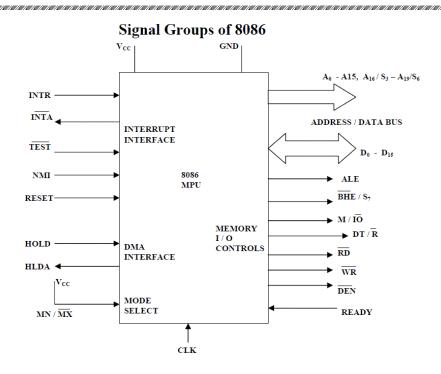

### Pin Diagram of 8086 and Pin description of 8086

Figure shows the Pin diagram of 8086. The description follows it.

## Pin Diagram of 8086

- The Microprocessor 8086 is a 16-bit CPU available in different clock rates and packaged in a 40 pin CERDIP or plastic package.

- The 8086 operates in single processor or multiprocessor configuration to achieve high performance. The pins serve a particular function in minimum mode (single processor mode) and other function in maximum mode configuration (multiprocessor mode).

- The 8086 signals can be categorized in three groups.

- The first are the signal having common functions in minimum as well as maximum mode.

- The second are the signals which have special functions for minimum mode

- The third are the signals having special functions for maximum mode.

- The following signal descriptions are common for both modes.

- AD15-AD0: These are the time multiplexed memory I/O address and data lines.

- Address remains on the lines during T1 state, while the data is available on the data bus during T2, T3, Tw and T4. These lines are active high and float to a tristate during interrupt acknowledge and local bus hold acknowledge cycles.

- A19/S6, A18/S5, A17/S4, and A16/S3: These are the time multiplexed address and status lines.

- During T1 these are the most significant address lines for memory operations.

- During I/O operations, these lines are low.

- During memory or I/O operations, status information is available on those lines for T2, T3, Tw and T4.

- The status of the interrupt enable flag bit is updated at the beginning of each clock cycle.

- The S4 and S3 combine indicate which segment registers is presently being used for memory accesses as in below fig.

- These lines float to tri-state off during the local bus hold acknowledge. The status line S6 is always low.

- The address bit is separated from the status bit using latches controlled by the ALE signal.

| <b>S</b> 4 | <b>S</b> 3 | Indication                         |

|------------|------------|------------------------------------|

| o          | o          | Alternate Data                     |

| o          | 1          | Stack                              |

| 1          | o          | Code or None                       |

| 1          | 1          | Data                               |

| o          | o          | Whole word                         |

| o          | 1          | Upper byte from or to even address |

| 1          | o          | Lower byte from or to even address |

- **BHE/S7:** The bus high enable is used to indicate the transfer of data over the higher order (D15-D8) data bus as shown in table. It goes low for the data transfer over D15-D8 and is used to derive chip selects of odd address memory bank or peripherals. BHE is low during T1 for read, write and interrupt acknowledge cycles, whenever a byte is to be transferred on higher byte of data bus. The status information is available during T2, T3 and T4. The signal is active low and tristated during hold. It is low during T1 for the first pulse of the interrupt acknowledge cycle.

- RD Read: This signal on low indicates the peripheral that the processor is performing memory or I/O read operation. RD is active low and shows the state for T2, T3, Tw of any read cycle. The signal remains tristated during the hold acknowledge.

- **READY:** This is the acknowledgement from the slow device or memory that they have completed the data transfer. The signal made available by the devices is synchronized by the 8284A clock generator to provide ready input to the 8086. the signal is active high.

- **INTR-Interrupt Request:** This is a triggered input. This is sampled during the last clock cycles of each instruction to determine the availability of the request. If any interrupt request is pending, the processor enters the interrupt acknowledge cycle. This can be internally masked by resulting the interrupt enable flag. This signal is active high and internally synchronized.

- **TEST:** This input is examined by a 'WAIT' instruction. If the TEST pin goes low, execution will continue, else the processor remains in an idle state. The input is synchronized internally during each clock cycle on leading edge of clock.

- **CLK- Clock Input:** The clock input provides the basic timing for processor operation and bus control activity. It's an asymmetric square wave with 33% duty cycle.

Figure shows the Pin functions of 8086.

The following pin functions are for the minimum mode operation of 8086.

- M/IO Memory/IO: This is a status line logically equivalent to S2 in maximum mode. When it is low, it indicates the CPU is having an I/O operation, and when it is high, it indicates that the CPU is having a memory operation. This line becomes active high in the previous T4 and remains active till final T4 of the current cycle. It is tristated during local bus "hold acknowledge ".

- **INTA Interrupt** Acknowledge: This signal is used as a read strobe for interrupt acknowledge cycles. i.e. when it goes low, the processor has accepted the interrupt.

- ALE Address Latch Enable: This output signal indicates the availability of the valid address on the address/data lines, and is connected to latch enable input of latches. This signal is active high and is never tristated.

- DT/R Data Transmit/Receive: This output is used to decide the direction of data flow through the transceivers (bidirectional buffers). When the processor sends out data, this signal is high and when the processor is receiving data, this signal is low.

- **DEN Data Enable:** This signal indicates the availability of valid data over the address/data lines. It is used to enable the transceivers (bidirectional buffers) to separate the data from the multiplexed address/data signal. It is active from the middle of T2 until the middle of T4. This is tristated during 'hold acknowledge' cycle.

- HOLD, HLDA- Acknowledge: When the HOLD line goes high; it indicates to the processor that another master is requesting the bus access. The processor, after receiving

the HOLD request, issues the hold acknowledge signal on HLDA pin, in the middle of the next clock cycle after completing the current bus cycle.

At the same time, the processor floats the local bus and control lines. When the processor detects the HOLD line low, it lowers the HLDA signal. HOLD is an asynchronous input, and is should be externally synchronized. If the DMA request is made while the CPU is performing a memory or I/O cycle, it will release the local bus during T4 provided :

1. The request occurs before T2 state of the current cycle. on or 2. The current cycle is not operating over the lower byte of a word. 3. The current cycle is not the first acknowledge of an interrupt acknowledge sequence. 4. A Lock instruction is not being executed.

#### The following pin functions are applicable for maximum mode operation of 8086.

- S2, S1, and S0 Status Lines: These are the status lines which reflect the type of operation, being carried out by the processor. These become activity during T4 of the previous cycle and active during T1 and T2 of the current bus cycles.

- LOCK: This output pin indicates that other system bus master will be prevented from gaining the system bus, while the LOCK signal is low. The LOCK signal is activated by the 'LOCK' prefix instruction and remains active until the completion of the next instruction. When the CPU is executing a critical instruction which requires the system bus, the LOCK prefix instruction ensures that other processors connected in the system will not gain the control of the bus.

The 8086, while executing the prefixed instruction, asserts the bus lock signal output, which may be connected to an external bus controller. By prefetching the instruction, there is a considerable speeding up in instruction execution in 8086. This is known as **instruction pipelining**.

| S2 | Sı | So | Indication            |

|----|----|----|-----------------------|

| 0  | 0  | 0  | Interrupt Acknowledge |

| 0  | 0  | 1  | Read I/O port         |

| 0  | 1  | 0  | Write I/O port        |

| 0  | 1  | 1  | Halt                  |

| 1  | 0  | 0  | Code Access           |

| 1  | 0  | 1  | Read Memory           |

| 1  | 1  | 0  | Write Memory          |

| 1  | 1  | 1  | Passive               |

|    |    |    | 1                     |

- At the starting the CS: IP is loaded with the required address from which the execution is to be started. Initially, the queue will be empty and the microprocessor starts a fetch operation to bring one byte (the first byte) of instruction code, if the CS: IP address is odd or two bytes at a time, if the CS: IP address is even.

- The first byte is a complete opcode in case of some instruction (one byte opcode instruction) and is a part of opcode, in case of some instructions (two byte opcode instructions), the remaining part of code lie in second byte.

- The second byte is then decoded in continuation with the first byte to decide the instruction length and the number of subsequent bytes to be treated as instruction data. The queue is updated after every byte is read from the queue but the fetch cycle is initiated by BIU only if at least two bytes of the queue are empty and the EU may be concurrently executing the fetched instructions.

- The next byte after the instruction is completed is again the first opcode byte of the next instruction. A similar procedure is repeated till the complete execution of the program. The fetch operation of the next instruction is overlapped with the execution of the current instruction. As in the architecture, there are two separate units, namely Execution unit and Bus interface unit.

- While the execution unit is busy in executing an instruction, after it is completely decoded, the bus interface unit may be fetching the bytes of the next instruction from memory, depending upon the queue status.

| QS1 | QSo | Indication                              |

|-----|-----|-----------------------------------------|

|     |     |                                         |

| 0   | o   | No Operation                            |

| 0   | 1   | First Byte of the opcode from the queue |

|     |     | rist byte of the optode from the queue  |

| 1   | 0   | Empty Queue                             |

| 1   | 1   | Subsequent Byte from the Queue          |

|     |     | Subsequence Syte nome the Quene         |

- RQ/GT0, RQ/GT1 Request/Grant: These pins are used by the other local bus master in maximum mode, to force the processor to release the local bus at the end of the processor current bus cycle.

- Each of the pin is bidirectional with RQ/GT0 having higher priority than RQ/GT1. RQ/GT pins have internal pull-up resistors and may be left unconnected. Request/Grant sequence is as follows:

- A pulse of one clock wide from another bus master requests the bus access to 8086.

- 2. During T4(current) or T1(next) clock cycle, a pulse one clock wide from 8086 to the requesting master, indicates that the 8086 has allowed the local bus to float and that it will enter the 'hold acknowledge' state at next cycle. The CPU bus interface unit is likely to be disconnected from the local bus of the system.

- 3. A one clock wide pulse from another master indicates to the 8086 that the hold request is about to end and the 8086 may regain control of the local bus at the next clock cycle. Thus each master to master exchange of the local bus is a sequence of 3 pulses. There must be at least one dead clock cycle after each bus exchange. The request and grant pulses are active low. For the bus request those are received while 8086 is performing memory or I/O cycle, the granting of the bus is governed by the rules as in case of HOLD and HLDA in minimum mode.

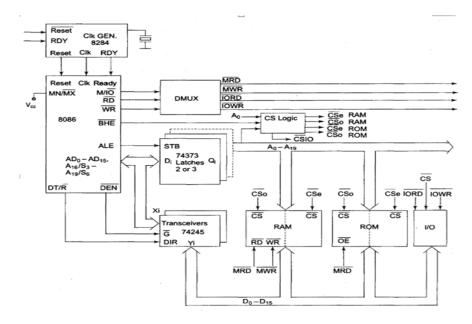

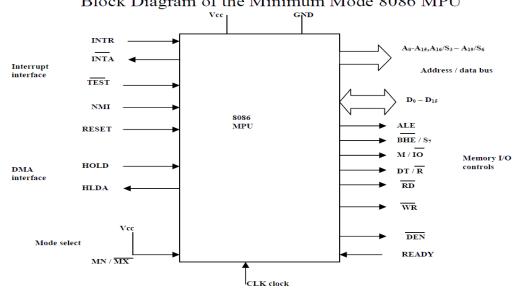

#### Minimum Mode 8086 System

#### Minimum mode 8086 system

- In a minimum mode 8086 system, the microprocessor 8086 is operated in minimum mode by strapping its MN/MX pin to logic 1.

- In this mode, all the control signals are given out by the microprocessor chip itself. There is a single microprocessor in the minimum mode system.

- The remaining components in the system are latches, transceivers, clock generator, memory and I/O devices. Some type of chip selection logic may be required for selecting memory or I/O devices, depending upon the address map of the system.

- Latches are generally buffered output D-type flip-flops like 74LS373 or 8282. They are used for separating the valid address from the multiplexed address/data signals and are controlled by the ALE signal generated by 8086.

- Transceivers are the bidirectional buffers and some times they are called as data amplifiers. They are required to separate the valid data from the time multiplexed address/data signals.

- They are controlled by two signals namely, DEN and DT/R.

- The DEN signal indicates the direction of data, i.e. from or to the processor. The system contains memory for the monitor and users program storage.

• Usually, EPROM is used for monitor storage, while RAM for users program storage. A system may contain I/O devices.

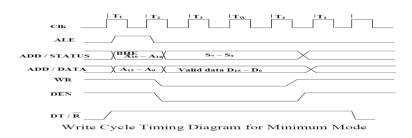

## Write Cycle Timing Diagram for Minimum Mode

- The working of the minimum mode configuration system can be better described in terms of the timing diagrams rather than qualitatively describing the operations.

- The opcode fetch and read cycles are similar. Hence the timing diagram can be categorized in two parts, the first is the timing diagram for read cycle and the second is the timing diagram for write cycle.

- The read cycle begins in T1 with the assertion of address latch enable (ALE) signal and also M / IO signal. During the negative going edge of this signal, the valid address is latched on the local bus.

- The BHE and A0 signals address low, high or both bytes. From T1 to T4, the M/IO signal indicates a memory or I/O operation.

- At T2, the address is removed from the local bus and is sent to the output. The bus is then tristated. The read (RD) control signal is also activated in T2.

- The read (RD) signal causes the address device to enable its data bus drivers. After RD goes low, the valid data is available on the data bus.

- The addressed device will drive the READY line high. When the processor returns the read signal to high level, the addressed device will again tristate its bus drivers.

- A write cycle also begins with the assertion of ALE and the emission of the address. The M/IO signal is again asserted to indicate a memory or I/O operation. In T2, after sending the address in T1, the processor sends the data to be written to the addressed location.

- The data remains on the bus until middle of T4 state. The WR becomes active at the beginning of T2 (unlike RD is somewhat delayed in T2 to provide time for floating).

- The BHE and A0 signals are used to select the proper byte or bytes of memory or I/O word to be read or write.

- The M/IO, RD and WR signals indicate the type of data transfer as specified in table below.

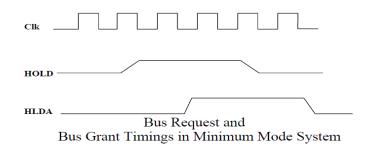

### **Bus Request and Bus Grant Timings in Minimum Mode System of 8086**

- Hold Response sequence: The HOLD pin is checked at leading edge of each clock pulse. If it is received active by the processor before T4 of the previous cycle or during T1 state of the current cycle, the CPU activates HLDA in the next clock cycle and for succeeding bus cycles, the bus will be given to another requesting master.

- The control of the bus is not regained by the processor until the requesting master does not drop the HOLD pin low. When the request is dropped by the requesting master, the HLDA is dropped by the processor at the trailing edge of the next clock.

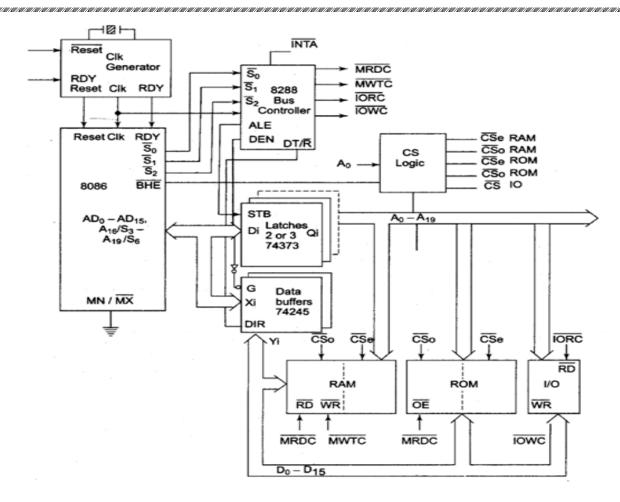

## Maximum Mode 8086 System

- In the maximum mode, the 8086 is operated by strapping the MN/MX pin to ground.

- In this mode, the processor derives the status signal S2, S1, S0. Another chip called bus controller derives the control signal using this status information.

- In the maximum mode, there may be more than one microprocessor in the system configuration.

- The components in the system are same as in the minimum mode system.

- The basic function of the bus controller chip IC8288 is to derive control signals like RD and WR (for memory and I/O devices), DEN, DT/R, ALE etc. using the information by the processor on the status lines.

- The bus controller chip has input lines S2, S1, S0 and CLK. These inputs to 8288 are driven by CPU.

- It derives the outputs ALE, DEN, DT/R, MRDC, MWTC, AMWC, IORC, IOWC and AIOWC. The AEN, IOB and CEN pins are especially useful for multiprocessor systems.

- AEN and IOB are generally grounded. CEN pin is usually tied to +5V. The significance of the MCE/PDEN output depends upon the status of the IOB pin.

- If IOB is grounded, it acts as master cascade enable to control cascade 8259A, else it acts as peripheral data enable used in the multiple bus configurations.

- INTA pin used to issue two interrupt acknowledge pulses to the interrupt controller or to an interrupting device.

- IORC, IOWC are I/O read command and I/O write command signals respectively.

- These signals enable an IO interface to read or write the data from or to the address port.

- The MRDC, MWTC are memory read command and memory write command signals respectively and may be used as memory read or write signals.

- All these command signals instructs the memory to accept or send data from or to the bus.

- For both of these write command signals, the advanced signals namely AIOWC and AMWTC are available.

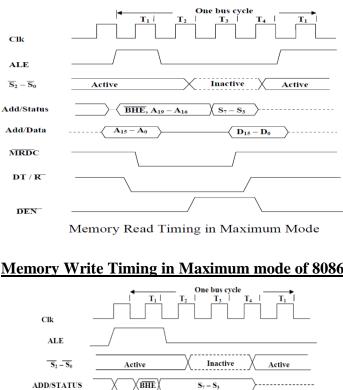

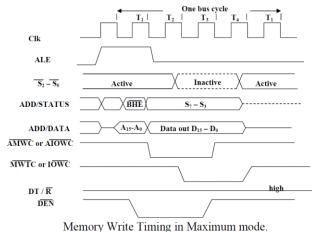

- Here the only difference between in timing diagram between minimum mode and maximum mode is the status signals used and the available control and advanced command signals.

- R0, S1, S2 are set at the beginning of bus cycle.8288 bus controller will output a pulse as on the ALE and apply a required signal to its DT / R pin during T1.

- In T2, 8288 will set DEN=1 thus enabling transceivers, and for an input it will activate MRDC or IORC. These signals are activated until T4. For an output, the AMWC or AIOWC is activated from T2 to T4 and MWTC or IOWC is activated from T3 to T4.

- The status bit S0 to S2 remains active until T3 and become passive during T3 and T4.

- If reader input is not activated before T3, wait state will be inserted between T3 and T4.

## Memory Read Timing Diagram in Maximum Mode of 8086

## Memory Write Timing in Maximum mode of 8086

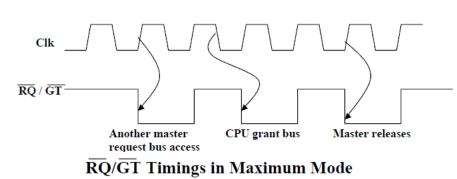

### **RQ/GT Timings in Maximum Mode**

- The request/grant response sequence contains a series of three pulses. The request/grant pins are checked at each rising pulse of clock input.

- When a request is detected and if the condition for HOLD request is satisfied, the processor issues a grant pulse over the RQ/GT pin immediately during T4 (current) or T1 (next) state.

- When the requesting master receives this pulse, it accepts the control of the bus, it sends a release pulse to the processor using RQ/GT pin.

## Minimum Mode Interface

- When the Minimum mode operation is selected, the 8086 provides all control signals needed to implement the memory and I/O interface.

- The minimum mode signal can be divided into the following basic groups :

- 1. Address/data bus

- 2. Status

- 3. Control

- 4. Interrupt and

- 5. DMA.

Each and every group is explained clearly.

#### Address/Data Bus:

- These lines serve two functions. As an address bus is 20 bits long and consists of signal lines A0 through A19. A19 represents the MSB and A0 LSB. A 20bit address gives the 8086 a 1Mbyte memory address space. More over it has an independent I/O address space which is 64K bytes in length.

- The 16 data bus lines D0 through D15 are actually multiplexed with address lines A0 through A15 respectively. By multiplexed we mean that the bus work as an address bus during first machine cycle and as a data bus during next machine cycles.

- D15 is the MSB and D0 LSB. When acting as a data bus, they carry read/write data for memory, input/output data for I/O devices, and interrupt type codes from an interrupt controller.

#### **Status signal:**

- The four most significant address lines A19 through A16 are also multiplexed but in this case with status signals S6 through S3.

- These status bits are output on the bus at the same time that data are transferred over the other bus lines.

Block Diagram of the Minimum Mode 8086 MPU

• Bit S4 and S3 together from a 2 bit binary code that identifies which of the 8086 internal segment registers is used to generate the physical address that was output on the address bus during the current bus cycle. Code S4S3 = 00 identifies a register known as extra segment register as the source of the segment address.

• Status line S5 reflects the status of another internal characteristic of the 8086. It is the logic level of the internal enable flag. The last status bit S6 is always at the logic 0 level.

| 84 | 83 | Segment Register  |

|----|----|-------------------|

| 0  | 0  | Extra             |

| 0  | 1  | Stack             |

| 1  | 0  | Code / none       |

| 1  | 1  | Data              |

|    |    | egment status cod |

#### **Control Signals:**

- The control signals are provided to support the 8086 memory I/O interfaces. They control functions such as when the bus is to carry a valid address in which direction data are to be transferred over the bus, when valid write data are on the bus and when to put read data on the system bus.

- ALE is a pulse to logic 1 that signals external circuitry when a valid address word is on the bus. This address must be latched in external circuitry on the 1-to-0 edge of the pulse at ALE.

- Another control signal that is produced during the bus cycle is BHE bank high enable.

Logic 0 on this used as a memory enable signal for the most significant byte half of the data bus D8 through D1. These lines also serve a second function, which is as the S7 status line.

- Using the M/IO and DT/R lines, the 8086 signals which type of bus cycle is in progress and in which direction data are to be transferred over the bus. The logic level of M/IO tells external circuitry whether a memory or I/O transfer is taking place over the bus. Logic 1 at this output signals a memory operation and logic 0 an I/O operation.

- The direction of data transfer over the bus is signaled by the logic level output at DT/R. When this line is logic 1 during the data transfer part of a bus cycle, the bus is in the transmit mode. Therefore, data are either written into memory or output to an I/O device. On the other hand, logic 0 at DT/R signals that the bus is in the receive mode. This corresponds to reading data from memory or input of data from an input port.

- The signals read RD and write WR indicates that a read bus cycle or a write bus cycle is in progress. The 8086 switches WR to logic 0 to signal external device that valid write or output data are on the bus.

- On the other hand, RD indicates that the 8086 is performing a read of data of the bus. During read operations, one other control signal is also supplied. This is DEN (data enable) and it signals external devices when they should put data on the bus. There is one other control signal that is involved with the memory and I/O interface. This is the READY signal.

- READY signal is used to insert wait states into the bus cycle such that it is extended by a

number of clock periods. This signal is provided by an external clock generator device and

can be supplied by the memory or I/O sub-system to signal the 8086 when they are ready

to permit the data transfer to be completed.

# **Interrupt signals:**

routine

- The key interrupt interface signals are interrupt request (INTR) and interrupt acknowledge (INTA).

- INTR is an input to the 8086 that can be used by an external device to signal that it need to be serviced.

- Logic 1 at INTR represents an active interrupt request. When an interrupt request has been recognized by the 8086, it indicates this fact to external circuit with pulse to logic 0 at the INTA output.

- The TEST input is also related to the external interrupt interface. Execution of a WAIT instruction causes the 8086 to check the logic level at the TEST input.

- If the logic 1 is found, the MPU suspend operation and goes into the idle state. The 8086 no longer executes instructions; instead it repeatedly checks the logic level of the TEST input waiting for its transition back to logic 0.

- As TEST switches to 0, execution resume with the next instruction in the program. This feature can be used to synchronize the operation of the 8086 to an event in external hardware.

- There are two more inputs in the interrupt interface: the nonmaskable interrupt NMI and the reset interrupt RESET.

- On the 0-to-1 transition of NMI control is passed to a nonmaskable interrupt service routine. The RESET input is used to provide a hardware reset for the 8086. Switching RESET to logic 0 initializes the internal register of the 8086 and initiates a reset service

# **DMA Interface signals:**

- The direct memory access DMA interface of the 8086 minimum mode consist of the HOLD and HLDA signals.

- When an external device wants to take control of the system bus, it signals to the 8086 by switching HOLD to the logic 1 level. At the completion of the current bus cycle, the 8086 enters the hold state. In the hold state, signal lines AD0 through AD15, A16/S3 through A19/S6, BHE, M/IO, DT/R, RD, WR, DEN and INTR are all in the high Z state.

- The 8086 signals external device that it is in this state by switching its HLDA output to logic 1 level.

# Maximum Mode Interface

- When the 8086 is set for the maximum-mode configuration, it provides signals for implementing a multiprocessor / coprocessor system environment.

- By multiprocessor environment we mean that one microprocessor exists in the system and that each processor is executing its own program.

- Usually in this type of system environment, there are some system resources that are common to all processors. They are called as global resources. There are also other resources that are assigned to specific processors. These are known as local or private resources.

- Coprocessor also means that there is a second processor in the system. In these two processors does not access the bus at the same time. One passes the control of the system bus to the other and then may suspend its operation.

- In the maximum-mode 8086 system, facilities are provided for implementing allocation of global resources and passing bus control to other microprocessor or coprocessor.

# 8288 Bus Controller – Bus Command and Control Signals:

• 8086 does not directly provide all the signals that are required to control the memory, I/O and interrupt interfaces.

- Specially the WR, M/IO, DT/R, DEN, ALE and INTA, signals are no longer produced by the 8086. Instead it outputs three status signals S0, S1, S2 prior to the initiation of each bus cycle. This 3- bit bus status code identifies which type of bus cycle is to follow.

- S2S1S0 are input to the external bus controller device, the bus controller generates the appropriately timed command and control signals.

- The 8288 produces one or two of these eight command signals for each bus cycles. For instance, when the 8086 outputs the code S2S1S0 equals 001; it indicates that an I/O read cycle is to be performed.

- In the code 111 is output by the 8086, it is signaling that no bus activity is to take place.

- The control outputs produced by the 8288 are DEN, DT/R and ALE. These 3 signals provide the same functions as those described for the minimum system mode.

| <u>82</u> | <u>81</u> | <u>so</u> | Indication            | 8288 Command |

|-----------|-----------|-----------|-----------------------|--------------|

|           |           |           |                       | INTA         |

| o         | o         | o         | Interrupt Acknowledge |              |

| o         | o         | 1         | Read I/O port         | IORC         |

| o         | 1         | o         | Write I/O port        | IOWC, AIOWC  |

| o         | 1         | 1         | Halt                  | None         |

| 1         | o         | o         | Instruction Fetch     | MRDC         |

| 1         | o         | 1         | Read Memory           | MRDC         |

| 1         | 1         | o         | Write Memory          |              |

| 1         | 1         | 1         | Passive               | MWTC, AMWC   |

|           |           |           |                       | None         |

- This set of bus commands and control signals is compatible with the Multibus and industry standard for interfacing microprocessor systems.

- The output of 8289 are bus arbitration signals:

Bus busy (BUSY), common bus request (CBRQ), bus priority out (BPRO), bus priority in (BPRN), bus request (BREQ) and bus clock (BCLK).

- They correspond to the bus exchange signals of the Multibus and are used to lock other processor off the system bus during the execution of an instruction by the 8086.

- In this way the processor can be assured of uninterrupted access to common system resources such as global memory.

- Queue Status Signals: Two new signals that are produced by the 8086 in the maximummode system are queue status outputs QS0 and QS1. Together they form a 2-bit queue status code, QS1QS0.

- Following table shows the four different queue status.

- Local Bus Control Signal Request / Grant Signals: In a maximum mode configuration, the minimum mode HOLD, HLDA interface is also changed

| QS1     | QSO | Queue Status                                                                                          |

|---------|-----|-------------------------------------------------------------------------------------------------------|

| 0 (low) | 0   | Queue Empty. The queue has been reinitialized as a result of the execution of a transfer instruction. |

| o       | 1   | First Byte. The byte taken from the queue was the first byte of the instruction.                      |

| 1       | 0   | Queue Empty. The queue has been reinitialized as a result of the execution of a transfer instruction. |

| 1       | 1   | Subsequent Byte. The byte taken from the queue<br>was a subsequent byte of the instruction.           |

Table - Queue status codes

• . These two are replaced by request/grant lines RQ/ GT0 and RQ/ GT1, respectively. They provide a prioritized bus access mechanism for accessing the local bus.

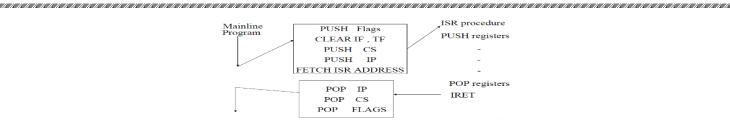

## **Interrupts**

**Definition:** The meaning of 'interrupts' is to break the sequence of operation. While the CPU is executing a program, on 'interrupt' breaks the normal sequence of execution of instructions, diverts its execution to some other program called Interrupt Service Routine (ISR). After executing ISR, the control is transferred back again to the main program. Interrupt processing is an alternative to polling.

**Need for Interrupt**: Interrupts are particularly useful when interfacing I/O devices that provide or require data at relatively low data transfer rate.

Types of Interrupts: There are two types of Interrupts in 8086. They are:

(i)Hardware Interrupts and

(ii)Software Interrupts

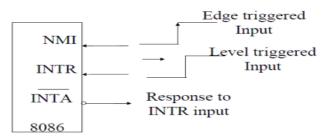

(i) **Hardware Interrupts** (External Interrupts). The Intel microprocessors support hardware interrupts through:

- Two pins that allow interrupt requests, INTR and NMI

- One pin that acknowledges, INTA, the interrupt requested on INTR.

## INTR and NMI

- INTR is a maskable hardware interrupt. The interrupt can be enabled/disabled using STI/CLI instructions or using more complicated method of updating the FLAGS register with the help of the POPF instruction.

- When an interrupt occurs, the processor stores FLAGS register into stack, disables further interrupts, fetches from the bus one byte representing interrupt type, and jumps to interrupt processing routine address of which is stored in location 4 \* <interrupt type>. Interrupt processing routine should return with the IRET instruction.

- NMI is a non-maskable interrupt. Interrupt is processed in the same way as the INTR interrupt. Interrupt type of the NMI is 2, i.e. the address of the NMI processing routine is stored in location 0008h. This interrupt has higher priority than the maskable interrupt.

- – Ex: NMI, INTR.

(ii) **Software Interrupts** (Internal Interrupts and Instructions) .Software interrupts can be caused by:

- INT instruction breakpoint interrupt. This is a type 3 interrupt.

- INT <interrupt number> instruction any one interrupt from available 256 interrupts.

- INTO instruction interrupt on overflow

- Single-step interrupt generated if the TF flag is set. This is a type 1 interrupt. When the CPU processes this interrupt it clears TF flag before calling the interrupt processing routine.

- Processor exceptions: Divide Error (Type 0), Unused Opcode (type 6) and Escape opcode (type 7).

- Software interrupt processing is the same as for the hardware interrupts.

- - Ex: INT n (Software Instructions)

- Control is provided through:

- IF and TF flag bits

- IRET and IRETD

# Performance of Software Interrupts

1. It decrements SP by 2 and pushes the flag register on the stack. 2. Disables INTR IF. clearing the by 3. It the TF in the flag Register. resets 5. It decrements SP 2 pushes CS by and on the stack. 6. It decrements SP by 2 and pushes IP on the stack. 6. Fetch the ISR address from the interrupt vector table.

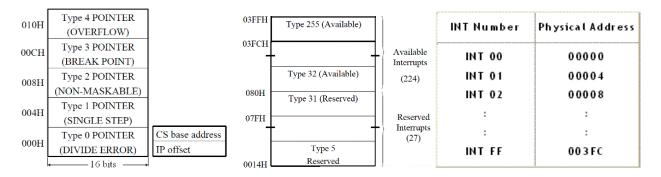

# **Interrupt Vector Table**

# Functions associated with INT00 to INT04

# INT 00 (divide error)

- INT00 is invoked by the microprocessor whenever there is an attempt to divide a number by zero.

- ISR is responsible for displaying the message "Divide Error" on the screen

# **INT 01**

- For single stepping the trap flag must be 1

- After execution of each instruction, 8086 automatically jumps to 00004H to fetch 4 bytes for CS: IP of the ISR.

• The job of ISR is to dump the registers on to the screen

# INT 02 (Non maskable Interrupt)

• When ever NMI pin of the 8086 is activated by a high signal (5v), the CPU Jumps to physical memory location 00008 to fetch CS:IP of the ISR associated with NMI.

# INT 03 (break point)

- A break point is used to examine the CPU and memory after the execution of a group of Instructions.

- It is one byte instruction whereas other instructions of the form "INT nn" are 2 byte instructions.

# INT 04 (Signed number overflow)

- There is an instruction associated with this INT 0 (interrupt on overflow).

- If INT 0 is placed after a signed number arithmetic as IMUL or ADD the CPU will activate INT 04 if 0F = 1.

- In case where 0F = 0, the INT 0 is not executed but is bypassed and acts as a NOP.

# Performance of Hardware Interrupts

- NMI : Non maskable interrupts TYPE 2 Interrupt

- INTR : Interrupt request Between 20H and FFH

# **Interrupt Priority Structure**

| Interrupt                 | Priority |

|---------------------------|----------|

| Divide Error, INT(n),INTO | Highest  |

| NMI                       |          |

| INTR                      |          |

| Single Step               | Lowest   |

# **INTRODUCTION TO MICRO CONTROLLERS**

#### **6.0 INTRODUCTION:**

We have noticed that Microprocessor is just not self-sufficient, and it requires other components like memory and input/output devices to form a minimum workable system configuration. To have all these components in a discrete form and to assemble them on a PCB is usually not an affordable solution for the following reasons:

- 1) The overall system cost of a microprocessor based system built around a CPU, memory and other peripherals is high as compared to a microcontroller based system.

- 2) A large sized PCB is required for assembling all these components, resulting in an enhanced cost of the system.

- 3) Design of such PCBs requires a lot of effort and time and thus the overall product design requires more time.

- 4) Due to the large size of the PCB and the discrete components used, physical size of the product is big and hence it is not handy.

- 5) As discrete components are used, the system is not reliable nor is it easy to trouble- shoot such a system.

Considering all these problems, Intel decided to integrate a microprocessor along with I/O ports and minimum memory into a single package. Another frequently used peripheral, a programmable timer, was also integrated to make this device a self-sufficient one. This device which contains a microprocessor and the above mentioned components has been named a microcontroller. A microcontroller is a microprocessor with integrated peripherals. Design with microcontrollers has the following advantages:

- 1. As the peripherals are integrated into a single chip, the overall system cost is very low.

- 2. The size of the product is small as compared to the microprocessor based systems thus very handy.

- 3. The system design requires very little efforts and is easy to troubleshoot and maintain.

- 4. As the peripherals are integrated with a microprocessor, the system is more reliable.

- 5. Though a microcontroller may have on-chip RAM, ROM and I/O ports, additional RAM, ROM and I/O ports may be interfaced externally, if required.

- 6. The microcontrollers with on-chip ROM provide a software security feature which is not available with microprocessor based systems using ROM/EPROM.

However, in case of a larger system design, which requires more number of I/O ports and more memory capacity, the system designer may interface external I/O ports and memory with

the system. In such cases, the microcontroller based systems are not so attractive as they are in case of the small dedicated systems. Figure 17.1 shows a typical microcontroller internal block diagram.

As a microcontroller contains most of the components required to form a microprocessor system, it is sometimes called a single chip microcomputer, since it also has the ability to easily implement simple control functions.

## 6.1 OVERVIEW OF 8051 MICRO CONTROLLER

Let us look at Intel's 8-bit microcontroller family, popularly known as MCS-51 family. The earlier versions of Intel's microcontrollers do not have on-chip EPROM. 8031 was one such microcontroller from Intel, followed by the 8051 family. 8751 was the first microcontroller version with on-chip EPROM, followed by a number of 8751 versions with slight modifications. Recently, an electrically programmable and erasable version of 8051, named as 8951, has been introduced. Table shows the comparison between different versions of 8051. All these members of the 8051 family have identical instruction set and similar architecture with slight variations as shown in Table.

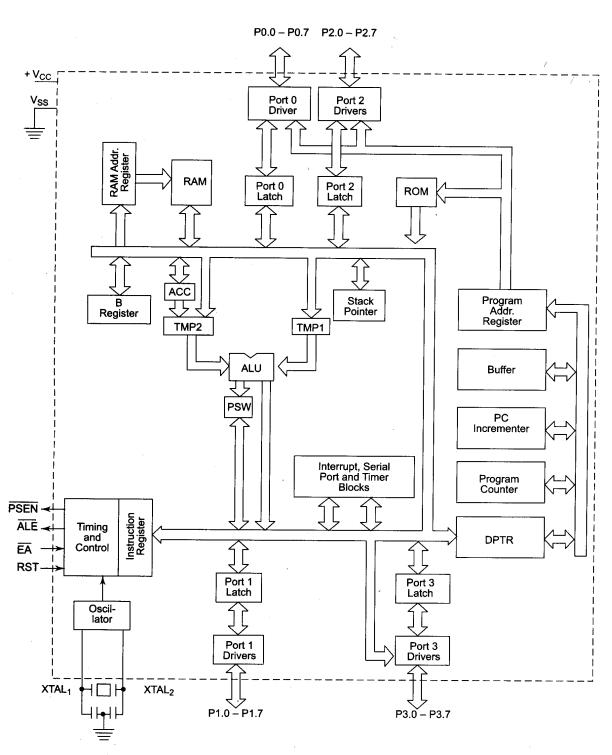

#### 6.2 ARCHITECTURE OF 8051

The internal architecture of 8051 is presented in Fig.

The functional description of each block is presented briefly below.

Accumulator (ACC): The accumulator register (ACC or A) acts as an operand register, in case of some instructions. This may either be implicit or specified in the instruction.

**B Register:** This register is used to store one of the operands for multiply and divide instructions. In other instructions, it may just be used as a scratch pad.

Program Status Word (PSW): This set of flags contains the status information.

**Stack Pointer (SP):** This 8-bit wide register is incremented before the data is stored onto the stack using push or call instructions. This register contains 8-bit stack top address. The stack may be defined anywhere in the on-chip 128-byte RAM. After reset, the SP register is initialised to 07. After each write to stack operation, the 8-bit contents of the operand are stored onto the stack, after incrementing the SP register by one. Thus if SP contains 07 H, the forthcoming PUSH operation will store the data at address 08H in the internal RAM. The SP content will be incremented to 08.

Fig. 17.2 8051 Block Diagram (Intel Corp.)

**Data Pointer (DTPR):** This 16-bit register contains a higher byte (DPH) and the lower byte (DPL) of a 16-bit external data RAM address. It is accessed as a 16-bit register or two 8-bit registers as specified above.

**Port 0 to 3 Latches and Drivers:** These four latches and driver pairs are allotted to each of the four on-chip I/O ports. Using the allotted addresses, the user can communicate with these ports. These are identified as P0, PI, P2 and P3.

**Serial Data Buffer:** The serial data buffer internally contains two independent registers. One of them is a transmit buffer which is necessarily a parallel-in serial-out register. The other is called receive buffer which is a serial-in parallel-out register. The serial data buffer is identified as SBUF.

**Timer Registers:** These two 16-bit registers can be accessed as their lower and upper bytes. For example, TL0 represents the lower byte of the timing register 0, while TH0 represents higher bytes of the timing register 0. Similarly, TL1 and TH1 represent lower and higher bytes of timing register 1.

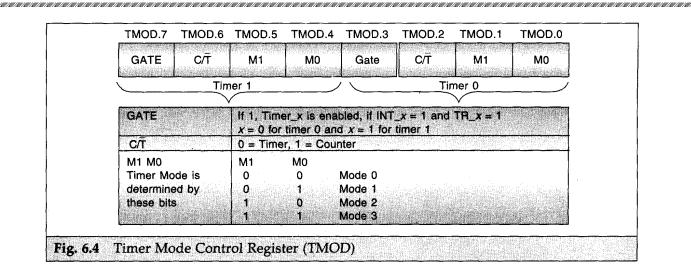

**Control Registers:** The special function registers IP, IE, TMOD, TCON, SCON and PCON contain control and status information for interrupts, timers/counters and serial port.

**Timing and Control Unit:** This unit derives all the necessary timing and control signals required for the internal operation of the circuit. It also derives control signals required for controlling the external system bus.

**Oscillator:** This circuit generates the basic timing clock signal for the operation of the circuit using crystal oscillator.

**Instruction Register:** This register decodes the opcode of an instruction to be executed and gives information to the timing and control unit to generate necessary signals for the execution of the instruction.

**EPROM and Program Address Register:** These blocks provide an on-chip EPROM/PROM and a mechanism to internally address it. Note that EPROM is not available in all 8051 versions.

**RAM and RAM Address Register:** These blocks provide internal 128 bytes of RAM and a mechanism to address it internally.

**ALU:** The arithmetic and logic unit performs 8-bit arithmetic and logical operations over the operands held by the temporary registers TMP1 and TMP2. Users cannot access these temporary registers.

**SFR Register Bank:** This is a set of special function registers, which can be addressed using their respective addresses which lie in the range 80H to FFH.

Finally, the interrupt, serial port and timer units control and perform their specific functions under the control of the timing and control unit.

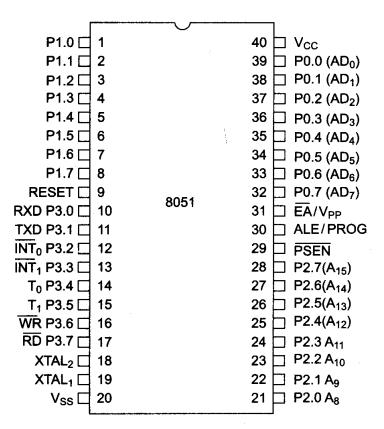

# 6.3 PIN DESCRIPTIONS OF 8051

8051 is available in a 40-pin plastic and ceramic DIP packages. The pin diagram of 8051 is shown in Fig. 17.3 followed by description of each pin.

Fig. 17.3 805 | Pin Configuration (Intel Corp.)

$V_{cc}$  This is a +5 V supply voltage pin

$V_{ss}$  This is a return pin for the supply.

**RESET** The reset input pin resets the 8051, only when it goes high for two or more machine cycles. For a proper reinitialization after reset, the clock must be running.

**ALE/PROG** The address latch enable output pulse indicates that the valid address bits are available on their respective pins. This ALE signal is valid only for external memory accesses. Normally, the ALE pulses are emitted at a rate of one-sixth of the oscillator frequency. This pin acts as program pulse input during on-chip EPROM programming. ALE may be used for external timing or clocking purpose. One ALE pulse is skipped during each access to external data memory.

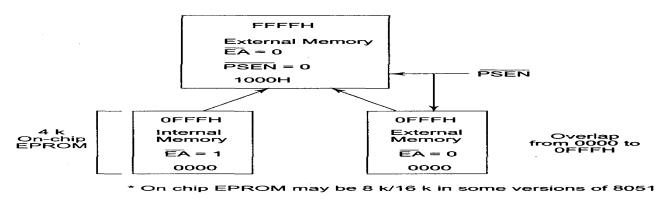

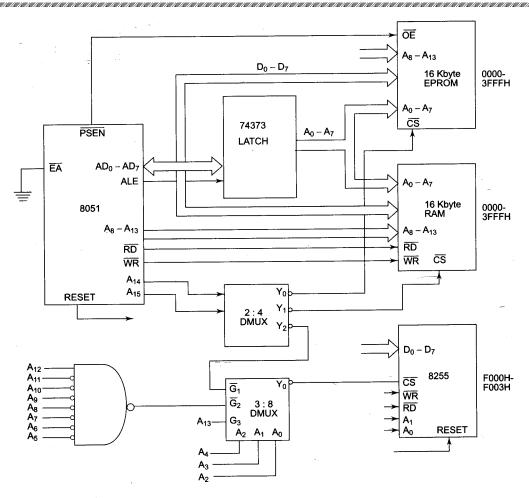

$\overline{\mathbf{EA}} / \mathbf{V_{pp}}$  External access enable pin, if tied low, indicates that the 8051 can address external program memory. In other words, the 8051 can execute a program in external memory, only if  $\overline{\mathbf{EA}}$  is tied low.

For execution of programs in internal memory, the  $\overline{EA}$  must be tied high. This pin also receives 21 volts for programming of the on-chip EPROM.

**PSEN** Program store enable is an active-low output signal that acts as a strobe to read the external program memory. This goes low during external program memory accesses.

**Port 0 (P0.0-P0.7)** Port 0 is an 8-bit bidirectional bit addressable I/O port. This has been allotted an address in the SFR address range. Port 0 acts as multiplexed address/data lines during external memory access, i.e. when  $\overline{EA}$  is low and ALE emits a valid signal. In case of controllers with on-chip EPROM, Port 0 receives code bytes during programming of the internal EPROM.

**Port 1 (P1.0-P1.7)** Port 1 acts as an 8-bit bidirectional bit addressable port. This has been allotted an address in the SFR address range.

**Port 2 (P2.0-P2.7)** Port 2 acts as 8-bit bidirectional bit addressable I/O port. It has been allotted an address in the SFR address range of 8051. During external memory accesses, port 2 emits higher eight bits of adress  $(A_8-A_{15})$  which are valid, if ALE goes high and EA is low. P2 also receives higher order address bits during programming of the on-chip EPROM.

**Port 3 (P3.0-P3.7)** Port 3 is an 8-bit bidirectional bit addressable I/O port which has been allotted an address in the SFR address range of 8051. The port 3 pins also serve the alternative functions as listed in the Table 17.2.

$\mathbf{XTAL_1}$  and  $\mathbf{XTAL_2}$  There is an inbuilt oscillator which derives the necessary clock frequency for the operation of the controller.  $\mathbf{XTAL_1}$  is the input of amplifier and  $\mathbf{XTAL_2}$  is the output of the amplifier. A crystal is to be connected externally between these two pins to complete the feedback path to start oscillations. The controller can be operated on an external clock. In this case the external clock is fed to the controller at pin  $\mathbf{XTAL_2}$  and  $\mathbf{XTAL_1}$  pin should be grounded. Commercially available versions of 8051 run on 12 MHz to 16 MHz frequency.

#### 6.4 REGISTER SET OF 8051

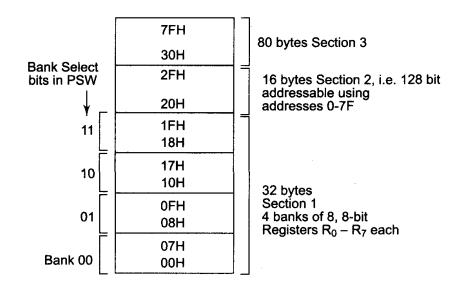

8051 has two 8-bit registers, registers A and B, which can be used to store operands, as allowed by the instruction set. Internal temporary registers of 8051 are not user accessible. Including these A and B registers, 8051 has a family of special purpose registers known as, Special Function Registers (SFRs). There are, in total, 21-bit addressable, 8-bit registers. ACC (A), B, PSW, PO, PI, P2, P3, IP, IE, TCON and SCON are all 8-bit, bit-addressable registers. The remaining registers, namely, SP, DPH, DPL, TMOD, TH0, TL0, TH1, TL1, SBUF and PCON registers are to be addressed as bytes, i.e. they are not bit-addressable. The registers DPH and DPL are the higher and lower bytes of a 16-bit register DPTR, i.e. data pointer, which is used for accessing external data memory. Starting 32-bytes of on-chip RAM may be used as general purpose registers. They have been allotted addresses in the range from 0000H to 001FH. These 32, 8-bit registers are divided into four groups of 8 registers each, called register banks.

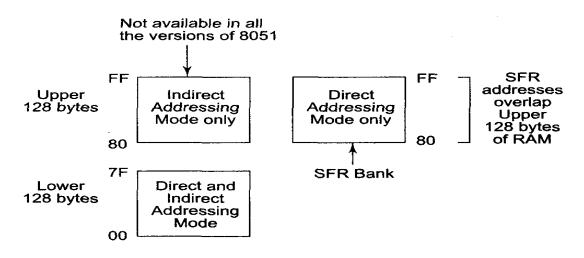

At a time only one of these four groups, i.e. banks can be accessed. The register bank to be accessed can be selected using the RS1 and RS0 bits of an internal register called program status word.