#### COMPUTER ORGANIZATION AND OPERATING SYSTEMS BY

Ms. A Swapna Assistant Professor

Ms. A Lakshmi Assistant Professor

Mr.Ch.Srikanth Assistant Professor

Mr.P.Sunil Kumar Assistant Professor

# UNIT-1

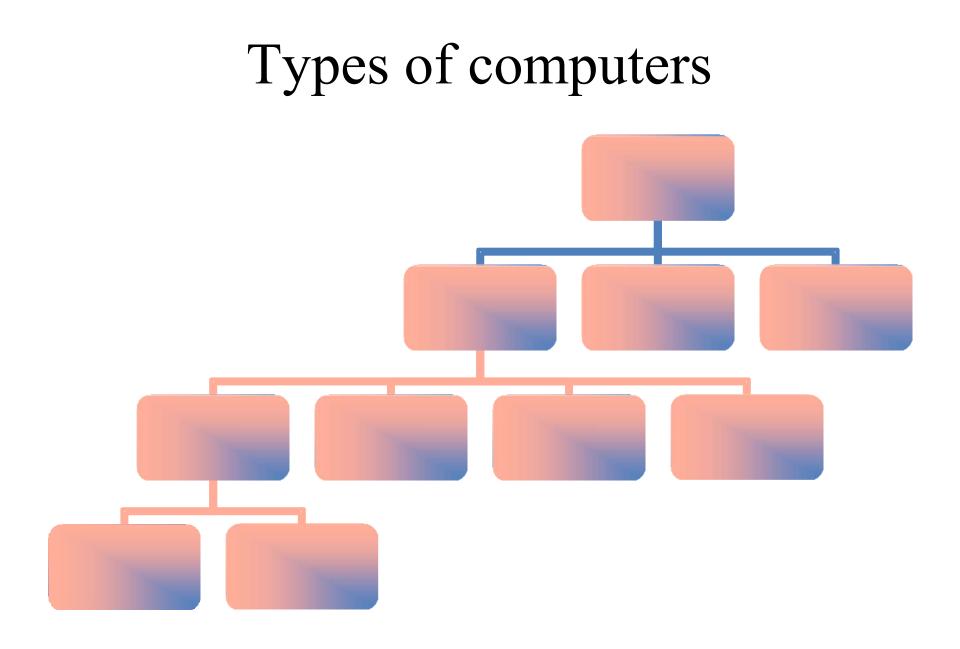

- **Computer Types**

- Functional Units

- Basic Operational Concept

- Bus Structures

- \*Software

- \* Performance

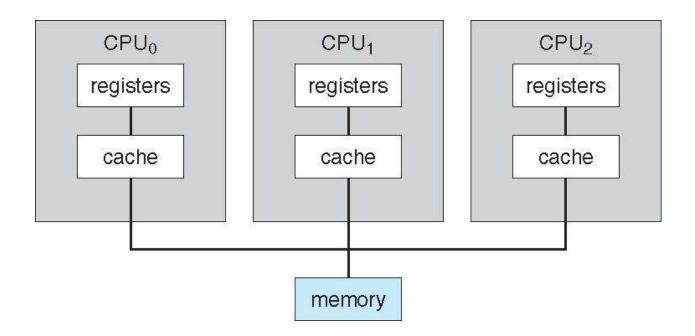

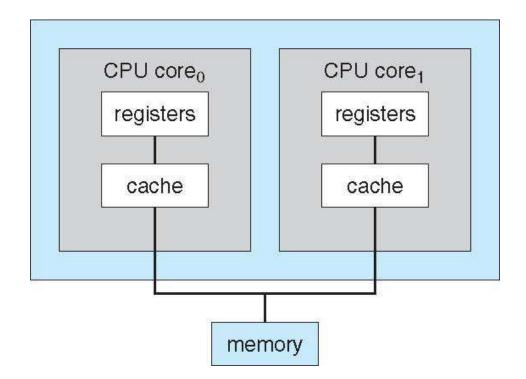

- Multi processors and Multi Computers

- Data Representation

# Analog computer

Analog computer measures and answer the questions by the method of "HOW MUCH". The input data is not a number infect a physical quantity like tem, pressure, speed, velocity.

- Signals are continuous of (0 to 10 V)

- Accuracy 1% Approximately

- High speed

- Output is continuous

- Time is wasted in transmission time

# **Digital Computers**

Digital computer counts and answer the questions by the method of "HOW Many". The input data is represented by a number. These are used for the logical and arithmetic operations.

- Signals are two level of (0 V or 5 V)

- Accuracy unlimited

- low speed sequential as well as parallel processing

- Output is continuous but obtain when computation is completed.

# Micro Computer

Micro computer are the smallest computer system. There size range from calculator to desktop size. Its CPU is microprocessor. It also known as Grand child Computer.

• Application : - personal computer, Multi user system, offices.

# Mini Computer

- These are also small general purpose system. They are generally more powerful and most useful as compared to micro computer. Mini computer are also known as mid range computer or Child computer.

- Application :- Departmental systems, Network Servers, work group system.

## Main Frame Computer

Mainframe computers are those computers that offer faster processing and grater storage area. The word "main frame" comes from the metal frames. It is also known as Father computer.

• Application – Host computer, Central data base server.

# Super Computer

- Super computer are those computer which are designed for scientific job like whether forecasting and artificial intelligence etc. They are fastest and expensive. A super computer contains a number of CPU which operate in parallel to make it faster. It also known as grand father computer.

- Application whether forecasting, weapons research and development.

# **Classification of Digital computer**

- Desktop

- Workstation

- Notebook

- Tablet PC

- Handheld computer

- Smart Phone

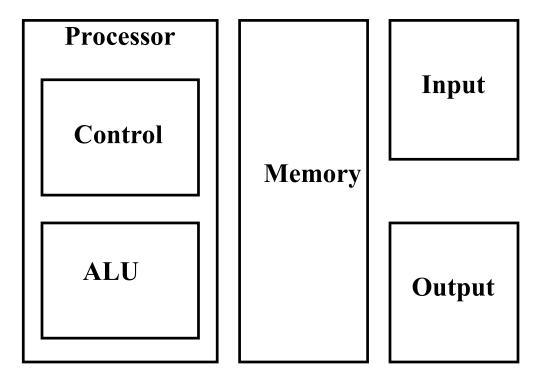

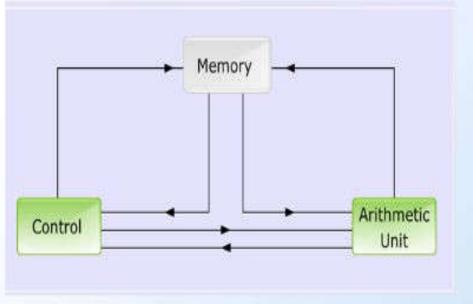

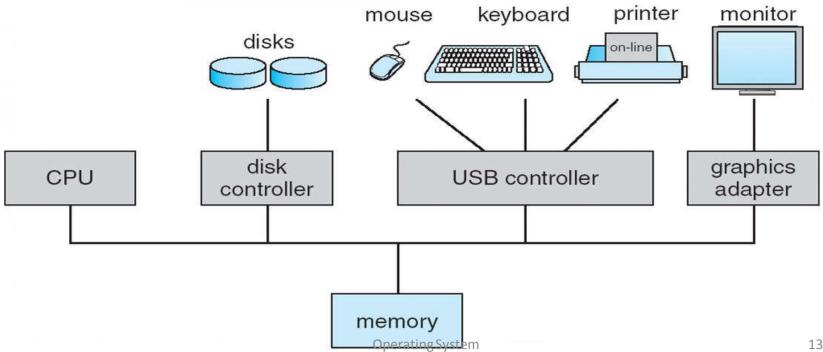

## FUNCTIONAL UNITS OF COMPUTER

- Input Unit

- Output Unit

- Central processing Unit (ALU and Control Units)

- Memory

- Bus Structure

# The Big Picture

Since 1946 all computers have had 5 components!!!

## Function

- <u>ALL</u> computer functions are:

- Data <u>PROCESSING</u>

- Data <u>STORAGE</u>

- Data <u>MOVEMENT</u>

- <u>CONTROL</u>

Data = Information

**Coordinates How Information is Used**

• <u>NOTHING ELSE!</u>

### **INPUT UNIT:**

•Converts the external world data to a binary format, which can be understood by CPU.

•Eg: Keyboard, Mouse, Joystick etc

### **OUTPUT UNIT:**

•Converts the binary format data to a format that a common man can understand.

•Eg: Monitor, Printer, LCD, LED etc

## **Central Processing Unit**

- The "brain" of the machine

- Responsible for carrying out computational task

- Contains ALU, CU, Registers

- ALU Performs Arithmetic and logical operations

- CU Provides control signals in accordance with some timings which in turn controls the execution process

- •Register Stores data and result and speeds up the operation

•Control unit works with a reference signal called processor clock

•Processor divides the operations into basic steps

•Each basic step is executed in one clock cycle

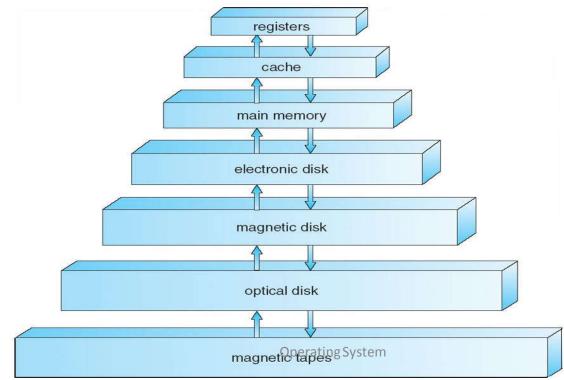

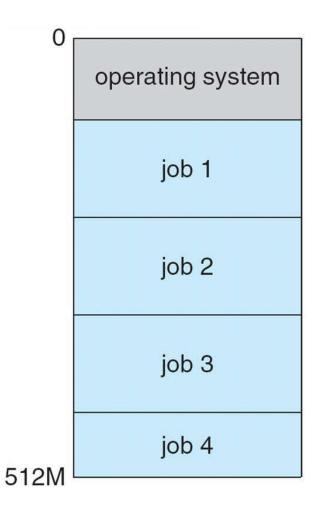

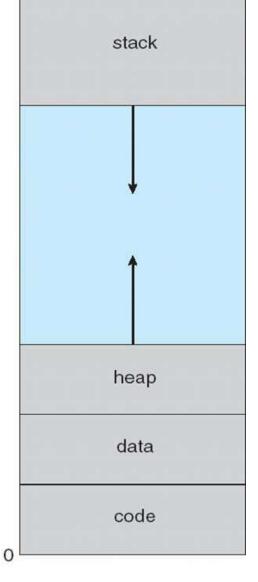

### MEMORY

- Stores data, results, programs

- Two class of storage Primary (ii) Secondary

- Two types are RAM or R/W memory and ROM read only memory

- ROM is used to store data and program which is not going to change.

- Secondary storage is used for bulk storage or mass storage

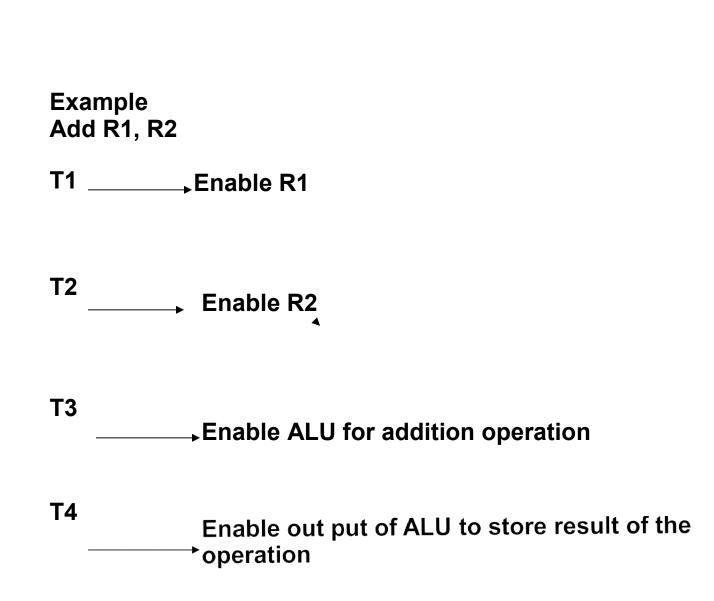

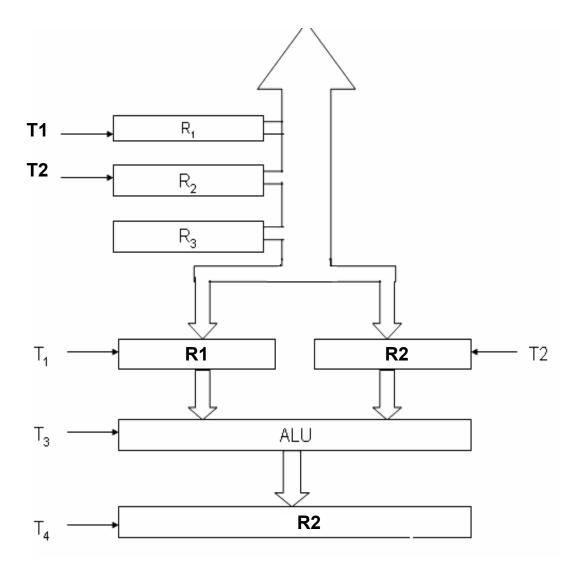

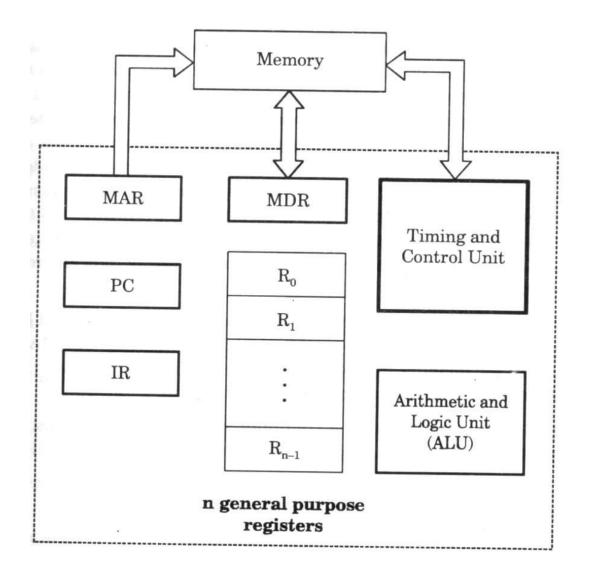

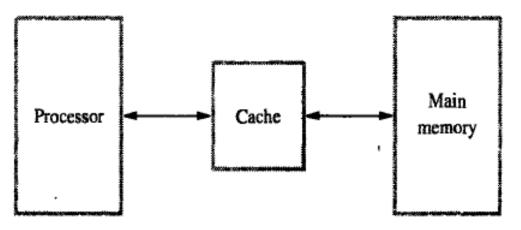

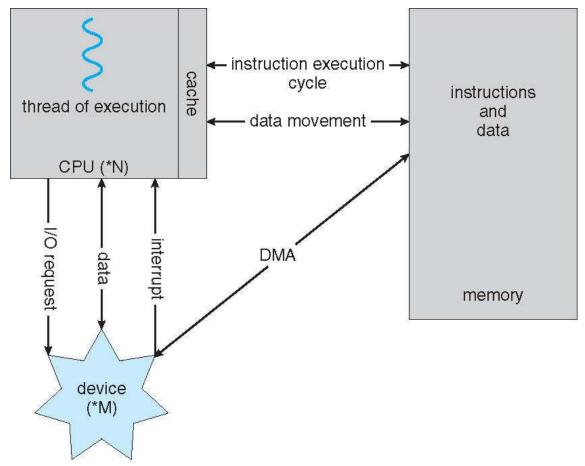

## **Basic Operational Concepts**

### **Basic Function of Computer**

- To Execute a given task as per the appropriate program

- Program consists of list of instructions stored in memory

Interconnection between Processor and Memory

### Registers

Registers are fast stand-alone storage locations that hold data temporarily. Multiple registers are needed to facilitate the operation of the CPU. Some of these registers are

□ Two registers-MAR (Memory Address Register) and MDR (Memory Data Register) : To handle the data transfer between main memory and processor. MAR-Holds addresses, MDR-Holds data

□ Instruction register (IR) : Hold the Instructions that is currently being executed

Program counter: Points to the next instructions that is to be fetched from memory

- (PC) the contents of PC transferred to MAR)

- (MAR) (Address bus) Select a particular memory location

- Issues RD control signals

- Reads instruction present in memory and loaded into MDR

- Will be placed in IR (Contents transferred from MDR to IR)

•Instruction present in IR will be decoded by which processor understand what operation it has to perform.

•Increments the contents of PC by 1, so that it points to the next instruction address.

•If data required for operation is available in register, it performs the operation.

•If data is present in memory following sequence is performed

•Address of the data \_\_\_\_\_ MAR

•MAR\_\_\_\_Address bus \_\_\_\_\_select memory location where is issued RD signal

•Reads data via data bus

MDR

•From MDR data can be directly routed to ALU or it can be placed in register and then operation can be performed

•Results of the operation can be directed towards output device, memory or register

•Normal execution preempted (interrupt)

### DATA REPRESENTATION

- •Data Types

- •Complements

- •Fixed Point Representations

- •Floating Point Representations

- **•Other Binary Codes**

- •Error Detection Codes

### DATA REPRESENTATION

Information that a Computer is dealing with

\* Data

- Numeric Data

- Numbers(Integer, real)

- Non-numeric Data Letters, Symbols

- \* Relationship between data elements

- Data Structures

Linear Lists, Trees, Rings, etc

\* Program(Instruction)

### NUMERIC DATA REPRESENTATION

Data

Numeric data - numbers(integer, real) Non-numeric data - symbols, letters

Number System

Nonpositional number system

- Roman number system

Positional number system

- Each digit position has a value called a *weight* associated with it

- Decimal, Octal, Hexadecimal, Binary

Base (or radix) R number

- Uses R distinct symbols for each digit

- Example

$$A_R = a_{n-1} a_{n-2} \dots a_1 a_0 . a_{-1} \dots a_{-m}$$

$$-V(A_R) = \sum_{i=-m}^{n-1} a_i R^i$$

Radix point(.) separates the integer portion and the fractional portion

R = 10 Decimal number system, R = 2 Binary R = 8 Octal,

R = 16 Hexadecimal

#### WHY POSITIONAL NUMBER SYSTEM IN DIGITAL COMPUTERS ?

Major Consideration is the COST and TIME

- Cost of building *hardware* Arithmetic and Logic Unit, CPU, Communications

- Time to processing

Arithmetic - Addition of Numbers - Table for Addition

\* Non-positional Number System

- Table for addition is infinite

- --> Impossible to build, very expensive even if it can be built

- \* Positional Number System

- Table for Addition is finite

- --> Physically realizable, but cost wise the smaller the table size, the less expensive --> Binary is favorable to Decimal

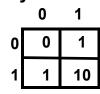

#### **Binary Addition Table**

| Dee | cin<br>0 | -  | <b>/</b><br>2 | -  | -  |    |    | Та<br>7 | -  | le<br>9 |

|-----|----------|----|---------------|----|----|----|----|---------|----|---------|

| 0   | 0        | 1  | 2             | 3  | 4  | 5  | 6  | 7       | 8  | 9       |

| 1   | 1        | 2  | 3             | 4  | 5  | 6  | 7  | 8       | 9  | 10      |

| 2   | 2        | 3  | 4             | 5  | 6  | 7  | 8  | 9       | 10 | 11      |

| 3   | 3        | 4  | 5             | 6  | 7  | 8  | 9  | 10      | 11 | 12      |

| 4   | 4        | 5  | 6             | 7  | 8  | 9  | 10 | 11      | 12 | 13      |

| 5   | 5        | 6  | 7             | 8  | 9  | 10 | 11 | 12      | 13 | 14      |

| 6   | 6        | 7  | 8             | 9  | 10 | 11 | 12 | 13      | 14 | 15      |

| 7   | 7        | 8  | 9             | 10 | 11 | 12 | 13 | 14      | 15 | 16      |

| 8   | 8        | 9  | 10            | 11 | 12 | 13 | 14 | 15      | 16 | 17      |

| 9   | 9        | 10 | 11            | 12 | 13 | 14 | 15 | 16      | 17 | 18      |

|     |          |    |               |    |    |    |    |         |    |         |

#### Data Types

#### REPRESENTATION OF NUMBERS - POSITIONAL NUMBERS

| Decimal | Binary | Octal | Hexadecimal |

|---------|--------|-------|-------------|

| 00      | 0000   | 00    | 0           |

| 01      | 0001   | 01    | 1           |

| 02      | 0010   | 02    | 2           |

| 03      | 0011   | 03    | 3           |

| 04      | 0100   | 04    | 4           |

| 05      | 0101   | 05    | 5           |

| 06      | 0110   | 06    | 6           |

| 07      | 0111   | 07    | 7           |

| 08      | 1000   | 10    | 8           |

| 09      | 1001   | 11    | 9           |

| 10      | 1010   | 12    | A           |

| 11      | 1011   | 13    | В           |

| 12      | 1100   | 14    | С           |

| 13      | 1101   | 15    | D           |

| 14      | 1110   | 16    | E           |

| 15      | 1111   | 17    | F           |

Binary, octal, and hexadecimal conversion

#### CONVERSION OF BASES

Base R to Decimal Conversion

$$A = a_{n-1} a_{n-2} a_{n-3} \dots a_0 \dots a_{-1} \dots a_{-m}$$

$$V(A) = \sum a_k R^k$$

$$(736.4)_8 = 7 \times 8^2 + 3 \times 8^1 + 6 \times 8^0 + 4 \times 8^{-1}$$

$$= 7 \times 64 + 3 \times 8 + 6 \times 1 + 4/8 = (478.5)_{10}$$

$$(110110)_2 = \dots = (54)_{10}$$

$$(110.111)_2 = \dots = (6.785)_{10}$$

$$(F3)_{16} = \dots = (243)_{10}$$

$$(0.325)_6 = \dots = (0.578703703 \dots)_{10}$$

Decimal to Base R number

- Separate the number into its *integer* and *fraction* parts and convert each part separately.

- Convert *integer part* into the base R number

- $\rightarrow$  successive divisions by R and accumulation of the remainders.

- Convert fraction part into the base R number

- $\rightarrow$  successive multiplications by R and accumulation of integer

digits

#### EXAMPLE

| Convert 41.6875 <sub>10</sub> to base 2. | Fraction = 0.6875            |

|------------------------------------------|------------------------------|

| Integer = 41                             | 0.6875<br>x 2                |

| 41                                       | 1.3750                       |

| 20 1                                     | <u>x 2</u>                   |

| 10 0                                     | 0.7500                       |

| 5 0                                      | <u>x 2</u>                   |

| 2 1                                      | 1.5000                       |

| 1 0                                      | <u>x 2</u>                   |

| 0 1                                      | 1.0000                       |

| $(41)_{10} = (101001)_2$                 | $(0.6875)_{10} = (0.1011)_2$ |

$(41.6875)_{10} = (101001.1011)_2$

#### **Exercise**

Convert  $(63)_{10}$  to base 5: $(223)_5$ Convert  $(1863)_{10}$  to base 8: $(3507)_8$ Convert  $(0.63671875)_{10}$  to hexadecimal:  $(0.A3)_{16}$

### COMPLEMENT OF NUMBERS

Two types of complements for base R number system:

- R's complement and (R-1)'s complement

The (R-1)'s Complement

Subtract each digit of a number from (R-1)

Example

- 9's complement of  $835_{10}$  is  $164_{10}$

- 1's complement of 1010<sub>2</sub> is 0101<sub>2</sub>(bit by bit complement operation)

#### The R's Complement

Add 1 to the low-order digit of its (R-1)'s complement

#### Example

- 10's complement of  $835_{10}$  is  $164_{10} + 1 = 165_{10}$

- 2's complement of  $1010_2$  is  $0101_2 + 1 = 0110_2$

#### FIXED POINT NUMBERS

Numbers: Fixed Point Numbers and Floating Point Numbers

**Binary Fixed-Point Representation**

$X = x_n x_{n-1} x_{n-2} \dots x_1 x_0 \dots x_{-1} x_{-2} \dots x_{-m}$

Sign Bit( $x_n$ ): 0 for positive - 1 for negative

Remaining Bits $(x_{n-1}x_{n-2} \dots x_1x_0, x_{-1}x_{-2} \dots x_{-m})$

#### SIGNED NUMBERS

Need to be able to represent both *positive* and *negative* numbers

- Following 3 representations

Signed magnitude representation Signed 1's complement representation Signed 2's complement representation

Example: Represent +9 and -9 in 7 bit-binary number

Only one way to represent +9 ==> 0 001001 Three different ways to represent -9: In signed-magnitude: 1 001001 In signed-1's complement: 1 110110 In signed-2's complement: 1 110111

In general, in computers, fixed point numbers are represented either integer part only or fractional part only.

#### CHARACTERISTICS OF 3 DIFFERENT REPRESENTATIONS

Complement

Signed magnitude: Complement *only* the sign bit Signed 1's complement: Complement *all* the bits including sign bit Signed 2's complement: Take the 2's complement of the number, *including* its sign bit.

Maximum and Minimum Representable Numbers and Representation of Zero

$X = x_n x_{n-1} \dots x_0 \dots x_{-1} \dots x_{-m}$

Signed Magnitude

| Max: 2 <sup>n</sup> - 2 <sup>-m</sup>     | 011 11.11 1 |

|-------------------------------------------|-------------|

| Min: -(2 <sup>n</sup> - 2 <sup>-m</sup> ) | 111 11.11 1 |

| Zero: +0                                  | 000 00.00 0 |

| -0                                        | 100 00.00 0 |

Signed 1's Complement

| Max: 2 <sup>n</sup> - 2 <sup>-m</sup>     | 011 11.11 1 |

|-------------------------------------------|-------------|

| Min: -(2 <sup>n</sup> - 2 <sup>-m</sup> ) | 100 00.00 0 |

| Zero: +0                                  | 000 00.00 0 |

| -0                                        | 111 11.11 1 |

#### Signed 2's Complement

| Max: 2 | <b>2<sup>n</sup> - 2</b> -m | 011 11.11 1 |

|--------|-----------------------------|-------------|

| Min:   | - <b>2</b> <sup>n</sup>     | 100 00.00 0 |

| Zero:  | 0                           | 000 00.00 0 |

### 2's COMPLEMENT REPRE"ENTATION WEIGHT"

- "igned 2's complement representation follows a "weight" scheme similar to that of unsigned numbers

- Sign bit has negative weight

- Other bits have regular weights

$$X = x_n x_{n-1} \dots x_0$$

$$Y(X) = -x_n \times 2^n + \sum_{i=0}^{n-1} x_i \times 2^i$$

# ARITHMETIC ADDITION: SIGNED MAGNITUDE

[1] Compare their signs

[2] If two signs are the *same*,

ADD the two magnitudes - Look out for an overflow

[3] If not the same, compare the relative magnitudes of the numbers and then SUBTRACT the smaller from the larger --> need a subtractor to add

[4] Determine the sign of the result

| 6 + 9                                                                                         | -6 + 9            |

|-----------------------------------------------------------------------------------------------|-------------------|

| 6 0110                                                                                        | 9 1001            |

| <u>+) 9 1001</u>                                                                              | - <u>) 6 0110</u> |

| 15 1111 -> 01111                                                                              | 3 0011 -> 00011   |

| 6 + (- 9)                                                                                     | -6 + (-9)         |

| 9 1001                                                                                        | 6 0110            |

| - <u>) 6 0110</u>                                                                             | +) 9 1001         |

| - 3 0011 -> 10011<br>Overflow 9 + 9 or (-9) + (-9)<br>9 1001<br>+) 9 1001<br>overflow (1)0010 | -15 1111 -> 11111 |

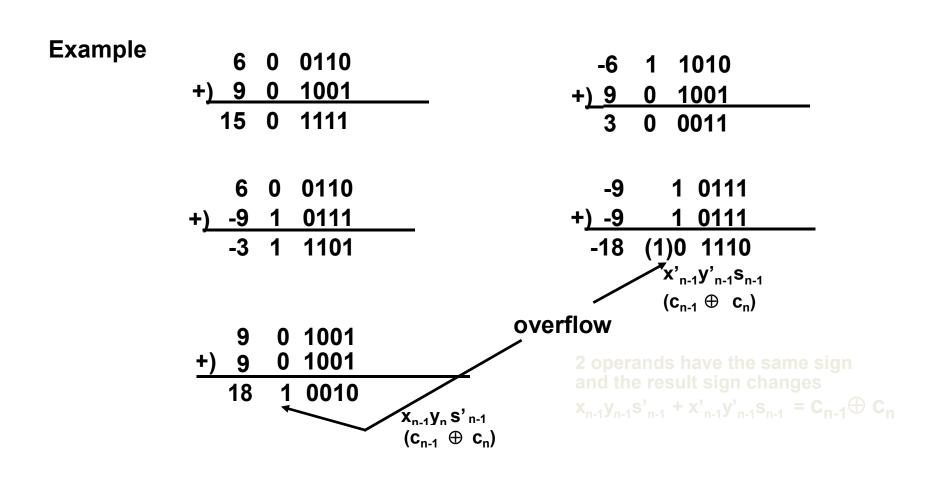

#### ARITHMETIC ADDITION: "IGNED 2's COMPLEMENT

Add the two numbers, including their sign bit, and discard any carry out of leftmost (sign) bit - Look out for an *overflow*

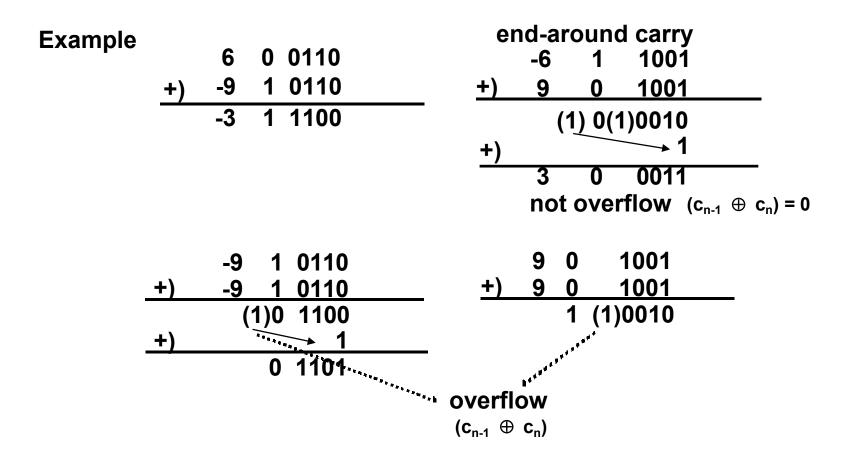

#### ARITHMETIC ADDITION: "IGNED 1's COMPLEMENT

Add the two numbers, including their sign bits.

- If there is a carry out of the most significant (sign) bit, the result is incremented by 1 and the carry is discarded.

### COMPARISON OF REPRESENTATIONS

- \* Easiness of negative conversion

- S + M > 1's Complement > 2's Complement

- \* Hardware

- S+M: Needs an adder and a subtractor for Addition

- 1's and 2's Complement: Need only an adder

- \* Speed of Arithmetic

2's Complement > 1's Complement(end-around C)

\* Recognition of Zero

2's Complement is fast

# ARITHMETIC SUBTRACTION

**Arithmetic Subtraction in 2's complement**

Take the complement of the subtrahend (including the sign bit) and add it to the minuend including the sign bits.

$$(\pm A) - (-B) = (\pm A) + B$$

$(\pm A) - B = (\pm A) + (-B)$

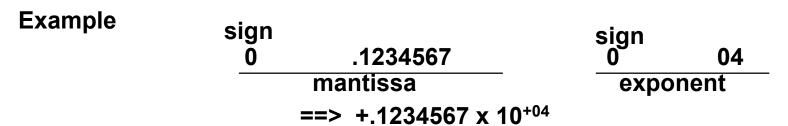

# FLOATING POINT NUMBER REPRESENTATION

\* The location of the fractional point is not fixed to a certain location

\* The range of the representable numbers is wide

F = EM

- Mantissa

Signed fixed point number, either an integer or a fractional number

#### - Exponent

Designates the position of the radix point

**Decimal Value**

$$V(F) = V(M) * R^{V(E)}$$

M:

E: Exponent

Mantissa

**R:** Radix

# FLOATING POINT NUMBERS

#### Note:

In Floating Point Number representation, only Mantissa(M) and Exponent(E) are explicitly represented. The Radix(R) and the position of the Radix Point are implied.

#### Example

A binary number +1001.11 in 16-bit floating point number representation (6-bit exponent and 10-bit fractional mantissa)

|    | 0 0 00100 100111000    |  |

|----|------------------------|--|

| or | Sign Exponent Mantissa |  |

| UI | 0 0 00101 010011100    |  |

#### CHARACTERISTICS OF FLOATING POINT NUMBER REPRESENTATIONS

#### Normal Form

- There are many different floating point number representations of the same number

- $\rightarrow$  Need for a unified representation in a given computer

- the most significant position of the mantissa contains a non-zero digit

**Representation of Zero**

- Zero Mantissa = 0

- Real Zero

- Mantissa = 0

- Exponent

- smallest representable number which is represented as 00 ... 0

- ← Easily identified by the hardware

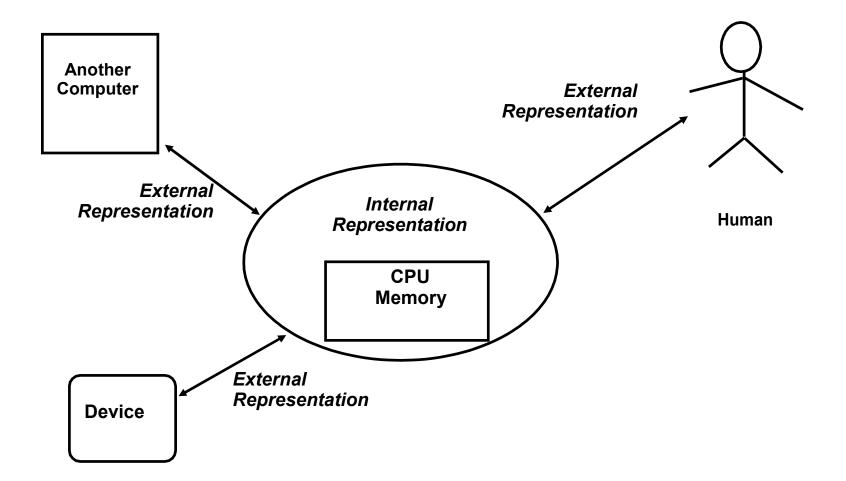

#### INTERNAL REPRESENTATION AND EXTERNAL REPRESENTATION

#### EXTERNAL REPRESENTATION

#### Numbers

Most of numbers stored in the computer are eventually changed by some kinds of calculations

- → *Internal Representation* for calculation efficiency

- → Final results need to be converted to as *External Representation* for presentability

Alphabets, Symbols, and some Numbers

Elements of these information do not change in the course of processing

- $\rightarrow$  No needs for Internal Representation since they are not used for calculations

- $\rightarrow$  External Representation for processing and presentability

Example

Decimal Number: 4-bit Binary Code BCD(Binary Coded Decimal)

| Decimal | BCD Code |

|---------|----------|

| 0       | 0000     |

| 1       | 0001     |

| 2       | 0010     |

| 3       | 0011     |

| 4       | 0100     |

| 5       | 0101     |

| 6       | 0110     |

| 7       | 0111     |

| 8       | 1000     |

| 9       | 1001     |

# OTHER DECIMAL CODES

| Decimal | BCD(8421) | 2421 | 84-2-1 | Excess-3 |                                                                                   |

|---------|-----------|------|--------|----------|-----------------------------------------------------------------------------------|

| 0       | 0000      | 0000 | 0000   | 0011     |                                                                                   |

| 1       | 0001      | 0001 | 0111   | 0100     |                                                                                   |

| 2       | 0010      | 0010 | 0110   | 0101     |                                                                                   |

| 3       | 0011      | 0011 | 0101   | 0110     |                                                                                   |

| 4       | 0100      | 0100 | 0100   | 0111     |                                                                                   |

| 5       | 0101      | 1011 | 1011   | 1000     |                                                                                   |

| 6       | 0110      | 1100 | 1010   | 1001     |                                                                                   |

| 7       | 0111      | 1101 | 1001   | 1010     | Note: 8,4,2,-2,1,-1 in this table is the wei                                      |

| 8       | 1000      | 1110 | 1000   | 1011     | associated with each bit position.                                                |

| 9       | 1001      | 1111 | 1111   | 1100     | d <sub>3</sub> d <sub>2</sub> d <sub>1</sub> d <sub>0</sub> : symbol in the codes |

BCD:

$$d_3 \times 8 + d_2 \times 4 + d_1 \times 2 + d_0 \times 1$$

$\Rightarrow 8421 \text{ code.}$

2421:  $d_3 \times 2 + d_2 \times 4 + d_1 \times 2 + d_0 \times 1$

84-2-1:  $d_3 \times 8 + d_2 \times 4 + d_1 \times (-2) + d_0 \times (-1)$

Excess-3: BCD + 3

BCD: It is difficult to obtain the 9's complement.

However, it is easily obtained with the other codes listed above.

$\rightarrow$  Self-complementing codes

### GRAY CODE

\* Characterized by having their representations of the binary integers differ in only one digit between consecutive integers

\* Useful in some applications

| ]                | Decimal |                       | Gray                  | y          |    | Bi             | nar            | y              |                |

|------------------|---------|-----------------------|-----------------------|------------|----|----------------|----------------|----------------|----------------|

|                  | number  | <b>g</b> <sub>3</sub> | <b>g</b> <sub>2</sub> | <b>g</b> 1 | g₀ | b <sub>3</sub> | $\mathbf{b}_2$ | $\mathbf{b}_1$ | b <sub>0</sub> |

|                  | 0       | 0                     | 0                     | 0          | 0  | 0              | 0              | 0              | 0              |

|                  | 1       | 0                     | 0                     | 0          | 1  | 0              | 0              | 0              | 1              |

|                  | 2       | 0                     | 0                     | 1          | 1  | 0              | 0              | 1              | 0              |

|                  | 3       | 0                     | 0                     | 1          | 0  | 0              | 0              | 1              | 1              |

|                  | 4       | 0                     | 1                     | 1          | 0  | 0              | 1              | 0              | 0              |

| 4-bit Gray codes | 5       | 0                     | 1                     | 1          | 1  | 0              | 1              | 0              | 1              |

|                  | 6       | 0                     | 1                     | 0          | 1  | 0              | 1              | 1              | 0              |

|                  | 7       | 0                     | 1                     | 0          | 0  | 0              | 1              | 1              | 1              |

|                  | 8       | 1                     | 1                     | 0          | 0  | 1              | 0              | 0              | 0              |

|                  | 9       | 1                     | 1                     | 0          | 1  | 1              | 0              | 0              | 1              |

|                  | 10      | 1                     | 1                     | 1          | 1  | 1              | 0              | 1              | 0              |

|                  | 11      | 1                     | 1                     | 1          | 0  | 1              | 0              | 1              | 1              |

|                  | 12      | 1                     | 0                     | 1          | 0  | 1              | 1              | 0              | 0              |

|                  | 13      | 1                     | 0                     | 1          | 1  | 1              | 1              | 0              | 1              |

|                  | 14      | 1                     | 0                     | 0          | 1  | 1              | 1              | 1              | 0              |

|                  | 15      | 1                     | 0                     | 0          | 0  | 1              | 1              | 1              | 1              |

#### **GRAY CODE - ANALYSIS**

#### Letting $g_ng_{n-1} \dots g_1 g_0$ be the (n+1)-bit Gray code for the binary number $b_n b_{n-1} \dots b_1 b_0$ $\mathbf{g}_i = \mathbf{b}_i \oplus \mathbf{b}_{i+1}$ , $\mathbf{0} \le \mathbf{i} \le \mathbf{n} \cdot \mathbf{1}$ $\mathbf{g}_n = \mathbf{b}_n$ **Reflection of Gray codes** and 0 000 $\mathbf{b}_{n-i} = \mathbf{g}_n \oplus \mathbf{g}_{n-1} \oplus \ldots \oplus \mathbf{g}_{n-i}$ $\mathbf{b}_n = \mathbf{g}_n$ <u>1 0 0 10</u> 0 010 1 10 0 110 1 11 0 111 1 01 0 101 0 100 1 00 Note: 1 100 1 101 The Gray code has a reflection property 1 111 - easy to construct a table without calculation, 1 010 - for any n: reflect case n-1 about a 1 011 mirror at its bottom and prefix 0 and 1 1 001 1 101 to top and bottom halves, respectively 1 000

### CHARACTER REPRESENTATION ASCII

ASCII (American Standard Code for Information Interchange) Code

|          |   | 0   | 1   | 2  | 3 | 4 | 5 | 6 | 7   |

|----------|---|-----|-----|----|---|---|---|---|-----|

| LSB      | 0 | NUL | DLE | SP | 0 | @ | Ρ | " | Ρ   |

| (4 bits) | 1 | SOH | DC1 | !  | 1 | Α | Q | а | q   |

| (1.0100) | 2 | STX | DC2 | "  | 2 | В | R | b | r   |

|          | 3 | ETX | DC3 | #  | 3 | С | S | С | S   |

|          | 4 | EOT | DC4 | \$ | 4 | D | Т | d | t   |

|          | 5 | ENQ | NAK | %  | 5 | Е | U | е | u   |

|          | 6 | ACK | SYN | &  | 6 | F | V | f | v   |

|          | 7 | BEL | ETB | "  | 7 | G | W | g | w   |

|          | 8 | BS  | CAN | (  | 8 | Н | Χ | h | x   |

|          | 9 | ΗT  | EM  | )  | 9 | I | Υ | I | У   |

|          | Α | LF  | SUB | *  | : | J | Ζ | j | z   |

|          | В | VT  | ESC | +  | ; | Κ | [ | k | {   |

|          | С | FF  | FS  | ,  | < | L | ١ | I | I   |

|          | D | CR  | GS  | -  | = | Μ | ] | m | }   |

|          | Е | SO  | RS  |    | > | Ν | m | n | ~   |

|          | F | SI  | US  | 1  | ? | 0 | n | 0 | DEL |

MSB (3 bits)

# CONTROL CHARACTER REPRESENTAION (ACSII)

| NUL | Null                     | DC1 | Device Control 1               |

|-----|--------------------------|-----|--------------------------------|

|     |                          |     |                                |

| SOH | Start of Heading (CC)    | DC2 | Device Control 2               |

| STX | Start of Text (CC)       | DC3 | Device Control 3               |

| ETX | End of Text (CC)         | DC4 | Device Control 4               |

| EOT | End of Transmission (CC) | NAK | Negative Acknowledge (CC)      |

| ENQ | Enquiry (CC)             | SYN | Synchronous Idle (CC)          |

| ACK | Acknowledge (CC)         | ETB | End of Transmission Block (CC) |

| BEL | Bell                     | CAN | Cancel                         |

| BS  | Backspace (FE)           | EM  | End of Medium                  |

| ΗТ  | Horizontal Tab. (FE)     | SUB | Substitute                     |

| LF  | Line Feed (FE)           | ESC | Escape                         |

| VT  | Vertical Tab. (FE)       | FS  | File Separator (IS)            |

| FF  | Form Feed (FE)           | GS  | Group Separator (IS)           |

| CR  | Carriage Return (FE)     | RS  | Record Separator (IS)          |

| SO  | Shift Out                | US  | Unit Separator (IS)            |

| SI  | Shift In                 | DEL | Delete                         |

| DLE | Data Link Escape (CC)    |     |                                |

- (CC) Communication Control

- (FE) Format Effector

- (IS) Information Separator

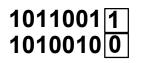

# ERROR DETECTING CODES

#### Parity System

- Simplest method for error detection

- One parity bit attached to the information

- Even Parity and Odd Parity

**Even Parity**

- One bit is attached to the information so that the total number of 1 bits is an even number

10110010 10100101

**Odd Parity**

- One bit is attached to the information so that the total number of 1 bits is an odd number

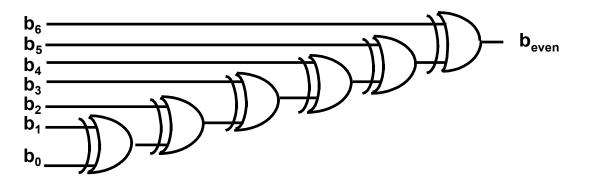

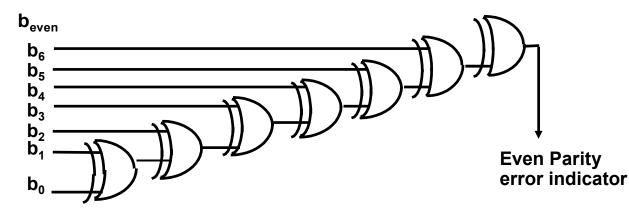

# **PARITY BIT GENERATION**

#### **Parity Bit Generation**

For  $b_6b_5...$   $b_0$ (7-bit information); even parity bit  $b_{even}$

$\mathbf{b}_{even} = \mathbf{b}_6 \oplus \mathbf{b}_5 \oplus ... \oplus \mathbf{b}_0$

For odd parity bit

$\mathbf{b}_{odd} = \mathbf{b}_{even} \oplus \mathbf{1} = \overline{\mathbf{b}}_{even}$

#### Error Detecting codes

### PARITY GENERATOR AND PARITY CHECKER

#### **Parity Generator Circuit (even parity)**

#### **Parity Checker**

# **REGISTER TRANSFER AND MICROOPERATIONS**

- Register Transfer Language

- Register Transfer

- Bus and Memory Transfers

- Arithmetic Micro-operations

- Logic Micro-operations

- Shift Micro-operations

- Arithmetic Logic Shift Unit

# SIMPLE DIGITAL SYSTEMS

- Combinational and sequential circuits (learned in Chapters 1 and 2) can be used to create simple digital systems.

- These are the low-level building blocks of a digital computer.

- Simple digital systems are frequently characterized in terms of

- the registers they contain, and

- the operations that they perform.

- Typically,

- What operations are performed on the data in the registers

- What information is passed between registers

# MICROOPERATIONS (1)

- The operations on the data in registers are called micro-operations.

- The functions built into registers are examples of micro-operations

- Shift

- Load

- Clear

- Increment

- ...

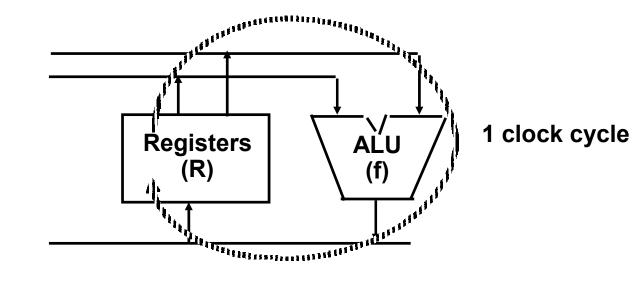

### **MICROOPERATION (2)**

An elementary operation performed (during one clock pulse), on the information stored in one or more registers

$R \leftarrow f(R, R)$

f: shift, load, clear, increment, add, subtract, complement, and, or, xor, ...

## **ORGANIZATION OF A DIGITAL SYSTEM**

### Definition of the (internal) organization of a computer

- Set of registers and their functions

- Micro-operations set

Set of allowable micro-operations provided by the organization of the computer

- Control signals that initiate the sequence of micro-operations (to perform the functions)

# **REGISTER TRANSFER LEVEL**

- Viewing a computer, or any digital system, in this way is called the register transfer level

- This is because we're focusing on

- The system's registers

- The data transformations in them, and

- The data transfers between them.

# REGISTER TRANSFER LANGUAGE

- Rather than specifying a digital system in words, a specific notation is used, *register transfer language*

- For any function of the computer, the register transfer language can be used to describe the (sequence of) micro-operations

- Register transfer language

- A symbolic language

- A convenient tool for describing the internal organization of digital computers

- Can also be used to facilitate the design process of digital systems.

# DESIGNATION OF REGISTERS

- Registers are designated by capital letters, sometimes followed by numbers (e.g., A, R13, IR)

- Often the names indicate function:

- MAR memory address register

- PC program counter

- IR instruction register

- Registers and their contents can be viewed and represented in *various ways*

- A register can be viewed as a single entity:

### MAR

- Registers may also be represented showing the bits of data they contain

# DESIGNATION OF REGISTERS

- Designation of a register

- a register

- portion of a register

- a bit of a register

• Common ways of drawing the block diagram of a register

| Register          |   |   | S | Showing individual bits |     |     |   |   |   |      |   |  |

|-------------------|---|---|---|-------------------------|-----|-----|---|---|---|------|---|--|

| R                 | 1 |   |   | 7                       | 6   | 5   | 4 | 3 | 2 | 1    | 0 |  |

| 15                |   | 0 | 1 | 5                       |     |     | 8 | 7 |   |      | 0 |  |

| R                 | 2 |   | E |                         | PC  | (H) |   |   | P | C(L) |   |  |

| Numbering of bits |   |   | S | ubfie                   | lds |     |   |   |   |      |   |  |

# **REGISTER TRANSFER**

- Copying the contents of one register to another is a register transfer

- A register transfer is indicated as

#### **R2** ← **R**1

- In this case the contents of register R2 are copied (loaded) into register R1

- A simultaneous transfer of all bits from the source R1 to the destination register R2, during one clock pulse

- Note that this is a non-destructive; i.e. the contents of R1 are not altered by copying (loading) them to R2

### **REGISTER TRANSFER**

- A register transfer such as

- $R3 \leftarrow R5$

Implies that the digital system has

- the data lines from the source register (R5) to the destination register (R3)

- Parallel load in the destination register (R3)

- Control lines to perform the action

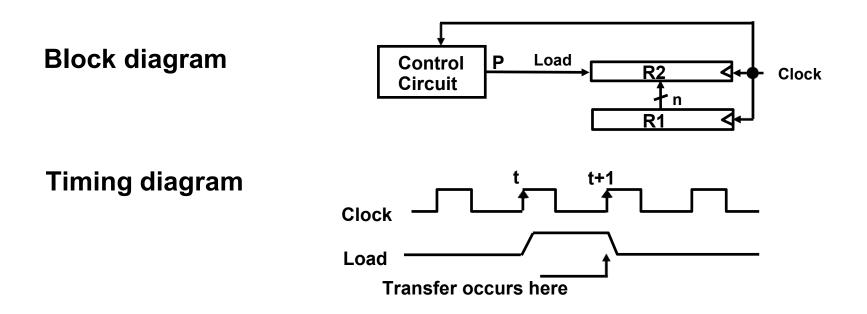

# **CONTROL FUNCTIONS**

- Often actions need to only occur if a certain condition is true

- This is similar to an "if" statement in a programming language

- In digital systems, this is often done via a *control signal*, called a *control function*

- If the signal is 1, the action takes place

- This is represented as:

$R2 \leftarrow R1$

Which means "if P = 1, then load the contents of register R1 into register R2", i.e., if (P = 1) then (R2  $\leftarrow$  R1)

#### HARDWARE IMPLEMENTATION OF CONTROLLED TRANSFERS

#### Implementation of controlled transfer

P: R2 ← R1

- The same clock controls the circuits that generate the control function and the destination register

- Registers are assumed to use *positive-edge-triggered* flip-flops

### SIMULTANEOUS OPERATIONS

• If two or more operations are to occur simultaneously, they are separated with commas

```

P: R3 \leftarrow R5, MAR \leftarrow IR

```

• Here, if the control function P = 1, load the contents of R5 into R3, and at the same time (clock), load the contents of register IR into register MAR

#### Register Transfer

# BASIC SYMBOLS FOR REGISTER TRANSFERS

| Symbols         | Description                                     | Examples                         |  |  |  |  |

|-----------------|-------------------------------------------------|----------------------------------|--|--|--|--|

| Capital letters | Denotes a register                              | MAR, R2                          |  |  |  |  |

| & numerals      |                                                 |                                  |  |  |  |  |

| Parentheses ()  | Denotes a part of a register                    | R2(0-7), R2(L)                   |  |  |  |  |

| Arrow ←         | Denotes transfer of information                 | R2 ← R1                          |  |  |  |  |

| Colon :         | Colon : Denotes termination of control function |                                  |  |  |  |  |

| Comma ,         | Separates two micro-operations                  | $A \leftarrow B, B \leftarrow A$ |  |  |  |  |

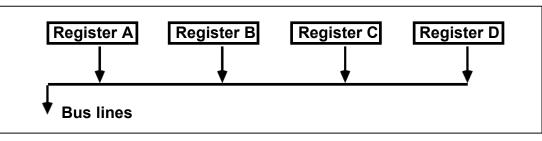

# CONNECTING REGISTRS

- In a digital system with many registers, it is impractical to have data and control lines to directly allow each register to be loaded with the contents of every possible other registers

- To completely connect n registers  $\rightarrow$  n(n-1) lines

- $O(n^2) \cos t$

- This is not a realistic approach to use in a large digital system

- Instead, take a different approach

- Have one centralized set of circuits for data transfer the bus

- Have control circuits to select which register is the source, and which is the destination

# BUS AND BUS TRANSFER

Bus is a path(of a group of wires) over which information is transferred, from any of several sources to any of several destinations.

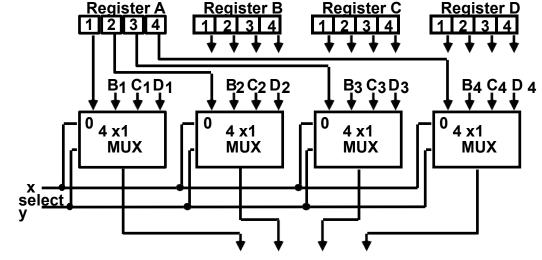

### From a register to bus: $BUS \leftarrow R$

4-line bus

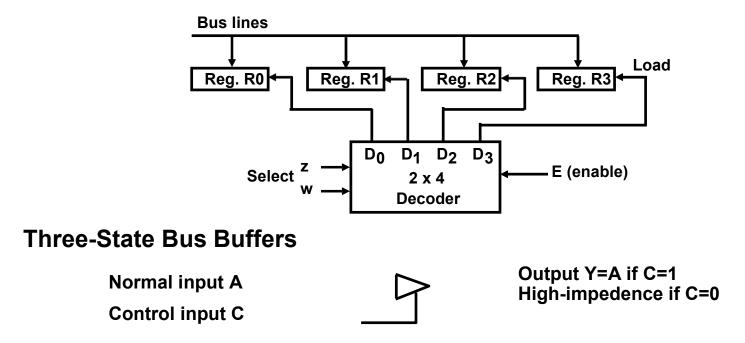

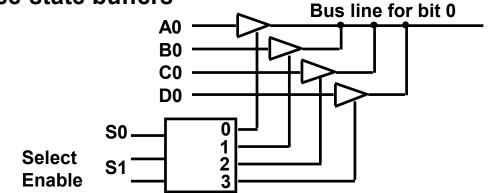

#### TRANSFER FROM BUS TO A DESTINATION REGISTER

Bus line with three-state buffers

#### BUS TRANSFER IN RTL

• Depending on whether the bus is to be mentioned explicitly or not, register transfer can be indicated as either

R2 ← R1

or  $BUS \leftarrow R1, R2 \leftarrow BUS$

• In the former case the bus is implicit, but in the latter, it is explicitly indicated

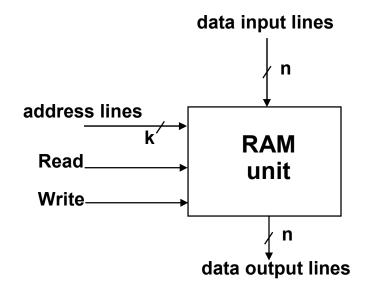

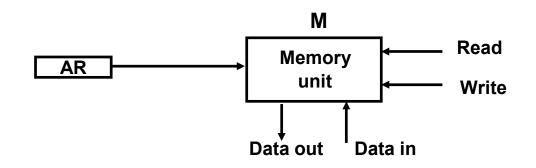

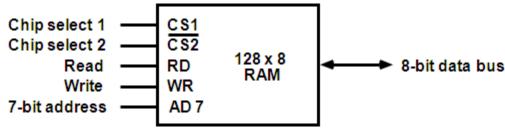

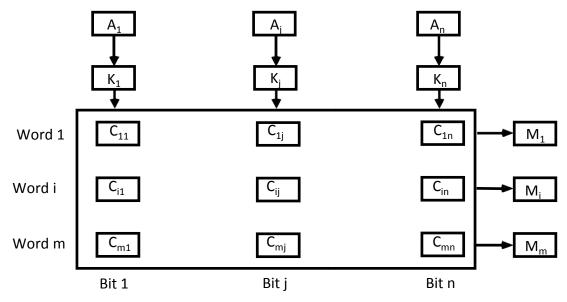

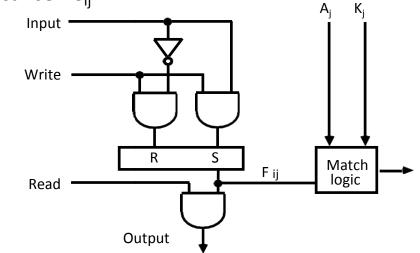

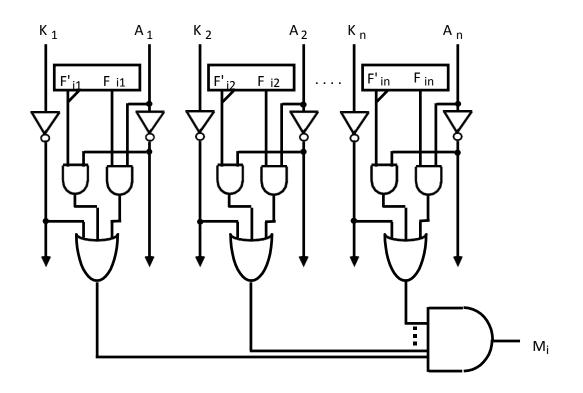

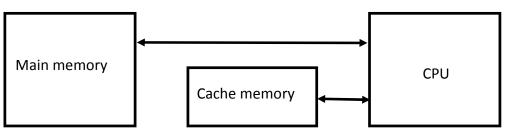

# MEMORY (RAM)

- Memory (RAM) can be thought as a sequential circuits containing some number of registers

- These registers hold the *words* of memory

- Each of the r registers is indicated by an *address*

- These addresses range from 0 to r-1

- Each register (word) can hold n bits of data

- Assume the RAM contains r = 2k words. It needs the following

- n data input lines

- n data output lines

- k address lines

- A Read control line

- A Write control line

#### MEMORY TRANSFER

- Collectively, the memory is viewed at the register level as a device, M.

- Since it contains multiple locations, we must specify which address in memory we will be using

- This is done by indexing memory references

- Memory is usually accessed in computer systems by putting the desired address in a special register, the *Memory Address Register* (*MAR*, or *AR*)

- When memory is accessed, the contents of the MAR get sent to the memory unit's address lines

# MEMORY READ

• To read a value from a location in memory and load it into a register, the register transfer language notation looks like this:

#### $R1 \leftarrow M[MAR]$

- This causes the following to occur

- The contents of the MAR get sent to the memory address lines

- A Read (= 1) gets sent to the memory unit

- The contents of the specified address are put on the memory's output data lines

- These get sent over the bus to be loaded into register R1

# MEMORY WRITE

• To write a value from a register to a location in memory looks like this in register transfer language:

#### $M[MAR] \leftarrow R1$

- This causes the following to occur

- The contents of the MAR get sent to the memory addresslines

- A Write (= 1) gets sent to the memory unit

- The values in register R1 get sent over the bus to the data input lines of the memory

- The values get loaded into the specified address in the memory

#### SUMMARY OF R. TRANSFER MICROOPERATIONS

| A ← B                  | Transfer content of reg. B into reg. A                   |

|------------------------|----------------------------------------------------------|

| $AR \leftarrow DR(AD)$ | Transfer content of AD portion of reg. DR into reg. AR   |

| A ← constant           | Transfer a binary constant into reg. A                   |

| ABUS $\leftarrow$ R1,  | Transfer content of R1 into bus A and, at the same time, |

| R2 ← ABUS              | transfer content of bus A into R2                        |

| AR                     | Address register                                         |

| DR                     | Data register                                            |

| M[R]                   | Memory word specified by reg. R                          |

| Μ                      | Equivalent to M[AR]                                      |

| $DR \leftarrow M$      | Memory read operation: transfers content of              |

|                        | memory word specified by AR into DR                      |

| M← DR                  | Memory write operation: transfers content of             |

|                        | DR into memory word specified by AR                      |

## MICROOPERATIONS

- Computer system microoperations are of four types:

- Register transfer microoperations

- Arithmetic microoperations

- Logic microoperations

- Shift microoperations

# ARITHMETIC MICROOPERATIONS

- The basic arithmetic microoperations are

- Addition

- Subtraction

- Increment

- Decrement

- The additional arithmetic microoperations are

- Add with carry

- Subtract with borrow

- Transfer/Load

- etc. ...

#### **Summary of Typical Arithmetic Micro-Operations**

| $R3 \leftarrow R1 + R2$ $R3 \leftarrow R1 - R2$ $R2 \leftarrow R2'$ $R2 \leftarrow R2' + 1$ | Contents of R1 plus R2 transferred to R3<br>Contents of R1 minus R2 transferred to R3<br>Complement the contents of R2<br>2's complement the contents of R2 (negate) |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R3 ← R1 + R2'+ 1<br>R1 ← R1 + 1                                                             | subtraction<br>Increment                                                                                                                                             |

| R1 ← R1 - 1                                                                                 | Decrement                                                                                                                                                            |

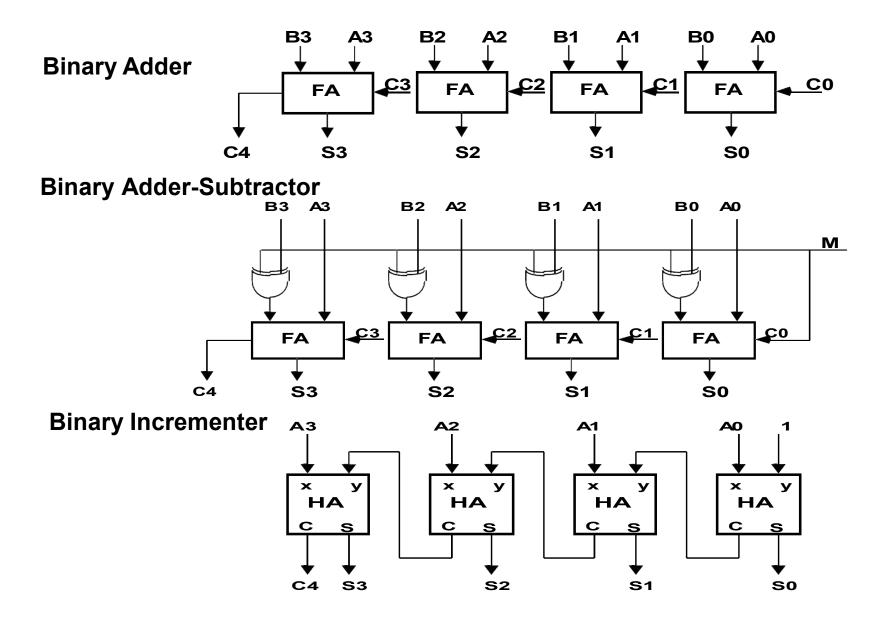

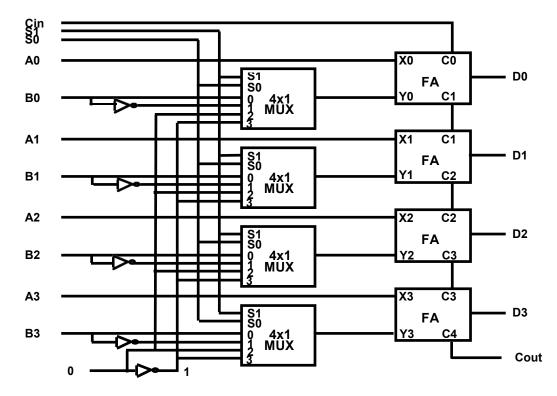

# BINARY ADDER / SUBTRACTOR / INCREMENTER

#### ARITHMETIC CIRCUIT

| S1 | S0 | Cin | Y  | Output        | Microoperation       |

|----|----|-----|----|---------------|----------------------|

| 0  | 0  | 0   | В  | D = A + B     | Add                  |

| 0  | 0  | 1   | В  | D = A + B + 1 | Add with carry       |

| 0  | 1  | 0   | B' | D = A + B'    | Subtract with borrow |

| 0  | 1  | 1   | B' | D = A + B'+ 1 | Subtract             |

| 1  | 0  | 0   | 0  | D = A         | Transfer A           |

| 1  | 0  | 1   | 0  | D = A + 1     | Increment A          |

| 1  | 1  | 0   | 1  | D = A - 1     | Decrement A          |

| 1  | 1  | 1   | 1  | D = A         | Transfer A           |

# LOGIC MICROOPERATIONS

- Specify binary operations on the strings of bits in registers

- Logic microoperations are bit-wise operations, i.e., they work on the individual bits of data

- useful for bit manipulations on binary data

- useful for making logical decisions based on the bitvalue

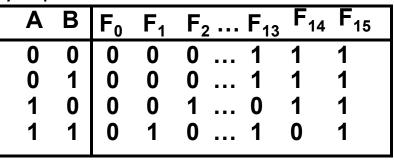

- There are, in principle, 16 different logic functions that can be defined over two binary input variables

- However, most systems only implement four of these

- − AND ( $\land$ ), OR ( $\lor$ ), XOR ( $\oplus$ ), Complement/NOT

- The others can be created from combination of these

# LIST OF LOGIC MICROOPERATIONS

#### List of Logic Microoperations

- 16 different logic operations with 2 binary vars.

- n binary vars  $\rightarrow$  2 <sup>2 n</sup>functions

- Truth tables for 16 functions of 2 variables and the corresponding 16 logic micro-operations

| X |      | Boolean       | Micro-                              | Name           |

|---|------|---------------|-------------------------------------|----------------|

| У | 0101 | Function      | Operations                          |                |

|   | 0000 | F0 = 0        | F ← 0                               | Clear          |

|   | 0001 | F1 = xy       | $F \leftarrow A \land B$            | AND            |

|   | 0010 | F2 = xy'      | $F \leftarrow A \land B'$           |                |

|   | 0011 | F3 = x        | F←A                                 | Transfer A     |

|   | 0100 | F4 = x'y      | F   ←   A'∧ B                       |                |

|   | 0101 | F5 = y        | F ← B                               | Transfer B     |

|   | 0110 | F6 = x⊕ y     | $F \leftarrow A \oplus B$           | Exclusive-OR   |

|   | 0111 | F7 = x + y    | $F \leftarrow A \lor B$             | OR             |

|   | 1000 | F8 = (x + y)' | <b>F</b> ← ( <b>A</b> ∨ <b>B</b> )' | NOR            |

|   | 1001 | F9 = (x ⊕ y)' | F ← (A ⊕ B)'                        | Exclusive-NOR  |

|   | 1010 | F10 = y'      | F   ← B'                            | Complement B   |

|   | 1011 | F11 = x + y'  | $F \leftarrow A \lor B$             |                |

|   | 1100 | F12 = x'      | F ← A'                              | Complement A   |

|   | 1101 | F13 = x' + y  | F ← A'∨ B                           |                |

|   | 1110 | F14 = (xy)'   | F ← (A ∧ B)'                        | NAND           |

|   | 1111 | F15 = 1       | F ← all 1's                         | Set to all 1's |

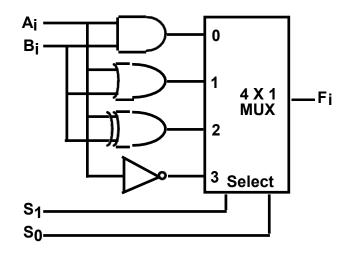

#### HARDWARE IMPLEMENTATION OF LOGIC MICROOPERATIONS

#### **Function table**

| S <sub>1</sub> | S <sub>0</sub> | Output           | μ-operation |

|----------------|----------------|------------------|-------------|

| 0              | 0              | F = A ∧ B        | AND         |

| 0              | 1              | $F = A \lor B$   | OR          |

| 1              | 0              | $F = A \oplus B$ | XOR         |

| 1              | 1              | F = A'           | Complement  |

# APPLICATIONS OF LOGIC MICROOPERATIONS

- Logic microoperations can be used to manipulate individual bits or a portions of a word in a register

- Consider the data in a register A. In another register, B, is bit data that will be used to modify the contents of A

- Selective-set

- Selective-complement

- Selective-clear

- Mask (Delete)

- Clear

- Insert

- Compare

$A \leftarrow A + B$  $A \leftarrow A \oplus B$  $A \leftarrow A \bullet B'$  $A \leftarrow A \bullet B$  $A \leftarrow A \oplus B$  $A \leftarrow (A \bullet B) + C$  $A \leftarrow A \oplus B$

# SELECTIVE SET

• In a selective set operation, the bit pattern in B is used to *set* certain bits in A

• If a bit in B is set to 1, that same position in A gets set to 1, otherwise that bit in A keeps its previous value

# SELECTIVE COMPLEMENT

• In a selective complement operation, the bit pattern in B is used to complement certain bits in A

> 1100 A<sub>t</sub> <u>1010 B</u>

> > 0110  $A_{t+1}$  (A  $\leftarrow$  A  $\oplus$  B)

• If a bit in B is set to 1, that same position in A gets complemented from its original value, otherwise it is unchanged

# SELECTIVE CLEAR

• In a selective clear operation, the bit pattern in B is used to *clear* certain bits in A

1100 A<sub>t</sub> <u>1010 B</u>

$\begin{array}{ccc} 0 \ 1 \ 0 \ 0 & A_{t+1} \end{array} & (A \leftarrow A \ \cdot B') \end{array}$

• If a bit in B is set to 1, that same position in A gets set to 0, otherwise it is unchanged

#### MASK OPERATION

In a mask operation, the bit pattern in B is used to *clear* certain bits in A

• If a bit in B is set to 0, that same position in A gets set to 0, otherwise it is unchanged

#### **CLEAR OPERATION**

• In a clear operation, if the bits in the same position in A and B are the same, they are cleared in A, otherwise they are set in A

# **INSERT OPERATION**

- An insert operation is used to introduce a specific bit pattern into A register, leaving the other bit positions unchanged

- This is done as

- A mask operation to clear the desired bit positions, followed by

- An OR operation to introduce the new bits into the desired positions

- Example

- Suppose you wanted to introduce 1010 into the low order four bits of A: 1101 1000 1011 0001 A (Original) 1101 1000 1011 1010 A

(Desired)

| • | 1101  | 1000           | 1011  | 0001 | A (Original) |

|---|-------|----------------|-------|------|--------------|

|   | 1111  | 1111           | 1111  | 0000 | Mask         |

|   | 1101  | 1000           | 1011  | 0000 | А            |

|   |       |                |       |      |              |

| • | (Inte | ermedi         | Late) |      |              |

| - | •     | ermedi<br>0000 | •     | 1010 | Added bits   |

#### SHIFT MICROOPERATIONS

- There are three types of shifts

- Logical shift

- Circular shift

- Arithmetic shift

- What differentiates them is the information that goes into the serial input

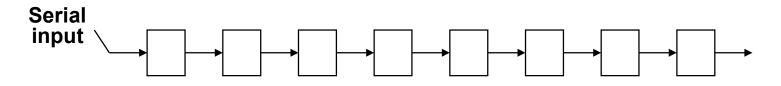

#### A right shift operation

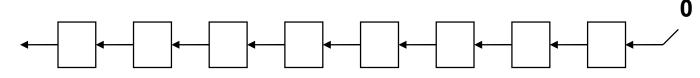

# LOGICAL SHIFT

- In a logical shift the serial input to the shift is a 0.

- A right logical shift operation:

• A left logical shift operation:

- In a Register Transfer Language, the following notation is used

- shl

for a logical shift left

- *shr* for a logical shift right

- Examples:

- R2  $\leftarrow$  shr R2

- R3  $\leftarrow$  shl R3

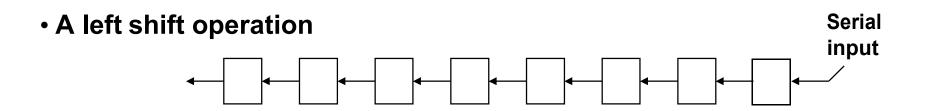

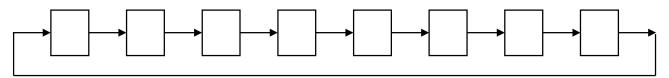

#### **CIRCULAR SHIFT**

- In a circular shift the serial input is the bit that is shifted out of the other end of the register.

- A right circular shift operation:

• A left circular shift operation:

- In a RTL, the following notation is used

- cil for a circular shift left

- *cir* for a circular shift right

- Examples:

- R2  $\leftarrow$  cir R2

- R3  $\leftarrow$  cil R3

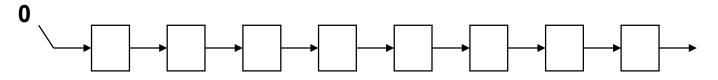

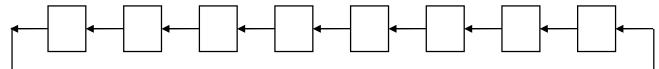

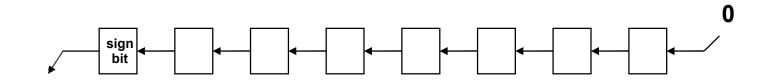

## **ARITHMETIC SHIFT**

- An arithmetic shift is meant for signed binary numbers (integer)

- An arithmetic left shift multiplies a signed number by two

- An arithmetic right shift divides a signed number by two

- The main distinction of an arithmetic shift is that it must keep the sign of the number the same as it performs the multiplication or division

- A right arithmetic shift operation:

A left arithmetic shift operation:

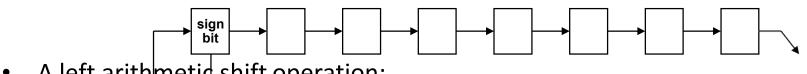

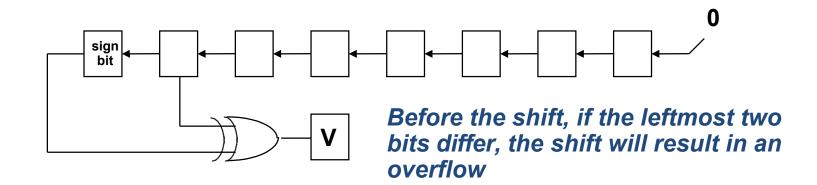

# **ARITHMETIC SHIFT**

• An left arithmetic shift operation must be checked for the overflow

- In a RTL, the following notation is used

- ashl for an arithmetic shift left

- *ashr* for an arithmetic shift right

- Examples:

- »  $R2 \leftarrow ashr R2$

- » R3 ← ashl R3

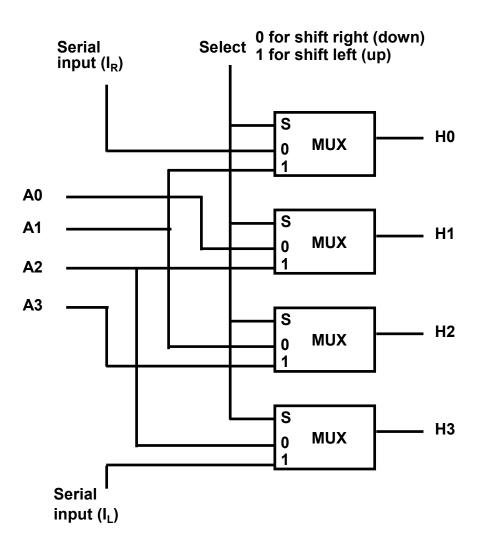

#### HARDWARE IMPLEMENTATION OF SHIFT MICROOPERATIONS

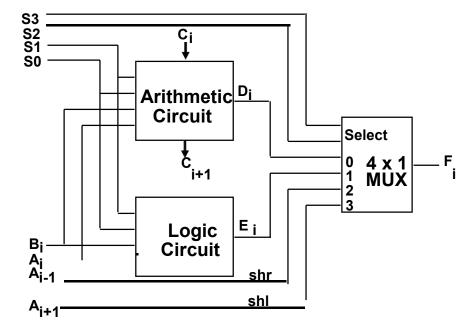

# ARITHMETIC LOGIC SHIFT UNIT

| <b>S</b> 3 | S2 | <b>S1</b> | S0 | Cin | Operation        | Function             |

|------------|----|-----------|----|-----|------------------|----------------------|

| 0          | 0  | 0         | 0  | 0   | F = A            | Transfer A           |

| 0          | 0  | 0         | 0  | 1   | F = A + 1        | Increment A          |

| 0          | 0  | 0         | 1  | 0   | F = A + B        | Addition             |

| 0          | 0  | 0         | 1  | 1   | F = A + B + 1    | Add with carry       |

| 0          | 0  | 1         | 0  | 0   | F = A + B'       | Subtract with borrow |

| 0          | 0  | 1         | 0  | 1   | F = A + B'+ 1    | Subtraction          |

| 0          | 0  | 1         | 1  | 0   | F = A - 1        | Decrement A          |

| 0          | 0  | 1         | 1  | 1   | F = A            | TransferA            |

| 0          | 1  | 0         | 0  | X   | $F = A \wedge B$ | AND                  |

| 0          | 1  | 0         | 1  | X   | $F = A \vee B$   | OR                   |

| 0          | 1  | 1         | 0  | X   | $F = A \oplus B$ | XOR                  |

| 0          | 1  | 1         | 1  | X   | F = A'           | Complement A         |

| 1          | 0  | Х         | Х  | X   | F = shr A        | Shift right A into F |

| 1          | 1  | Χ         | X  | X   | F = shl A        | Shift left A into F  |

## **BASIC COMPUTER ORGANIZATION AND DESIGN**

- Instruction Codes

- Computer Registers

- Computer Instructions

- Timing and Control

- Instruction Cycle

- Memory Reference Instructions

- Input-Output and Interrupt

- Complete Computer Description

- Design of Basic Computer

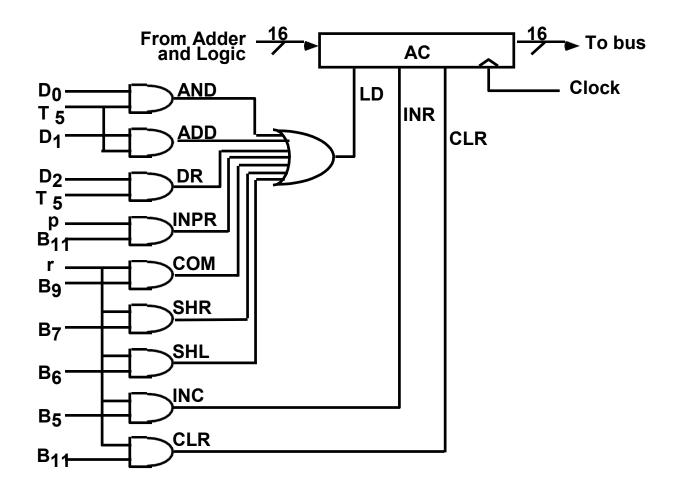

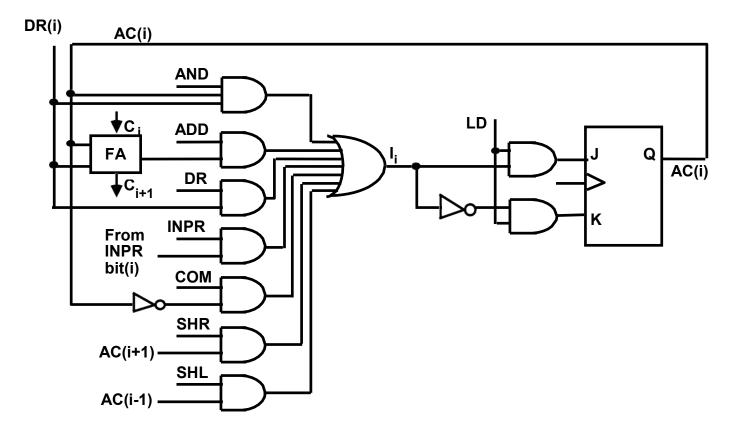

- Design of Accumulator Logic

# INTRODUCTION

- Every different processor type has its own design (different registers, buses, micro-operations, machine instructions, etc)

- Modern processor is a very complex device

- It contains

- Many registers

- Multiple arithmetic units, for both integer and floating point calculations

- The ability to pipeline several consecutive instructions to speed execution

- Etc.

- However, to understand how processors work, we will start with a simplified processor model

- This is similar to what real processors were like  $\sim 25$  years ago

- M. Morris Mano introduces a simple processor model he calls the *Basic Computer*

- We will use this to introduce processor organization and the relationship of the RTL model to the higher level computer processor

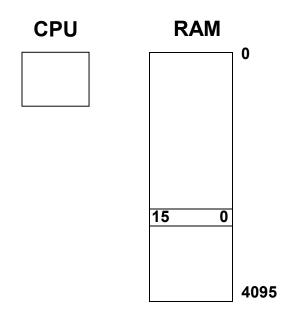

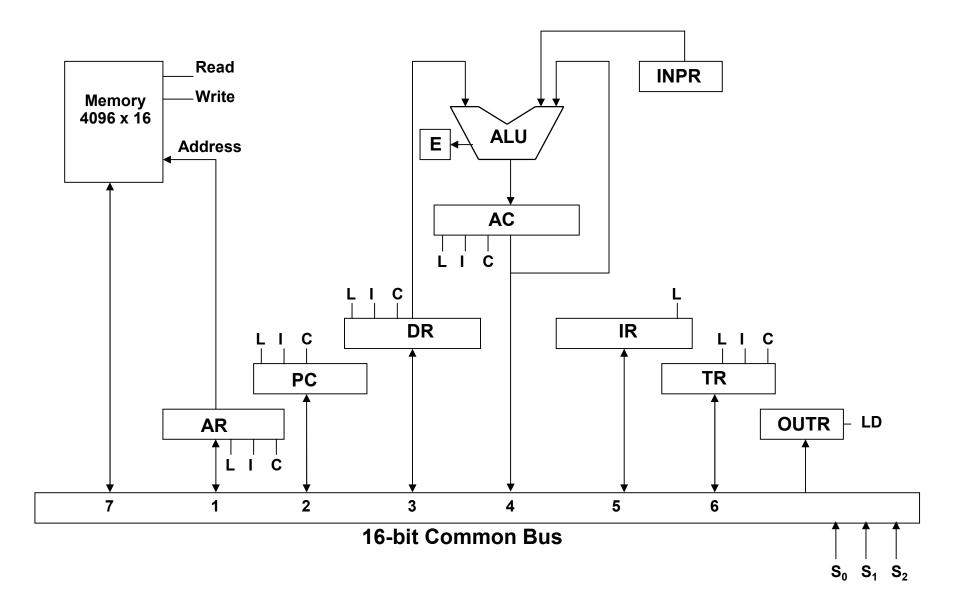

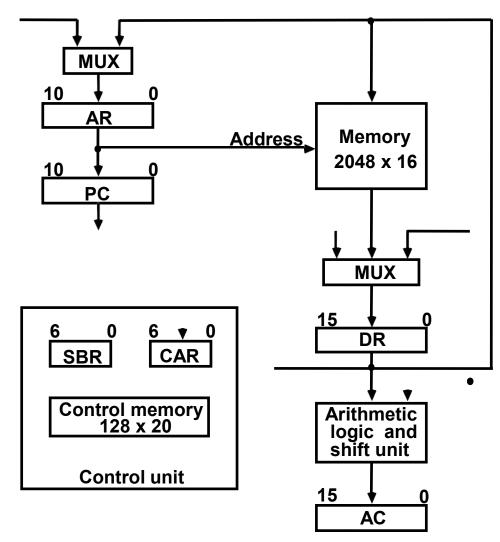

# THE BASIC COMPUTER

- The Basic Computer has two components, a processor and memory

- The memory has 4096 words in it

- $-4096 = 2^{12}$ , so it takes 12 bits to select a word in memory

- Each word is 16 bits long

# INSTRUCTIONS

- Program

- A sequence of (machine) instructions

- (Machine) Instruction

- A group of bits that tell the computer to *perform a specific operation* (a sequence of micro-operation)

- The instructions of a program, along with any needed data are stored in memory

- The CPU reads the next instruction from memory

- It is placed in an *Instruction Register* (IR)

- Control circuitry in control unit then translates the instruction into the sequence of microoperations necessary to implement it

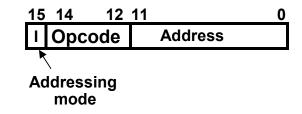

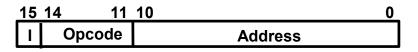

# INSTRUCTION FORMAT

- A computer instruction is often divided into two parts

- An *opcode* (Operation Code) that specifies the operation for that instruction

- An *address* that specifies the registers and/or locations in memory to use for that operation

- In the Basic Computer, since the memory contains 4096 (= 2<sup>12</sup>) words, we needs 12 bit to specify which memory address this instruction will use

- In the Basic Computer, bit 15 of the instruction specifies the *addressing mode* (0: direct addressing, 1: indirect addressing)

- Since the memory words, and hence the instructions, are 16 bits long, that leaves 3 bits for the instruction's opcode

#### Instruction Format

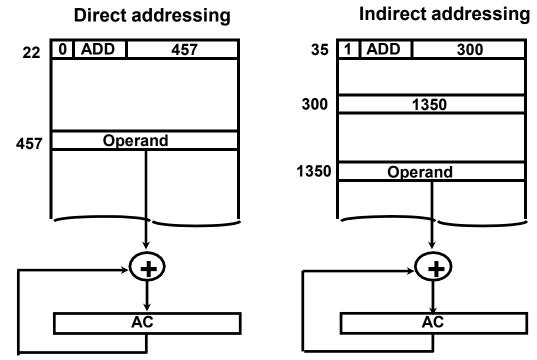

#### ADDRESSING MODES

- The address field of an instruction can represent either

- Direct address: the address in memory of the data to use (the address of the operand), or

- Indirect address: the address in memory of the address in memory of the data to use

- Effective Address (EA)

- The address, that can be directly used without modification to access an operand for a computation-type instruction, or as the target address for a branch-type instruction

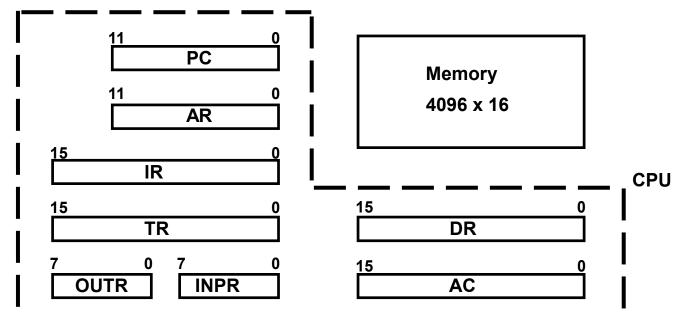

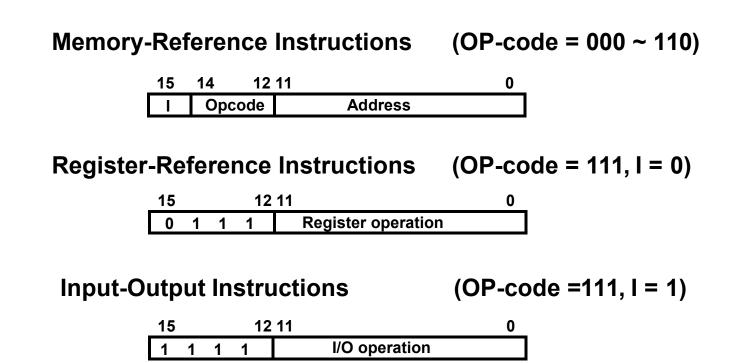

#### **PROCESSOR REGISTERS**

- A processor has many registers to hold instructions, addresses, data, etc

- The processor has a register, the *Program Counter* (PC) that holds the memory address of the next instruction to get

- Since the memory in the Basic Computer only has 4096 locations, the PC only needs 12 bits

- In a direct or indirect addressing, the processor needs to keep track of what locations in memory it is addressing: The *Address Register* (AR) is used for this

- The AR is a 12 bit register in the Basic Computer

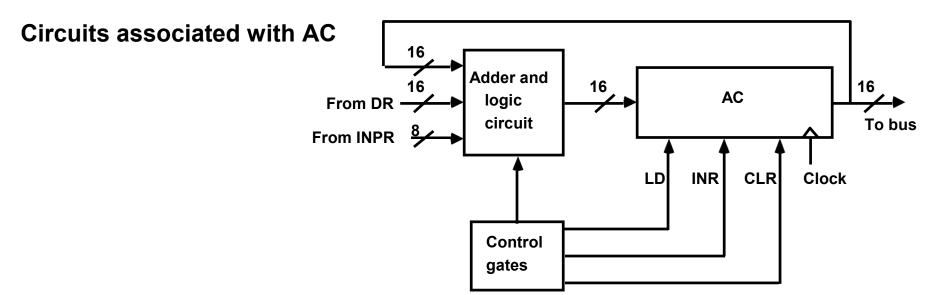

- When an operand is found, using either direct or indirect addressing, it is placed in the *Data Register* (DR). The processor then uses this value as data for its operation

- The Basic Computer has a single *general purpose register* the *Accumulator* (AC)

# PROCESSOR REGISTERS

- The significance of a general purpose register is that it can be referred to in instructions

- e.g. load AC with the contents of a specific memory location; store the contents of AC into a specified memory location

- Often a processor will need a scratch register to store intermediate results or other temporary data; in the Basic Computer this is the *Temporary Register* (TR)

- The Basic Computer uses a very simple model of input/output (I/O) operations

- Input devices are considered to send 8 bits of character data to the processor

- The processor can send 8 bits of character data to output devices

- The *Input Register* (INPR) holds an 8 bit character gotten from an input device

- The *Output Register* (OUTR) holds an 8 bit character to be send to an output device

Registers

#### BASIC COMPUTER REGISTERS

#### **Registers in the Basic Computer**

#### List of BC Registers

| DR   | 16 | Data Register        | Holds memory operand         |

|------|----|----------------------|------------------------------|

| AR   | 12 | Address Register     | Holds address for memory     |

| AC   | 16 | Accumulator          | Processor register           |

| IR   | 16 | Instruction Register | Holds instruction code       |

| PC   | 12 | Program Counter      | Holds address of instruction |

| TR   | 16 | Temporary Register   | Holds temporary data         |

| INPR | 8  | Input Register       | Holds input character        |

| OUTR | 8  | Output Register      | Holds output character       |

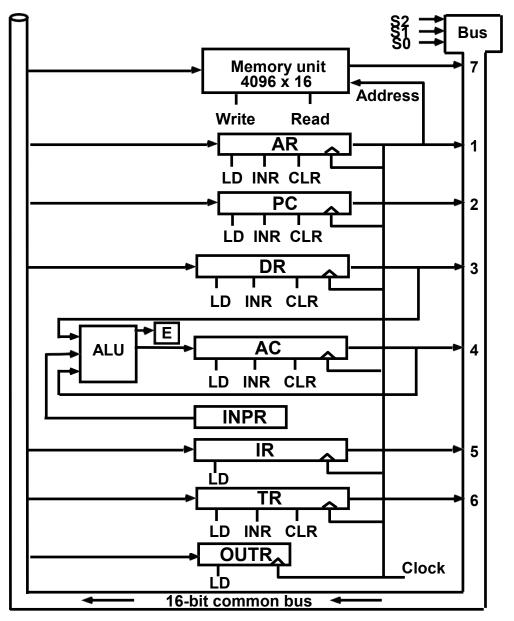

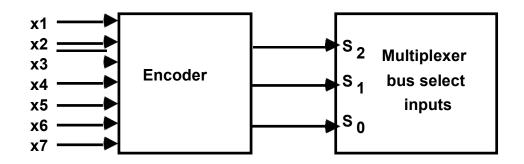

## COMMON BUS SYSTEM

- The registers in the Basic Computer are connected using a bus

- This gives a savings in circuitry over complete connections between registers

Registers

#### COMMON BUS SYSTEM

Registers

## COMMON BUS SYSTEM

## COMMON BUS SYSTEM

• Three control lines, S<sub>2</sub>, S<sub>1</sub>, and S<sub>0</sub> control which register the bus selects as its input

| $S_2 S_1 S_0$ | Register |

|---------------|----------|

| 0 0 0         | X        |

| 001           | AR       |

| 0 1 0         | PC       |

| 0 1 1         | DR       |

| 100           | AC       |

| 101           | IR       |

| 1 1 0         | TR       |

| 1 1 1         | Memory   |

- Either one of the registers will have its load signal activated, or the memory will have its read signal activated

- Will determine where the data from the bus gets loaded

- The 12-bit registers, AR and PC, have 0's loaded onto the bus in the high order 4 bit positions

- When the 8-bit register OUTR is loaded from the bus, the data comes from the low order 8 bits on the bus

## BASIC COMPUTER INSTRUCTIONS

#### Basic Computer Instruction Format

Instructions

## BASIC COMPUTER INSTRUCTIONS

|        | Hex   | Code  |                                    |

|--------|-------|-------|------------------------------------|

| Symbol | 1 = 0 | l = 1 | Description                        |

| AND    | 0xxx  | 8xxx  | AND memory word to AC              |

| ADD    | 1xxx  | 9xxx  | Add memory word to AC              |

| LDA    | 2xxx  | Axxx  | Load AC from memory                |

| STA    | 3xxx  | Bxxx  | Store content of AC into memory    |

| BUN    | 4xxx  | Сххх  | Branch unconditionally             |

| BSA    | 5xxx  | Dxxx  | Branch and save return address     |

| ISZ    | 6xxx  | Exxx  | Increment and skip if zero         |

| CLA    | 78    | 00    | Clear AC                           |

| CLE    | 74    | 00    | Clear E                            |

| СМА    | 72    | 00    | Complement AC                      |

| CME    | 71    | 00    | Complement E                       |

| CIR    | 70    | 80    | Circulate right AC and E           |

| CIL    | 70    | 40    | Circulate left AC and E            |

| INC    | 70    |       | Increment AC                       |

| SPA    | 70    |       | Skip next instr. if AC is positive |

| SNA    | 70    |       | Skip next instr. if AC is negative |

| SZA    | -     | 04    | Skip next instr. if AC is zero     |

| SZE    | -     | 02    | Skip next instr. if E is zero      |

| HLT    | 70    | 01    | Halt computer                      |

| INP    | F8    | 00    | Input character to AC              |

| OUT    | F4    | 00    | Output character from AC           |

| SKI    | F2    | 00    | Skip on input flag                 |

| SKO    | F1    | 00    | Skip on output flag                |

| ION    | F0    | 80    | Interrupt on                       |

| IOF    | F0    | 40    | Interrupt off                      |

## INSTRUCTION SET COMPLETENESS

A computer should have a set of instructions so that the user can construct machine language programs to evaluate any function that is known to be computable.

#### Instruction Types

**Functional Instructions**

- Arithmetic, logic, and shift instructions

- ADD, CMA, INC, CIR, CIL, AND, CLA

**Transfer Instructions**

- Data transfers between the main memory and the processor registers

- LDA, STA

**Control Instructions**

- Program sequencing and control

- BUN, BSA, ISZ

Input/Output Instructions

- Input and output

- INP, OUT

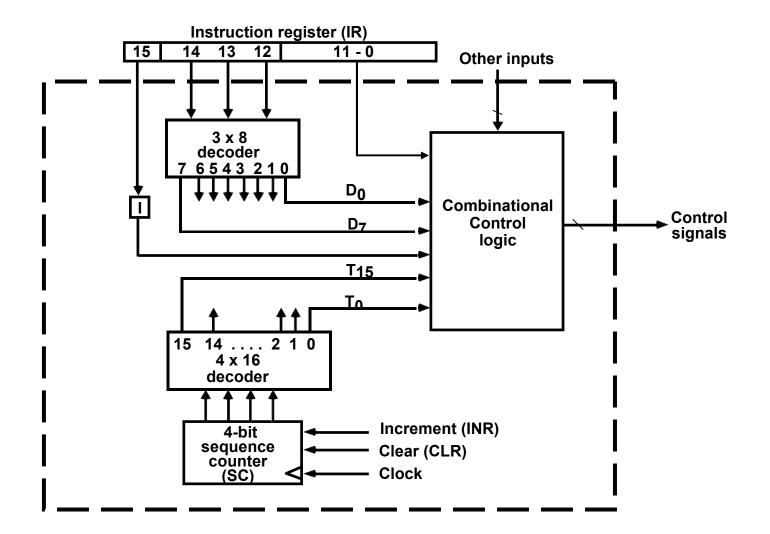

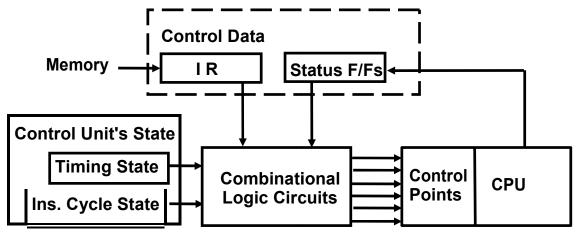

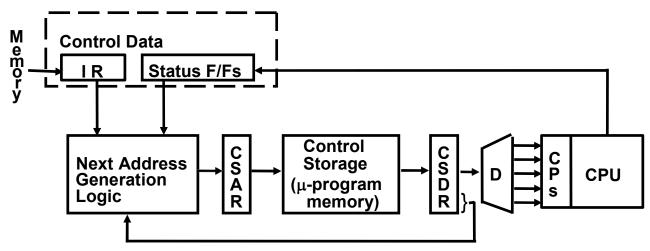

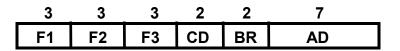

## CONTROL UNIT

- Control unit (CU) of a processor translates from machine instructions to the control signals for the microoperations that implement them

- Control units are implemented in one of two ways

- *Hardwired* Control

- CU is made up of sequential and combinational circuits to generate the control signals

- *Microprogrammed* Control

- A control memory on the processor contains microprograms that activate the necessary control signals

- We will consider a hardwired implementation of the control unit for the Basic Computer

#### TIMING AND CONTROL

#### **Control unit of Basic Computer**

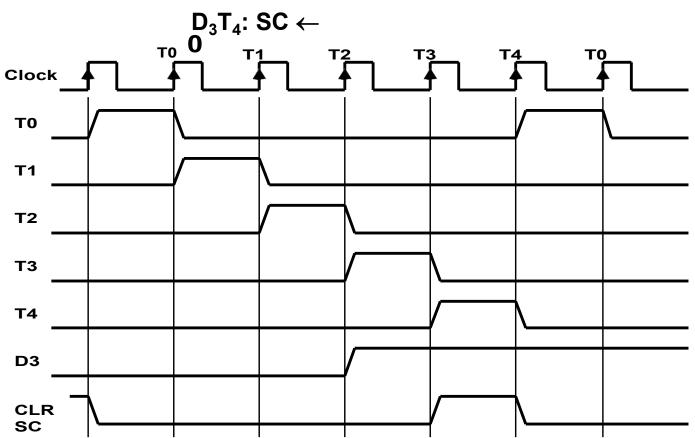

#### TIMING SIGNALS

- Generated by 4-bit sequence counter and 4×16 decoder

- The SC can be incremented or cleared.

- Example:  $T_0$ ,  $T_1$ ,  $T_2$ ,  $T_3$ ,  $T_4$ ,  $T_0$ ,  $T_1$ , ... Assume: At time  $T_4$ , SC is cleared to 0 if decoder output D3 is active.

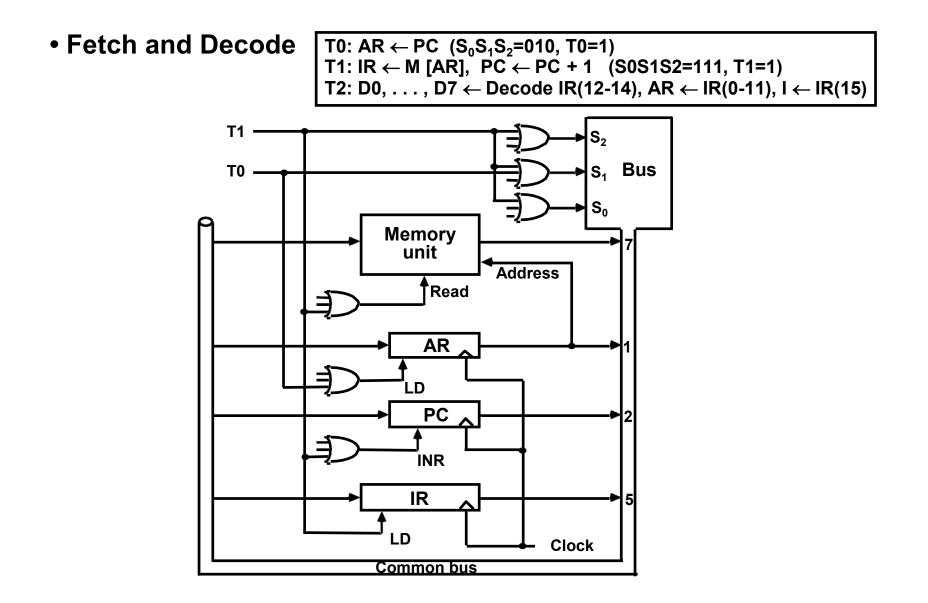

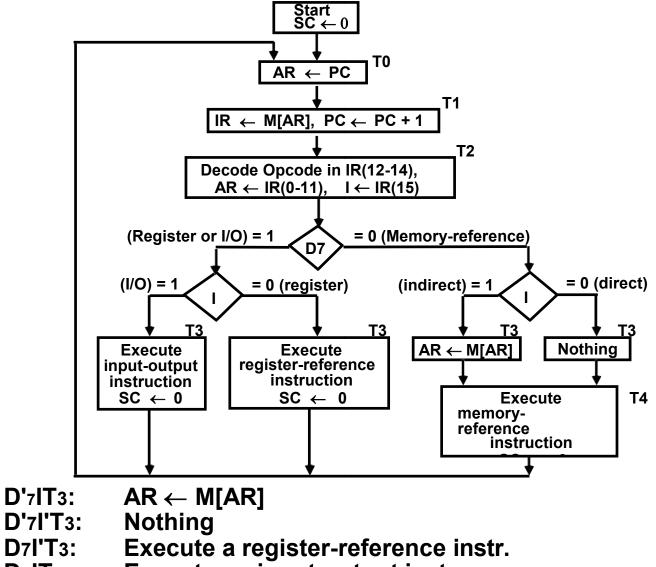

## INSTRUCTION CYCLE

- In Basic Computer, a machine instruction is executed in the following cycle:

- 1. Fetch an instruction from memory

- 2. Decode the instruction

- 3. Read the effective address from memory if the instruction has an indirect address

- 4. Execute the instruction

- After an instruction is executed, the cycle starts again at step 1, for the next instruction

- *Note*: Every different processor has its own (different) instruction cycle

Instruction Cycle

#### FETCH and DECODE

#### DETERMINE THE TYPE OF INSTRUCTION

D7IT3: Execute an input-output instr.

## REGISTER REFERENCE INSTRUCTIONS

**Register Reference Instructions are identified when**

- $D_7 = 1$ , I = 0

- Register Ref. Instr. is specified in  $b_0 \sim b_{11}$  of IR

- Execution starts with timing signal  $\rm T_3$

r = D<sub>7</sub> I'T<sub>3</sub> => Register Reference Instruction

B<sub>i</sub> = IR(i) , i=0,1,2,...,11

| CLA<br>CLE<br>CMA<br>CME<br>CIR<br>CIL<br>INC<br>SPA<br>SNA<br>SZA<br>SZE<br>HLT | $\begin{array}{c} r: \\ rB_{11}: \\ rB_{10}: \\ rB_{9}: \\ rB_{8}: \\ rB_{7}: \\ rB_{6}: \\ rB_{5}: \\ rB_{4}: \\ rB_{3}: \\ rB_{2}: \\ rB_{1}: \\ rB_{0}: \end{array}$ | $\begin{array}{c} SC \leftarrow 0 \\ AC \leftarrow 0 \\ E \leftarrow 0 \\ AC \leftarrow AC' \\ E \leftarrow E' \\ AC \leftarrow shr AC, AC(15) \leftarrow E, E \leftarrow AC(0) \\ AC \leftarrow shl AC, AC(0) \leftarrow E, E \leftarrow AC(15) \\ AC \leftarrow AC + 1 \\ if (AC(15) = 0) then (PC \leftarrow PC+1) \\ if (AC(15) = 1) then (PC \leftarrow PC+1) \\ if (AC = 0) then (PC \leftarrow PC+1) \\ if (E = 0) then (PC \leftarrow PC+1) \\ if (E = 0) then (PC \leftarrow PC+1) \\ S \leftarrow 0 (S  is a start-stop flip-flop) \end{array}$ |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

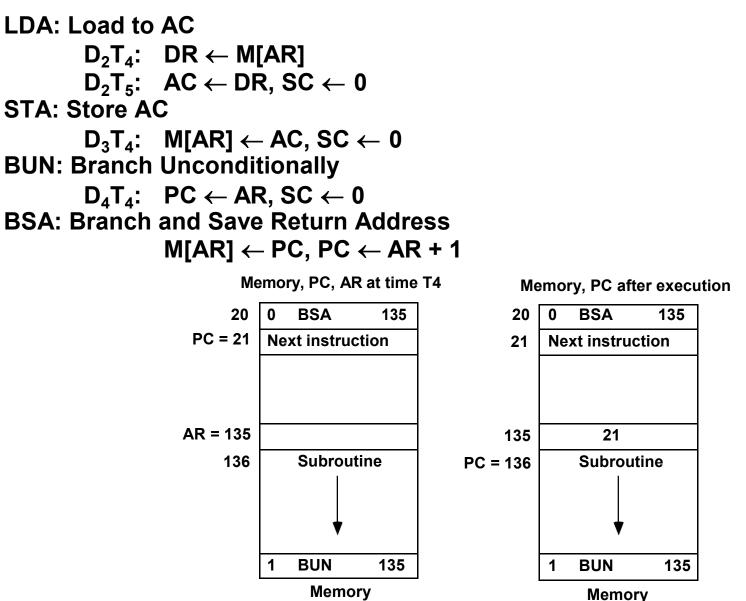

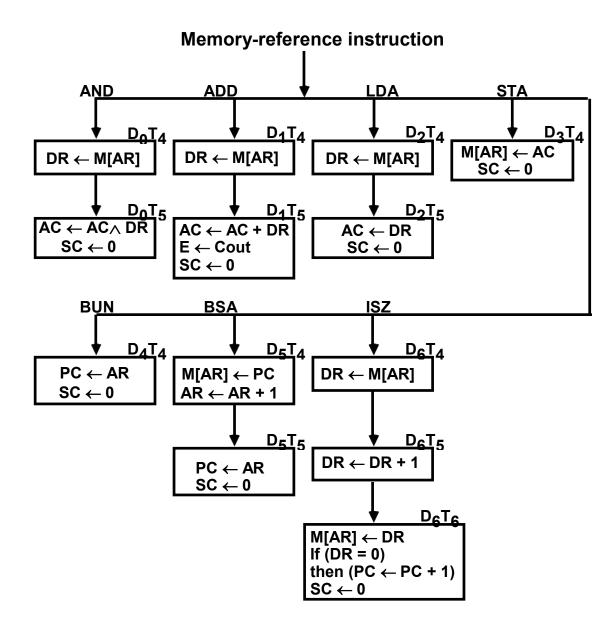

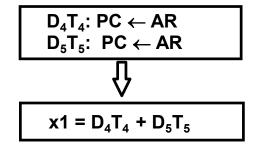

#### MEMORY REFERENCE INSTRUCTIONS

| Symbol | Operation<br>Decoder | Symbolic Description                                                        |

|--------|----------------------|-----------------------------------------------------------------------------|

| AND    | D <sub>0</sub>       | $AC \leftarrow AC \land M[AR]$                                              |

| ADD    | $\mathbf{D}_{1}$     | $AC \leftarrow AC + M[AR], E \leftarrow C_{out}$                            |

| LDA    | $D_2^{\cdot}$        | $AC \leftarrow M[AR]$                                                       |

| STA    | $\overline{D_3}$     | $M[AR] \leftarrow AC$                                                       |

| BUN    | $D_4$                | PĊ ← AR                                                                     |

| BSA    | $D_5$                | $M[AR] \leftarrow PC, PC \leftarrow AR + 1$                                 |

| ISZ    | $D_6$                | $M[AR] \leftarrow M[AR] + 1$ , if $M[AR] + 1 = 0$ then $PC \leftarrow PC+1$ |

- The effective address of the instruction is in AR and was placed there during timing signal  $T_2$  when I = 0, or during timing signal  $T_3$  when I = 1

- Memory cycle is assumed to be short enough to complete in a CPU cycle

- The execution of MR instruction starts with T<sub>4</sub>

## MEMORY REFERENCE INSTRUCTIONS

## MEMORY REFERENCE INSTRUCTIONS

**BSA**:

**ISZ: Increment and Skip-if-Zero**

$\begin{array}{lll} D_6T_4 & DR \leftarrow M[AR] \\ D_6T_5 & DR \leftarrow DR + 1 \\ D_6T_4 & M[AR] \leftarrow DR, \mbox{ if } (DR = 0) \mbox{ then } (PC \leftarrow PC + 1), \mbox{ } SC \leftarrow 0 \end{array}$

#### FLOWCHART FOR MEMORY REFERENCE INSTRUCTIONS

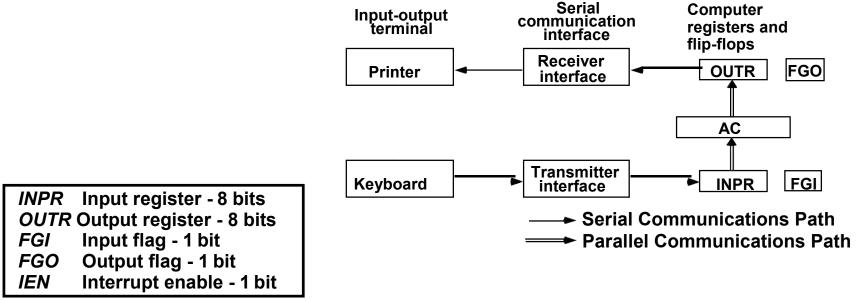

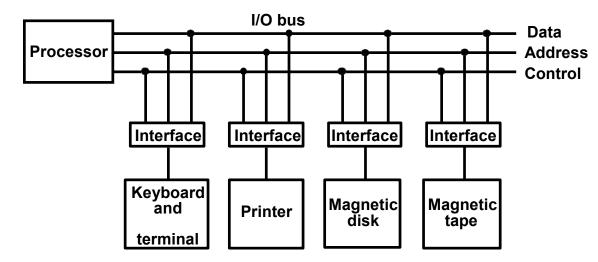

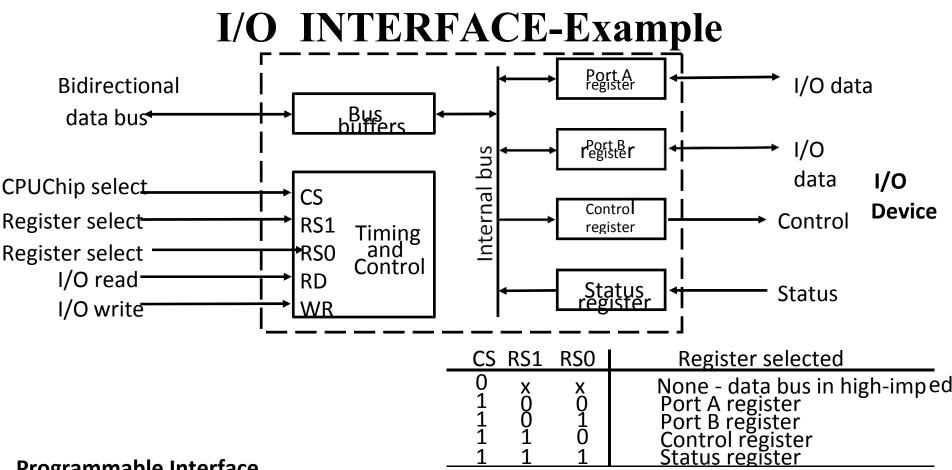

## INPUT-OUTPUT AND INTERRUPT

#### A Terminal with a keyboard and a Printer

#### Input-Output Configuration

- The terminal sends and receives serial information

- The serial info. from the keyboard is shifted into INPR

- The serial info. for the printer is stored in the OUTR

- INPR and OUTR communicate with the terminal serially and with the AC in parallel.

- The flags are needed to synchronize the timing difference between I/O device and the computer

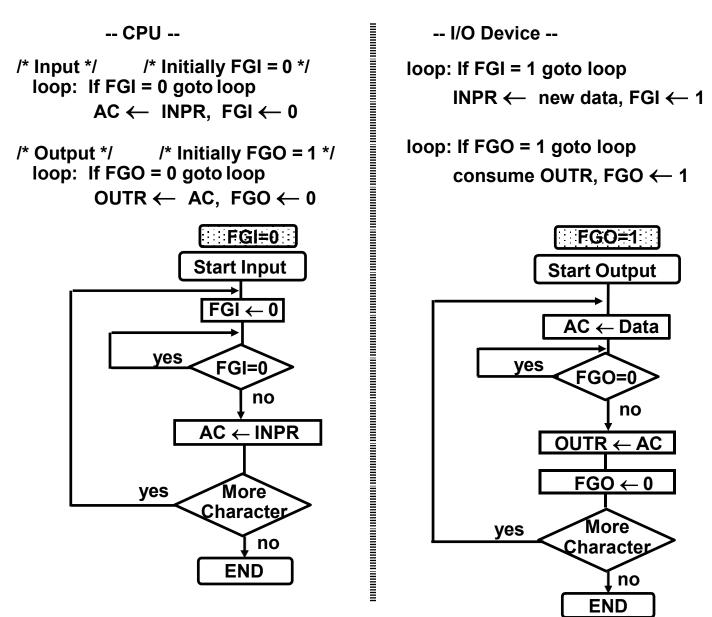

#### PROGRAM CONTROLLED DATA TRANSFER

## INPUT-OUTPUT INSTRUCTIONS

```

D<sub>7</sub>IT<sub>3</sub> = p

IR(i) = B<sub>i</sub>, i = 6, ..., 11

```

| INP<br>OUT<br>SKI<br>SKO<br>ION<br>IOF | - |  | Clear SC<br>Input char. to AC<br>Output char. from AC<br>Skip on input flag<br>Skip on output flag<br>Interrupt enable on<br>Interrupt enable off |

|----------------------------------------|---|--|---------------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------|---|--|---------------------------------------------------------------------------------------------------------------------------------------------------|

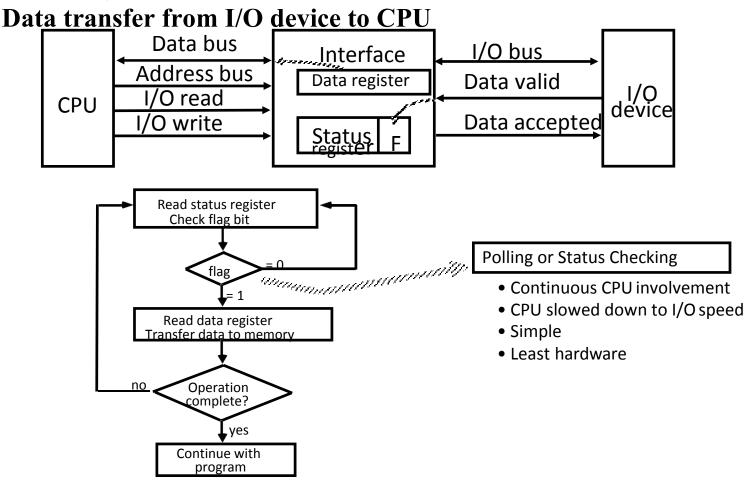

## PROGRAM-CONTROLLED INPUT/OUTPUT

#### Program-controlled I/O

- Continuous CPU involvement I/O takes valuable CPU time

- CPU slowed down to I/O speed

- Simple

- Least hardware

#### Input

| LOOP, | SKI | DEV  |

|-------|-----|------|

|       | BUN | LOOP |

|       | INP | DEV  |

#### Output

| LOOP, | LDA | DATA |

|-------|-----|------|

| LOP,  | SKO | DEV  |

|       | BUN | LOP  |

|       | OUT | DEV  |

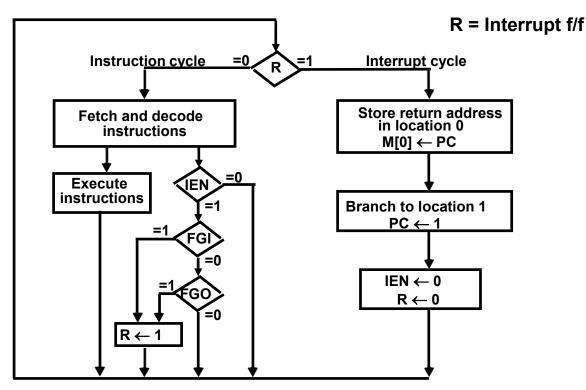

## INTERRUPT INITIATED INPUT/OUTPUT

- Open communication only when some data has to be passed --> interrupt.

- The I/O interface, instead of the CPU, monitors the I/O device.

- When the interface founds that the I/O device is ready for data transfer, it generates an interrupt request to the CPU

- Upon detecting an interrupt, the CPU stops momentarily the task it is doing, branches to the service routine to process the data transfer, and then returns to the task it was performing.

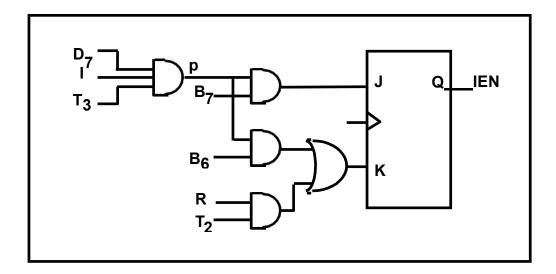

- \* IEN (Interrupt-enable flip-flop)

- can be set and cleared by instructions

- when cleared, the computer cannot be interrupted

## FLOWCHART FOR INTERRUPT CYCLE

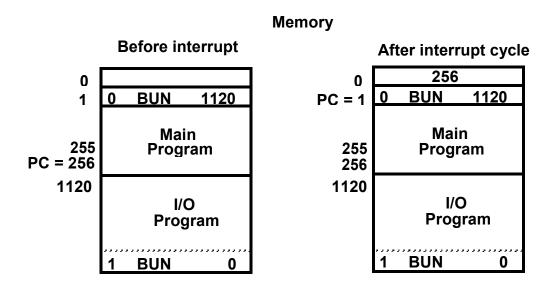

- The interrupt cycle is a HW implementation of a branch and save return address operation.

- At the beginning of the next instruction cycle, the instruction that is read from memory is in address 1.

- At memory address 1, the programmer must store a branch instruction that sends the control to an interrupt service routine

- The instruction that returns the control to the original program is "indirect BUN 0"

#### REGISTER TRANSFER OPERATIONS IN INTERRUPT CYCLE

Register Transfer Statements for Interrupt Cycle- R F/F  $\leftarrow$  1if IEN (FGI + FGO)T<sub>0</sub>'T<sub>1</sub>'T<sub>2</sub>' $\Leftrightarrow$  T<sub>0</sub>'T<sub>1</sub>'T<sub>2</sub>' (IEN)(FGI + FGO): R  $\leftarrow$  1

The fetch and decode phases of the instruction cycle must be modified → Replace T<sub>0</sub>, T<sub>1</sub>, T<sub>2</sub> with R'T<sub>0</sub>, R'T<sub>1</sub>, R'T<sub>2</sub>

The interrupt cycle :

$$RT_0$$

:  $AR \leftarrow 0$ ,  $TR \leftarrow PC$

$$RT_1$$

: M[AR]  $\leftarrow$  TR, PC  $\leftarrow$  0

$RT_2$ : PC  $\leftarrow$  PC + 1, IEN  $\leftarrow$  0, R  $\leftarrow$  0, SC  $\leftarrow$  0

#### FURTHER QUESTIONS ON INTERRUPT

How can the CPU recognize the device requesting an interrupt ?

Since different devices are likely to require different interrupt service routines, how can the CPU obtain the starting address of the appropriate routine in each case ?

Should any device be allowed to interrupt the CPU while another interrupt is being serviced ?

How can the situation be handled when two or more interrupt requests occur simultaneously ?

Description

#### Description

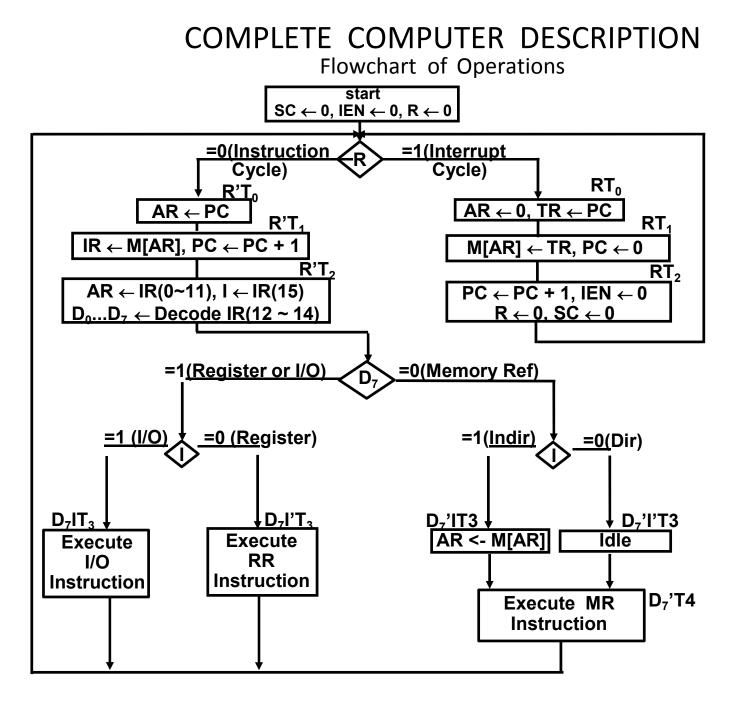

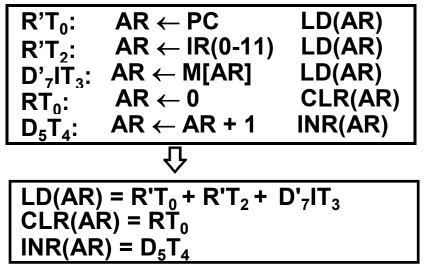

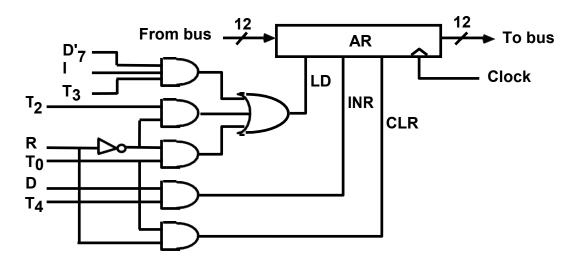

# COMPLETE COMPUTER DESCRIPTION

#### Microoperations

| Fetch        | R′T₀:                             | AR ← PC                                                                            |

|--------------|-----------------------------------|------------------------------------------------------------------------------------|

|              | R′T₁:                             | $IR \leftarrow M[AR], PC \leftarrow PC + 1$                                        |

| Decode       | R'T <sub>2</sub> :                | D0,, D7 ← Decode IR(12 ~ 14),                                                      |

|              | _                                 | $AR \leftarrow IR(0 \sim 11), I \leftarrow IR(15)$                                 |

| Indirect     | D <sub>7</sub> ′IT <sub>3</sub> : | $AR \leftarrow M[AR]$                                                              |

| Interrupt    |                                   |                                                                                    |

|              | EN)(FGI + FGO):                   | R ← 1                                                                              |

| 0120         | ÂRT₀:                             | $AR \leftarrow 0, TR \leftarrow PC$                                                |

|              | RT₁́:                             | $M[AR] \leftarrow TR, PC \leftarrow 0$                                             |

|              | $RT_2$ :                          | $PC \leftarrow PC + 1$ , IEN $\leftarrow 0$ , R $\leftarrow 0$ , SC $\leftarrow 0$ |

| Memory-Refer | ence                              |                                                                                    |

| AND          | $D_0T_4$ :                        | $DR \leftarrow M[AR]$                                                              |

|              | $D_0T_5$ :                        | $AC \leftarrow AC \land DR, SC \leftarrow 0$                                       |

| ADD          | D <sub>1</sub> T <sub>4</sub> :   | $DR \leftarrow M[AR]$                                                              |

|              | D <sub>1</sub> T <sub>5</sub> :   | $AC \leftarrow AC + DR, E \leftarrow C_{out}, SC \leftarrow 0$                     |

| LDA          | $D_2T_4$ :                        | $DR \leftarrow M[AR]$                                                              |

|              | $D_2T_5$ :                        | $AC \leftarrow DR, SC \leftarrow 0$                                                |

| STA          | $D_3T_4$ :                        | $M[AR] \leftarrow AC, SC \leftarrow 0$                                             |

| BUN          | $D_4 T_4$ :                       | $PC \leftarrow AR, SC \leftarrow 0$                                                |

| BSA          | $D_5T_4$ :                        | $M[AR] \leftarrow PC, AR \leftarrow AR + 1$                                        |

|              | $D_5T_5$ :                        | $PC \leftarrow AR, SC \leftarrow 0$                                                |

| ISZ          | D <sub>6</sub> T <sub>4</sub> :   | $DR \leftarrow M[AR]$                                                              |

|              | $D_6T_5$ :                        | DR ← DR + 1                                                                        |

|              | $D_6T_6$ :                        | M[AR] $\leftarrow$ DR, if(DR=0) then (PC $\leftarrow$ PC + 1),                     |

|              |                                   | SC ← 0                                                                             |

|              |                                   |                                                                                    |

# COMPLETE COMPUTER DESCRIPTION

Microoperations

| Register-Refer                                                                   | ence                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |