# Unit 1 NUMBER SYSTEMS

# Any number in one base system can be converted into another base system Types decimal to any base Any base to decimal Any base to Any base

### **Number Systems**

Decimal number:  $123.45 = 1.10^2 + 2.10^1 + 3.10^0 + 4.10^{-1} + 5.10^{-2}$ .

Base *b* number:  $N = a_{q-1}b^{q-1} + \dots + a_{q}b^{0} + \dots + a_{-q}b^{-p}$   $b > 1, \quad 0 <= a_i <= b-1$ Integer part:  $a_{q-1}a_{q-2} = a_0$ Fractional part:  $a_{-1}a_{-2} = a_{-p}$ Most significant digit:  $a_{q-1} = \dots$ Least significant digit:  $a_{-p}$

Binary number (b=2):  $1101.01 = 12^3 + 12^2 + 02^1 + 12^0 + 02^{-1} + 12^{-2}$

Representing number N in base b: (N)<sub>b</sub> · · · · ·

Complement of digit *a*: *a*' = (*b*-1)-*a* Decimal system: 9's complement of 3 = 9-3 = 6 Binary system: 1's complement of 1 = 1-1 = 0

## **Representation of Integers**

|      | Base |    |    |    |  |  |  |  |

|------|------|----|----|----|--|--|--|--|

| 2    | 4    | 8  | 10 | 12 |  |  |  |  |

| 0000 | 0    | 0  | 0  | 0  |  |  |  |  |

| 0001 | 1    | 1  | 1  | 1  |  |  |  |  |

| 0010 | 2    | 2  | 2  | 2  |  |  |  |  |

| 0011 | 3    | 3  | 3  | 3  |  |  |  |  |

| 0100 | 10   | 4  | 4  | 4  |  |  |  |  |

| 0101 | 11   | 5  | 5  | 5  |  |  |  |  |

| 0110 | 12   | 6  | 6  | 6  |  |  |  |  |

| 0111 | 13   | 7  | 7  | 7  |  |  |  |  |

| 1000 | 20   | 10 | 8  | 8  |  |  |  |  |

| 1001 | 21   | 11 | 9  | 9  |  |  |  |  |

| 1010 | 22   | 12 | 10 | α  |  |  |  |  |

| 1011 | 23   | 13 | 11 | β  |  |  |  |  |

| 1100 | 30   | 14 | 12 | 10 |  |  |  |  |

| 1101 | 31   | 15 | 13 | 11 |  |  |  |  |

| 1110 | 32   | 16 | 14 | 12 |  |  |  |  |

| 1111 | 33   | 17 | 15 | 13 |  |  |  |  |

#### **Base Conversions**

#### Example: Base 8 to base 10

$(432.2)_8 = 48^2 + 38^1 + 28^0 + 28^{-1} = (282.25)_{10}$

Example: Base 2 to base 10  $(1101.01)_2 = 12^3 + 12^2 + 02^1 + 12^0 + 02^{-1} + 12^{-2} = (13.25)_{10}$ Base  $b_1$  to  $b_2$ , where  $b_1 > b_2$ :

$$(N)_{b_1} = a_{q-1}b_2^{q-1} + a_{q-2}b_2^{q-2} + \dots + a_1b_2^1 + a_0b_2^0$$

$$\frac{(N)_{b_1}}{b_2} = \underbrace{a_{q-1}b_2^{q-2} + a_{q-2}b_2^{q-3} + \dots + a_1}_{Q_0} + \underbrace{a_0}_{D_2}$$

$$\left(\frac{Q_0}{b_2}\right)_{b_1} = \underbrace{a_{q-1}b_2^{q-3} + a_{q-2}b_2^{q-4} + \cdots}_{Q_1} + \frac{a_1}{b_2}$$

4

#### **Conversion of Bases (Contd.)**

Example: Convert (548)<sub>10</sub> to base 8

$$\begin{array}{c|c} Q_i & r_i \\ \hline 68 & 4 = a_0 \\ 8 & 4 = a_1 \\ 1 & 0 = a_2 \\ 1 = a_3 \end{array}$$

Thus,  $(548)_{10} = (1044)_8$

Example: Convert (345)<sub>10</sub> to base 6

$$\begin{array}{c|c} Q_i & r_i \\ \hline 57 & 3 = a_0 \\ 9 & 3 = a_1 \\ 1 & 3 = a_2 \\ & 1 = a_3 \end{array}$$

<sup>5</sup> Thus,  $(345)_{10} = (1333)_6$

#### **Conversions of fractional numbers**

Fractional number:

$$(N)_{b_1} = a_{-1}b_2^{-1} + a_{-2}b_2^{-2} + \dots + a_{-p}b_2^{-p}$$

$$b_2 \cdot (N)_{b_1} = a_{-1} + a_{-2}b_2^{-1} + \dots + a_{-p}b_2^{-p+1}$$

Example: Convert  $(0.3125)_{10}$  to base 8 0.3125 8 = 2.5000 hence  $a_{-1} = 2$ 0.5000 8 = 4.0000 hence  $a_{-2} = 4$

Thus,  $(0.3125)_{10} = (0.24)_8$

#### **Decimal to Binary**

#### Example: Convert (432.354)<sub>10</sub> to binary

~ I

| $Q_i$ | $r_i$     |                 |                          |

|-------|-----------|-----------------|--------------------------|

| 216   | $0 = a_0$ | 0.354 2 = 0.708 | hence $a_{-1} = 0$       |

| 108   | $0 = a_1$ | 0.708 2=1.416   | hence a <sub>-2</sub> =1 |

| 54    | $0 = a_2$ | 0.416 2 = 0.832 | hence a <sub>-3</sub> =0 |

| 27    | $0 = a_3$ | 0.832 2 = 1.664 | hence $a_4 = 1$          |

| 13    | $1 = a_4$ | 0.664 2 = 1.328 | hence $a_{-5} = 1$       |

| 6     | $1 = a_5$ | 0.328 2 = 0.656 | hence $a_{-6} = 0$       |

| 3     | $0 = a_6$ | 1.<br>1.        | a_7=1                    |

| 1     | $1 = a_7$ |                 | etc.                     |

|       | $1 = a_8$ |                 |                          |

Thus,  $(432.354)_{10} = (110110000.0101101...)_2$

#### **Octal to Binary Conversion**

Example: Convert  $(123.4)_8$  to binary  $(123.4)_8 = (001\ 010\ 011.100)_2$

Example: Convert  $(1010110.0101)_2$  to octal  $(1010110.0101)_2 = (001\ 010\ 110.010\ 100)_2 = (126.24)_8$

#### Complements

Complements arc used in digital computers to simplify the subtraction operation and for log- ical manipulation They are two types of complements 1) Diminished radix complement  $(r^{n} - 1)$ -N {r is the base of num system } 2) Radix Complement  $(r^{n} - 1) - N + 1$

#### (r-1)'s complement

- If the base = 10

- The 9's complement of 546700 is

999999 546700 = 453299.

- If the base = 2

- The 1's complement of 1011000 is 0100111.

#### r's complement

- the 10's complement of 012398 is 987602

- the 1's complement of 1101100 is 0010100

#### Subtraction using complements

Discard end carry for r's complement Using 10's complement subtract 72532 -3250.

M = 72532 10's complement of N = + 96750 Sum = 169282Discard end carry for 10's complement

Answer =

69282

# Subtraction using (r-1)'s complement

• X - Y = 1010100 - 1000011 X = 1010100 1's comp of Y = + 0111100 Sum = 1 0010000 Add End-around carry = + 1 1 X - Y = 0010001

| <b>Binary</b> | Codes |

|---------------|-------|

|---------------|-------|

| Decimal |   |    |          |   | r      | $w_4w$ | $_{3}w_{2}$ | $w_1$ |        |          |          |    |

|---------|---|----|----------|---|--------|--------|-------------|-------|--------|----------|----------|----|

| digit   | 8 | 4  | <b>2</b> | 1 | $^{2}$ | 4      | <b>2</b>    | 1     | 6      | <b>4</b> | <b>2</b> | -3 |

| 0       | 0 | 0  | 0        | 0 | 0      | 0      | 0           | 0     | 0      | 0        | 0        | 0  |

| 1       | 0 | 0  | 0        | 1 | 0      | 0      | 0           | 1     | 0      | 1        | 0        | 1  |

| $^{2}$  | 0 | 0  | 1        | 0 | 0      | 0      | 1           | 0     | 0      | 0        | 1        | 0  |

| 3       | 0 | 0  | 1        | 1 | 0      | 0      | 1           | 1     | 1      | 0        | 0        | 1  |

| 4       | 0 | 1  | 0        | 0 | 0      | 1      | 0           | 0     | 0      | 1        | 0        | 0  |

| 5       | 0 | 1  | 0        | 1 | 1      | 0      | 1           | 1     | 1      | 0        | 1        | 1  |

| 6       | 0 | 1  | 1        | 0 | 1      | 1      | 0           | 0     | 0      | 1        | 1        | 0  |

| 7       | 0 | 1  | 1        | 1 | 1      | 1      | 0           | 1     | 1      | 1        | 0        | 1  |

| 8       | 1 | 0  | 0        | 0 | 1      | 1      | 1           | 0     | 1      | 0        | 1        | 0  |

| 9       | 1 | 0  | 0        | 1 | 1      | 1      | 1           | 1     | 1      | 1        | 1        | 1  |

|         | L |    |          | 1 |        |        |             |       |        |          |          | 1  |

|         |   | BC | D        |   | 1      | Self   | -co         | mplem | enting | Cod      | es       |    |

Self-complementing code: Code word of 9's complement of N obtained by interchanging 1's and 0's in the code word of N

#### **Non Weighted Codes**

| Decimal<br>digit |   | Excoloring Excolorin | e <b>ss-</b> . | 3 |   | Cy | clic         |   |

|------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---|---|----|--------------|---|

| 0                | 0 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1              | 1 | 0 | 0  | 0            | 0 |

| 1                | 0 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0              | 0 | 0 | 0  | 0            | 1 |

| 2                | 0 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0              | 1 | 0 | 0  | 1            | 1 |

| 3                | 0 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1              | 0 | 0 | 0  | 1            | 0 |

| 4                | 0 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1              | 1 | 0 | 1  | 1            | 0 |

| 5                | 1 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0              | 0 | 1 | 1  | 1            | 0 |

| 6                | 1 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0              | 1 | 1 | 0  | 1            | 0 |

| 7                | 1 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1              | 0 | 1 | 0  | 0            | 0 |

| 8                | 1 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1              | 1 | 1 | 1  | 0            | 0 |

| 9                | 1 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0              | 0 | 0 | 1  | 0            | 0 |

|                  | L |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |   | L |    |              |   |

|                  |   | Add 3 to<br>BCD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |   |   |    | sive<br>n on |   |

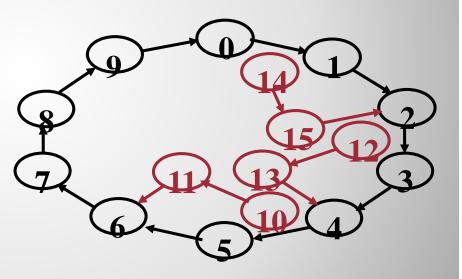

## Gray Code(Unit distance Code)

| Decimal |       | $G_{1}$ | ray   |       |       | Bir   | nary  |       |

|---------|-------|---------|-------|-------|-------|-------|-------|-------|

| number  | $g_3$ | $g_2$   | $g_1$ | $g_0$ | $b_3$ | $b_2$ | $b_1$ | $b_0$ |

| 0       | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0     |

| 1       | 0     | 0       | 0     | 1     | 0     | 0     | 0     | 1     |

| $^{2}$  | 0     | 0       | 1     | 1     | 0     | 0     | 1     | 0     |

| 3       | 0     | 0       | 1     | 0     | 0     | 0     | 1     | 1     |

| 4       | 0     | 1       | 1     | 0     | 0     | 1     | 0     | 0     |

| 5       | 0     | 1       | 1     | 1     | 0     | 1     | 0     | 1     |

| 6       | 0     | 1       | 0     | 1     | 0     | 1     | 1     | 0     |

| 7       | 0     | 1       | 0     | 0     | 0     | 1     | 1     | 1     |

| 8       | 1     | 1       | 0     | 0     | 1     | 0     | 0     | 0     |

| 9       | 1     | 1       | 0     | 1     | 1     | 0     | 0     | 1     |

| 10      | 1     | 1       | 1     | 1     | 1     | 0     | 1     | Ο     |

| 11      | 1     | 1       | 1     | 0     | 1     | Ο     | 1     | 1     |

| 12      | 1     | 0       | 1     | 0     | 1     | 1     | 0     | 0     |

| 13      | 1     | 0       | 1     | 1     | 1     | 1     | 0     | 1     |

| 14      | 1     | 0       | 0     | 1     | 1     | 1     | 1     | 0     |

| 15      | 1     | 0       | 0     | 0     | 1     | 1     | 1     | 1     |

#### **Binary to Gray Conversion** Example: **Binary:** $b_4$ $b_5$ $b_2$ $b_3$ b1 bo Đ Gray: $g_3$ $g_2$ $g_5$ $g_4$ $g_1$ $g_0$

Gray-to-binary: *b<sub>i</sub>* = *g<sub>i</sub>* if no. of 1's preceding *g<sub>i</sub>* is even *b<sub>i</sub>* = *g<sub>i</sub>*' if no. of 1's preceding *g<sub>i</sub>* is odd

#### Mirror Image Representation in Gray Code

| 00 | 0 | 00 | 0 | 000 |

|----|---|----|---|-----|

| 01 | 0 | 01 | 0 | 001 |

| 11 | 0 | 11 | 0 | 011 |

| 10 | 0 | 10 | 0 | 010 |

| -  | 1 | 10 | 0 | 110 |

|    | 1 | 11 | 0 | 111 |

|    | 1 | 01 | 0 | 101 |

|    | 1 | 00 | 0 | 100 |

|    | _ |    | 1 | 100 |

|    |   |    | 1 | 101 |

|    |   |    | 1 | 111 |

|    |   |    | 1 | 110 |

|    |   |    | 1 | 010 |

|    |   |    | 1 | 011 |

|    |   |    | 1 | 001 |

|    |   |    | 1 | 000 |

#### **Error Detection and Correction**

- No communication channel or storage device is completely error-free

- As the number of bits per area or the transmission rate increases, more errors occur.

- Impossible to detect or correct 100% of the errors

#### **Types of Error Detection**

- 3 Types of Error Detection/Correction Methods

- Cyclic Redundancy Check (CRC)

- Hamming Codes

- Reed-Solomon (RS)

```

10011001011 = 1001100 + 1011

Code word information error-checking bits/

bits parity bits/

syndrome/

redundant bits

```

#### **Hamming Codes**

- One of the most effective codes for error-recovery

Used in situations where random errors are likely to occur

- 3. Error detection and correction increases in proportion to the number of parity bits (error-checking bits) added to the end of the information bits code word = information bits + parity bits Hamming distance: the number of bit positions in which two code words differ. 10001001

Minimum Hamming distance or D(min) : determines its error detecting and correcting capability.

4. Hamming codes can always detect D(min) - 1 errors, but can only correct half of those errors.

#### **Hamming Codes**

EX. Data Bits 00 01 10 11

Parity

Code

Bit

Word

0

000

1

011

1

101

0

110

#### 000\* 100 001 101\* 010 110\* 011\* 111

- Single parity bit can only detect error, not correct it

- Error-correcting codes require more than a single parity bit

- EX. 00000 01011

- 10110

- 1 1 1 0 1

Minimum Hamming distance = 3 Can detect up to 2 errors and correct 1 error

#### **Cyclic Redundancy Check**

- 1. Let the information byte F = 1001011

- 2. The sender and receiver agree on an arbitrary binary pattern P. Let P = 1011.

- 3. Shift F to the left by 1 less than the number of bits in P. Now, F = 1001011000.

- 4. Let F be the dividend and P be the divisor. Perform "modulo 2 division".

- 5. After performing the division, we ignore the quotient. We got 100 for the remainder, which becomes the actual CRC checksum.

- 6. Add the remainder to F, giving the message M:

1001011 + 100 = 1001011100 = M

#### **Calculating and Using CRCs**

7. M is decoded and checked by the message receiver using the reverse process.

#### 1010100

$\begin{array}{c|cccc} 1011 & | & 1001011100 \\ & \underline{1011} \\ & 001001 \\ & 1001 \\ & 0010 \\ & 001011 \\ & \underline{1011} \\ & 0000 \end{array}$

← Remainder

#### **Canonical and Standard Forms**

- We need to consider formal techniques for the simplification of Boolean functions.

- Identical functions will have exactly the same canonical form.

- Minterms and Maxterms

- Sum-of-Minterms and Product-of- Maxterms

- Product and Sum terms

- Sum-of-Products (SOP) and Product-of-Sums (POS)

#### Definitions

- Literal: A variable or its complement

- Product term: literals connected by

- Sum term: literals connected by +

- Minterm: a product term in which all the variables appear exactly once, either complemented or uncomplemented

- Maxterm: a sum term in which all the variables appear exactly once, either complemented or uncomplemented

#### Truth Table notation for Minterms and Maxterms

- Minterms and X Y Z

Maxterms are easy 0 0 0

to denote using a 0 0 1

truth table. 0 1 0

- Example:

Assume 3 variables

x.v.z

(order is fixed)

|     | × | У | Z | Minterm                | Maxterm                  |

|-----|---|---|---|------------------------|--------------------------|

| şγ  | 0 | 0 | 0 | $x'y'z' = m_0$         | $x+y+z = M_0$            |

|     | 0 | 0 | 1 | $x'y'z = m_1$          | x+y+z' = M1              |

|     | 0 | 1 | 0 | x'yz' = m <sub>2</sub> | x+y'+z = M <sub>2</sub>  |

|     | 0 | 1 | 1 | x'yz = m <sub>3</sub>  | x+y'+z'= M <sub>3</sub>  |

| ŧ\$ | 1 | 0 | 0 | $xy'z' = m_4$          | x'+y+z = M4              |

| ſ   | 1 | 0 | 1 | $xy'z = m_5$           | x'+y+z' = M <sub>5</sub> |

| T   | 1 | 1 | 0 | xyz' = m <sub>6</sub>  | x'+y'+z = M <sub>6</sub> |

| t   | 1 | 1 | 1 | xyz = m7               | x'+y'+z' = M7            |

#### **Canonical Forms (Unique)**

- Any Boolean function F() can be expressed as a *unique* sum of minterms and a unique product of maxterms (under a fixed variable ordering).

- In other words, every function F() has two canonical forms:

- Canonical Sum-Of-Products (sum of minterms)

Canonical Product-Of-Sums (product of maxterms)

#### **Canonical Forms (cont.)**

- Canonical Sum-Of-Products: The minterms included are those m<sub>j</sub> such that F() = 1 in row j of the truth table for F().

- Canonical Product-Of-Sums: The maxterms included are those M<sub>j</sub> such that F() = 0 in row j of the truth table for F().

#### Example

- Truth table for f<sub>1</sub>(a,b,c) at right

- The canonical sum-of-products form for f<sub>1</sub> is

$f_1(a,b,c) = m_1 + m_2 + m_4 + m_6$ = a'b'c + a'bc' + ab'c' + abc'

The canonical product-of-sums form for f<sub>1</sub> is f<sub>1</sub>(a,b,c) = M<sub>0</sub> • M<sub>3</sub> • M<sub>5</sub> • M<sub>7</sub>

= (a+b+c)•(a+b'+c')•

(a'+b+c')•(a'+b'+c').

Observe that: m<sub>j</sub> = M<sub>j</sub><sup>2</sup>

a 0 O n Ο O O n O n

#### **Conversion Between Canonical Forms**

- Replace Σ with Π (or vice versa) and replace those j's that appeared in the original form with those that do not.

Example: f<sub>1</sub>(a,b,c) = a'b'c + a'bc' + ab'c' + abc'

- $= m_1 + m_2 + m_4 + m_6$ =  $\Sigma(1,2,4,6)$ =  $\Pi(0,3,5,7)$

$(a+b+c)\bullet(a+b'+c')\bullet(a'+b+c')\bullet(a'+b'+c')$

# Conversion of SOP from standard to canonical form

- Expand non-canonical terms by inserting equivalent of 1 in each missing variable x: (x + x') = 1

- Remove duplicate minterms

- $f_1(a,b,c) = a'b'c + bc' + ac'$

- = a'b'c + (a+a')bc' + a(b+b')c'= a'b'c + abc' + a'bc' + abc' +

ab'c'

= a'b'c + abc' + a'bc + ab'c'

#### Conversion of POS from standard to canonical form

- Expand noncanonical terms by adding 0 in terms of missing variables (*e.g.*, xx' = 0) and using the distributive law

- Remove duplicate maxterms

- $f_1(a,b,c) = (a+b+c) \cdot (b'+c') \cdot (a'+c')$ =  $(a+b+c) \cdot (aa'+b'+c') \cdot (a'+bb'+c')$ =  $(a+b+c) \cdot (a+b'+c') \cdot (a'+b'+c') \cdot (a'+b+c') \cdot (a'+b+c') \cdot (a'+b'+c')$

(a+b+c)•(a+b'+c')•(a'+b'+c')•(a'+b+c')

# **Boolean Algebra and Basic Gates**

### **LOGIC GATES**

**Formal logic**: In formal logic, a statement (proposition) is a declarative sentence that is either

true(1) or false (0).

It is easier to communicate with computers using formal logic.

Boolean variable: Takes only two values – either

true (1) or false (0).

They are used as basic units of formal logic.

### Boolean function and logic diagram

Boolean function: Mapping from Boolean variables to a Boolean value.

#### • Truth table:

- Represents relationship between a Boolean function and its binary variables.

- It enumerates all possible combinations of arguments and the corresponding function values.

### Boolean function and logic diagram

- **Boolean algebra**: Deals with binary variables and logic operations operating on those variables.

- Logic diagram: Composed of graphic symbols for logic gates. A simple circuit sketch that represents inputs and outputs of Boolean functions.

Refer to the hardware to implement Boolean operators.

#### The most basic gates are

| Name     | Graphic<br>symbol | Algebraic<br>function | Truth<br>table                                   |                             |

|----------|-------------------|-----------------------|--------------------------------------------------|-----------------------------|

| Inverter | а — Субан х       | x = A'                | A x<br>0 1<br>1 0                                | -                           |

| AND      | А —<br>В — — х    | x = AB                | A B x<br>0 0 0<br>0 1 0<br>1 0 0<br>1 1 1        | True if both are true.      |

| OR       | A<br>B<br>X       | x = A + B             | <u>A B x</u><br>0 0 0<br>0 1 1<br>1 0 1<br>1 1 1 | True if either one is true. |

### **Boolean function and truth table**

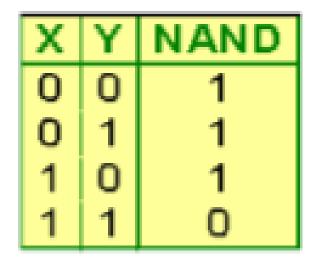

| • | Other common<br>Name  | gates include:<br>Graphic<br>symbol | Algebraic<br>function    | Truth<br>table                                   |                                         |

|---|-----------------------|-------------------------------------|--------------------------|--------------------------------------------------|-----------------------------------------|

|   | Exclusive-OR<br>(XOR) |                                     | x = A ⊕ B<br>= A'B + AB' | ABX<br>000<br>011<br>101<br>101                  | Parity check: True if only one is true. |

|   | NAND                  | А                                   | x = (AB)'                | <u>A B x</u><br>0 0 1<br>0 1 1<br>1 0 1<br>1 1 0 | Inversion of AND.                       |

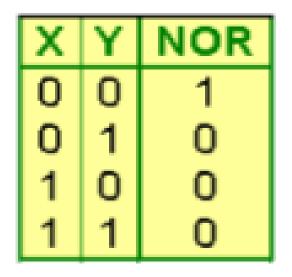

|   | NOR                   |                                     | x = A + B                | ABX<br>001<br>010<br>100<br>100                  | Inversion of OR.                        |

### BASIC IDENTITIES OF BOOLEAN ALGEBRA

Postulate 1 (Definition): A Boolean algebra is a closed algebraic system containing a set K of two or more elements and the two operators · and + which refer to logical AND and logical OR

#### Basic Identities of Boolean Algebra (Existence of 1 and 0 element)

$$(1) x + 0 = x$$

$$(2) x \cdot 0 = 0$$

$$(3) x + 1 = 1$$

$$(4) x \cdot 1 = 1$$

$$(5) x + x = x$$

$$(6) x \cdot x = x$$

$$(7) x + x' = x$$

$$(8) x \cdot x' = 0$$

### **Basic Identities of Boolean Algebra (Commutatively):**

$$(9) x + y = y + x$$

$$(10) xy = yx$$

$$(11) x + (y + z) = (x + y) + z$$

$$(12) x (yz) = (xy) z$$

$$(13) x (y + z) = xy + xz$$

$$(14) x + yz = (x + y)(x + z)$$

$$(15) (x + y)' = x' y'$$

$$(16) (xy)' = x' + y'$$

$$(17) (x')' = x$$

# Function Minimization using Boolean Algebra

#### • Examples:

(a)

$$a + ab = a(1+b)=a$$

(b)

$$a(a + b) = a.a + ab = a + ab = a(1+b) = a.$$

(c)

$$a + a'b = (a + a')(a + b) = 1(a + b) = a+b$$

(d)

$$a(a' + b) = a. a' + ab = 0 + ab = ab$$

### **DeMorgan's Theorem**

(a) (a + b)' = a'b'(b) (ab)' = a' + b'

Generalized DeMorgan's Theorem (a) (a + b + ... z)' = a'b' ... z'(b) (a.b ... z)' = a' + b' + ... z'

### **DeMorgan's Theorem**

- F = ab + c'd'

- F' = ??

- F = ab + c'd' + b'd

F' = ??

### More DeMorgan's example

Show that: (a(b + z(x + a')))' = a' + b'(z' + x')

$$(a(b + z(x + a')))' = a' + (b + z(x + a'))'$$

= a' + b' (z(x + a'))'

= a' + b' (z' + (x + a')')

= a' + b' (z' + x'(a')')

= a' + b' (z' + x'a)

= a' + b' (z' + x'a)

= a' + b' x' + b' z'

= (a' + b'x')(a + a') + b' z'

= a' + b'x' + b' z'

= a' + b' (z' + x')

### **Two Level implantation**

- NAND-AND

- AND-NOR

- NOR-OR

- OR-NAND

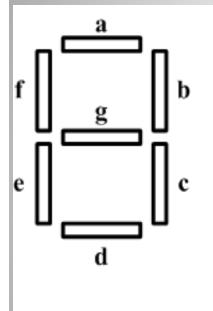

### NAND-AND

#### **AND-NOR functions:**

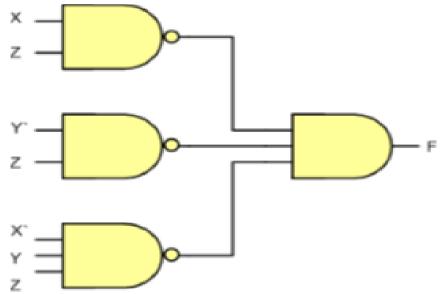

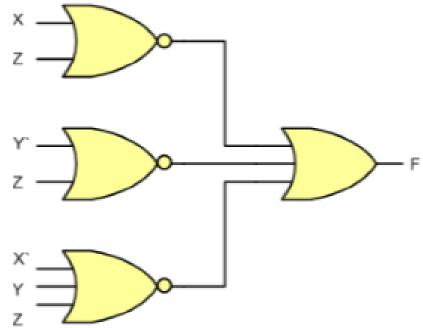

**Example 3:** Implement the following function  $F = \overline{XZ + \overline{Y}Z + \overline{X}YZ}$  or

$\overline{F} = XZ + \overline{Y}Z + \overline{X}YZ$

Since **F'** is in SOP form, it can be implemented by using NAND-NAND circuit. By complementing the output we can get **F**, or by using *NAND-AND* circuit as shown in the figure.

# It can also be implemented using AND-NOR circuit as it is equivalent to NAND- AND circuit

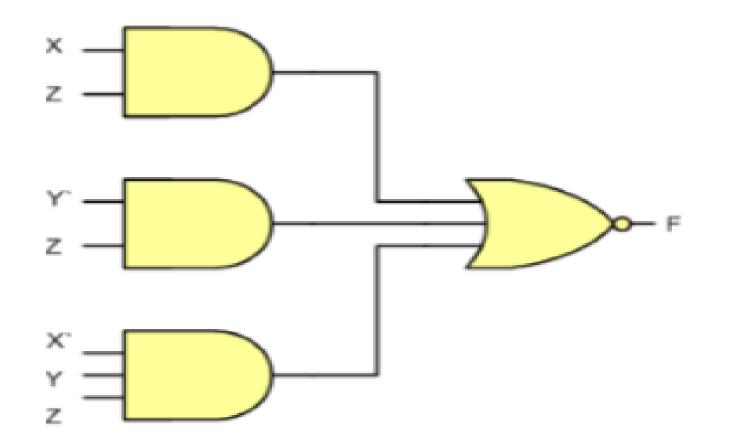

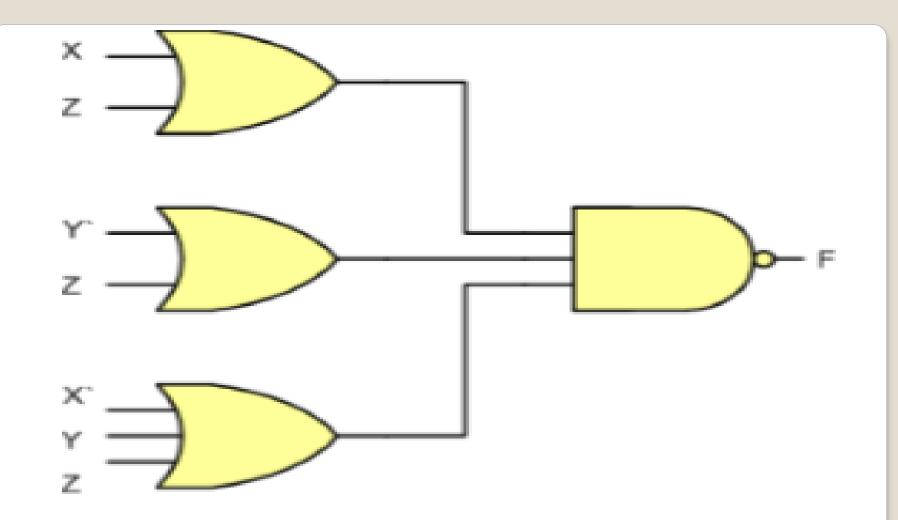

#### **OR-NAND functions: Example 4:** Implement the following function $F = \overline{(X+Z).(\overline{Y}+Z).(\overline{X}+Y+Z)}$ or $\overline{F} = (X+Z)(\overline{Y}+Z)(\overline{X}+Y+Z)$

Since **F**' is in POS form, it can be implemented by using NOR-NOR circuit. By complementing the output we can get **F**, or by using *NOR-OR* circuit as shown in the figure.

It can also be implemented using OR-NAND circuit as it is equivalent to NOR-OR circuit

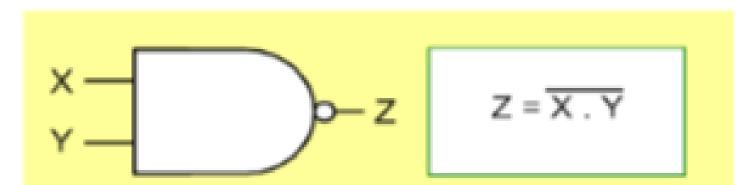

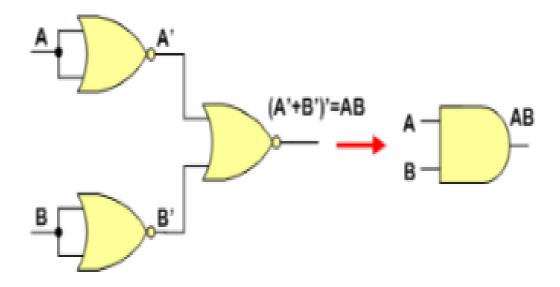

### **Universal Gates**

- The objectives of this lesson are to learn about:

- 1. Universal gates NAND and NOR.

- 2. How to implement NOT, AND, and OR gate using NAND gates only.

- 3. How to implement NOT, AND, and OR gate using NOR gates only.

- 4. Equivalent gates.

### **NAND GATE**

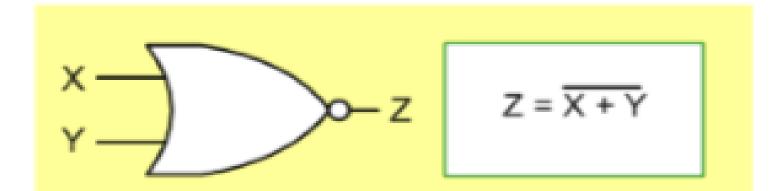

#### **NOR GATE**

1. All NAND input pins connect to the input signal A gives an output A<sup>2</sup>.

2. One NAND input pin is connected to the input signal **A** while all other input pins are connected to logic **1**. The output will be **A**<sup>2</sup>.

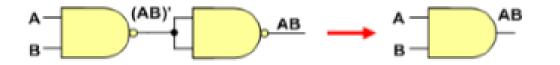

#### Implementing AND Using only NAND Gates

An AND gate can be replaced by NAND gates as shown in the figure (The AND is replaced by a NAND gate with its output complemented by a NAND gate inverter).

## NAND AS A UNIVERSAL GATE

#### Implementing OR Using only NAND Gates

An OR gate can be replaced by NAND gates as shown in the figure (The OR gate is replaced by a NAND gate with all its inputs complemented by NAND gate inverters).

Thus, the NAND gate is a universal gate since it can implement the AND, OR and NOT functions.

1. All NOR input pins connect to the input signal A gives an output A'.

One NOR input pin is connected to the input signal A while all other input pins are connected to logic 0. The output will be A<sup>2</sup>.

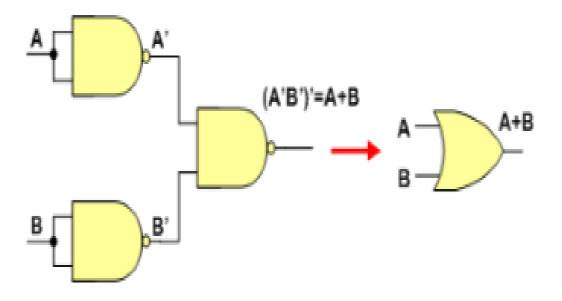

#### Implementing OR Using only NOR Gates

An OR gate can be replaced by NOR gates as shown in the figure (The OR is replaced by a NOR gate with its output complemented by a NOR gate inverter)

### **NOR AS A UNIVERSAL GATE**

#### Implementing AND Using only NOR Gates

An AND gate can be replaced by NOR gates as shown in the figure (The AND gate is replaced by a NOR gate with all its inputs complemented by NOR gate inverters)

Thus, the NOR gate is a universal gate since it can implement the AND, OR and NOT functions.

# UNIT 2

# Gate Level Minimization of Logic Circuits

### **Combinational Logic Design**

#### A process with 5 steps

- Specification

- Formulation

- Optimization

- Technology mapping

- Verification

- 1<sup>st</sup> three steps and last best illustrated by example

### **Functional Blocks**

- Fundamental circuits that are the base building blocks of most larger digital circuits

- They are reusable and are common to many systems.

- Examples of functional logic circuits

- –Decoders

- –Encoders

- -Code converters

- Multiplexers

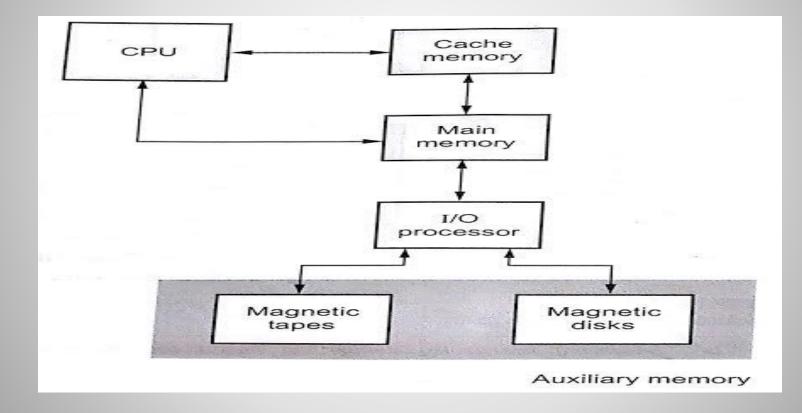

### Where they are used

- Multiplexers

- Selectors for routing data to the processor, memory, I/O

- Multiplexers route the data to the correct bus or port.

- Decoders

- are used for selecting things like a bank of memory and then the address within the bank. This is also the function needed to 'decode' the instruction to determine the operation to perform.

- Encoders

are used in various components such as keyboards.

#### **BCD-to-Excess-3 Code converter**

BCD is a code for the decimal digits 0-9

Excess-3 is also a code for the decimal

| Decimal<br>Digit | Input<br>BCD | Output<br>Excess-3 |

|------------------|--------------|--------------------|

| 0                | 0 0 0 0      | 0011               |

| 1                | 0001         | 0100               |

| 2                | 0010         | 0101               |

| 3                | 0011         | 0 1 1 0            |

| 4                | 0100         | 0111               |

| 5                | 0101         | 1000               |

| 6                | 0 1 1 0      | 1001               |

| 7                | 0111         | 1010               |

| 8                | 1000         | 1011               |

| 9                | 1001         | 1100               |

digits

### **Specification of BCD-to-Excess3**

- Inputs: a BCD input, A,B,C,D with A as the most significant bit and D as the least significant bit.

- Outputs: an Excess-3 output W,X,Y,Z that corresponds to the BCD input.

- Internal operation circuit to do the conversion in combinational logic.

### **Formulation of BCD-to-Excess-3**

- Excess-3 code is easily formed by adding a binary 3 to the binary or BCD for the digit.

- There are 16 possible inputs for both BCD and Excess-3.

- It can be assumed that only valid BCD inputs will appear so the six combinations not used can be treated as don't cares.

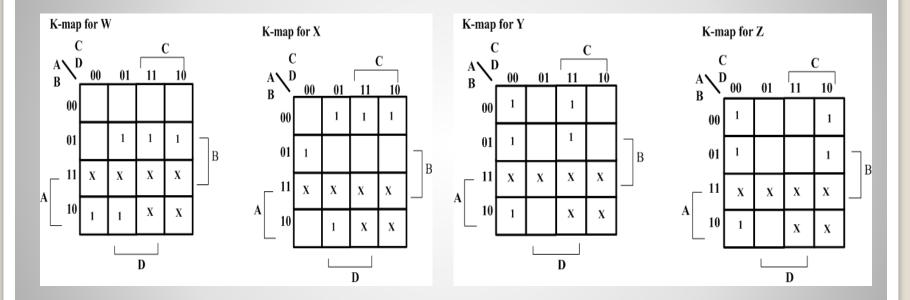

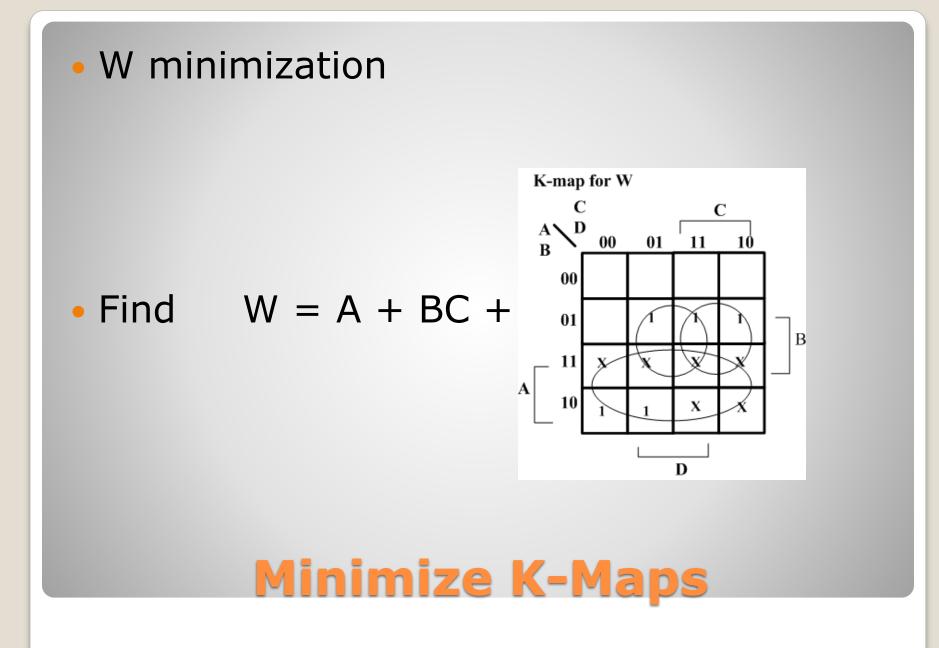

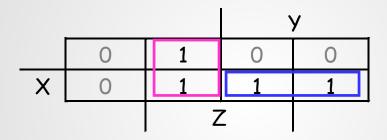

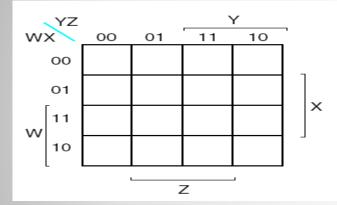

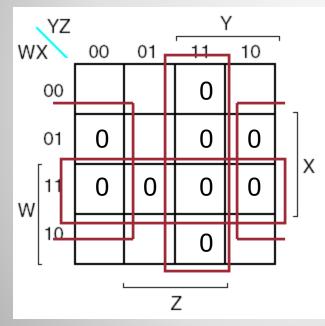

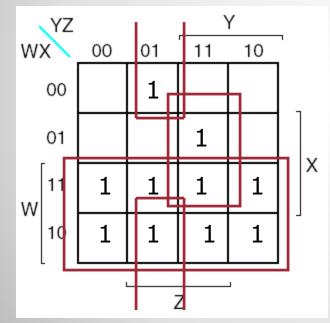

### **Optimization – BCD-to-Excess-3**

Lay out K-maps for each output, W X Y Z

A step in the digital circuit design process.

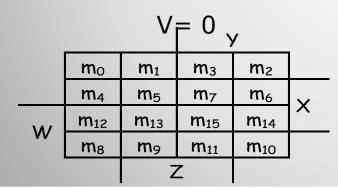

### • W(A,B,C,D) = $\Sigma m(5,6,7,8,9)$ +d(10,11,12,13,14,15)• $X(A,B,C,D) = \Sigma m(1,2,3,4,9)$ +d(10,11,12,13,14,15)• $Y(A,B,C,D) = \Sigma m(0,3,4,7,8)$ +d(10,11,12,13,14,15)• $Z(A,B,C,D) = \Sigma m(0,2,4,6,8)$ +d(10,11,12,13,14,15)

### **Expressions for W X Y Z**

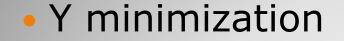

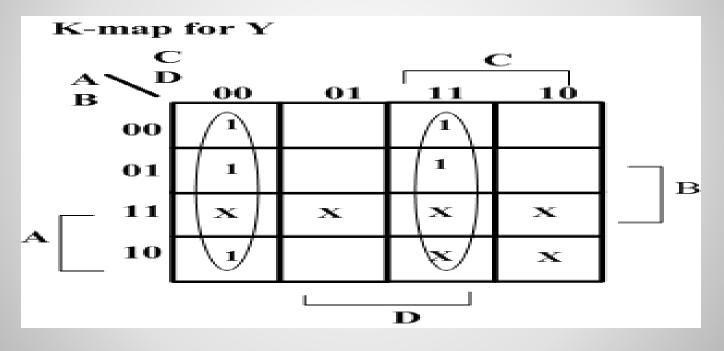

### **Minimize K-Maps**

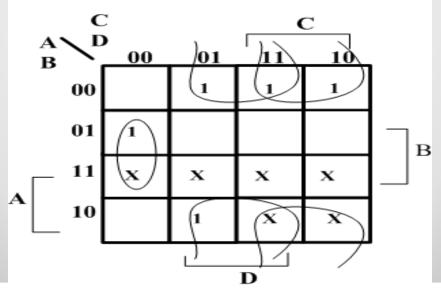

#### X minimization

#### • Find X = BC'D' + B'C + B'D

#### K-map for X

#### • Find Y = CD + C'D'

#### **Minimize K-Maps**

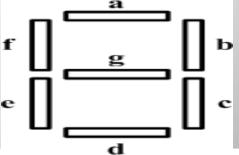

#### **BCD-to-Seven-Segment Decoder**

#### Specification

- Digital readouts on many digital products often use LED seven-segment displays.

- Each digit is created by lighting the appropriate segments. The segments are labeled a,b,c,d,e,f,g

- The decoder takes a BCD input and outputs the correct code for the seven-segment display.

## Specification

- Input: A 4-bit binary value that is a BCD coded input.

- Outputs: 7 bits, a through g for each of the segments of the display.

- Operation: Decode the input to activate the correct segments.

#### Construct a truth table

| Decim<br>Digit | al    | Input<br>BCD |     | Seven-Segmer<br>Decoder Outp<br>a b c d e f g |   |   |   |   |   | ł |   |

|----------------|-------|--------------|-----|-----------------------------------------------|---|---|---|---|---|---|---|

| 0              | 0     | 0            | 0   | 0                                             | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1              | 0     | 0            | 0   | 1                                             | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 2              | 0     | 0            | 1   | 0                                             | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 3              | 0     | 0            | 1   | 1                                             | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 4              | 0     | 1            | 0   | 0                                             | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 5              | 0     | 1            | 0   | 1                                             | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6              | 0     | 1            | 1   | 0                                             | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 7              | 0     | 1            | 1   | 1                                             | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 8              | 1     | 0            | 0   | 0                                             | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9              | 1     | 0            | 0   | 1                                             | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| A11            | other | ir           | ıpι | ıts                                           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

## **Formulation**

### Optimization

Create a K-map for each output and get

- $\circ A = A'C + A'BD + B'C'D' + AB'C'$

- B = A'B' + A'C'D' + A'CD + AB'C'

- $\circ C = A'B + A'D + B'C'D' + AB'C'$

- D = A'CD' + A'B'C + B'C'D' + AB'C' + A'BC'D

- E = A'CD' + B'C'D'

- F = A'BC' + A'C'D' + A'BD' + AB'C'

- G = A'CD' + A'B'C + A'BC' + AB'C'

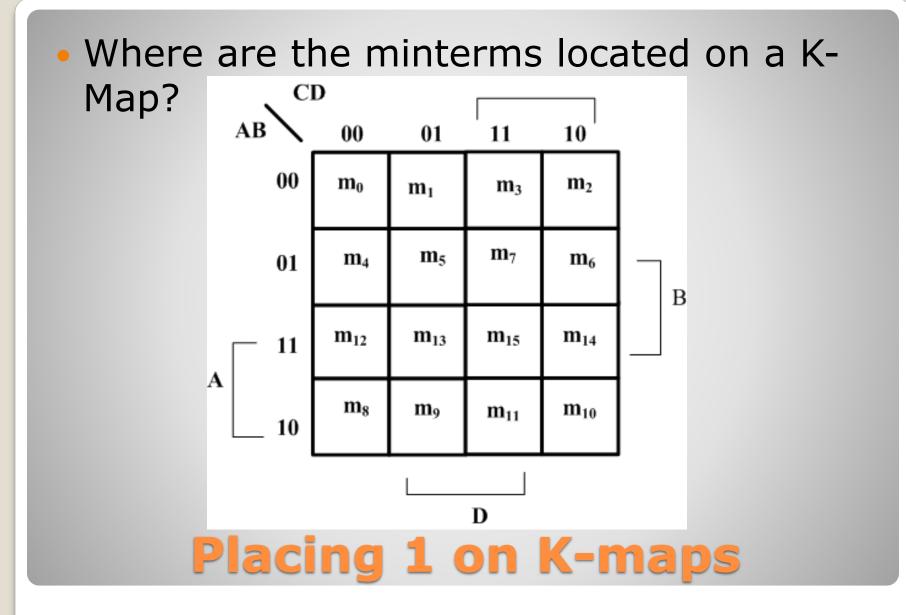

# Karnaugh Maps for Simplification

## **Karnaugh Maps**

- Boolean algebra helps us simplify expressions and circuits

- Karnaugh Map: A graphical technique for simplifying a Boolean expression into either form:

- minimal sum of products (MSP)

- minimal product of sums (MPS)

- Goal of the simplification.

- There are a minimal number of product/sum terms

- Each term has a minimal number of literals

- Circuit-wise, this leads to a minimal two-level implementation

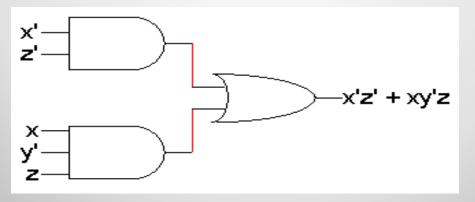

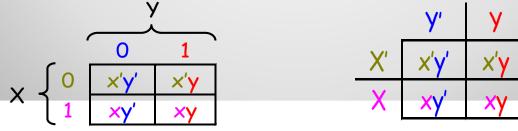

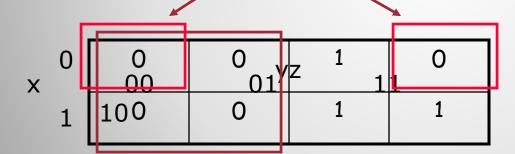

# **Re-arranging the Truth Table**

A two-variable function has four possible minterms. We can re-arrange these minterms into a Karnaugh map

- Now we can easily see which minterms contain common literals

- Minterms on the left and right sides contain y' and y respectively

- Minterms in the top and bottom rows contain x' and x respectively

# **Karnaugh Map Simplifications**

- Imagine a two-variable sum of minterms:

- x'y' + x'y

Both of these minterms appear in the top row of a Karnaugh map, which means that they both contain the literal x'

What happens if you simplify this expression using Boolean algebra?

## **More Two-Variable Examples**

х'y

Х

x'ν

- Another example expression is x'y + xy

- Both minterms appear in the right side, where y is uncomplemented

- Thus, we can reduce x'y + xy to just y

- We have x'y' + x'y in the top row, corresponding to x'

- There's also x'y + xy in the right side, corresponding to y

- This whole expression can be reduced to x' + y

У

x'y'

X\

Х

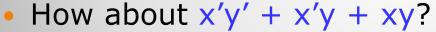

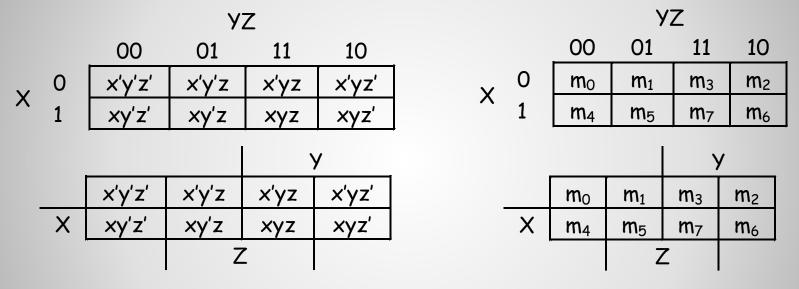

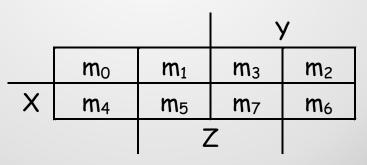

#### For a three-variable expression with inputs x, y, z, the arrangement of minterms is more tricky:

Another way to label the K-map (use whichever you like):

#### **A Three-Variable Karnaugh Map**

With this ordering, any group of 2, 4 or 8 adjacent squares on the map

contains common literals that can be factored out

$$x'y'z + x'y' = x'z(y' + y) = x'z \bullet 1 = x'z$$

"Adjacency" includes wrapping around the left and right sides:

x'y'z' + xy'z' +

• We'll use this property of adjacent squares to do our simplifications.

# Why the funny ordering?

x'yz' + xyz'

x'y + xy

y(x' + x))

= z'(y'+y)

= z'(x'y' + xy' +

= z'(y'(x' + x) +

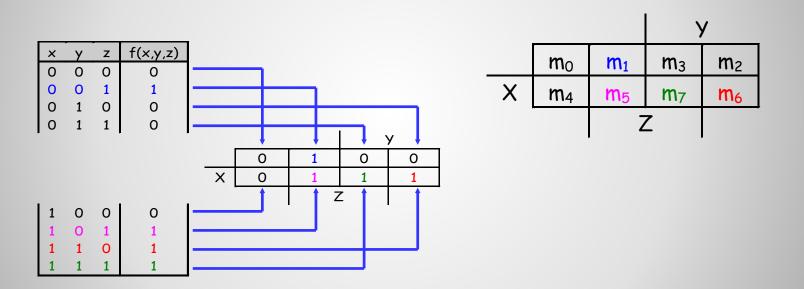

- We can fill in the K-map directly from a truth table

- The output in row *i* of the table goes into square *m<sub>i</sub>* of the K-map

- Remember that the rightmost columns of the K-map are "switched"

## **K-maps From Truth Tables**

You can find the minimal SoP expression

- Each rectangle corresponds to one product term

- The product is determined by finding the common literals in that rectangle

F(x,y,z) = y'z + xy

#### **Reading the MSP from the K-map**

- The most difficult step is grouping together all the 1s in the K-map

- Make rectangles around groups of one, two, four or eight 1s

- All of the 1s in the map should be included in at least one rectangle

- Do not include any of the 0s

- Each group corresponds to one product term

#### **Grouping the Minterms Together**

## **For the Simplest Result**

- Make as few rectangles as possible, to minimize the number of products in the final expression.

- Make each rectangle as large as possible, to minimize the number of literals in each term.

- Rectangles can be overlapped, if that makes them larger.

- Let's consider simplifying f(x,y,z) = xy + y'z + xz

- You should convert the expression into a sum of minterms form,

- The easiest way to do this is to make a truth table for the function, and then read off the minterms

- You can either write out the literals or use the minterm shorthand

- Here is the truth table and sum of minterms for our example:

| × | У | z | f(x,y,z) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | 0        |

| 0 | 1 | 1 | 0        |

| 1 | 0 | 0 | 0        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | 1        |

| 1 | 1 | 1 | 1        |

$$f(x,y,z) = x'y'z + xy'z + (yz' + xyz) = m_1 + m_5 + m_6 + m_7$$

#### K-map Simplification of SoP Expressions

# **Unsimplifying Expressions**

- You can also convert the expression to a sum of minterms with Boolean algebra

- Apply the distributive law in reverse to add in missing variables.

- Very few people actually do this, but it's occasionally useful.  $xy + y'z + xz = (xy \bullet 1) + (y'z \bullet 1) + (xz \bullet 1)$

- $= (xy \bullet (z' + z)) + (y'z \bullet (x' + x)) + (xz \bullet (y' + y))$ = (xy + (x' + z)) + (xz + (y' + y))

- = (xyz' + xyz) + (x'y'z + xy'z) + (xy'z + xyz)

$$= xyz' + xyz + x'y'z + xy'z$$

$= m_1 + m_5 + m_6 + m_7$

- In both cases, we're actually "unsimplifying" our example expression

- The resulting expression is larger than the original one!

- But having all the individual minterms makes it easy to combine them

together with the K-map

#### In our example, we can write f(x,y,z) in two equivalent ways

$f(x,y,z) = x'y'z + xy'z + xyz' + xyz f(x,y,z) = m_1 + m_5 + m_6 + m_7$

|   |        |       |      | Y     |   |       |            | >              | /              |

|---|--------|-------|------|-------|---|-------|------------|----------------|----------------|

|   | x'y'z' | x'y'z | x'yz | x'yz' |   | mo    | <b>m</b> 1 | m <sub>3</sub> | m <sub>2</sub> |

| Х | xy'z'  | xy'z  | xyz  | xyz'  | Х | $m_4$ | <b>m</b> 5 | <b>m</b> 7     | m <sub>6</sub> |

|   |        | Z     |      |       |   |       | Z          | 2              |                |

In either case, the resulting K-map is shown below

0

# Making the Example K-map

Х

$\cap$

1

7

1

## **Practice K-map 1**

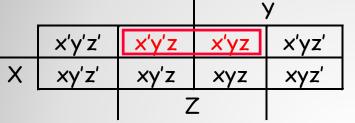

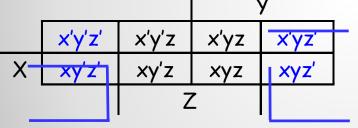

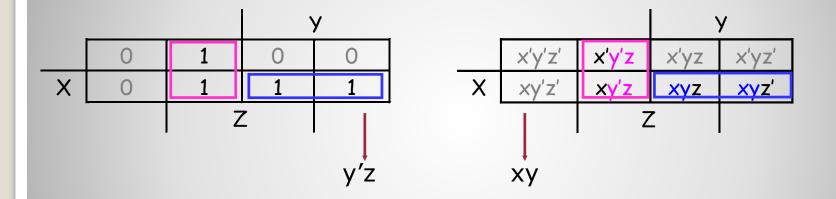

• Simplify the sum of minterms  $m_1 + m_3 + m_5 + m_6$  | y

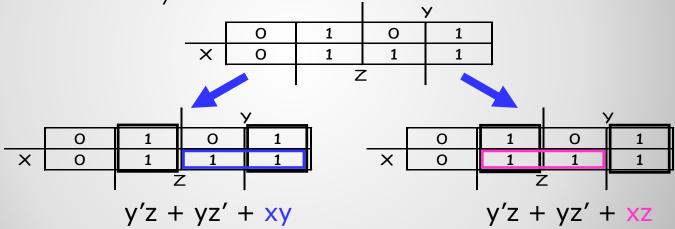

# **Solutions for Practice K-map 1**

- Here is the filled in K-map, with all groups shown

- The magenta and green groups overlap, which makes each of them as large as possible

- Minterm m<sub>6</sub> is in a group all by its lonesome

The final MSP here is x'z + y'z + xyz'

There may not necessarily be a *unique* MSP. The K-map below yields two valid and equivalent MSPs, because there are two possible

ways to

include minterm m<sub>7</sub>

Remember that overlapping groups is possible, as shown above

#### K-maps can be tricky!

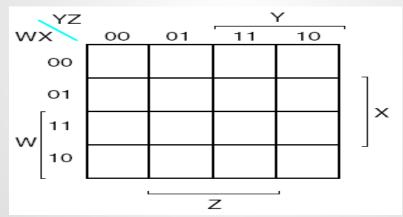

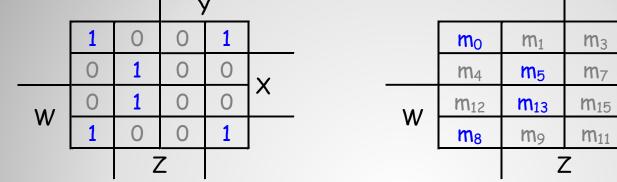

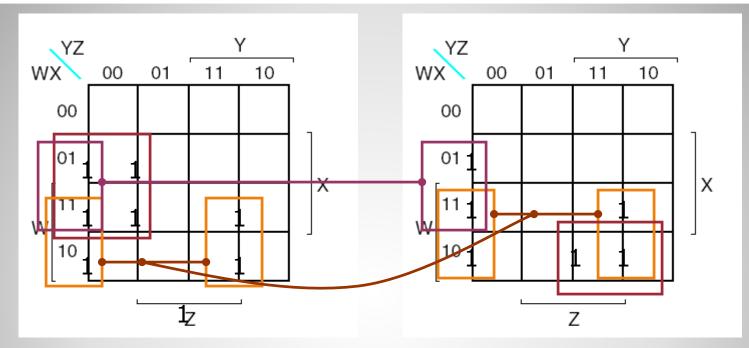

#### Four-variable K-maps – f(W,X,Y,Z)

- We can do four-variable expressions too!

- The minterms in the third and fourth columns, and in the third and fourth rows, are switched around.

- Again, this ensures that adjacent squares have common literals

- Grouping minterms is similar to the three-variable case, but:

- You can have rectangular groups of 1, 2, 4, 8 or 16 minterms

- You can wrap around all four sides

#### **Four-variable K-maps**

The expression is already a sum of minterms, so here's the K-map:

We can make the following groups, resulting in the MSP x'z' + xy'z

$m_2$

$m_6$

$m_{14}$

$\mathbf{m}_{10}$

X

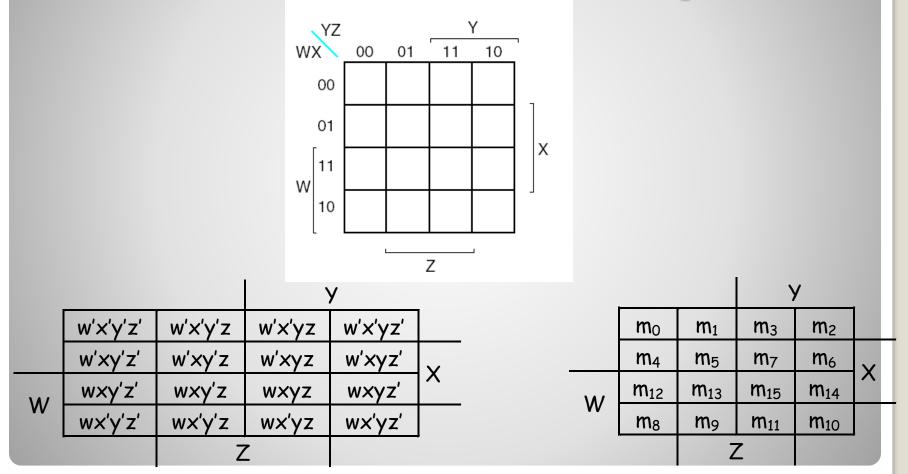

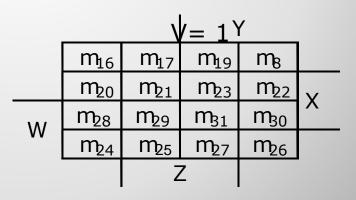

#### Five-variable K-maps – f(V,W,X,Y,Z)

V = 0

V = 1

f = XZ'  $\Sigma m(4,6,12,14,20,22,28,30)$   $+ V'W'Y' \Sigma m(0,1,4,5)$   $+ W'Y'Z' \Sigma m(0,4,16,20)$   $+ VWXY \Sigma m(30,31)$ + V'WX'YZ m11

Simplify f(V,W,X,Y,Z)=Σm(0,1,4,5,6,11,12,14,16,20,22,28,30,31)

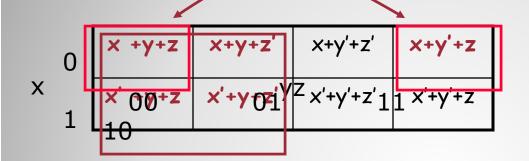

#### **PoS Optimization**

Maxterms are grouped to find minimal PoS expression 00

yz 01

11

10

|   | U . |         |         |          |         |

|---|-----|---------|---------|----------|---------|

| Х |     | х +y+z  | x+y+z'  | x+y'+z'  | x+y'+z  |

|   | 1   | x' +y+z | x'+y+z' | x'+y'+z' | x'+y'+z |

$F(W,X,Y,Z) = Y \cdot (X + Z)$

**PoS Optimization**

$F(W,X,Y,Z) = \Sigma m(0,1,2,5,8,9,10)$ =  $\Pi M(3,4,6,7,11,12,13,14,15)$

F(W,X,Y,Z) = (W' + X')(Y' + Z')(X' + Z)Or, F(W,X,Y,Z) = X'Y' + X'Z' + W'Y'ZWhich one is the minimal one?

#### **PoS Optimization from SoP**

$F(W,X,Y,Z) = \prod M(0,2,3,4,5,6)$ =  $\Sigma m(1,7,8,9,10,11,12,13,14,15)$

F(W,X,Y,Z) = W + XYZ + X'Y'Z

## **SoP Optimization from PoS**

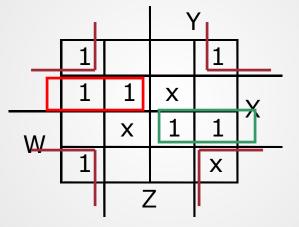

- You don't always need all 2<sup>n</sup> input combinations in an n-variable function

- If you can guarantee that certain input combinations never occur

- If some outputs aren't used in the rest of the circuit

- We mark don't-care outputs in truth tables and K-maps with Xs.

| × | Y | z | f(x,y,z) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | ×        |

| 0 | 1 | 1 | 0        |

| 1 | 0 | 0 | 0        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | ×        |

| 1 | 1 | 1 | 1        |

• Within a K-map, each X can be considered as either 0 or 1. You should pick the interpretation that allows for the most simplification.

#### Find a MSP for

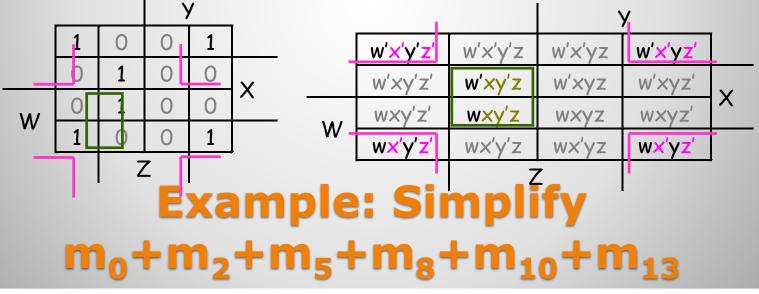

#### $f(w,x,y,z) = \Sigma m(0,2,4,5,8,14,15), d(w,x,y,z)$ $= \Sigma m(7,10,13)$

This notation means that input combinations wxyz = 0111, 1010 and 1101 (corresponding to minterms  $m_7$ ,  $m_{10}$  and  $m_{13}$ ) are unused.

# 1 0 1 1 1 1 × 1 1 × 0 × w 0 × 1 1 w 1 0 × × Z Z Z Z

• Find a MSP for:

$f(w,x,y,z) = \Sigma m(0,2,4,5,8,14,15), d(w,x,y,z) = \Sigma m(7,10,13)$

f(w,x,y,z) = x'z' + w'xy' + wxy

#### **Solutions for Practice K-map**

# **K-map Summary**

- K-maps are an alternative to algebra for simplifying expressions

- The result is a MSP/MPS, which leads to a minimal two-level circuit

- It's easy to handle don't-care conditions

- K-maps are really only good for manual simplification of small expressions...

- Things to keep in mind:

- Remember the correct order of minterms/maxterms on the K-map

- When grouping, you can wrap around all sides of the Kmap, and your groups can overlap

- Make as few rectangles as possible, but make each of them as large as possible. This leads to fewer, but simpler, product terms

- There may be more than one valid solution

## **Combinational Logic**

- Logic circuits for digital systems may be combinational or sequential.

- A combinational circuit consists of input variables, logic gates, and output variables.

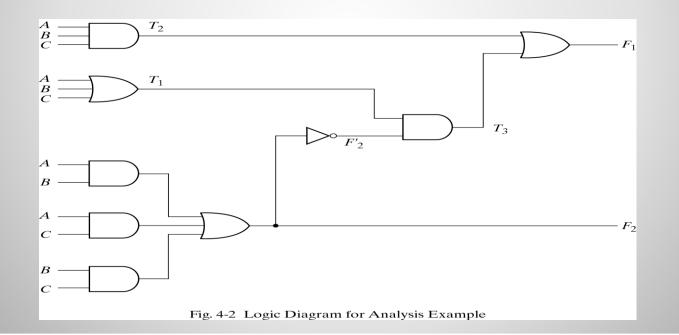

#### **2. Analysis procedure**

- To obtain the output Boolean functions from a logic diagram, proceed as follows:

- Label all gate outputs that are a function of input variables with arbitrary symbols. Determine the Boolean functions for each gate output.

- Label the gates that are a function of input variables and previously labeled gates with other arbitrary symbols. Find the Boolean functions for these gates.

- 3. Repeat the process outlined in step 2 until the outputs of the circuit are obtained.

- By repeated substitution of previously defined functions, obtain the output Boolean functions in terms of input variables.

#### Example

$F_{2} = AB + AC + BC; T_{1} = A + B + C; T_{2} = ABC; T_{3} = F_{2}'T_{1};$   $F_{1} = T_{3} + T_{2}$  $F_{1} = T_{3} + T_{2} = F_{2}'T_{1} + ABC = A'BC' + A'B'C + AB'C' + ABC$

#### Derive truth table from logic diagram

We can derive the truth table in Table 4-1 by using the circuit of Fig.2.

Table 4-1

Truth Table for the Logic Diagram of Fig. 4-2

| A | В | с | F2 | <b>F</b> <sub>2</sub> | T <sub>1</sub> | T <sub>2</sub> | T <sub>3</sub> | F <sub>1</sub> |

|---|---|---|----|-----------------------|----------------|----------------|----------------|----------------|

| 0 | 0 | 0 | 0  | 1                     | 0              | 0              | 0              | 0              |

| 0 | 0 | 1 | 0  | 1                     | 1              | 0              | 1              | 1              |

| 0 | 1 | 0 | 0  | 1                     | 1              | 0              | 1              | 1              |

| 0 | 1 | 1 | 1  | 0                     | 1              | 0              | 0              | 0              |

| 1 | 0 | 0 | 0  | 1                     | 1              | 0              | 1              | 1              |

| 1 | 0 | 1 | 1  | 0                     | 1              | 0              | 0              | 0              |

| 1 | 1 | 0 | 1  | 0                     | 1              | 0              | 0              | 0              |

| 1 | 1 | 1 | 1  | 0                     | 1              | 1              | 0              | 1              |

#### **3. Design procedure**

Table4-2 is a Code-Conversion example, first, we can list the relation of the BCD and Excess-3 codes in the truth table.

Table 4-2 Truth Table for Code-Conversion Example

Input BCD

Output Excess-3 Code

A

B

C

D

w

x

y

z

0

0

0

0

1

1

1

0

0

0

1

0

1

1

0

0

0

0

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

<t

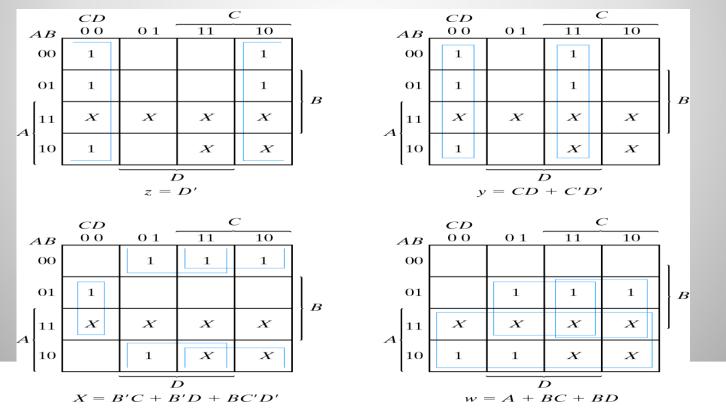

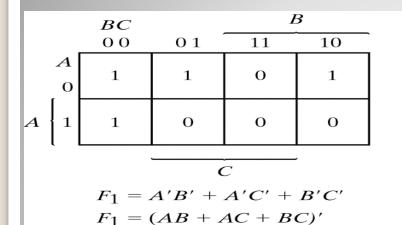

#### Karnaugh map

For each symbol of the Excess-3 code, we use 1's to draw the map for simplifying Boolean function.

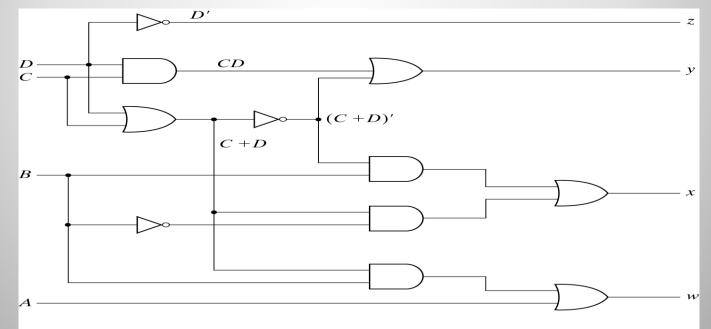

#### **Circuit implementation**

z = D'; y = CD + C'D' = CD + (C + D)' x = B'C + B'D + BC'D' = B'(C + D) + B(C + D)'w = A + BC + BD = A + B(C + D)

Fig. 4-4 Logic Diagram for BCD to Excess-3 Code Converter

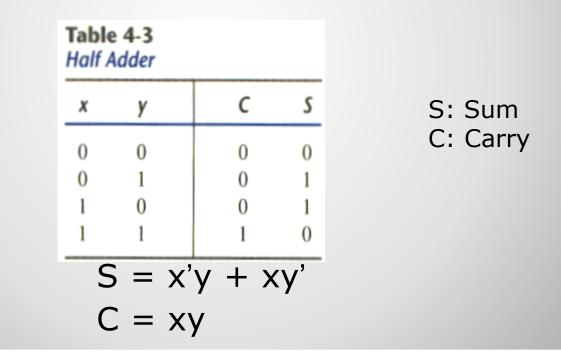

#### 4. Binary Adder-Subtractor

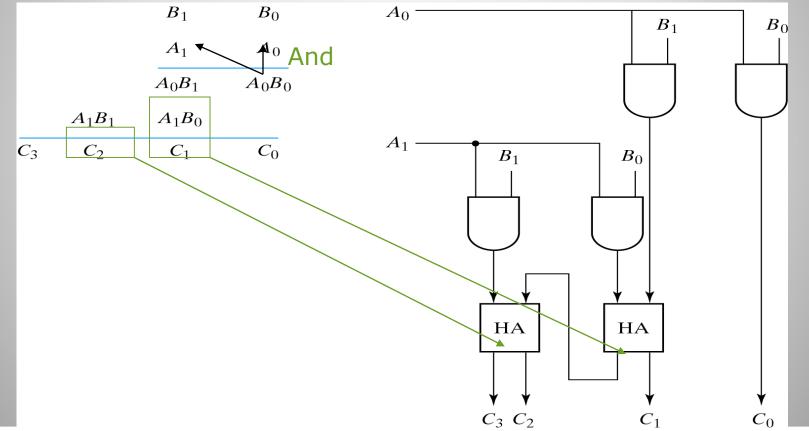

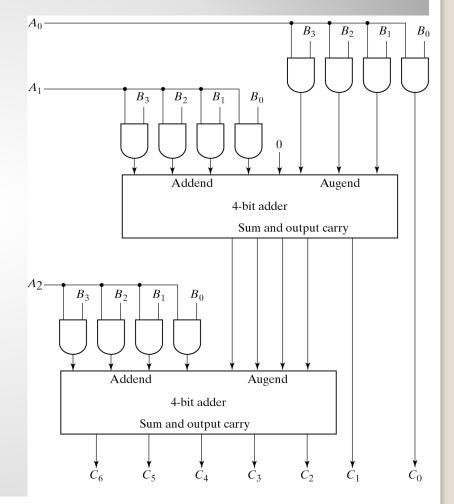

- A combinational circuit that performs the addition of two bits is called a half adder.

- The truth table for the half adder is listed below:

Fig. 4-5 Implementation of Half-Adder

#### **Implementation of Half-Adder**

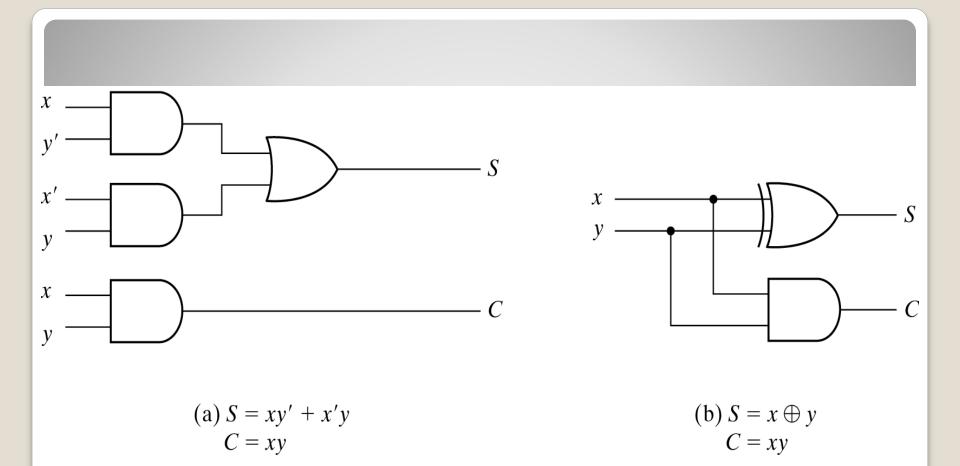

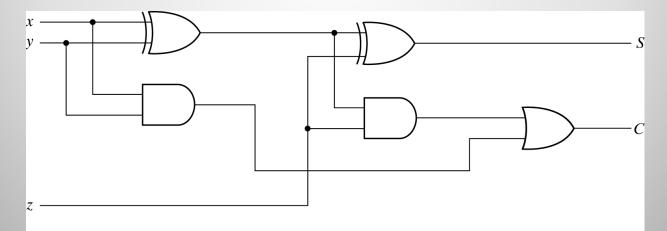

#### **Full-Adder**

One that performs the addition of three bits(two significant bits and a previous carry) is a full adder.

|   | Table 4-4<br>Full Adder |   |   |   |  |  |  |  |  |

|---|-------------------------|---|---|---|--|--|--|--|--|

| x | У                       | z | С | S |  |  |  |  |  |

| 0 | 0                       | 0 | 0 | 0 |  |  |  |  |  |

| 0 | 0                       | 1 | 0 | 1 |  |  |  |  |  |

| 0 | 1                       | 0 | 0 | 1 |  |  |  |  |  |

| 0 | 1                       | 1 | 1 | 0 |  |  |  |  |  |

| 1 | 0                       | 0 | 0 | 1 |  |  |  |  |  |

| 1 | 0                       | 1 | 1 | 0 |  |  |  |  |  |

| 1 | 1                       | 0 | 1 | 0 |  |  |  |  |  |

| 1 | 1                       | 1 | 1 | 1 |  |  |  |  |  |

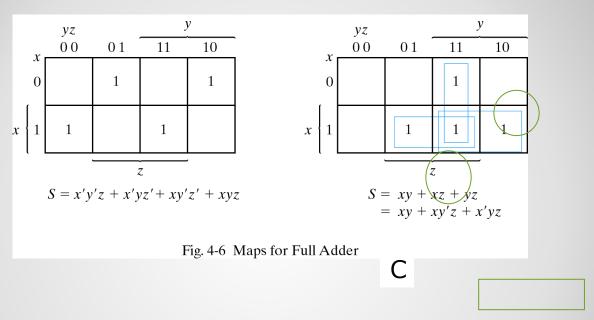

#### **Simplified Expressions**

## S = x'y'z + x'yz' + xy'z' + xyzC = xy + xz + yz

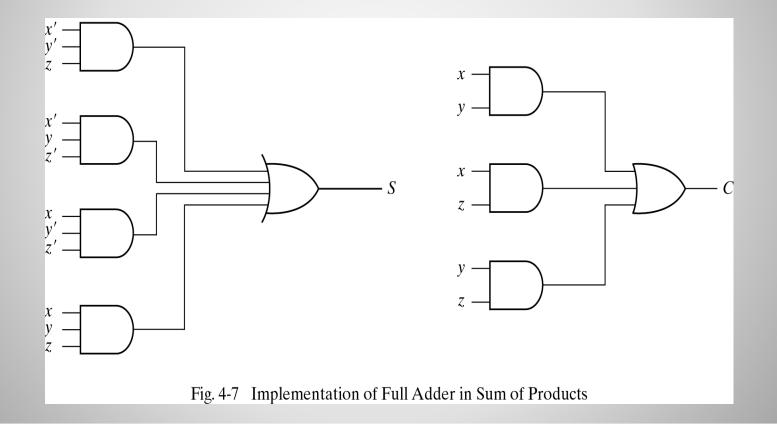

#### **Full adder implemented in SOP**

#### **Another implementation**

Full-adder can also implemented with two half adders and one OR gate (Carry Look-Ahead adder).

$$S = z \oplus (x \oplus y)$$

= z'(xy' + x'y) + z(xy' + x'y)'

= xy'z' + x'yz' + xyz + x'y'z

$$C = z(xy' + x'y) + xy = xy'z + x'yz + xy$$

Fig. 4-8 Implementation of Full Adder with Two Half Adders and an OR Gate

#### **Binary adder**

$C_{4}$

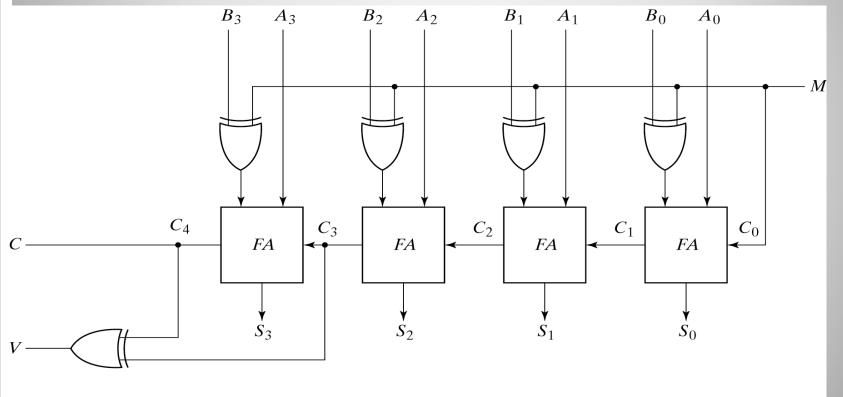

This is also called Ripple Carry Adder , because of the construction with full adders are connected in cascade.

| Subscript i:                                          | 3              | 2                                                                                                      | 1                     | 0                                                                       | and a              |

|-------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------|--------------------|

| Input carry                                           | 0              | 1                                                                                                      | 1                     | 0                                                                       | $C_i$              |

| Augend                                                | 1              | 0                                                                                                      | 1                     | 1                                                                       | $A_i$              |

| Addend                                                | 0              | 0                                                                                                      | 1                     | 1                                                                       | $B_i$              |

| Sum                                                   | 1              | 1                                                                                                      | 1                     | 0                                                                       | Si                 |

| Output carry                                          | 0              | 0                                                                                                      | 1                     | 1                                                                       | $S_i$<br>$C_{i+1}$ |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | C <sub>2</sub> | $\begin{array}{c c} B_1 & A_1 \\ \downarrow & \downarrow \\ \downarrow & \downarrow \\ FA \end{array}$ | <i>C</i> <sub>1</sub> | $\begin{array}{c} B_0  A_0 \\ \downarrow  \downarrow \\ FA \end{array}$ | ]                  |

| $FA$ $\leftarrow$ $C_3$ $FA$ $\leftarrow$             | •              |                                                                                                        |                       |                                                                         |                    |

Fig. 4-9 4-Bit Adder

#### **Carry Propagation**

- Fig.4-9 causes a unstable factor on carry bit, and produces a longest propagation delay.

- The signal from  $C_i$  to the output carry  $C_{i+1}$ , propagates through an AND and OR gates, so, for an n-bit RCA, there are 2n gate levels for the carry to propagate from input to output.

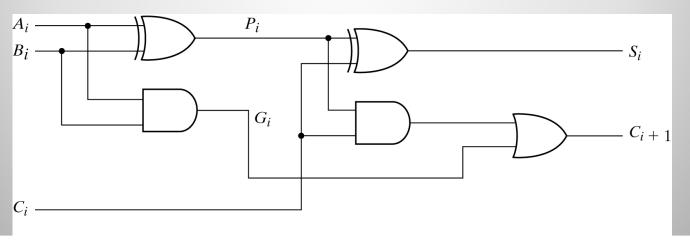

#### **Carry Propagation**

- Because the propagation delay will affect the output signals on different time, so the signals are given enough time to get the precise and stable outputs.

- The most widely used technique employs the principle of carry look-ahead to improve the speed of the algorithm.

Fig. 4-10 Full Adder with P and G Shown

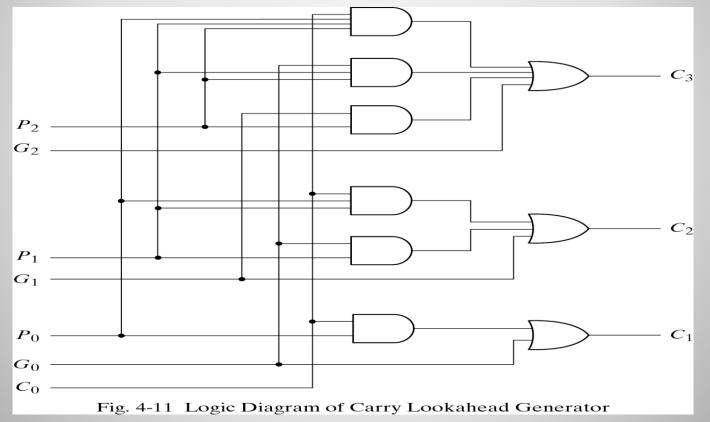

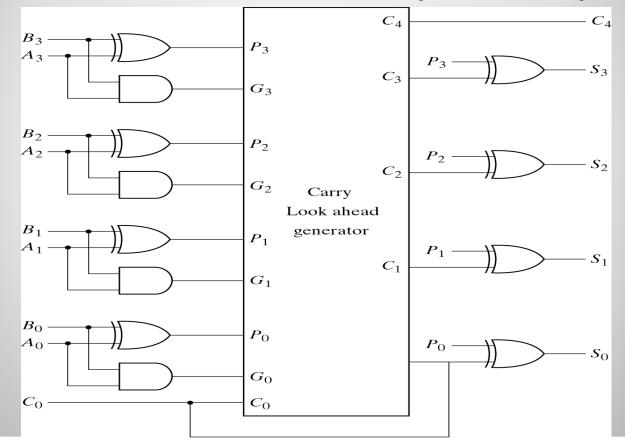

#### **Boolean functions** $P_i = A_i \oplus B_i$ steady state value $G_i = A_i B_i$ steady state value Output sum and carry $S_i = P_i \oplus C_i$ $C_{i+1} = G_i + P_i C_i$ G<sub>i</sub> : carry generate P<sub>i</sub> : carry propagate $C_0 = input carry$ $C_1 = G_0 + P_0 C_0$ $C_2 = G_1 + P_1C_1 = G_1 + P_1G_0 + P_1P_0C_0$ $C_3 = G_2 + P_2C_2 = G_2 + P_2G_1 + P_2P_1G_0 + P_2P_1P_0C_0$ $C_3$ does not have to wait for $C_2$ and $C_1$ to propagate.

#### Logic diagram of carry look-ahead generator

$C_3$  is propagated at the same time as  $C_2$  and  $C_1$ .

#### 4-bit adder with carry lookahead

Delay time of n-bit CLAA = XOR + (AND + OR) + XOR

Fig. 4-12 4-Bit Adder with Carry Lookahead

#### **Binary subtractor**

$M = 1 \rightarrow subtractor$ ;  $M = 0 \rightarrow adder$

Fig. 4-13 4-Bit Adder Subtractor

#### Overflow

It is worth noting Fig.4-13 that binary numbers in the signed-complement system are added and subtracted by the same basic addition and subtraction rules as unsigned numbers.

Overflow is a problem in digital computers because the number of bits that hold the number is finite and a result that contains n+1 bits cannot be accommodated.

# **Overflow on signed and unsigned**

- When two unsigned numbers are added, an overflow is detected from the end carry out of the MSB position.

- When two signed numbers are added, the sign bit is treated as part of the number and the end carry does not indicate an overflow.

- An overflow cann't occur after an addition if one number is positive and the other is negative.

- An overflow may occur if the two numbers added are both positive or both negative.

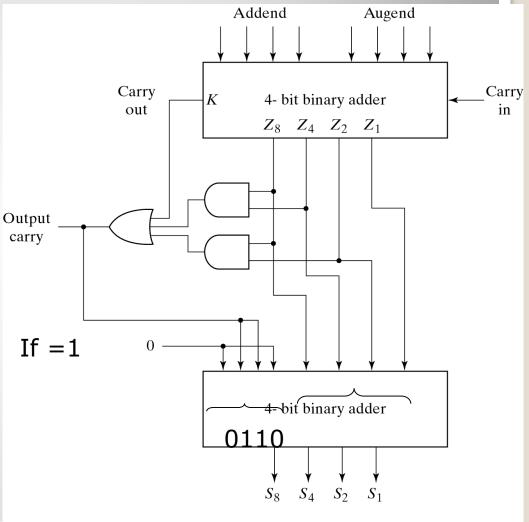

#### **5 Decimal adder**

#### BCD adder can't exceed 9 on each input digit. K is the carry.

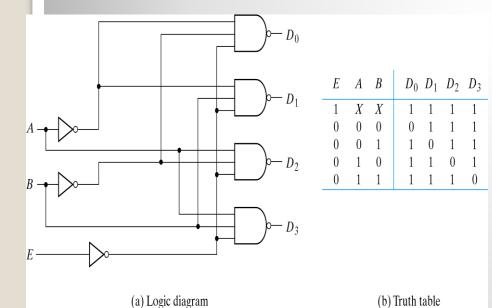

#### Table 4-5 Derivation of BCD Adder