# DIGITAL LOGIC DESIGN PPT

#### INSTITUTE OF AERONAUTICAL ENGINEERING

(Autonomous)

Dundigal, Hyderabad -500 043

# COMPUTER SCIENCE AND ENGINEERING/INFORMATION TECHNOLOGY DIGITAL LOGIC DESIGN PPT AEC020

#### **Course Coordinator**

Mr. K.Ravi, Assistant Professor, ECE

Ms. G. Bhavana, Assistant Professor, ECE

Ms. L.Shruthi, Assistant Professor, ECE

Ms. V.Bindusree, Assistant Professor, ECE

Ms. J.Swetha, Assistant Professor, ECE

Ms. Shreya verma, Assistant Professor, ECE

### INTRODUCTION TO DIGITAL LOGIC DESIGN

## UNIT 1

# INTRODUCTION TO DIGITAL LOGIC DESIGN

#### INTRODUCTION TO DIGITAL LOGIC DESIGN

Digital logic design is a system in electrical and computer engineering that uses simple number values to produce input and output operations.

#### INTRODUCTION TO DIGITAL LOGIC DESIGN

#### Advantages:

- •A digital computer stores data in terms of digits (numbers) and proceeds in discrete steps from one state to the next.

- •The states of a digital computer typically involve binary digits which may take the form of the presence or absence of magnetic markers in a storage medium, on-off switches or relays. In digital computers, even letters, words and whole texts are represented digitally.

### **NUMBER SYSTEMS**

# **Number Systems**

```

Decimal number: 123.45 = 1 \cdot 10^{2} + 2 \cdot 10^{1} + 3 \cdot 10^{0} + 4 \cdot 10^{-1} + 5 \cdot 10^{-2}

Base b number: N = a_{q-1}b^{q-1} + a_qb^0 +

b > 1, 0 <= a_i <= b-1

Integer part: a_{q-1}a_{q-2}

Fractional part: 0,10,2

Most significant digit: a_{o-1} \cdot \cdot \cdot

Least significant digit: o_p

Binary number (b=2): 1101.01 = 12^3 + 12^2 + 02^1 + 12^0 + 02^{-1} + 12^{-2}

Representing number N in base b: (N)_b

Complement of digit a: a' = (b-1)-a

Decimal system: 9's complement of 3 = 9-3 = 6

```

Binary system: 1's complement of 1 = 1-1 = 0

#### **Binary to Decimal Conversion:**

It is by the positional weights method. In this method, each binary digit of the no. is multiplied by its position weight. The product terms are added to obtain the decimal no.

#### **Binary to Octal conversion:**

Starting from the binary pt. make groups of 3 bits each, on either side of the binary pt, & replace each 3 bit binary group by the equivalent octal digit.

#### **Binary to Hexadecimal conversion:**

For this make groups of 4 bits each, on either side of the binary pt & replace each 4 bit group by the equivalent hexadecimal digit.

#### **Decimal to Binary conversion:**

**I.method**: is for small no.s The values of various powers of 2 need to be remembered. for conversion of larger no.s have a table of powers of 2 known as the sum of weights method. The set of binary weight values whose sum is equal to the decimal no. is determined.

**II.**method: It converts decimal integer no. to binary integer no by successive division by 2 & the decimal fraction is converted to binary fraction by double –dabble method

#### **Octal to decimal Conversion:**

Multiply each digit in the octal no by the weight of its position&add all the product termsDecimal value of the octal no.

#### **Decimal to Octal Conversion:**

To convert a mixed decimal no. To a mixed octal no. convert the integer and fraction parts separately. To convert decimal integer no. to octal, successively divide the given no by 8 till the quotient is 0. The last remainder is the MSD .The remainder read upwards give the equivalent octal integer no. To convert the given decimal fraction to octal, successively multiply the decimal fraction&the subsequent decimal fractions by 8 till the product is 0 or till the required accuracy is the MSD. The integers to the left of the octal pt read downwards give the octal fraction.

#### **Decimal to Hexadecimal conversion:**

It is successively divide the given decimal no. by 16 till the quotient is zero. The last remainder is the MSB. The remainder read from bottom to top gives the equivalent hexadecimal integer. To convert a decimal fraction to hexadecimal successively multiply the given decimal fraction & subsequent decimal fractions by 16, till the product is zero. Or till the required accuracy is obtained, and collect all the integers to the left of decimal pt. The first integer is MSB & the integer read from top to bottom give the hexadecimal fraction known as the hexadabble method.

#### Octal to hexadecimal conversion:

The simplest way is to first convert the given octal no. to binary & then the binary no. to hexadecimal.

#### FINDING THE BASE OF THE NUMBER SYSTEM

• Find r such that (121)r=(144)8, where r and 8 are the bases

$$1*8^{2} + 4*8+4*8^{0} = 64+32+4 = 100$$

$1*r^{2}+2*r+1*r^{0} = r^{2}+2r+1=(r+1)^{2}$

$(r+1)^{2}=100$

$r+1=10$

$r=9$

# **Binary Addition:**

Rules:

$$0+0=0$$

$$0+1=1$$

i.e, 0 with a carry of 1.

### **Binary Subtraction:**

Rules: 0-0=0

1-1=0

1-0=1

0-1=1 with a borrow of 1

#### **Binary multiplication:**

Rules:

$$0x0=0$$

$$1x1=0$$

$$1x0=0$$

$$0x1=0$$

#### **Binary Division:**

```

Example: 101101<sub>2</sub> by 110

110 ) 101101 ( 111.1

110

1010

110

1001

110

110

110

000

```

Ans: 111.1

#### 9's & 10's Complements:

It is the Subtraction of decimal no.s can be accomplished by the 9's & 10's compliment methods similar to the 1's & 2's compliment methods of binary . the 9's compliment of a decimal no. is obtained by subtracting each digit of that decimal no. from 9. The 10's compliment of a decimal no is obtained by adding a 1 to its 9's compliment.

### 1's compliment of n number:

It is obtained by simply complimenting each bit of the no,. & also, 1's comp of a no, is subtracting each bit of the no. form 1. This complemented value rep the —ve of the original no. One of the difficulties of using 1's comp is its rep of zero. Both 00000000 & its 1's comp 11111111 rep zero. The 000000000 called +ve zero 11111111 called —ve zero.

# 1's compliment arithmetic:

In 1's comp subtraction, add the 1's comp of the subtrahend to the minuend. If there is a carryout, bring the carry around & add it to the LSB called the **end around carry.** Look at the sign bit (MSB). If this is a 0, the result is +ve & is in true binary. If the MSB is a 1 ( carry or no carry ), the result is -ve & is in its is comp form .Take its 1's comp to get the magnitude inn binary.

### 9's & 10's Complements:

It is the Subtraction of decimal no.s can be accomplished by the 9's & 10's compliment methods similar to the 1's & 2's compliment methods of binary . the 9's compliment of a decimal no. is obtained by subtracting each digit of that decimal no. from 9. The 10's compliment of a decimal no is obtained by adding a 1 to its 9's compliment.

#### Methods of obtaining 2's comp of a no:

In 3 ways

By obtaining the 1's comp of the given no. (by changing all 0's to 1's & 1's to 0's) & then adding 1.

By subtracting the given n bit no N from 2<sup>n</sup>

Starting at the LSB, copying down each bit upto & including the first 1 bit encountered, and complimenting the remaining bits.

# 2's compliment Arithmetic:

The 2's comp system is used to rep —ve no.s using modulus arithmetic. The word length of a computer is fixed. i.e, if a 4 bit no. is added to another 4 bit no. the result will be only of 4 bits. Carry if any, from the fourth bit will overflow called the Modulus arithmetic.

Ex:1100+1111=1011

# 9's & 10's Complements:

•

It is the Subtraction of decimal no.s can be accomplished by the 9's & 10's compliment methods similar to the 1's & 2's compliment methods of binary . the 9's compliment of a decimal no. is obtained by subtracting each digit of that decimal no. from 9. The 10's compliment of a decimal no is obtained by adding a 1 to its 9's compliment

## 1's compliment of n number:

It is obtained by simply complimenting each bit of the no,. & also, 1's comp of a no, is subtracting each bit of the no. form 1. This complemented value rep the —ve of the original no. One of the difficulties of using 1's comp is its rep of zero. Both 00000000 & its 1's comp 11111111 rep zero. The 000000000 called +ve zero 11111111 called —ve zero.

# 1's compliment arithmetic:

In 1's comp subtraction, add the 1's comp of the subtrahend to the minuend. If there is a carryout, bring the carry around & add it to the LSB called the **end around carry.** Look at the sign bit (MSB). If this is a 0, the result is +ve & is in true binary. If the MSB is a 1 ( carry or no carry ), the result is -ve & is in its is comp form .Take its 1's comp to get the magnitude inn binary.

### 9's & 10's Complements:

It is the Subtraction of decimal no.s can be accomplished by the 9's & 10's compliment methods similar to the 1's & 2's compliment methods of binary . the 9's compliment of a decimal no. is obtained by subtracting each digit of that decimal no. from 9. The 10's compliment of a decimal no is obtained by adding a 1 to its 9's compliment.

#### BINARY WEIGHTED AND NON- WEIGHTED CODES

#### Weighted Codes:-

The weighted codes are those that obey the position weighting principle, which states that the position of each number represent a specific weight. In these codes each decimal digit is represented by a group of four bits. In weighted codes, each digit is assigned a specific weight according to its position. For example, in 8421/BCD code, 1001 the weights of 1, 1, 0, 1 (from left to right) are 8, 4, 2 and 1 respectively.

Examples:8421,2421 are all weighted codes.

#### BINARY WEIGHTED AND NON- WEIGHTED CODES

#### Non-weightedcodes:

The non-weighted codes are not positionally weighted. In other words codes that are not assigned with any weight to each digit position.

Examples: Excess-3(XS-3) and Gray Codes.

#### **BCD Addition:**

It is individually adding the corresponding digits of the decimal no,s expressed in 4 bit binary groups starting from the LSD . If there is no carry & the sum term is not an illegal code , no correction is needed. If there is a carry out of one group to the next group or if the sum term is an illegal code then  $6_{10}(0100)$  is added to the sum term of that group & the resulting carry is added to the next group.

#### **BCD Subtraction:**

Performed by subtracting the digits of each 4 bit group of the subtrahend the digits from the corresponding 4- bit group of the minuend in binary starting from the LSD . if there is no borrow from the next group , then  $6_{10}(0110)$  is subtracted from the difference term of this group.

#### **Excess-3Addition:**

Add the xs-3 no.s by adding the 4 bit groups in each column starting from the LSD. If there is no carry starting from the addition of any of the 4-bit groups , subtract 0011 from the sum term of those groups ( because when 2 decimal digits are added in xs-3 & there is no carry , result in xs-6). If there is a carry out, add 0011 to the sum term of those groups ( because when there is a carry, the invalid states are skipped and the result is normal binary).

#### **Excess -3 (XS-3) Subtraction:**

Subtract the xs-3 no.s by subtracting each 4 bit group of the subtrahend from the corresponding 4 bit group of the minuend starting form the LSD .if there is no borrow from the next 4-bit group add 0011 to the difference term of such groups (because when decimal digits are subtracted in xs-3 & there is no borrow , result is normal binary). If there is a borrow , subtract 0011 from the difference term(b coz taking a borrow is equivalent to adding six invalid states , result is in xs-6)

#### SIGNED BINARY NUMBERS

# Representation of signed no.s binary arithmetic in computers:

Two ways of rep signed no.s

Sign Magnitude form

Complemented form

Two complimented forms

1's compliment form

2's compliment form

#### SIGNED BINARY NUMBERS

**Error – Detecting codes:**When binary data is transmitted & processed, it is susceptible to noise that can alter or distort its contents. The 1's may get changed to 0's & 1's .because digital systems must be accurate to the digit, error can pose a problem. Several schemes have been devised to detect the occurrence of a single bit error in a binary word, so that whenever such an error occurs the concerned binary word can be corrected & retransmitted.

#### Introduction:

- When we talk about digital systems, be it a digital computer or a digital communication set-up, the issue of error detection and correction is of great practical significance.

- Errors creep into the bit stream owing to noise or other impairments during the course of its transmission from the transmitter to the receiver.

- While the addition of redundant bits helps in achieving the goal of making transmission of information from one place to another error free or reliable, it also makes it inefficient.

- Some Common Error Detecting and Correcting Codes

- Parity Code

- Repetition Code

- Cyclic Redundancy Check Code

- Hamming Code

## Parity Code:

- A parity bit is an extra bit added to a string of data bits in order to detect any error that might have crept into it while it was being stored or processed and moved from one place to another in a digital system.

- This simple parity code suffers from two limitations. Firstly, it cannot detect the error if the number of bits having undergone a change is even.

## Repetition Code:

- The repetition code makes use of repetitive transmission of each data bit in the bit stream. In the case of threefold repetition, '1' and '0' would be transmitted as '111' and '000' respectively.

- The repetition code is highly inefficient and the information throughput drops rapidly as we increase the number of times each data bit needs to be repeated to build error detection and correction capability.

## Cyclic Redundancy Check Code:

- Cyclic redundancy check (CRC) codes provide a reasonably high level of protection at low redundancy level.

- The probability of error detection depends upon the number of check bits, n used to construct the cyclic code. It is 100 % for single-bit and two-bit errors. It is also 100 % when an odd number of bits are in error and the error bursts have a length less than . n+1

- The probability of detection reduces to  $1-(1/2)^{n-1}$  for an error burst length equal to n+1, and to  $1-(1/2)^n$  for an error burst length greater than n+1.

#### Hamming Code:

- An increase in the number of redundant bits added to message bits can enhance the capability of the code to detect and correct errors.

- If sufficient number of redundant bits arranged such that different error bits produce different error results, then it should be possible not only to detect the error bit but also to identify its location.

- In fact, the addition of redundant bits alters the 'distance' code parameter, which has come to be known as the Hamming distance.

## Hamming Distance:

• The Hamming distance is nothing but the number of bit disagreements between two code words.

- For example, the addition of single-bit parity results in a code with a Hamming distance of at least 2.

- The smallest Hamming distance in the case of a threefold repetition code would be 3.

- Hamming noticed that an increase in distance enhanced the code's ability to detect and correct errors.

- Hamming's code was therefore an attempt at increasing the Hamming distance and at the same time having as high an information throughput rate as possible.

- The algorithm for writing the generalized Hamming code is as follows:

- 1. The generalized form of code is  $P_1P_2D_1P_3D_2D_3D_4P_4D_5D_6D_7D_8D_9D_{10}D_{11}P_{5.....}$ , where P and D respectively represent parity and data bits.

- 2. We can see from the generalized form of the code that all bit positions that are powers of 2 (positions 1, 2, 4, 8, 16 ...) are used as parity bits.

- 3. All other bit positions (positions 3, 5, 6, 7, 9, 10, 11 ...) are used to encode data.

- 4. Each parity bit is allotted a group of bits from the data bits in the code word, and the value of the parity bit (0 or 1) is used to give it certain parity.

- 1. Groups are formed by first checking bits and then alternately skipping and checking bits following the parity bit. Here, is the position of the parity bit; 1 for  $P_1$ , 2 for  $P_2$ , 4 for  $P_3$ , 8 for  $P_4$  and so on.

- 2. For example, for the generalized form of code given above, various groups of bits formed with different parity bits would be  $P_1D_1D_2D_4D_5...$ ,  $P_2D_1D_3D_4D_6D_7...$ ,  $P_3D_2D_3D_4D_8D_9...$ ,  $P_4D_5D_6D_7D_8D_9D_{10}D_{11...}$  and so on. To illustrate the formation of groups further, let us examine the group corresponding to parity bit  $P_3$ .

- 3. Now, the position of  $P_3$  is at number 4. In order to form the group, we check the first three bits N-1=3 and then follow it up by alternately skipping and checking four bits (N=4).

- The Hamming code is capable of correcting single-bit errors on messages of any length.

- Although the Hamming code can detect two-bit errors, it cannot give the error locations.

- The number of parity bits required to be transmitted along with the message, however, depends upon the message length.

- The number of parity bits n required to encode m message bits is the smallest integer that satisfies the condition  $\binom{2^n n}{n} > m$ .

- The most commonly used Hamming code is the one that has a code word length of seven bits with four message bits and three parity bits.

- It is also referred to as the Hamming (7, 4) code

• The code word sequence for this code is written as  $P_1P_2D_1P_3D_2D_3D_4$ , with  $P_1$ ,  $P_2$  and  $P_3$  being the parity bits and  $D_1$ ,  $D_2$ ,  $D_3$  and  $D_4$  being the data bits.

## Generation of Hamming Code:

|                                 | $P_1$ | $P_2$ | $D_1$ | $P_3$ | $D_2$ | $D_3$ | $D_4$ |

|---------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Data bits (without parity)      |       |       | 0     |       | 1     | 1     | 0     |

| Data bits with parity bit $P_1$ | 1     |       | 0     |       | 1     |       | 0     |

| Data bits with parity bit $P_2$ |       | 1     | 0     |       |       | 1     | 0     |

| Data bits with parity bit $P_3$ |       |       |       | 0     | 1     | 1     | 0     |

| Data bits with parity           | 1     | 1     | 0     | 0     | 1     | 1     | 0     |

## **BOOLEAN ALGEBRA**

# UNIT 2

# INTRODUCTION TO BOOLEAN ALGEBRA

## **BOOLEAN ALGEBRA**

- Also known as Switching Algebra

- Invented by mathematician George Boole in 1849

- Used by Claude Shannon at Bell Labs in 1938

- To describe digital circuits built from relays

- Digital circuit design is based on

- › Boolean Algebra

- Attributes

- Postulates

- Theorems

- These allow minimization and manipulation of logic gates for optimizing digital circuits

## **BOOLEAN ALGEBRA ATTRIBUTES**

## Binary

X'

$\mathbf{X}$

- > A1a: X=0 if X=1 /

- > A1b: X=1 if X=0

- Complement

- > aka invert, NOT

- $\rightarrow$  A2a: if X=0, X'=1

- > A2b: if X=1, X'=0

- The tick mark ' means complement, invert, or NOT

- $\begin{array}{c|c}

\hline

1 \\

\hline

0 \\

\hline

\end{array}$  Other symbol for complement: X' =  $\overline{X}$

- AND operation

- > A3a:0•0=0

- > A4a:1•1=1

- > A5a: 0•1=1•0=0

- The dot means AND

- Other symbol for AND:

X•Y=XY (no symbol)

| Χ | Υ | X∙Y |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

- OR Operation

- > A3b:1+1=1

- > A4b:0+0=0

- > A5b: 1+0=0+1=1

- The plus + means OR

| Х | Υ | X+Y |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

## **BOOLEAN ALGEBRA ATTRIBUTES**

- Variable: Variables are the different symbols in a Boolean expression

- Literal: Each occurrence of a variable or its complement is called a literal

- Term: A term is the expression formed by literals and operations at one level

$$\overline{A} + A.B + A.\overline{C} + \overline{A}.B.C$$

- A, B, C are three variables

- Eight Literals

- Expression has five terms including four AND terms and the OR term that combines the first-level AND terms.

## **BOOLEAN ALGEBRA POSTULATES**

## OR operation

- Identity Elements

- > P2a: X+0=X

- > P2b: X•1=X

- Commutativity

- > P3a: X+Y=Y+X

- > P3b: X•Y=Y•X

- Complements

- > P6a: X+X'=1

- > P6b: X•X'=0

| Χ | Υ | X+0 | X+Y | Y+X | X' | X+X' |

|---|---|-----|-----|-----|----|------|

| 0 | 0 | 0   | 0   | 0   | 1  | 1    |

| 0 | 1 | 0   | 1   | 1   | 1  | 1    |

| 1 | 0 | 1   | 1   | 1   | 0  | 1    |

| 1 | 1 | 1   | 1   | 1   | 0  | 1    |

## **AND** operation

| Χ | Υ | X•1 | X•Y | Y•X | X' | <b>X•X′</b> |

|---|---|-----|-----|-----|----|-------------|

| 0 | 0 | 0   | 0   | 0   | 1  | 0           |

| 0 | 1 | 0   | 0   | 0   | 1  | 0           |

| 1 | 0 | 1   | 0   | 0   | 0  | 0           |

| 1 | 1 | 1   | 1   | 1   | 0  | 0           |

## **BOOLEAN ALGEBRA POSTULATES**

## Associativity

- > P4a: (X+Y)+Z=X+(Y+Z)

- $\rightarrow$  P4b:  $(X \bullet Y) \bullet Z = X \bullet (Y \bullet Z)$

| Х | Υ | Z | X+Y | (X+Y)+Z | Y+Z | X+(Y+Z) | X•Y | (X•Y)•Z | Y•Z | <b>X</b> •( <b>Y</b> • <b>Z</b> ) |

|---|---|---|-----|---------|-----|---------|-----|---------|-----|-----------------------------------|

| 0 | 0 | 0 | 0   | 0       | 0   | 0       | 0   | 0       | 0   | 0                                 |

| 0 | 0 | 1 | 0   | 1       | 1   | 1       | 0   | 0       | 0   | 0                                 |

| 0 | 1 | 0 | 1   | 1       | 1   | 1       | 0   | 0       | 0   | 0                                 |

| 0 | 1 | 1 | 1   | 1       | 1   | 1       | 0   | 0       | 1   | 0                                 |

| 1 | 0 | 0 | 1   | 1       | 0   | 1       | 0   | 0       | 0   | 0                                 |

| 1 | 0 | 1 | 1   | 1       | 1   | 1       | 0   | 0       | 0   | 0                                 |

| 1 | 1 | 0 | 1   | 1       | 1   | 1       | 1   | 0       | 0   | 0                                 |

| 1 | 1 | 1 | 1   | 1       | 1   | 1       | 1   | 1       | 1   | 1                                 |

## **BOOLEAN ALGEBRA POSTULATES**

#### Distributivity

- $\rightarrow$  P5a: X+(Y•Z) = (X+Y)•(X+Z)

- $\rightarrow$  P5b: X•(Y+Z) = (X•Y)+(X•Z)

|   |   |   |     |     | (X+Y)• |     | X+    |     |     | X•Y+ |     | Χ•    |

|---|---|---|-----|-----|--------|-----|-------|-----|-----|------|-----|-------|

| Х | Υ | Z | X+Y | X+Z | (X+Z)  | Y•Z | (Y•Z) | Χ•Υ | X•Z | X∙Z  | Y+Z | (Y+Z) |

| 0 | 0 | 0 | 0   | 0   | 0      | 0   | 0     | 0   | 0   | 0    | 0   | 0     |

| 0 | 0 | 1 | 0   | 1   | 0      | 0   | 0     | 0   | 0   | 0    | 1   | 0     |

| 0 | 1 | 0 | 1   | 0   | 0      | 0   | 0     | 0   | 0   | 0    | 1   | 0     |

| 0 | 1 | 1 | 1   | 1   | 1      | 1   | 1     | 0   | 0   | 0    | 1   | 0     |

| 1 | 0 | 0 | 1   | 1   | 1      | 0   | 1     | 0   | 0   | 0    | 0   | 0     |

| 1 | 0 | 1 | 1   | 1   | 1      | 0   | 1     | 0   | 1   | 1    | 1   | 1     |

| 1 | 1 | 0 | 1   | 1   | 1      | 0   | 1     | 1   | 0   | 1    | 1   | 1     |

| 1 | 1 | 1 | 1   | 1   | 1      | 1   | 1     | 1   | 1   | 1    | 1   | 1     |

## Idempotency

- > T1a: X+X=X

- > T1b: X•X=X

- Null elements

- > T2a: X+1=1

- > T2b:X•0=0

- Involution

- > T3: (X')'=X

| Х | Υ | Х+Ү | Х∙Ү | X+X | X•X | X+1 | X•0 | X' | Χ'' |

|---|---|-----|-----|-----|-----|-----|-----|----|-----|

| 0 | 0 | 0   | 0   | 0   | 0   | 1   | 0   | 1  | 0   |

| 0 | 1 | 1   | 0   | 0   | 0   | 1   | 0   | 1  | 0   |

| 1 | 0 | 1   | 0   | 1   | 1   | 1   | 0   | 0  | 1   |

| 1 | 1 | 1   | 1   | 1   | 1   | 1   | 0   | 0  | 1   |

#### Absorption (aka covering)

> T4a: X+(X•Y)=X

$\rightarrow$  T4b: X•(X+Y)=X

> T5a: X+(X'•Y)=X+Y

> T5b: X•(X'+Y)=X•Y

|   |   |     |     | X+            | <b>X•</b> |    |      | X+     |      | X•     |

|---|---|-----|-----|---------------|-----------|----|------|--------|------|--------|

| X | Y | X+Y | X•Y | $(X \cdot Y)$ | (X+Y)     | X' | X'•Y | (X'•Y) | X'+Y | (X'+Y) |

| 0 | 0 | 0   | 0   | 0             | 0         | 1  | 0    | 0      | 1    | 0      |

| 0 | 1 | 1   | 0   | 0             | 0         | 1  | 1    | 1      | 1    | 0      |

| 1 | 0 | 1   | 0   | 1             | 1         | 0  | 0    | 1      | 0    | 0      |

| 1 | 1 | 1   | 1   | 1             | 1         | 0  | 0    | 1      | 1    | 1      |

Absorption (aka combining)

> T6a: (X•Y)+(X•Y')=X

> T6b: (X+Y) • (X+Y')=X

|   |   |     |     |    |      | $(X \bullet Y) +$ |      | (X+Y)• |

|---|---|-----|-----|----|------|-------------------|------|--------|

| X | Y | X+Y | X•Y | Y' | X•Y' | (X•Y')            | X+Y' | (X+Y') |

| 0 | 0 | 0   | 0   | 1  | 0    | 0                 | 1    | 0      |

| 0 | 1 | 1   | 0   | 0  | 0    | 0                 | 0    | 0      |

| 1 | 0 | 1   | 0   | 1  | 1    | 1                 | 1    | 1      |

| 1 | 1 | 1   | 1   | 0  | 0    | 1                 | 1    | 1      |

- Absorption (aka combining)

- > T7a: (X•Y)+(X•Y'•Z)=(X•Y)+(X•Z)

- $> T7b: (X+Y) \bullet (X+Y'+Z) = (X+Y) \bullet (X+Z)$

|       |   |    |      | (XY)+  |    | (XY)+ |     | X+Y' | (X+Y)•   |     | (X+Y)• |

|-------|---|----|------|--------|----|-------|-----|------|----------|-----|--------|

| XYZ   | Y | XY | XY'Z | (XY'Z) | XZ | (XZ)  | X+Y | +Z   | (X+Y'+Z) | X+Z | (X+Z)  |

| 0 0 0 | 1 | 0  | 0    | 0      | 0  | 0     | 0   | 1    | 0        | 0   | 0      |

| 0 0 1 | 1 | 0  | 0    | 0      | 0  | 0     | 0   | 1    | 0        | 1   | 0      |

| 0 1 0 | 0 | 0  | 0    | 0      | 0  | 0     | 1   | 0    | 0        | 0   | 0      |

| 0 1 1 | 0 | 0  | 0    | 0      | 0  | 0     | 1   | 1    | 1        | 1   | 1      |

| 1 0 0 | 1 | 0  | 0    | 0      | 0  | 0     | 1   | 1    | 1        | 1   | 1      |

| 1 0 1 | 1 | 0  | 1    | 1      | 1  | 1     | 1   | 1    | 1        | 1   | 1      |

| 1 1 0 | 0 | 1  | 0    | 1      | 0  | 1     | 1   | 1    | 1        | 1   | 1      |

| 1 1 1 | 0 | 1  | 0    | 1      | 1  | 1     | 1   | 1    | 1        | 1   | 1      |

- DeMorgan's theorem (very important!)

- > T8a: (X+Y)'= X' Y'

- $\overline{X+Y} = \overline{X} \cdot \overline{Y}$  break (or connect) the bar & change the sign

- > T8b: (X•Y)'= X'+Y'

- X•Y = X+Y break (or connect) the bar & change the sign

- Generalized DeMorgan's theorem:

- GT8a:  $(X_1+X_2+...+X_{n-1}+X_n)'=X_1'\bullet X_2'\bullet...\bullet X_{n-1}'\bullet X_n'$

- GT8b:  $(X_1 \bullet X_2 \bullet ... \bullet X_{n-1} \bullet X_n)' = X_1' + X_2' + ... + X_{n-1}' + X_n'$

| X | Y | X+Y | X•Y | X' | Y' | (X+Y)' | X'•Y' | (X•Y)' | X'+Y' |

|---|---|-----|-----|----|----|--------|-------|--------|-------|

| 0 | 0 | 0   | 0   | 1  | 1  | 1      | 1     | 1      | 1     |

| 0 | 1 | 1   | 0   | 1  | 0  | 0      | 0     | 1      | 1     |

| 1 | 0 | 1   | 0   | 0  | 1  | 0      | 0     | 1      | 1     |

| 1 | 1 | 1   | 1   | 0  | 0  | 0      | 0     | 0      | 0     |

#### Consensus Theorem

- $\Rightarrow T9a: (X \bullet Y) + (X' \bullet Z) + (Y \bullet Z) = (X \bullet Y) + (X' \bullet Z)$

- $\rightarrow T9b: (X+Y) \bullet (X'+Z) \bullet (Y+Z) = (X+Y) \bullet (X'+Z)$

|     |   |            |    |     |    | (XY)+  |       |     |      |     | (X+Y)•  |        |

|-----|---|------------|----|-----|----|--------|-------|-----|------|-----|---------|--------|

|     |   |            |    |     |    | (X'Z)+ | (XY)+ |     |      |     | (X'+Z)• | (X+Y)• |

| Х Ү | Z | <b>X</b> ′ | XY | X'Z | YZ | (YZ)   | (X'Z) | X+Y | X'+Z | Y+Z | (Y+Z)   | (X'+Z) |

| 0 0 | 0 | 1          | 0  | 0   | 0  | 0      | 0     | 0   | 1    | 0   | 0       | 0      |

| 0 0 | 1 | 1          | 0  | 1   | 0  | 1      | 1     | 0   | 1    | 1   | 0       | 0      |

| 0 1 | 0 | 1          | 0  | 0   | 0  | 0      | 0     | 1   | 1    | 1   | 1       | 1      |

| 0 1 | 1 | 1          | 0  | 1   | 1  | 1      | 1     | 1   | 1    | 1   | 1       | 1      |

| 1 0 | 0 | 0          | 0  | 0   | 0  | 0      | 0     | 1   | 0    | 0   | 0       | 0      |

| 1 0 | 1 | 0          | 0  | 0   | 0  | 0      | 0     | 1   | 1    | 1   | 1       | 1      |

| 1 1 | 0 | 0          | 1  | 0   | 0  | 1      | 1     | 1   | 0    | 1   | 0       | 0      |

| 1 1 | 1 | 0          | 1  | 0   | 1  | 1      | 1     | 1   | 1    | 1   | 1       | 1      |

## **MORE THEOREMS?**

- Shannon's expansion theorem (also very important!)

- $\rightarrow$  T10a:  $f(X_1, X_2, ..., X_{n-1}, X_n) =$

- $(X_1' \bullet f(0, X_2, ..., X_{n-1}, X_n)) + (X_1 \bullet f(1, X_2, ..., X_{n-1}, X_n))$

- Can be taken further:

•

$$f(X_1, X_2, ..., X_{n-1}, X_n) = (X_1' \bullet X_2' \bullet f(0, 0, ..., X_{n-1}, X_n))$$

• +

$$(X_1 \bullet X_2' \bullet f(1,0,...,X_{n-1},X_n)) + (X_1' \bullet X_2 \bullet f(0,1,...,X_{n-1},X_n))$$

- + $(X_1 \bullet X_2 \bullet f(1,1,...,X_{n-1},X_n))$

- Can be taken even further:

•

$$f(X_1, X_2, ..., X_{n-1}, X_n) = (X_1' \bullet X_2' \bullet ... \bullet X_{n-1}' \bullet X_n' \bullet f(0, 0, ..., 0, 0))$$

• +

$$(X_1 \bullet X_2' \bullet ... \bullet X_{n-1}' \bullet X_n' \bullet f(1,0,...,0,0)) + ...$$

• +

$$(X_1 \bullet X_2 \bullet ... \bullet X_{n-1} \bullet X_n \bullet f(1,1,...,1,1))$$

- $\rightarrow$  T10b:  $f(X_1, X_2, ..., X_{n-1}, X_n) =$

- $(X_1+f(0,X_2,...,X_{n-1},X_n)) \bullet (X_1'+f(1,X_2,...,X_{n-1},X_n))$

- Can be taken further as in the case of T10a

- We'll see significance of Shannon's expansion theorem later

## Idempotency

- > T1a: X+X=X

- > T1b: X•X=X

- Null elements

- > T2a: X+1=1

- > T2b:X•0=0

- Involution

- > T3: (X')'=X

| Х | Υ | X+Y | X∙Y | X+X | X•X | X+1 | X•0 | X' | X'' |

|---|---|-----|-----|-----|-----|-----|-----|----|-----|

| 0 | 0 | 0   | 0   | 0   | 0   | 1   | 0   | 1  | 0   |

| 0 | 1 | 1   | 0   | 0   | 0   | 1   | 0   | 1  | 0   |

| 1 | 0 | 1   | 0   | 1   | 1   | 1   | 0   | 0  | 1   |

| 1 | 1 | 1   | 1   | 1   | 1   | 1   | 0   | 0  | 1   |

#### Absorption (aka covering)

> T4a: X+(X•Y)=X

$\rightarrow$  T4b: X•(X+Y)=X

> T5a: X+(X'•Y)=X+Y

> T5b: X•(X'+Y)=X•Y

|   |   |     |     | X+            | X•    |    |      | X+     |      | X•     |

|---|---|-----|-----|---------------|-------|----|------|--------|------|--------|

| X | Y | X+Y | X•Y | $(X \cdot Y)$ | (X+Y) | X' | X'•Y | (X'•Y) | X'+Y | (X'+Y) |

| 0 | 0 | 0   | 0   | 0             | 0     | 1  | 0    | 0      | 1    | 0      |

| 0 | 1 | 1   | 0   | 0             | 0     | 1  | 1    | 1      | 1    | 0      |

| 1 | 0 | 1   | 0   | 1             | 1     | 0  | 0    | 1      | 0    | 0      |

| 1 | 1 | 1   | 1   | 1             | 1     | 0  | 0    | 1      | 1    | 1      |

Absorption (aka combining)

> T6a: (X•Y)+(X•Y')=X

> T6b: (X+Y) • (X+Y')=X

|   |   |     |     |    |      | $(X \bullet Y) +$ |      | (X+Y)• |

|---|---|-----|-----|----|------|-------------------|------|--------|

| X | Y | X+Y | X•Y | Y' | X•Y' | (X•Y')            | X+Y' | (X+Y') |

| 0 | 0 | 0   | 0   | 1  | 0    | 0                 | 1    | 0      |

| 0 | 1 | 1   | 0   | 0  | 0    | 0                 | 0    | 0      |

| 1 | 0 | 1   | 0   | 1  | 1    | 1                 | 1    | 1      |

| 1 | 1 | 1   | 1   | 0  | 0    | 1                 | 1    | 1      |

- Absorption (aka combining)

- > T7a: (X•Y)+(X•Y'•Z)=(X•Y)+(X•Z)

- $\rightarrow$  T7b: (X+Y)•(X+Y'+Z) = (X+Y)•(X+Z)

|       |   |    |      | (XY)+  |    | (XY)+ |     | X+Y' | (X+Y)•   |     | (X+Y)• |

|-------|---|----|------|--------|----|-------|-----|------|----------|-----|--------|

| XYZ   | Y | XY | XY'Z | (XY'Z) | XZ | (XZ)  | X+Y | +Z   | (X+Y'+Z) | X+Z | (X+Z)  |

| 0 0 0 | 1 | 0  | 0    | 0      | 0  | 0     | 0   | 1    | 0        | 0   | 0      |

| 0 0 1 | 1 | 0  | 0    | 0      | 0  | 0     | 0   | 1    | 0        | 1   | 0      |

| 0 1 0 | 0 | 0  | 0    | 0      | 0  | 0     | 1   | 0    | 0        | 0   | 0      |

| 0 1 1 | 0 | 0  | 0    | 0      | 0  | 0     | 1   | 1    | 1        | 1   | 1      |

| 1 0 0 | 1 | 0  | 0    | 0      | 0  | 0     | 1   | 1    | 1        | 1   | 1      |

| 1 0 1 | 1 | 0  | 1    | 1      | 1  | 1     | 1   | 1    | 1        | 1   | 1      |

| 1 1 0 | 0 | 1  | 0    | 1      | 0  | 1     | 1   | 1    | 1        | 1   | 1      |

| 1 1 1 | 0 | 1  | 0    | 1      | 1  | 1     | 1   | 1    | 1        | 1   | 1      |

- DeMorgan's theorem (very important!)

- > T8a: (X+Y)'= X' Y'

- $\overline{X+Y} = \overline{X} \cdot \overline{Y}$  break (or connect) the bar & change the sign

- > T8b: (X•Y)'= X'+Y'

- X•Y = X+Y break (or connect) the bar & change the sign

- Generalized DeMorgan's theorem:

- GT8a:  $(X_1+X_2+...+X_{n-1}+X_n)'=X_1'\bullet X_2'\bullet...\bullet X_{n-1}'\bullet X_n'$

- GT8b:  $(X_1 \bullet X_2 \bullet ... \bullet X_{n-1} \bullet X_n)' = X_1' + X_2' + ... + X_{n-1}' + X_n'$

| X | Y | X+Y | X•Y | X' | Y' | (X+Y)' | X'•Y' | (X•Y)' | X'+Y' |

|---|---|-----|-----|----|----|--------|-------|--------|-------|

| 0 | 0 | 0   | 0   | 1  | 1  | 1      | 1     | 1      | 1     |

| 0 | 1 | 1   | 0   | 1  | 0  | 0      | 0     | 1      | 1     |

| 1 | 0 | 1   | 0   | 0  | 1  | 0      | 0     | 1      | 1     |

| 1 | 1 | 1   | 1   | 0  | 0  | 0      | 0     | 0      | 0     |

#### Consensus Theorem

- $\Rightarrow T9a: (X \bullet Y) + (X' \bullet Z) + (Y \bullet Z) = (X \bullet Y) + (X' \bullet Z)$

- $\rightarrow T9b: (X+Y) \bullet (X'+Z) \bullet (Y+Z) = (X+Y) \bullet (X'+Z)$

|     |   |            |    |     |    | (XY)+  |       |     |      |     | (X+Y)•  |        |

|-----|---|------------|----|-----|----|--------|-------|-----|------|-----|---------|--------|

|     |   |            |    |     |    | (X'Z)+ | (XY)+ |     |      |     | (X'+Z)• | (X+Y)• |

| Х Ү | Z | <b>X</b> ′ | XY | X'Z | YZ | (YZ)   | (X'Z) | X+Y | X'+Z | Y+Z | (Y+Z)   | (X'+Z) |

| 0 0 | 0 | 1          | 0  | 0   | 0  | 0      | 0     | 0   | 1    | 0   | 0       | 0      |

| 0 0 | 1 | 1          | 0  | 1   | 0  | 1      | 1     | 0   | 1    | 1   | 0       | 0      |

| 0 1 | 0 | 1          | 0  | 0   | 0  | 0      | 0     | 1   | 1    | 1   | 1       | 1      |

| 0 1 | 1 | 1          | 0  | 1   | 1  | 1      | 1     | 1   | 1    | 1   | 1       | 1      |

| 1 0 | 0 | 0          | 0  | 0   | 0  | 0      | 0     | 1   | 0    | 0   | 0       | 0      |

| 1 0 | 1 | 0          | 0  | 0   | 0  | 0      | 0     | 1   | 1    | 1   | 1       | 1      |

| 1 1 | 0 | 0          | 1  | 0   | 0  | 1      | 1     | 1   | 0    | 1   | 0       | 0      |

| 1 1 | 1 | 0          | 1  | 0   | 1  | 1      | 1     | 1   | 1    | 1   | 1       | 1      |

## **MORE THEOREMS?**

- Shannon's expansion theorem (also very important!)

- $\rightarrow$  T10a:  $f(X_1, X_2, ..., X_{n-1}, X_n) =$

- $(X_1' \bullet f(0, X_2, ..., X_{n-1}, X_n)) + (X_1 \bullet f(1, X_2, ..., X_{n-1}, X_n))$

- Can be taken further:

- $f(X_1, X_2, ..., X_{n-1}, X_n) = (X_1' \bullet X_2' \bullet f(0, 0, ..., X_{n-1}, X_n))$

- +  $(X_1 \bullet X_2' \bullet f(1,0,...,X_{n-1},X_n)) + (X_1' \bullet X_2 \bullet f(0,1,...,X_{n-1},X_n))$

- + $(X_1 \bullet X_2 \bullet f(1,1,...,X_{n-1},X_n))$

- Can be taken even further:

- $f(X_1, X_2, ..., X_{n-1}, X_n) = (X_1' \bullet X_2' \bullet ... \bullet X_{n-1}' \bullet X_n' \bullet f(0, 0, ..., 0, 0))$

- +  $(X_1 \bullet X_2' \bullet ... \bullet X_{n-1}' \bullet X_n' \bullet f(1,0,...,0,0)) + ...$

- +  $(X_1 \bullet X_2 \bullet ... \bullet X_{n-1} \bullet X_n \bullet f(1,1,...,1,1))$

- $\rightarrow$  T10b:  $f(X_1, X_2, ..., X_{n-1}, X_n) =$

- $(X_1+f(0,X_2,...,X_{n-1},X_n)) \bullet (X_1'+f(1,X_2,...,X_{n-1},X_n))$

- Can be taken further as in the case of T10a

- We'll see significance of Shannon's expansion theorem later

## **SWITCHING FUNCTIONS**

## Objective:

Understand the logic functions of the digital circuits

# Course Outcomes(CAEC020.05):

**Describe** minimization techniques and other optimization techniques for Boolean formulas in general and digital circuits.

## SWITCHING FUNCTIONS

- For n variables, there are 2<sup>n</sup> possible combinations of values

- > From all 0s to all 1s

- There are 2 possible values for the output of a combination of values of n variables

function of a given

- > 0 and 1

- There are 2<sup>2<sup>n</sup></sup> different switching functions for

n variables

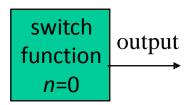

## SWITCHING FUNCTION EXAMPLES

*n*=0 (no inputs)

$$\Rightarrow$$

$2^{2^n} = 2^{2^0} = 2^1 = 2$

- Output can be either 0 or 1

•

$$n=1$$

(1 input, A)  $\implies 2^{2^n} = 2^{2^1} = 2^2 = 4$

> Output can be 0, 1, A, or A'

A

$$\xrightarrow{\text{switch}}$$

output  $n=1$

$$f_0 = 0$$

$$f_1 = A'$$

$$f_2 = A$$

$$f_3 = 1$$

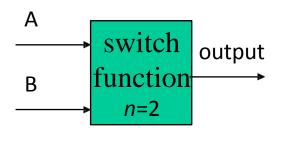

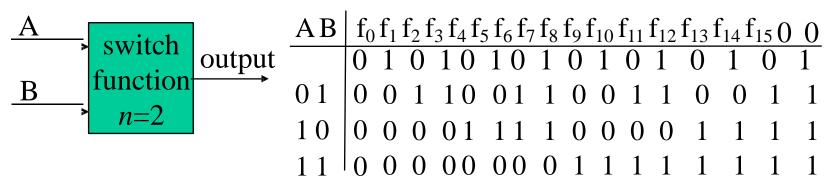

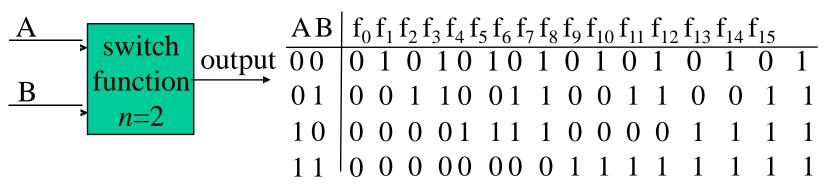

## SWITCHING FUNCTION EXAMPLES

$$\Rightarrow$$

$2^{2^n} = 2^{2^2} = 2^4 = 16$

$$f_0 = 0$$

$f_1 = A'B' = (A+B)'$

$f_2 = A'B$

$f_3 = A'B' + A'B = A'(B'+B) = A'$

logic 0

NOT-OR or NOR

invert A

Most frequently used

Less frequently used

Least frequently used

## **SWITCHING FUNCTION EXAMPLES**

•

$$n=2$$

(2 inputs, A and B)  $\Rightarrow 2^{2^n} = 2^{2^2} = 2^4 = 16$

$$f_4$$

= AB'

$f_5$  = A'B'+AB' = (A'+A)B' = B'

$f_6$  = A'B+AB'

$f_7$  = A'B'+A'B+AB' = A'(B'+B)+(A'+A)B'

= A'+B' = (AB)'

Most frequently used Less frequently used

invert B exclusive-OR

NOT-AND or NAND

Least frequently used

6

#### SWITCHING FUNCTION EXAMPLES

•

$$n=2$$

(2 inputs, A and B)  $\Rightarrow 2^{2^n} = 2^{2^2} = 2^4 = 16$

$$f_8 = AB$$

$f_9 = A'B' + AB$

$f_{10} = A'B + AB = (A' + A)B = B$

$f_{11} = A'B' + A'B + AB = A'(B' + B) + (A' + A)B = A' + B$

AND

exclusive-NOR

buffer B

Most frequently used

Less frequently used

Least frequently used

#### SWITCHING FUNCTION EXAMPLES

•

$$n=2$$

(2 inputs, A and B)  $\Rightarrow 2^{2^n} = 2^{2^2} = 2^4 = 16$

$$f_{12} = AB' + AB = A(B' + B) = A$$

buffer A

$f_{13} = A'B' + AB' + AB = A(B' + B) + A'B' = A + A'B' = A + B'$

$f_{14} = A'B + AB' + AB = A(B' + B) + (A' + A)B = A + B$  OR

$f_{15} = A'B' + A'B + AB' + AB = A'(B' + B) + A(B' + B)$

$= A' + A = 1$  logic 1

Most frequently used

Less frequently used

Least frequently used

8

# **CANONICAL AND STANDERED FORMS**

- Logical functions are generally expressed in terms of different combinations of logical variables with their true forms as well as the complement forms. Binary logic values obtained by the logical functions and logic variables are in binary form. An arbitrary logic function can be expressed in the following forms.

- Sum of the Products (SOP)

- Product of the Sums (POS)

## **CANONICAL AND STANDERED FORMS**

- Product Term: In Boolean algebra, the logical product of several variables on which a function depends is considered to be a product term. In other words, the AND function is referred to as a product term or standard product.

- Sum Term: An OR function is referred to as a sum term.

- **Sum of Products (SOP):** The logical sum of two or more logical product terms is referred to as a sum of products expression

$$Y = AB + BC + AC$$

• **Product of Sums (POS):** Similarly, the logical product of two or more logical sum terms is called a product of sums expression

$$Y = (A + B + C)(\bar{A} + \bar{B} + \bar{C})$$

• **Standard form:** The standard form of the Boolean function is when it is expressed in sum of the products or product of the sums fashion

$$Y = AB + BC + AC$$

# **CANONICAL AND STANDERED FORMS**

- **Nonstandard Form:** Boolean functions are also sometimes expressed in nonstandard forms like  $F = (AB + CD)(\bar{A}\bar{B} + \bar{C}\bar{D})$ , which is neither a sum of products form nor a product of sums form.

- Minterm: A product term containing all n variables of the function in either true or complemented form is called the minterm. Each minterm is obtained by an AND operation of the variables in their true form or complemented form.

- Maxterm: A sum term containing all n variables of the function in either true or complemented form is called the Maxterm. Each Maxterm is obtained by an OR operation of the variables in their true form or complemented form.

- When a Boolean function is expressed as the logical sum of all the minterms from the rows of a truth table, for which the value of the function is 1, it is referred to as the canonical sum of product expression

- For example, if the canonical sum of product form of a three-variable logic function F has the minterms \$\bar{A} \bar{B} \omega h \dagger \omega \omeg

$$F(A,B,C) = \Sigma(3,5,6)$$

$$= m_3 + m_5 + m_6$$

$$= \bar{A}BC + A\bar{B}C + AB\bar{C}$$

- The canonical sum of products form of a logic function can be obtained by using the following procedure:

- Check each term in the given logic function. Retain if it is a minterm, continue to examine the next term in the same manner.

- Examine for the variables that are missing in each product which is not a minterm. If the missing variable in the minterm is X, multiply that minterm with (X+X').

- Multiply all the products and discard the redundant terms.

• Example: Obtain the canonical sum of product form of the following function F(A,B,C) = A + BC

• Solution:

$$F(A,B,C) = A + BC$$

$$= A(B + \overline{B})(C + \overline{C}) + BC(A + \overline{A})$$

$$= (AB + A\overline{B})(C + \overline{C}) + ABC + \overline{A}BC$$

$$= ABC + A\overline{B}C + AB\overline{C} + AB\overline{C} + ABC + \overline{A}BC$$

$$= ABC + AB\overline{C} + AB\overline{C} + ABC = ABC$$

Hence the canonical sum of the product expression of the given function is

$$F(A,B,C) = ABC + A\bar{B}C + AB\bar{C} + A\bar{B}\bar{C} + \bar{A}BC$$

The product of sums form is a method (or form) of simplifying the Boolean expressions of logic gates. In this POS form, all the variables are ORed, i.e. written as sums to form sum terms. All these sum terms are ANDed (multiplied) together to get the product-of-sum form. This form is exactly opposite to the SOP form. So this can also be said as "Dual of SOP form".

$$(A+B) * (A + B + C) * (C +D)$$

$$(A+B)^* (C+D+E)$$

#### POS form can be obtained by

- Writing an OR term for each input combination, which produces LOW output.

- Writing the input variables if the value is 0, and write the complement of the variable if its value is AND the OR terms to obtain the output function.

#### Example:

Boolean expression for majority function F = (A + B + C) (A + B + C') (A + B' + C) (A' + B + C)

| A | В | C | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Now write the input variables combination with high output. F = AB + BC + AC.

- Boolean algebra helps us simplify expressions and circuits

- Karnaugh Map: A graphical technique for simplifying a Boolean expression into either form:

- minimal sum of products (MSP)

- minimal product of sums (MPS)

- Goal of the simplification.

- There are a minimal number of product/sum terms

- Each term has a minimal number of literals

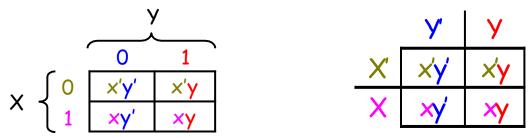

A two-variable function has four possible minterms. We can rearrange these minterms into a Karnaugh map

| × | У | minterm |   |                | >    | <b>/</b> |

|---|---|---------|---|----------------|------|----------|

| 0 | 0 | ×'y'    |   |                | 0    | 1        |

| 0 | 1 | ×'y     |   | So             | x'y' | x'v      |

| 1 | 0 | ×y'     | X | $\int_{1}^{3}$ | XV'  | XV       |

| 1 | 1 | хy      |   | <u> </u>       | /    | ,        |

- Now we can easily see which minterms contain common literals

- Minterms on the left and right sides contain y' and y respectively

- $\circ$  Minterms in the top and bottom rows contain x' and x respectively

- Make as few rectangles as possible, to minimize the number of products in the final expression.

- Make each rectangle as large as possible, to minimize the number of literals in each term.

- Rectangles can be overlapped, if that makes them larger

- The most difficult step is grouping together all the 1s in the K-map

- Make rectangles around groups of one, two, four or eight 1s

- All of the 1s in the map should be included in at least one rectangle. Do not include any of the 0s

- Each group corresponds to one product term

|   |   |   | • | У |

|---|---|---|---|---|

|   | 0 | 1 | 0 | 0 |

| X | 0 | 1 | 1 | 1 |

| · |   | Z |   |   |

Maxterms are grouped to find minimal PoS expression yz 01 11 10

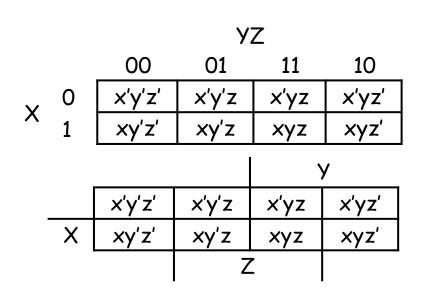

# 3 Variable k-Map

- Let's consider simplifying f(x,y,z) = xy + y'z + xz

- You should convert the expression into a sum of minterms form,

- The easiest way to do this is to make a truth table for the function, and then read off the minterms

- You can either write out the literals or use the minterm shorthand

- Here is the truth table and sum of minterms for our example:

| × | У | Z | f(x,y,z) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | 0        |

| 0 | 1 | 1 | 0        |

| 1 | 0 | 0 | 0        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | 1        |

| 1 | 1 | 1 | 1        |

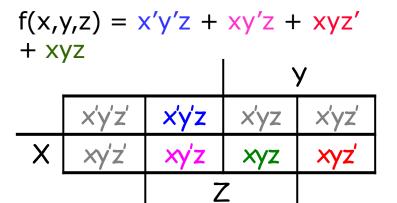

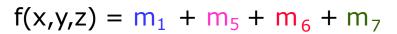

$$f(x,y,z) = x'y'z + xy'z + xyz' + xyz' + xyz = m_1 + m_5 + m_6 + m_7$$

• For a three-variable expression with inputs x, y, z, the arrangement of minterms is more tricky:

- Here is the filled in K-map, with all groups shown

- The magenta and green groups overlap, which makes each of them as

- large as possible

- Minterm m<sub>6</sub> is in a group all by its lonesome

The final MSP here is x'z + y'z + xyz'

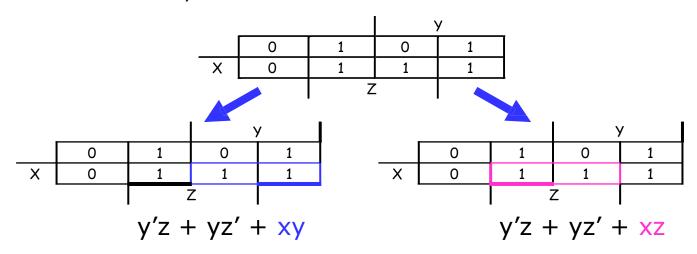

There may not necessarily be a unique MSP. The K-map below yields two

valid and equivalent MSPs, because there are two possible ways to include minterm m<sub>7</sub>

Remember that overlapping groups is possible, as shown above

Maxterms are grouped to find minimal PoS expression yz 01 11 10

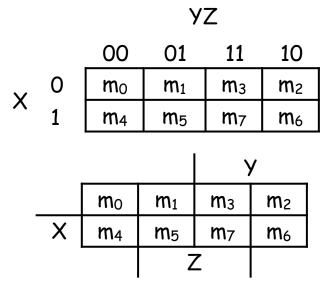

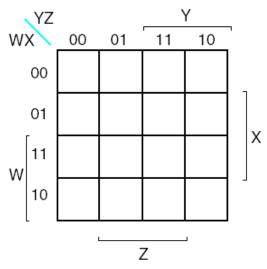

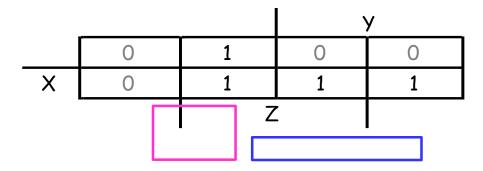

- We can do four-variable expressions too!

- The minterms in the third and fourth columns, and in the third and

- fourth rows, are switched around.

- Again, this ensures that adjacent squares have common literals

- Grouping minterms is similar to the three-variable case, but:

- You can have rectangular groups of 1, 2, 4, 8 or 16 minterms

- You can wrap around all four sides

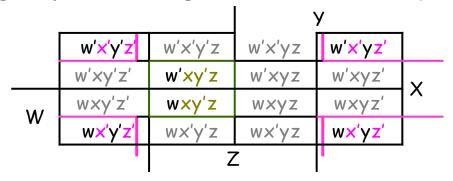

|    |          |         | ,      | У       |   |

|----|----------|---------|--------|---------|---|

|    | w'x'y'z' | w'x'y'z | w'x'yz | w'x'yz' | ] |

|    | w'xy'z'  | w'xy'z  | w'xyz  | w'xyz'  | X |

| W  | wxy'z'   | wxy'z   | wxyz   | wxyz'   |   |

| VV | wx'y'z'  | wx'y'z  | wx'yz  | wx'yz'  |   |

|    | Z        |         |        |         | _ |

|    |                        |                        | }                      | /                      | _ |

|----|------------------------|------------------------|------------------------|------------------------|---|

|    | $m_0$                  | m <sub>1</sub>         | <b>m</b> 3             | m <sub>2</sub>         |   |

|    | m <sub>4</sub>         | <b>m</b> 5             | <b>m</b> <sub>7</sub>  | <b>m</b> 6             | X |

| W  | <b>m</b> <sub>12</sub> | <b>m</b> <sub>13</sub> | <b>m</b> <sub>15</sub> | m <sub>14</sub>        |   |

| VV | m <sub>8</sub>         | <b>m</b> 9             | m <sub>11</sub>        | <b>m</b> <sub>10</sub> |   |

|    |                        | 7                      | <u> </u>               |                        | - |

The express ion isalready a sum of minterms, so her e'sthe K -map:

|    |                        |                        |                        | <u> </u>               | - |

|----|------------------------|------------------------|------------------------|------------------------|---|

|    | <b>m</b> <sub>0</sub>  | $m_1$                  | <b>m</b> <sub>3</sub>  | <b>m</b> 2             |   |

|    | m <sub>4</sub>         | <b>m</b> 5             | $m_7$                  | m <sub>6</sub>         | _ |

| W  | <b>m</b> <sub>12</sub> | <b>m</b> <sub>13</sub> | <b>m</b> <sub>15</sub> | m <sub>14</sub>        | ^ |

| VV | <b>m</b> 8             | m <sub>9</sub>         | m <sub>11</sub>        | <b>m</b> <sub>10</sub> |   |

|    |                        | 7                      | 7                      |                        | - |

We can make the following groups, resulting in the MSP x'z' + xy'z

Example: Simplify  $m_0+m_2+m_5+m_8+m_{10}+m_{13}$

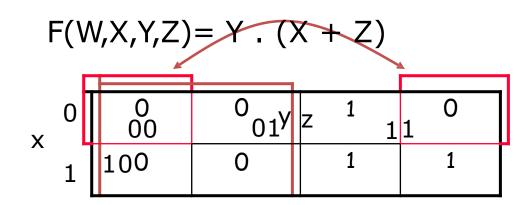

•  $F(W,X,Y,Z) = \prod_{X+Y+Z} M(0,1,2,4,5)$ x  $O(X+Y+Z) \times Y+Y+Z' \times Y+Z' \times Y+Y+Z' \times Y+Z' \times Y+Y+Z' \times Y+Z' \times Y+Z'$

# Objective:

Understand the 5-Variable K-map

Course Outcomes(CAEC020.06):

Evaluate the functions using various types of minimizing algorithms like Karanaugh map method.

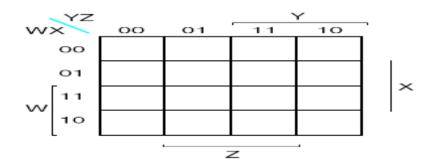

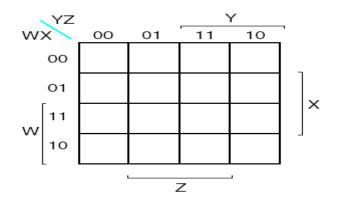

# 5-variable K-map

|    | ΥZ |    |    | `  | Y  |   |

|----|----|----|----|----|----|---|

| W  | ×  | 00 | 01 | 11 | 10 |   |

|    | 00 |    |    |    |    | _ |

|    | 01 |    |    |    |    |   |

| w  | 11 |    |    |    |    | × |

| vv | 10 |    |    |    |    |   |

|    |    |    |    | z  | _  |   |

|   | V <sub>F</sub> 0 <sub>y</sub> |                        |                 |                        |                        |   |

|---|-------------------------------|------------------------|-----------------|------------------------|------------------------|---|

|   |                               | m <sub>0</sub>         | m <sub>1</sub>  | m <sub>3</sub>         | m <sub>2</sub>         |   |

|   |                               | <b>m</b> 4             | <b>m</b> 5      | <b>m</b> 7             | <b>m</b> 6             | X |

|   | <b>/</b>                      | <b>m</b> <sub>12</sub> | m <sub>13</sub> | m <sub>15</sub>        | m <sub>14</sub>        |   |

| v | /V                            | m <sub>8</sub>         | <b>m</b> 9      | <b>m</b> <sub>11</sub> | <b>m</b> <sub>10</sub> |   |

|   |                               |                        | 7               | 7                      |                        | - |

|    | V= 1 <u>Y</u> |                 |          |                 |             |

|----|---------------|-----------------|----------|-----------------|-------------|

|    | $m_{16}$      | m <sub>17</sub> | $m_{19}$ | $m_8$           |             |

|    | $m_{20}$      | m <sub>21</sub> | $m_{23}$ | m <sub>22</sub> | <b>&gt;</b> |

| W  | $m_{28}$      | m <sub>29</sub> | $m_{31}$ | m <sub>30</sub> | ^           |

| VV | $m_{24}$      | m <sub>25</sub> | $m_{27}$ | m <sub>26</sub> |             |

|    |               |                 | 7        |                 | -           |

In our example, we can write f(x,y,z) in two equivalent ways

|   |                |            | `                     | /              |

|---|----------------|------------|-----------------------|----------------|

|   | $m_0$          | $m_1$      | <b>m</b> <sub>3</sub> | m <sub>2</sub> |

| X | m <sub>4</sub> | <b>m</b> 5 | <b>m</b> <sub>7</sub> | <b>m</b> 6     |

| · |                | Z          |                       |                |

In either case, the resulting K-map is shown below

$\begin{array}{ll} m(4,6,12,14,20,22,28,30) \\ + \ V'W'Y' & \Sigma m(0,1,4,5) \\ + \ W'Y'Z' & \Sigma m(0,4,16,20) \\ + \ VWXY & \Sigma m(30,31) \\ + \ V'WX'YZ & m11 \end{array}$

# DON'T CARE CONDITION

- You don't always need all 2<sup>n</sup> input combinations in ann-variable function

- If you can guarantee that certain input combinations never occur

- If some outputs aren't used in the rest of the circuit

| × | У | Z | f(x,y,z) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | X        |

| 0 | 1 | 1 | 0        |

| 1 | 0 | 0 | 0        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | X        |

| 1 | 1 | 1 | 1        |

We mark don't-care outputs in truth tables and K-maps with Xs.

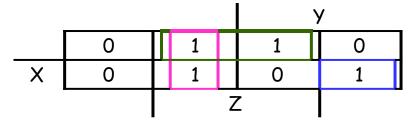

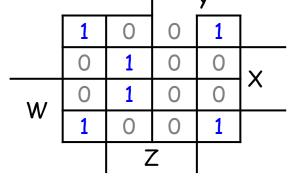

# DON'T CARE CONDITION

Find a MSP for

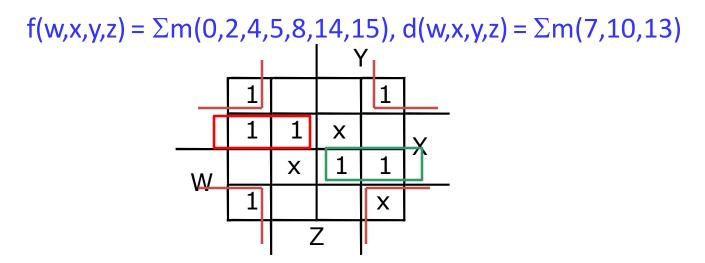

$$f(w,x,y,z) = \sum m(0,2,4,5,8,14,15), d(w,x,y,z) = \sum m(7,10,13)$$

This notation means that input combinations wxyz = 0111, 1010 and 1101(corresponding to minterms  $m_7$ ,  $m_{10}$  and  $m_{13}$ ) are unused.

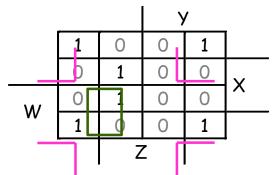

|   |   |   | У |   | _ |

|---|---|---|---|---|---|

|   | 1 | 0 | 0 | 1 |   |

|   | 1 | 1 | × | 0 | X |

| W | 0 | × | 1 | 1 |   |

|   | 1 | 0 | 0 | × |   |

|   |   | Z |   |   | _ |

# DON'T CARE CONDITIONS

Find a MSP for:

$$f(w,x,y,z) = x'z' + w'xy' + wxy$$

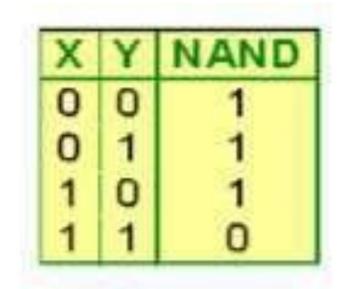

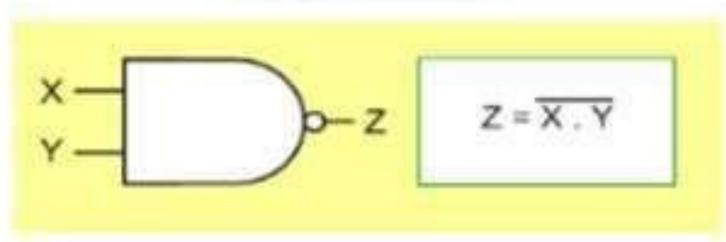

- The objectives of this lesson are to learn about:

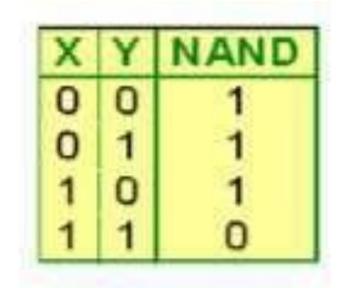

- 1. Universal gates NAND and NOR.

- 2. How to implement NOT, AND, and OR gate using NAND gates only.

- 3. How to implement NOT, AND, and OR gate using NOR gates only.

- 4. Equivalent gates.

| X | Υ | NOR |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 0   |

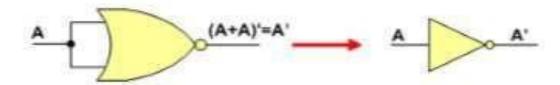

1. All NAND input pins connect to the input signal A gives an output A'.

One NAND input pin is connected to the input signal A while all other input pins are connected to logic 1. The output will be A'.

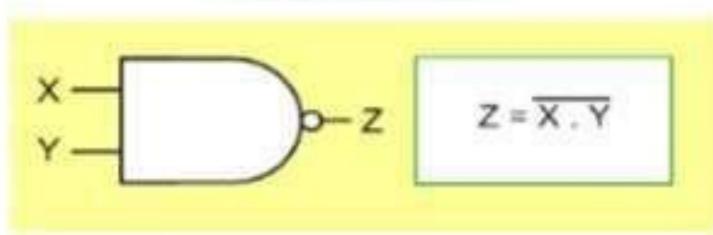

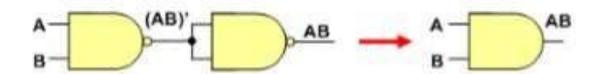

#### Implementing AND Using only NAND Gates

An AND gate can be replaced by NAND gates as shown in the figure (The AND is replaced by a NAND gate with its output complemented by a NAND gate inverter).

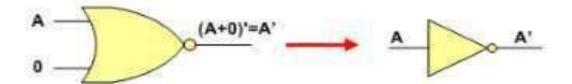

1. All NOR input pins connect to the input signal A gives an output A'.

2. One NOR input pin is connected to the input signal A while all other input pins are connected to logic 0. The output will be A'.

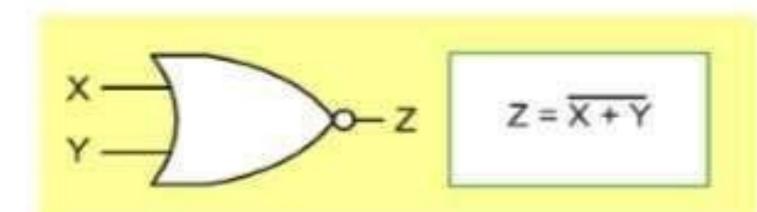

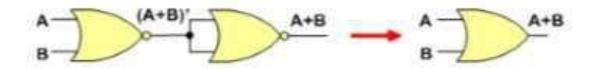

#### Implementing OR Using only NOR Gates

An OR gate can be replaced by NOR gates as shown in the figure (The OR is replaced by a NOR gate with its output complemented by a NOR gate inverter)

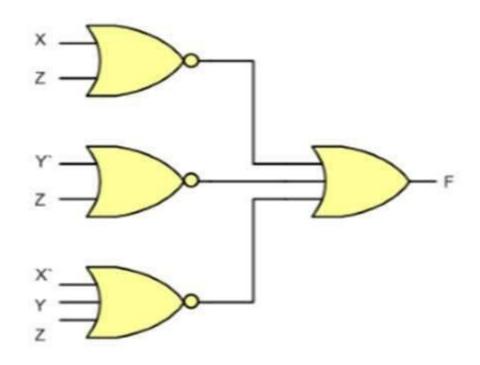

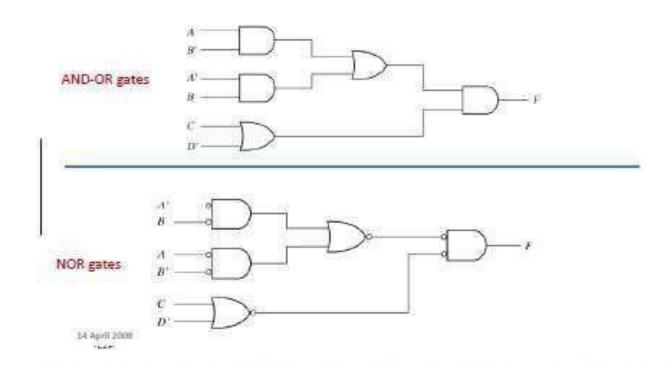

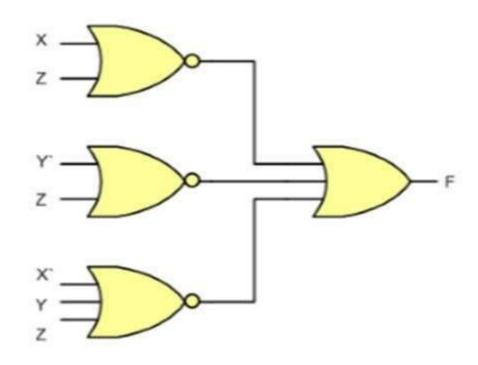

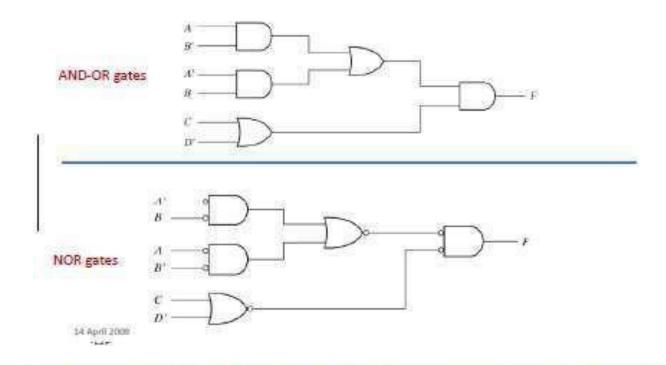

#### **OR NAND Function:**

$$F = (X + Z).(\overline{Y} + Z).(\overline{X} + Y + Z)$$

or  $\overline{F} = (X + Z)(\overline{Y} + Z)(\overline{X} + Y + Z)$

Since 'F' is in POS form Z can be implemented by using NOR NOR circuit. Similarly complementing the output we can get F,or by using NOR –OR Circuit as shown in figure

It can also be implemented using OR-NAND circuit as it is equivalent to NOR-OR circuit

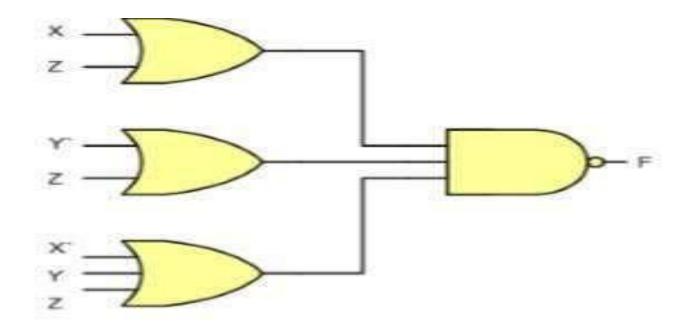

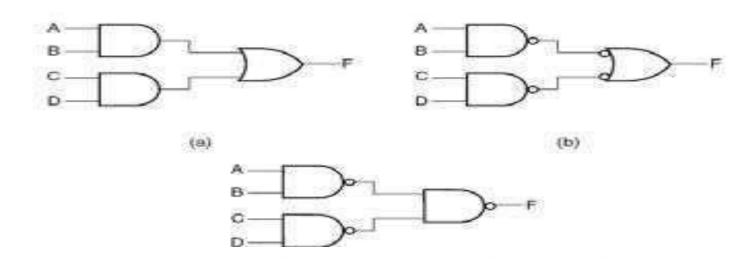

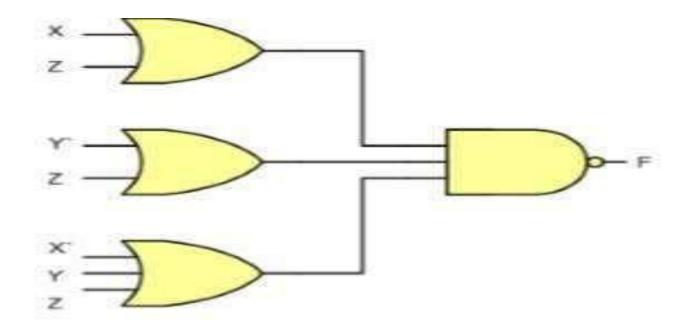

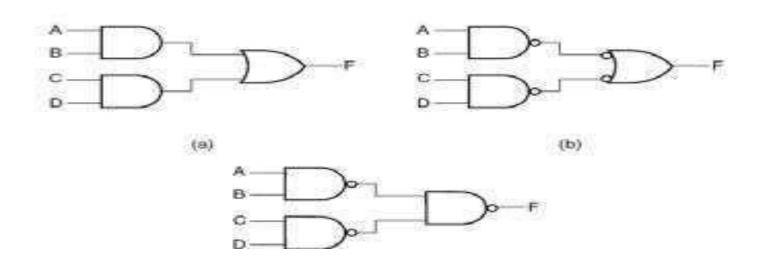

- Example1: implement the following function F = AB + CD

- The implementation of Boolean functions with NAND gates requires that the functions be in

- sum of products (SOP) form.

- The Rule

- This function can This function can be implemented by three different ways as shown in the circuit diagram a, b, c

Example 2: Consider the following Boolean function, implement the circuit diagram by using multilevel NOR gate. F = (AB' + A'B)i(C + D')

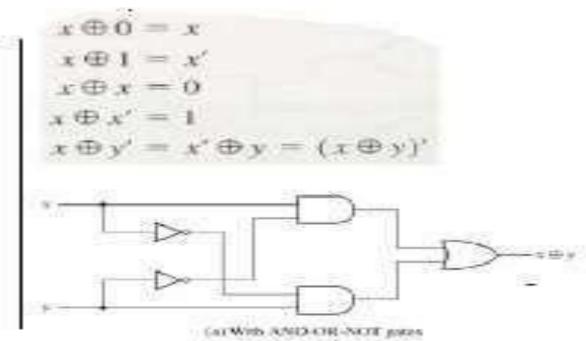

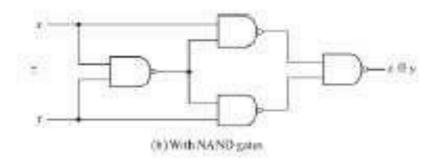

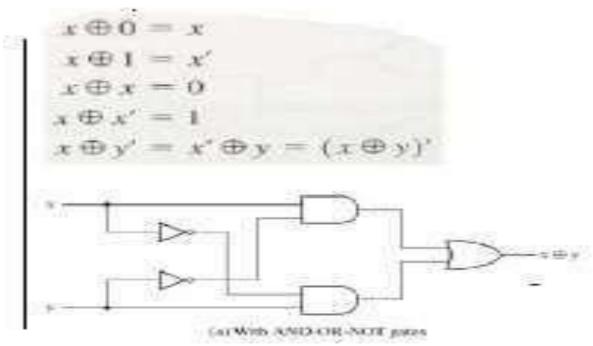

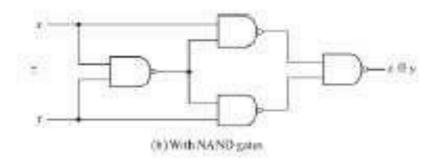

#### **Exclusive-OR (XOR) Function:**

XOR:

$$y = xy' + x'y$$

#### **Exclusive-NOR = equivalence**

$$(x y)' = (xy' + x'y)'$$

=  $(x' + y)(x + y') = x'y' + xy$

#### **OR NAND Function:**

$$F = (X + Z).(\overline{Y} + Z).(\overline{X} + Y + Z) \text{ or }$$

$$\overline{F} = (X + Z)(\overline{Y} + Z)(\overline{X} + Y + Z)$$

Since 'F' is in POS form Z can be implemented by using NOR NOR circuit. Similarly complementing the output we can get F,or by using NOR –OR Circuit as shown in figure

It can also be implemented using OR-NAND circuit as it is equivalent to NOR-OR circuit

- Example1: implement the following function F = AB +CD

- The implementation of Boolean functions with NAND gates requires that the functions be in

- sum of products (SOP) form.

- The Rule

- This function can This function can be implemented by three different ways as shown in the circuit diagram a, b, c

Example 2: Consider the following Boolean function, implement the circuit diagram by using multilevel NOR gate. F = (AB' + A'B)i(C + D')

#### **Exclusive-OR (XOR) Function:**

XOR: xy' + x'y

#### **Exclusive-NOR = equivalence**

$$= (x' + y)(x + y') = x'y' + xy$$

# COMBINATIONAL CIRCUITS

# UNIT 3

# COMBINATIONAL CIRCUITS

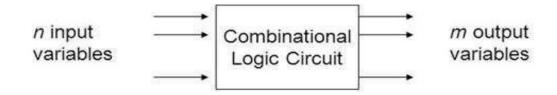

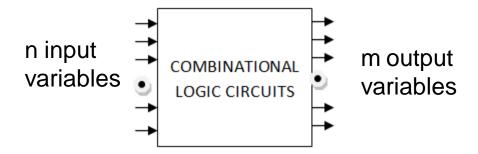

## **Combinational Circuits**

- Combinational circuit is a circuit in which we combine the different gates in the circuit, for example encoder, decoder, multiplexer and demultiplexer.

- Some of the characteristics of combinational circuits are following:

- The output of combinational circuit at any instant of time, depends only on the levels present at input terminals.

- The combinational circuit do not use any memory. The previous state of input does not have any effect on the present state of the circuit.

- A combinational circuit can have an n number of inputs and m number of outputs.

## COMBINATIONAL CIRCUITS

- Block diagram:

- 2<sup>n</sup> possible combinations of input values.

Specific functions :of combinational circuits

Adders, subtractors, multiplexers, comprators, encoder, Decoder.

MSI Circuits and standard cells

## ANALYSIS PROCEDURE

#### **Analysis procedure**

- To obtain the output Boolean functions from a logic diagram, proceed as follows:

- 1. Label all gate outputs that are a function of input variables with arbitrary symbols. Determine the Boolean functions for each gate output.

- Label the gates that are a function of input variables and previously labeled gates with other arbitrary symbols. Find the Boolean functions for these gates.

- 3. Repeat the process outlined in step 2 until the outputs of the circuit are obtained.

## DESIGN PROCEDURE

#### **Design Procedure**

- 1. The problem is stated

- 2. The number of available input variables and required output variables is determined.

- 3. The input and output variables are assigned letter symbols.

- 4. The truth table that defines the required relationship between inputs and outputs is derived.

- 5. The simplified Boolean function for each output is obtained.

- 6. The logic diagram is drawn.

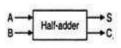

## BINARY ADDERS

#### **ADDERS**

#### Half Adder

A Half Adder is a combinational circuit with two binary inputs (augends and addend bits and two binary outputs (sum and carry bits.) It adds the two inputs (A and B) and produces the sum (S) and the carry (C) bits.

Fig 1:Block diagram

| Inp | uts | Out | puts |

|-----|-----|-----|------|

| A   | В   | s   | С    |

| 0   | 0   | 0   | 0    |

| 0   | 1   | 1   | 0    |

| 1   | 0   | 1   | 0    |

| 1   | 1   | 0   | 1    |

Fig 2:Truth table

## **BINARY ADDERS**

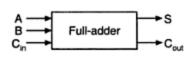

#### **Full Adder**

The full-adder adds the bits A and B and the carry from the previous column called the carry-in  $C_{in}$  and outputs the sum bit S and the carry bit called the carry-out  $C_{out}$ .

Fig 3: block diagram

|    | Inputs |     | Sum | Carry |

|----|--------|-----|-----|-------|

| Α  | В      | Cin | S   | Cout  |

| 0  | 0      | 0   | 0   | 0     |

| 0  | 0      | 1   | 1   | 0     |

| 0  | 1      | 0   | 1   | 0     |

| 0  | 1      | 1   | 0   | 1     |

| 1  | 0      | 0   | 1   | 0     |

| 1  | 0      | 1   | 0   | 1     |

| 1  | 1      | 0   | 0   | 1     |

| 1_ | _1_    | _1_ | 1   | 1_    |

Fig 4:Truth table

$$S = \overline{A}\overline{B}C$$

in  $+ \overline{A}B\overline{C}$  in  $+ AB\overline{C}$  in  $+ ABC$  in  $C$  out  $= \overline{A}BC$  in  $+ A\overline{B}C$  in  $+ AB\overline{C}$  in  $+ ABC$  in  $S = A \oplus B \oplus C$  in  $C$  out  $= AC$  in  $+ BC$  in  $+ AB$

## **BINARY SUBTRACTORS**

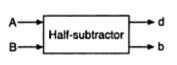

#### **Half Subtractor**

A Half-subtractor is a combinational circuit with two inputs A and B and two outputs difference(d) and barrow(b).

| Inputs |   | Outputs |    |  |

|--------|---|---------|----|--|

| A      | В | d       | b  |  |

| 0      | 0 | 0       | 0  |  |

| 1      | 0 | 1       | 0  |  |

| 1      | 1 | 0       | 0  |  |

| 0      | 1 | 1       | 1_ |  |

Fig 5:Block diagram

Fig 6: Truth table

## BINARY SUBTRACTORS

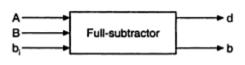

#### **Full subtractor**

The full subtractor perform subtraction of three input bits: the minuend, subtrahend, and borrow in and generates two output bits difference and borrow out.

Difference

Fig 7:Block diagram

Fig 8: Truth table

$$d = \overline{A}\overline{B}b_i + \overline{A}B\overline{b}_i + A\overline{B}\overline{b}_i + ABb_i = A \oplus B \oplus b_i$$

$$b = \overline{A}\overline{B}b_i + \overline{A}B\overline{b}_i + \overline{A}Bb_i + ABb_i = \overline{A}B + (\overline{A \oplus B})b_i$$

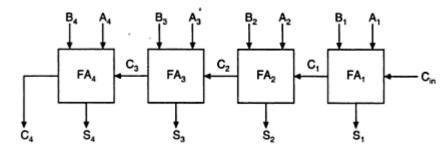

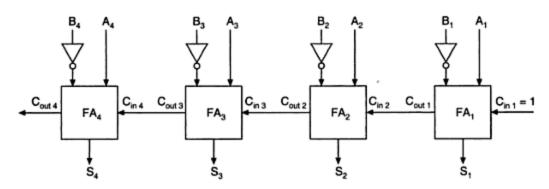

## PARALLEL ADDER AND SUBTRACTOR

A binary parallel adder is a digital circuit that adds two binary numbers in parallel form and produces the arithmetic sum of those numbers in parallel form

Fig 9:parallel adder

Fig 10:parallel subtractor

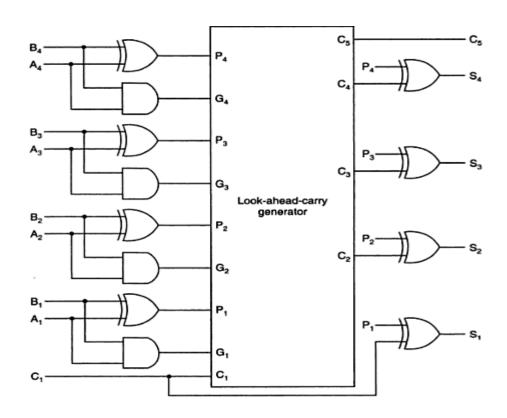

## CARRY LOOK-A- HEAD ADDER

- In parallel-adder, the speed with which an addition can be performed is governed by the time required for the carries to propagate or ripple through all of the stages of the adder.

- The look-ahead carry adder speeds up the process by eliminating this ripple carry delay.

$$S_n = P_n \oplus C_n$$

where  $P_n = A_n \oplus B_n$

$C_{on} = C_{n+1} = G_n + P_n C_n$  where  $G_n = A_n \cdot B_n$

#### CARRY LOOK-A- HEAD ADDER

Fig:1 block diagram

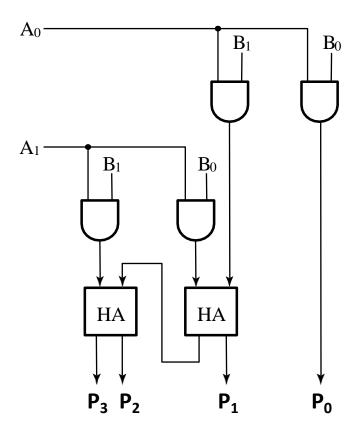

## **BINARY MULTIPLIER**

A binary multiplier is an electronic circuit used in digital electronics, such as a computer, to multiply two binary numbers. It is built using binary adders.

Example: (101 x 011)

Partial products are:  $101 \times 1$ ,  $101 \times 1$ , and  $101 \times 0$

## **BINARY MULTIPLIER**

- We can also make an  $n \times m$  "block" multiplier and use that to form partial products.

- Example: 2 × 2 The logic equations for each partial-product binary digit are shown below

- We need to "add" the columns to get the product bits P0, P1, P2, and P3.

## **BINARY MULTIPLIER**

Fig 1: 2 x 2 multiplier array

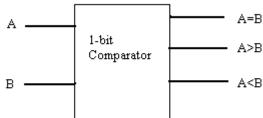

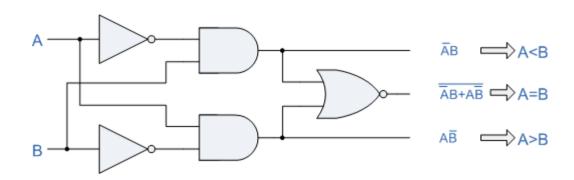

Magnitude comparator takes two numbers as input in binary form and determines whether one number is greater than, less than or equal to the other number.

#### 1-Bit Magnitude Comparator

A comparator used to compare two bits is called a single bit comparator.

Fig:1 Block diagram

| Inputs           |   | Outputs |       |       |

|------------------|---|---------|-------|-------|

| $\boldsymbol{A}$ | В | A > B   | A = B | A < B |

| 0                | 0 | 0       | 1     | 0     |

| 0                | 1 | 0       | 0     | 1     |

| 1                | 0 | 1       | 0     | 0     |

| 1                | 1 | 0       | 1     | 0     |

Fig 2:Logic diagram of 1-bit comparator

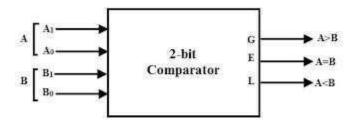

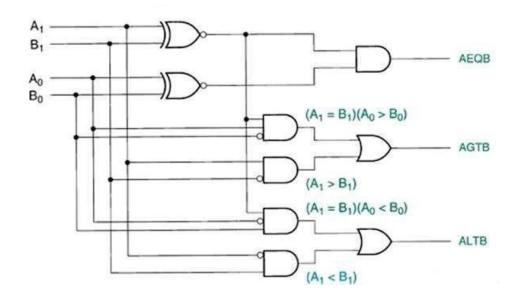

## • 2 Bit magnitude comparator

Fig: 3 Block diagram

|                | Inp   | outs           |                |     | Outputs |                   |

|----------------|-------|----------------|----------------|-----|---------|-------------------|

| $\mathbf{A}_1$ | $A_0$ | B <sub>1</sub> | B <sub>0</sub> | A>B | A=B     | A <b< th=""></b<> |

| 0              | 0     | 0              | 0              | 0   | 1       | 0                 |

| 0              | 0     | 0              | 1              | 0   | 0       | 1                 |

| 0              | 0     | 1.             | 0              | 0   | 0       | 1                 |

| 0              | 0     | 1              | 1              | 0   | 0       | 1                 |

| 0              | 1     | 0              | 0              | 1   | 0       | 0                 |

| 0              | 1     | 0              | 1              | 0   | 1       | 0                 |

| 0              | 1     | 1.             | 0              | 0   | 0       | 1                 |

| 0              | 1     | 1              | 1              | 0   | 0       | 1                 |

| 1              | 0     | 0              | 0              | 1   | 0       | 0                 |

| 1              | 0     | 0              | 1              | 1   | 0       | 0                 |

| 1              | 0     | 1.             | 0              | 0   | 1       | 0                 |

| 1              | 0     | 1              | 1              | 0   | 0       | 1                 |

| 1              | 1     | 0              | 0              | 1   | 0       | 0                 |

| 1              | 1     | 0              | 1              | 1   | 0       | 0                 |

| 1              | 1     | 1.             | 0              | 1   | 0       | 0                 |

| 1              | 1     | 1              | 1              | 0   | 1       | 0                 |

Fig: 4 Truth table

Fig 5:Logic diagram of 2-bit comparator

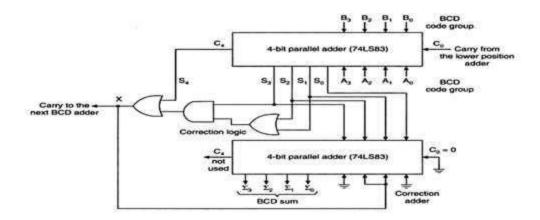

#### BCD ADDER

#### **BCD Adder**

- Perform the addition of two decimal digits in BCD, together with an input carry from a previous stage.

- When the sum is 9 or less, the sum is in proper BCD form and no correction is needed.

- When the sum of two digits is greater than 9, a correction of 0110 should be added to that sum, to produce the proper BCD result.

This will produce a carry to be added to the next decimal position.

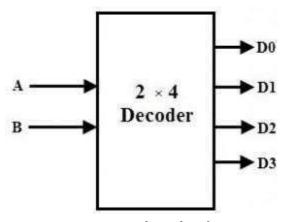

#### DECODER

- A binary decoder is a combinational logic circuit that converts binary information from the n coded inputs to a maximum of 2<sup>n</sup>unique outputs.

- We have following types of decoders 2x4,3x8,4x16....

#### 2x4 decoder

Fig 1: Block diagram

| Inputs |   | Output |    |    |    |  |

|--------|---|--------|----|----|----|--|

| Α      | В | D.     | D. | D: | D, |  |

| 0      | 0 | 1      | 0  | 0  | 0  |  |

| 0      | 1 | 0      | 1  | 0  | 0  |  |

| 0      | 1 | 0      | 0  | 1  | 0  |  |

| 1      | 1 | 0      | 0  | 0  | 1  |  |

Fig 2:Truth table

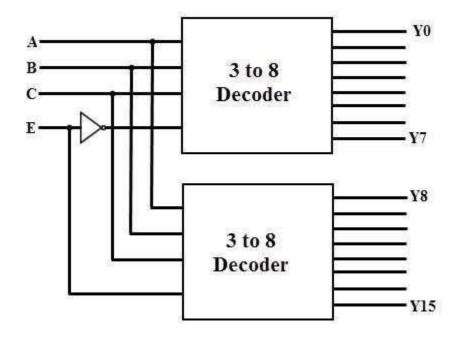

### **DECODERS**

Higher order decoder implementation using lower order.

Ex:4x16 decoder using 3x8 decoders

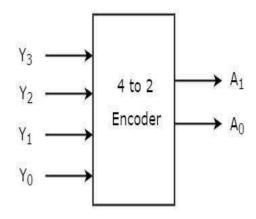

### **ENCODERS**

- An Encoder is a combinational circuit that performs the reverse operation of Decoder. It has maximum of 2<sup>n</sup> input lines and 'n' output lines.

- It will produce a binary code equivalent to the input, which is active High.

Fig 1:block diagram of 4x2 encoder

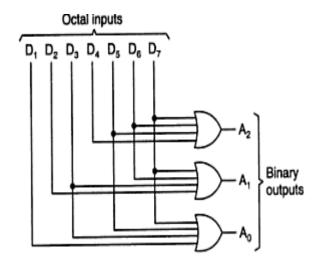

### **ENCODERS**

### Octal to binary encoder

| Octal                                              | digits | Binary         |    |                |  |

|----------------------------------------------------|--------|----------------|----|----------------|--|

|                                                    |        | A <sub>2</sub> | Α, | A <sub>0</sub> |  |

| D <sub>0</sub>                                     | 0      | 0              | 0  | 0              |  |

| D <sub>1</sub>                                     | 1      | 0              | 0  | 1              |  |

| $D_2$                                              | 2      | 0              | 1  | 0              |  |

| $\overline{D_3}$                                   | 3      | 0              | 1  | 1              |  |

| D <sub>4</sub>                                     | 4      | 1              | 0  | 0              |  |

|                                                    | 5      | 1              | 0  | 1              |  |

| $D_6$                                              | 6      | 1              | 1  | 0              |  |

| D <sub>5</sub><br>D <sub>6</sub><br>D <sub>7</sub> | 7      | 1              | 1  | 1              |  |

Fig 2:Truth table

Fig 3: Logic diagram

## **ENCODER**

### **Priority encoder**

A 4 to 2 priority encoder has four inputs  $Y_3$ ,  $Y_2$ ,  $Y_1$  &  $Y_0$  and two outputs  $A_1$  &  $A_0$ . Here, the input,  $Y_3$  has the highest priority, whereas the input,  $Y_0$  has the lowest priority.

|            | Inp            | uts            |       | Outputs               |                       |   |

|------------|----------------|----------------|-------|-----------------------|-----------------------|---|

| <b>Y</b> 3 | Y <sub>2</sub> | Y <sub>1</sub> | $Y_0$ | <b>A</b> <sub>1</sub> | <b>A</b> <sub>0</sub> | v |

| 0          | 0              | 0              | 0     | 0                     | 0                     | 0 |

| 0          | 0              | 0              | 1     | 0                     | 0                     | 1 |

| 0          | 0              | 1              | х     | 0                     | 1                     | 1 |

| 0          | 1              | х              | х     | 1                     | 0                     | 1 |

| 1          | х              | х              | х     | 1                     | 1                     | 1 |

Fig 4:Truth table

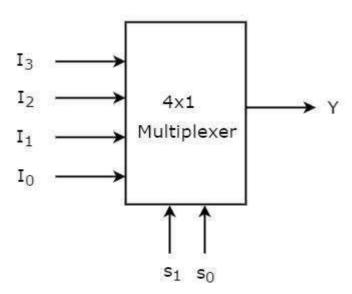

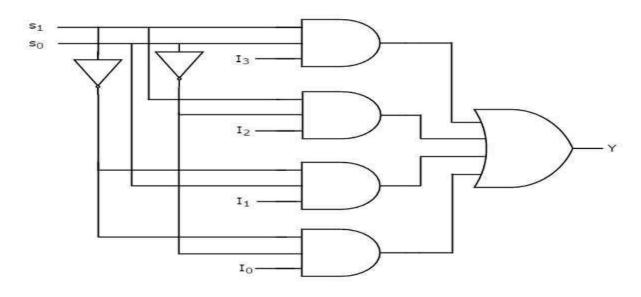

- Multiplexer is a combinational circuit that has maximum of 2<sup>n</sup> data inputs, 'n' selection lines and single output line. One of these data inputs will be connected to the output based on the values of selection lines.

- We have different types of multiplexers 2x1,4x1,8x1,16x1,32x1......

Fig 1: Block diagram

| Selection | Selection Lines |                |  |  |  |

|-----------|-----------------|----------------|--|--|--|

| $s_1$     | S <sub>0</sub>  | Y              |  |  |  |

| 0         | 0               | IQ             |  |  |  |

| 0         | 1               | l <sub>1</sub> |  |  |  |

| 1         | 0               | I2             |  |  |  |

| 1         | 1               | I <sub>3</sub> |  |  |  |

Fig 2: Truth table

Fig 3: Logic diagram

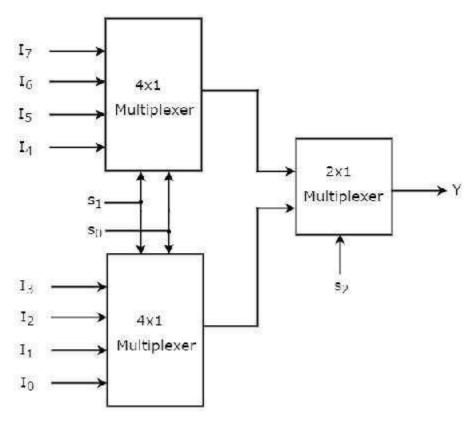

Now, let us implement the higher-order Multiplexer using lower-order Multiplexers.

• Ex: 8x1 Multiplexer

Fig 3: 8x1 Multiplexer diagram

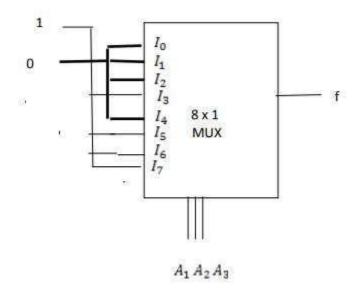

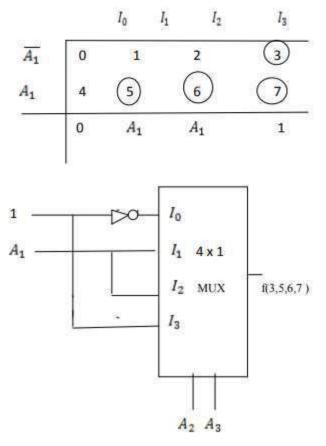

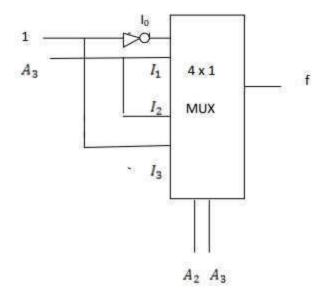

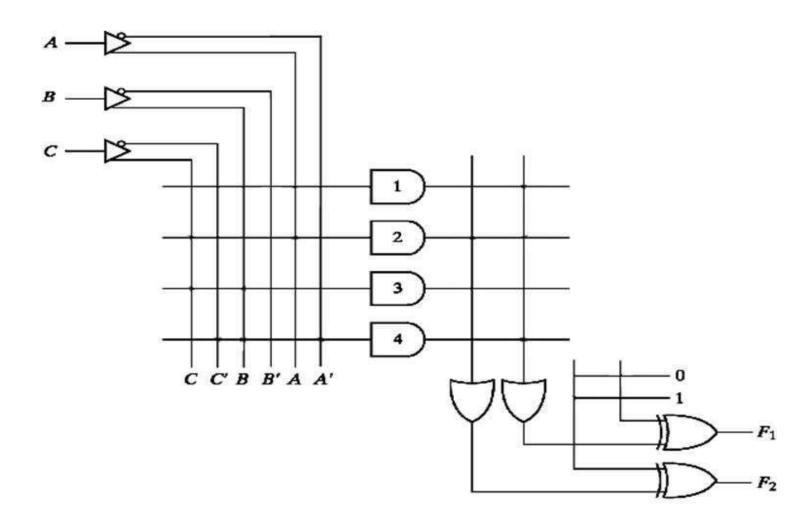

- Implementation of Boolean function using multiplexer

- $f(A1, A2, A3) = \Sigma(3,5,6,7)$  implementation using 8x1 mux

$f(A1, A2, A3) = \Sigma(3,5,6,7)$  implementation using 4x1 mux **Method:1**

| Minterms | A <sub>1</sub> | $A_2$ | $A_3$ | f |

|----------|----------------|-------|-------|---|

| 0        | 0              | 0     | 0     | 0 |

| 1        | 0              | 0     | 1     | 0 |

| 2        | 0              | 1     | 0     | 0 |

| 3        | 0              | 1     | 1     | 1 |

| 4        | 1              | 0     | 0     | 0 |

| 5        | 1              | 0     | 1     | 1 |

| 6        | 1              | 1     | 0     | 1 |

| 7        | 1              | 1     | 1     | 1 |

### Method:2

| Minterm | $A_1$ | $A_2$ | $A_3$ | 12. | f         |                |

|---------|-------|-------|-------|-----|-----------|----------------|

| 0       | 0     | 0     | 0     | 0   |           |                |

| I       | 0     | 0     | 1     | 0   | f=0       | I <sub>0</sub> |

| 2       | 0     | 1     | 0     | 0   | j.        |                |

| 3       | 0     | 1     | 1     | 1   | $f = A_3$ | $I_1$          |

| 4       | 1     | 0     | 0     | 0   | 3         |                |

| 5       | 1     | 0     | 1     | 1   | $f = A_3$ | $I_2$          |

| 6       | 1     | T .   | 0     | 1   | - 3       |                |

| 7       | 1     | 1     | 1     | 1   | f= 1      | $I_3$          |

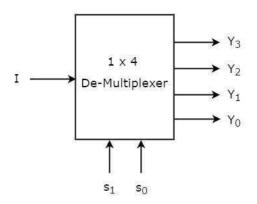

### DEMULTIPLEXER

- A demultiplexer is a device that takes a single input line and routes it to one of several digital output lines.

- A demultiplexer of 2<sup>n</sup> outputs has n select lines, which are used to select which output line to send the input.

- We have 1x2,1x4,8x1.... Demultiplexers.

Fig:1 Block diagram

| Selectio | n Inputs | Outputs |    |    |                |  |  |

|----------|----------|---------|----|----|----------------|--|--|

| $s_1$    | $s_0$    | Υ3      | Y2 | Υ1 | Υ <sub>0</sub> |  |  |

| 0        | 0        | 0       | 0  | 0  | 1              |  |  |

| 0        | 1        | 0       | 0  | I  | 0              |  |  |

| 1        | 0        | 0       | I  | 0  | 0              |  |  |

| 1        | 1        | I       | 0  | 0  | 0              |  |  |

Fig: 2 Truth table

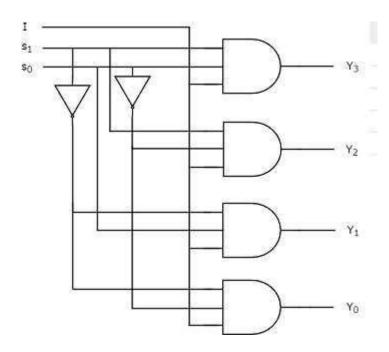

## DEMULTIPLEXER

### Boolean functions for each output as

$$Y_3 = s_1 s_0 I$$

$$Y_2 = s_1 s_0{'}I$$

$$Y_1 = s_1{}'s_0I$$

$$Y_0={s_1}^{\prime}{s_0}^{\prime}I$$

Fig:3 Logic diagram

### CODE CONVERTERS

A code converter is a logic circuit whose inputs are bit patterns representing numbers (or character) in one code and whose outputs are the corresponding representation in a different code.

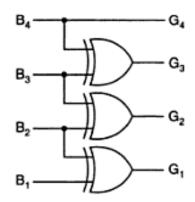

### Design of a 4-bit binary to gray code converter

| B <sub>4</sub> | D     |       |    |                | 4-bit          | a.a.y          |    |

|----------------|-------|-------|----|----------------|----------------|----------------|----|

| -4             | $B_3$ | $B_2$ | В, | G <sub>4</sub> | G <sub>3</sub> | G <sub>2</sub> | G, |

| 0              | 0     | 0     | 0  | 0              | 0              | 0              | 0  |

| 0              | 0     | 0     | 1  | 0              | 0              | 0              | 1  |

| 0              | 0     | 1     | 0  | 0              | 0              | 1              | 1  |

| 0              | 0     | 1     | 1  | 0              | 0              | 1              | 0  |

| 0              | 1     | 0     | 0  | 0              | 1              | 1              | 0  |

| 0              | 1     | 0     | 1  | 0              | 1              | 1              | 1  |

| 0              | 1     | 1     | 0  | 0              | 1              | 0              | 1  |

| 0              | 1     | 1     | 1  | 0              | 1              | 0              | 0  |

| 1              | 0     | 0     | 0  | 1              | 1              | 0              | 0  |

| 1              | 0     | 0     | 1  | 1              | 1              | 0              | 1  |

| 1              | 0     | 1     | 0  | 1              | 1              | 1              | 1  |

| 1              | 0     | 1     | 1  | 1              | 1              | 1              | 0  |

| 1              | 1     | 0     | 0  | 1              | 0              | 1              | 0  |

| 1              | 1     | 0     | 1  | 1              | 0              | 1              | 1  |

| 1              | 1     | 1     | 0  | 1              | 0              | 0              | 1  |

| 1              | 1     | 1     | 1  | 1_             | 0              | 0              | 0  |

Fig:1 Truth table

### **CODE CONVERTERS**

### K-map simplification

$$G_4 = \Sigma m(8, 9, 10, 11, 12, 13, 14, 15) \qquad G_4 = B_4$$

$$G_3 = \Sigma m(4, 5, 6, 7, 8, 9, 10, 11) \qquad G_3 = \overline{B}_4 B_3 + B_4 \overline{B}_3 = B_4 \oplus B_3$$

$$G_2 = \Sigma m(2, 3, 4, 5, 10, 11, 12, 13) \qquad G_2 = \overline{B}_3 B_2 + B_3 \overline{B}_2 = B_3 \oplus B_2$$

$$G_1 = \Sigma m(1, 2, 5, 6, 9, 10, 13, 14) \qquad G_1 = \overline{B}_2 B_1 + B_2 \overline{B}_1 = B_2 \oplus B_1$$

# **CODE CONVERTERS**

Fig: 2 Logic diagram

# **UNIT 4**

# INTRODUCTION TO SEQUENTIAL LOGIC CIRCUITS

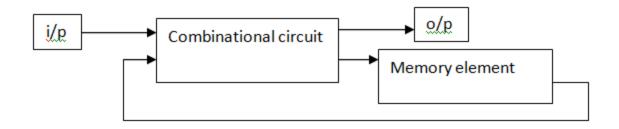

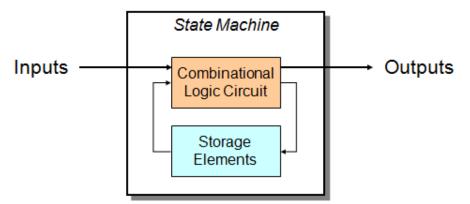

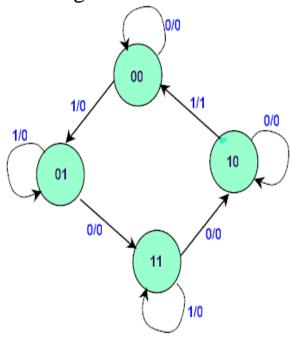

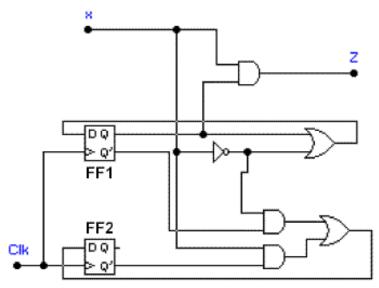

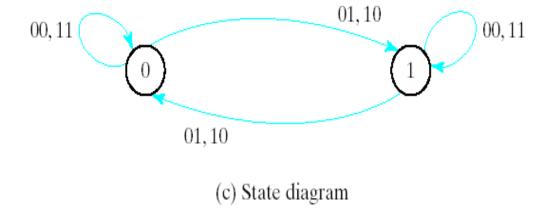

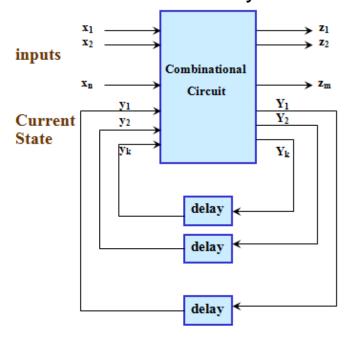

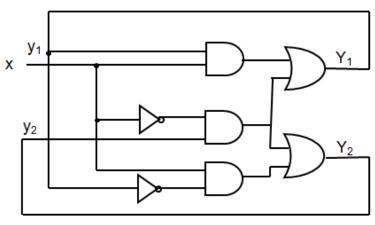

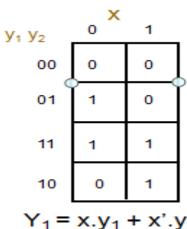

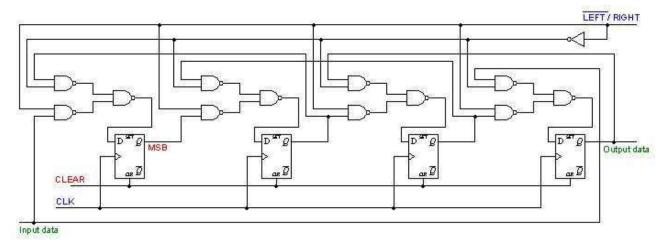

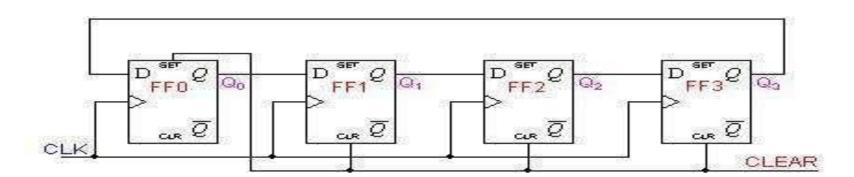

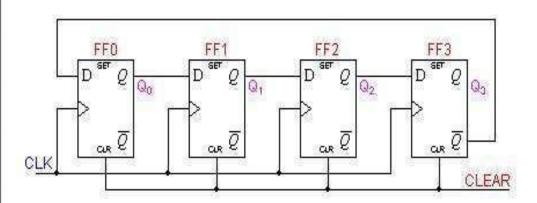

# SEQUENTIAL LOGIC CIRCUITS

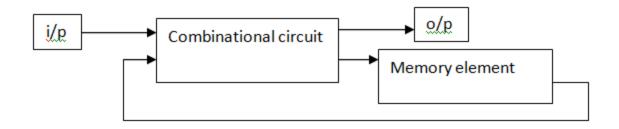

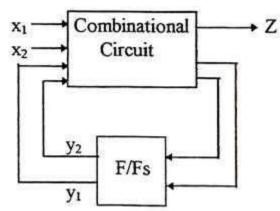

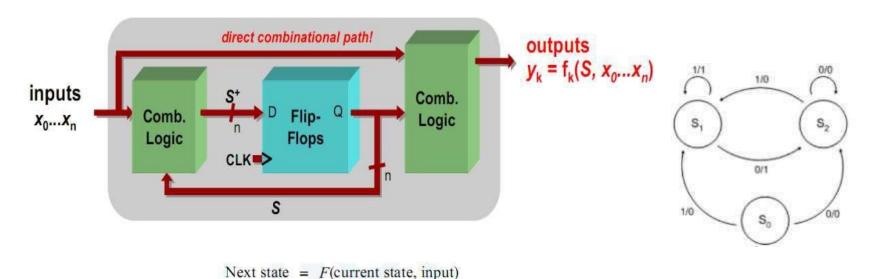

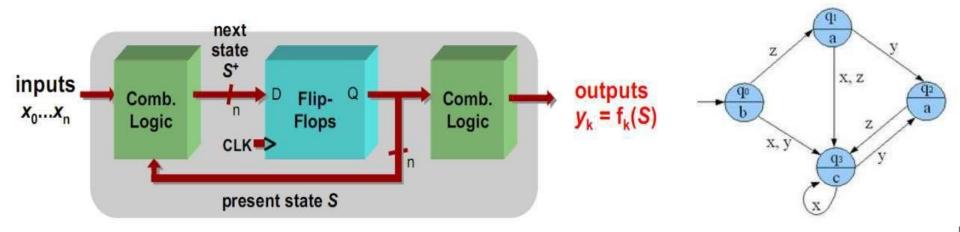

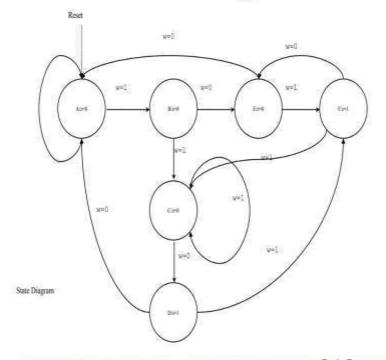

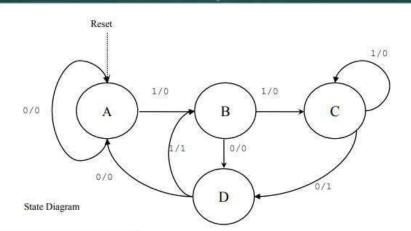

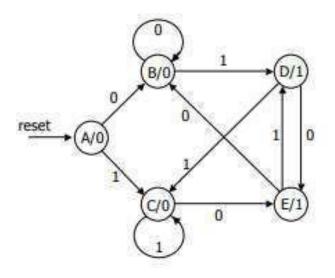

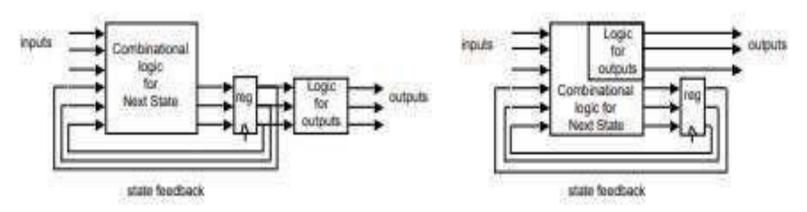

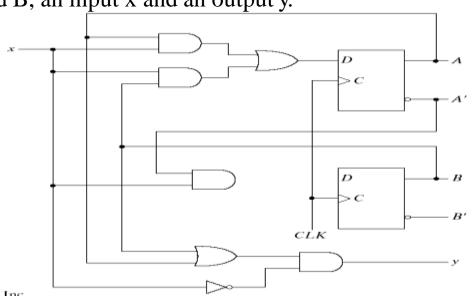

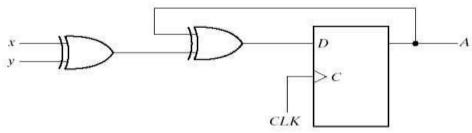

Sequential logic circuit consists of a combinational circuit with storage elements connected as a feedback to combinational circuit

- output depends on the sequence of inputs (past and present)

- stores information (state) from past inputs

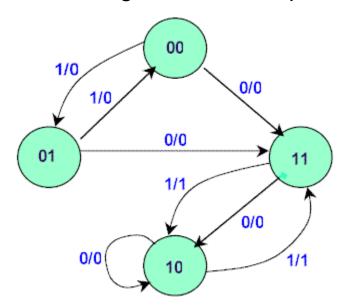

Figure 1: Sequential logic circuits

- Output depends on

- Input

- Previous state of the circuit

- Flip-flop: basic memory element

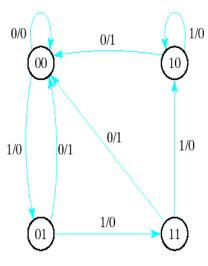

- State table: output for all combinations of input and previous states(Truth Table)

- 1. Sequential circuit receives the binary information from external inputs and with the present state of the storage elements together determine the binary value of the outputs.

- 2. The output in a sequential circuit are a function of not only the inputs, but also the present state of the storage elements.

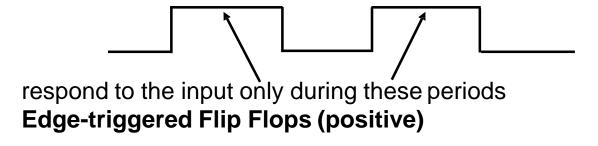

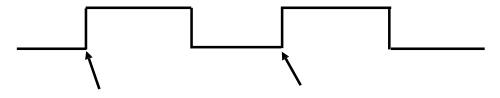

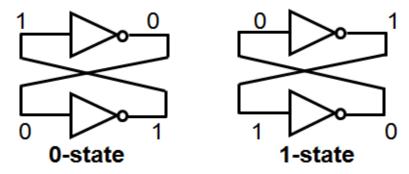

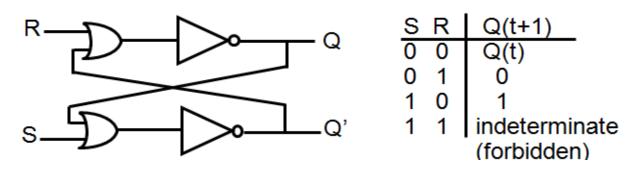

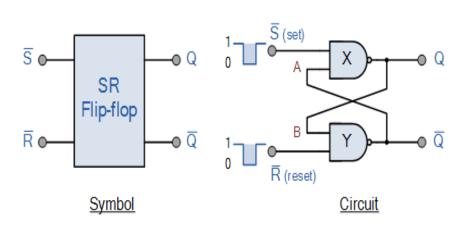

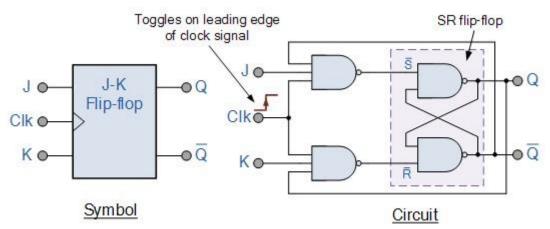

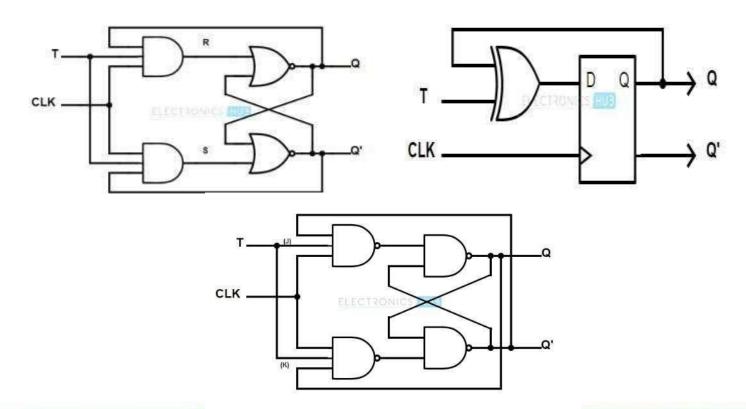

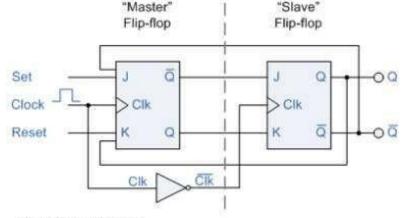

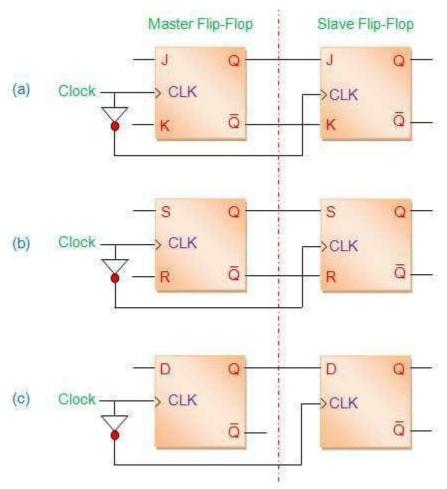

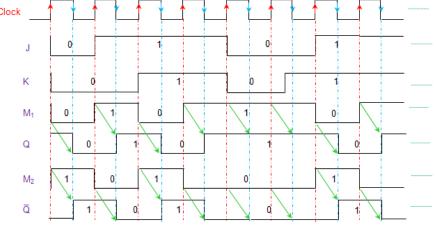

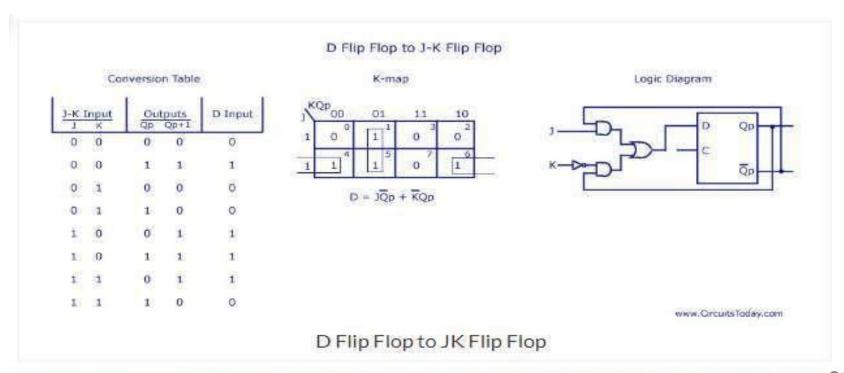

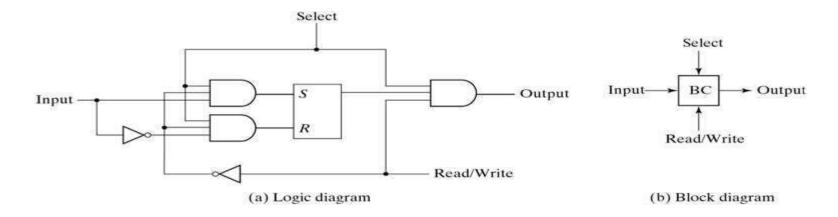

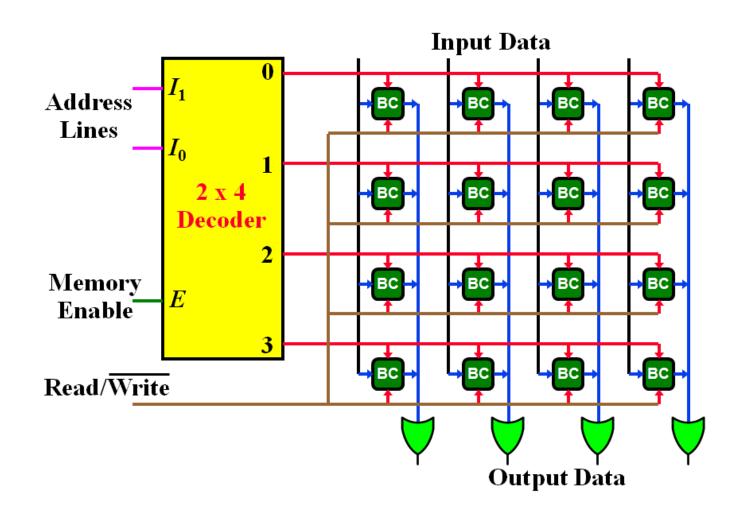

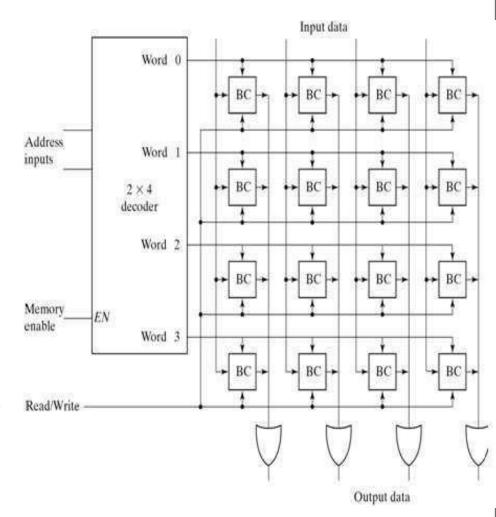

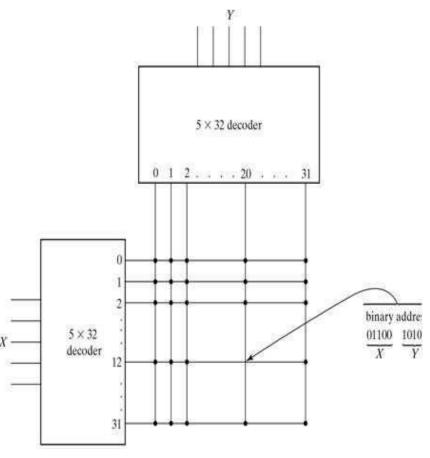

- 3. The next state of the storage elements is also a function of external inputs and the present state.