# **Microprocessors and Microcontrollers**

Prepared By Papa Rao N, Asst. Professor

# What is Microprocessor?

- ≻ 1960s' CPU designed with logic gates

- LSI Large Scale Integration

- ≻ SSI to LSI called Microprocessor

- > Microcomputer

- ≻ Intel 4 bit microprocessor 4004 in 1971

- ➢ 8 bit microprocessor 8080

- > 8-bit 8085 (8 bit data bus + 16 bit address bus)

- ➤ 16-bit 8086 (16 bit data bus + 20 bit address bus)

- ➤ 16 bit processors 8088,80186,80188, 80286

- ➤ 32 bit processors 80386, 80486, 80586 (P)

# What is Microprocessor?

➤ The word comes from the combination micro and processor.

$\triangleright$  Processor means a device that processes whatever. In this context processor means a device that processes numbers, specifically binary numbers, 0's and 1's.

> To process means to manipulate. It is a general term that describes all manipulation. Again in this content, it means to perform certain operations on the numbers that depend on the microprocessor's design.

> The microprocessor is a programmable device that "takes in numbers, performs on them arithmetic or logical operations according to the program stored in memory and then produces other numbers as a result".

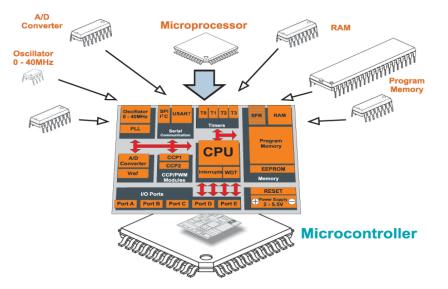

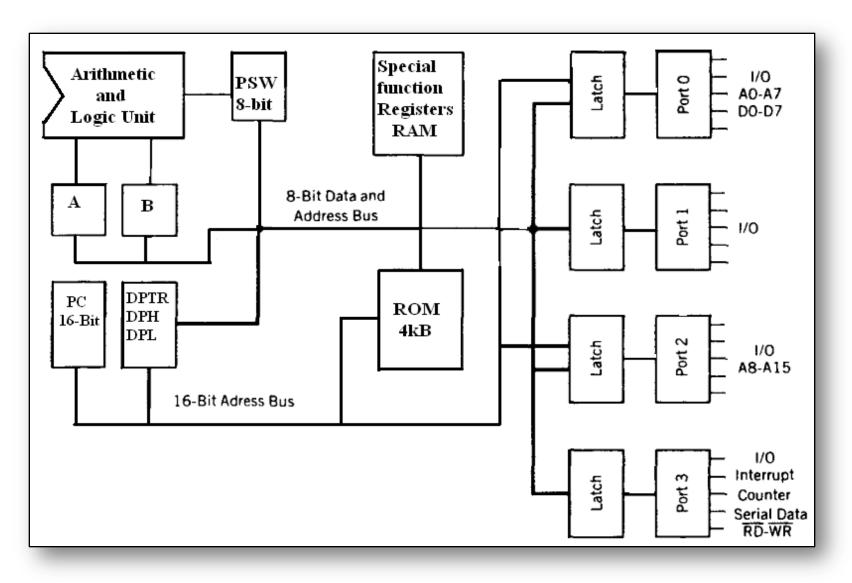

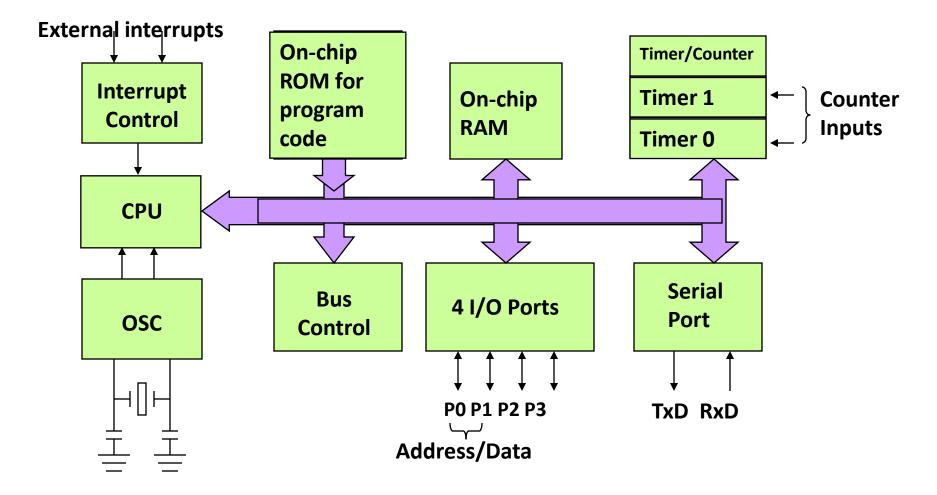

# What is Microcontroller?

- ➤ LSI to VLSI called Microcontroller

- To build Microprocessor, memory and I/O devices on a single chip

- > Components

- Microprocessor

- A/D Converter

- D/A Converter

- Parallel I/O Interface

- Serial I/O Interface

- Timers and Counters

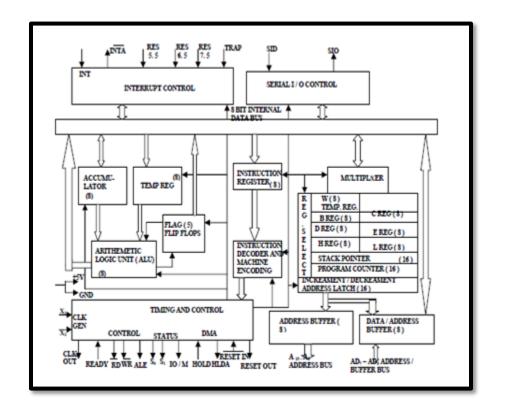

## **8085 Microprocessor**

#### The salient features of 8085 µp are:

- > It is a 8 bit microprocessor.

- ➤ It is manufactured with N-MOS technology.

- It has 16-bit address bus and hence can address up to 216 = 65536 bytes (64KB)

- > memory locations through  $A_0$ - $A_{15}$ .

- > The first 8 lines of address bus and 8 lines of data bus are multiplexed  $AD_0 AD_7$ .

- > Data bus is a group of 8 lines  $D_0 D_7$ .

- > It supports external interrupt request.

- ➤ A 16 bit program counter (PC)

- ➤ A 16 bit stack pointer (SP)

- Six 8-bit general purpose register arranged in pairs: BC, DE, HL.

- It requires a signal +5V power supply and operates at 3.2 MHZ single phase clock. It is enclosed with 40 pins DIP (Dual in line package).

#### 8085 Architecture

**Figure: 8085 Micro Processor Architecture**

# Flag register and GPR of 8085

#### **Flag register**

| D7 | D6 | D5 | <b>D</b> 4 | D3 | D2 | D1 | <b>D</b> 0 |

|----|----|----|------------|----|----|----|------------|

| S  | Z  | х  | AC         | х  | Р  | х  | CY         |

#### **General Purpose registers:**

| Individual   | B, C, D, H and L |  |  |

|--------------|------------------|--|--|

| Combinations | BC, DE and HL    |  |  |

# **Instruction Set**

- 8085 instruction set consists of the following instructions:

- ➤ Data moving instructions.

- > Arithmetic add, subtract, increment and decrement.

- ≻ Logic AND, OR, XOR and rotate.

- Control transfer conditional, unconditional, call subroutine, return from subroutine and restarts.

- ➤ Input / Output instructions.

- Other setting/clearing flag bits, enabling/disabling interrupts, stack operations, etc.

# **Addressing modes**

#### > Register:

references the data in a register or in a register pair.

#### > Register indirect:

instruction specifies register pair containing address, where the data is located.

Direct, Immediate:

8 or 16-bit data.

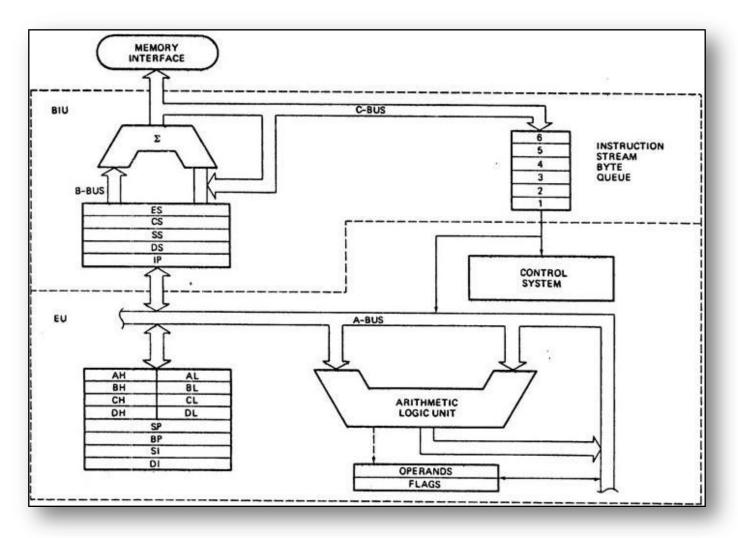

# 8086 microprocessor

- > It is a 16-bit  $\mu p$ .

- 8086 has a 20 bit address bus can access up to 220 memory locations (1 MB).

- ▶ It can support up to 64K I/O ports.

- ▶ It provides 14, 16 -bit registers.

- > It has multiplexed address and data bus AD0- AD15 and A16 A19.

- It requires single phase clock with 33% duty cycle to provide internal timing.

- > 8086 is designed to operate in two modes, Minimum and Maximum.

- It can prefetches upto 6 instruction bytes from memory and queues them in order to speed up instruction execution.

- > It requires +5V power supply.

- ➤ A 40 pin dual in line package.

#### > The 8086 architecture has two parts:

- Bus Interface Unit(BIU)

– Execution Unit(EU)

#### 8086 block diagram

**Figure: 8086 Microprocessor Architecture**

- Bus Interface Unit contains

- Instruction queue,

- Segment registers,

- Instruction pointer, and

- Address adder.

- Execution Unit contains

- Control circuitry,

- Instruction decoder,

- ALU,

- Pointer and Index register,

- Flag register

## Bus interface unit functions

#### **Responsible for performing external bus operations**

#### > The functions of BIU are:

- Instruction Fetch

- Instruction Queuing

- Operand Fetch & storage

- Address Relocation

- Bus control

- ➤ Idle state

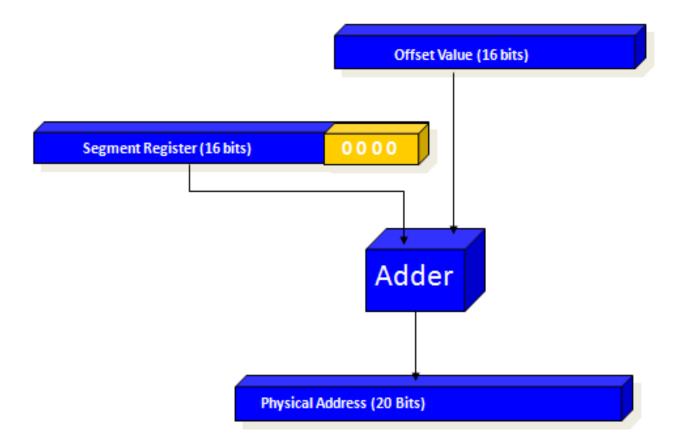

➤ Address adder – fetching of physical address of next instruction( CS+IP

# **Execution Unit Functions**

- Decoding of Instructions

- Execution of instructions

> Steps

- EU extracts instructions from top of queue in BIU

- Decode the instructions

- Generates operands if necessary

- Passes operands to BIU & requests it to perform read or write bus cycles to memory or I/o

- Perform the operation specified by the instruction on operands

- Branch or jump instruction

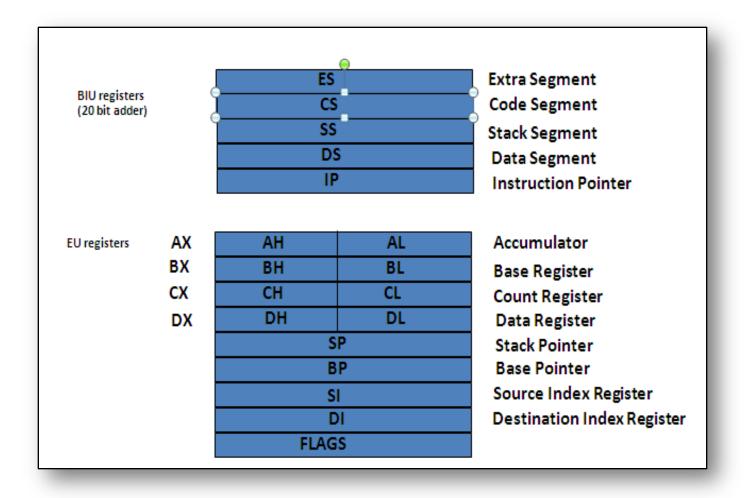

# **Register Organization**

- $\succ$  The types of registers are:

- 1. General Data Registers(AX, BX, CX, DX)

- 2. Segment Registers(CS, DS, ES, SS)

- 3. Pointers and Index Registers(IP, BP, SP)

- 4. Flag Registers(S,Z,P,C,T,I,D,AC,O)

## General Data Registers

- ➤ AX—16 bit accumulator(AH+AL)

- ➢ BX-offset storage(BH+BL)

- CX-default counter in case of string and loop instructions(CH+CL)

- DX-General purpose register (DH+DL)

# **Segment Registers**

- Code Segment Register(CS)

- Data Segment Register(DS)

- Extra Segment Register(ES)

- Stack Segment Register(SS)

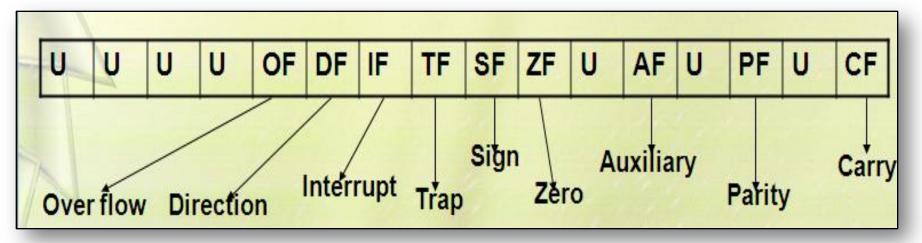

## Flag Registers(S,Z,P,C,T,I,D,AC,O)

- ➤ A flag is a flip flop which indicates some conditions produced by the execution of an instruction or controls certain operations of the EU.

- ≻ In 8086 The EU contains

- a 16 bit flag register

- 9 of the 16 are active flags and remaining 7 are undefined.

- 6 flags indicates some conditions- status flags

- 3 flags –control Flags

# Programming model

Figure: 8086 Micro Processor Programming Model

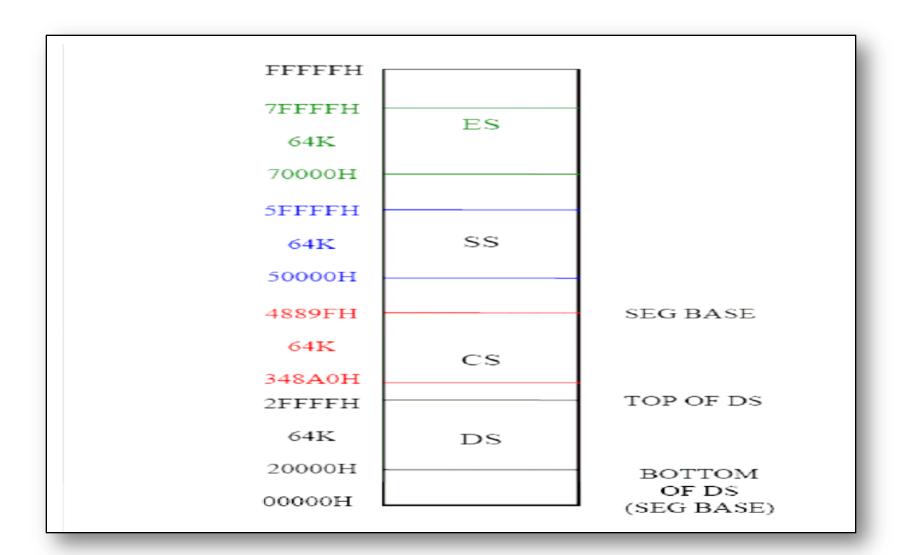

## Memory Segmentation

# Memory address, physical memory organization

# **Address calculation**

If the data segment starts at location 1000h and a data reference contains the address 29h where is the actual data?

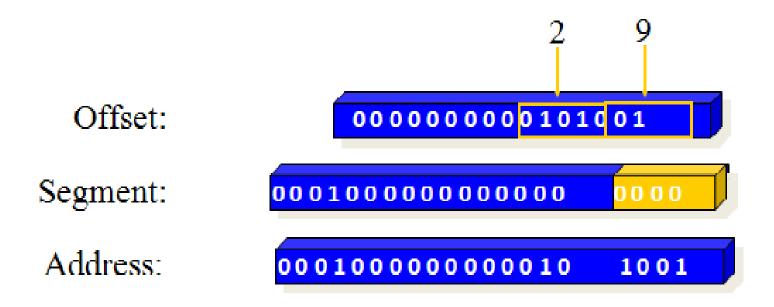

# Generation of 20 bit physical address

The 20-bit Physical address is often represented as: Segment Base : Offset OR CS : IP CS  $34800 \rightarrow$ Implied Zero (from shft Left) +IP 1234

3 5 A3 4 H

# **Signal Description of 8086**

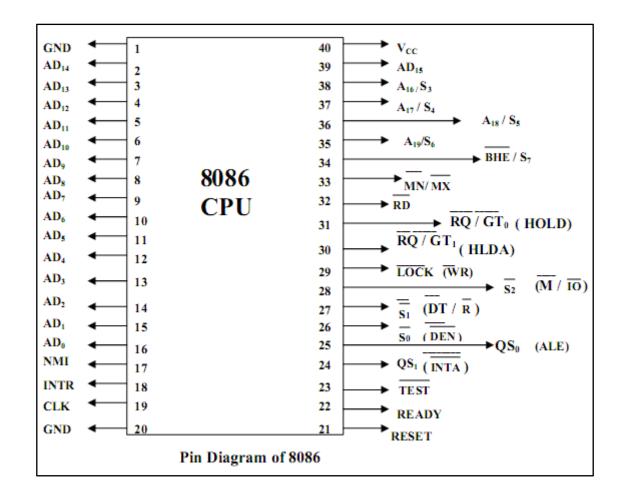

- ➤ The Microprocessor 8086 is a 16-bit CPU available in different clock rates and packaged in a 40 pin CERDIP or plastic package.

- The 8086 operates in single processor or multiprocessor configuration to achieve high performance. The pins serve a particular function in minimum mode (single processor mode) and other function in maximum mode configuration (multiprocessor mode).

- The 8086 signals can be categorized in three groups. The first are the signal having common functions in minimum as well as maximum mode.

- The second are the signals which have special functions for minimum mode and third are the signals having special functions for maximum mode.

# signal descriptions are common for both modes

- > AD15-AD0: These are the time multiplexed memory I/O address and data lines.

- Address remains on the lines during T1 state, while the data is available on the data bus during T2, T3, Tw and T4.

- These lines are active high and float to a tristate during interrupt acknowledge and local bus hold acknowledge cycles.

- A19/S6,A18/S5,A17/S4,A16/S3: These are the time multiplexed address and status lines.

- > During T1 these are the most significant address lines for memory operations.

- During I/O operations, these lines are low. During memory or I/O operations, status information is available on those lines for T2,T3,Tw and T4.

- The status of the interrupt enable flag bit is updated at the beginning of each clock cycle.

- The S4 and S3 combined to indicate which segment register is presently being used for memory accesses as in below fig.

| S <sub>4</sub> | S <sub>3</sub> | Indication     |

|----------------|----------------|----------------|

| 0              | 0              | Alternate Data |

| 0              | 1              | Stack          |

| 1              | 0              | Code or none   |

| 1              | 1              | Data           |

# **8086 OPERATION's**

It contains two modes of operation

i) Maximum mode of operation

ii) Minimum mode of operation

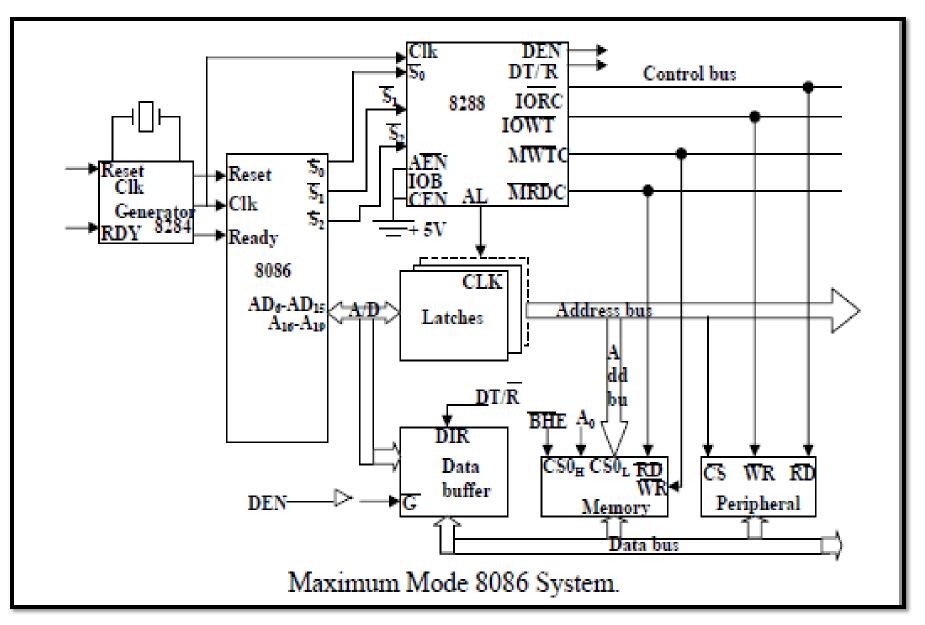

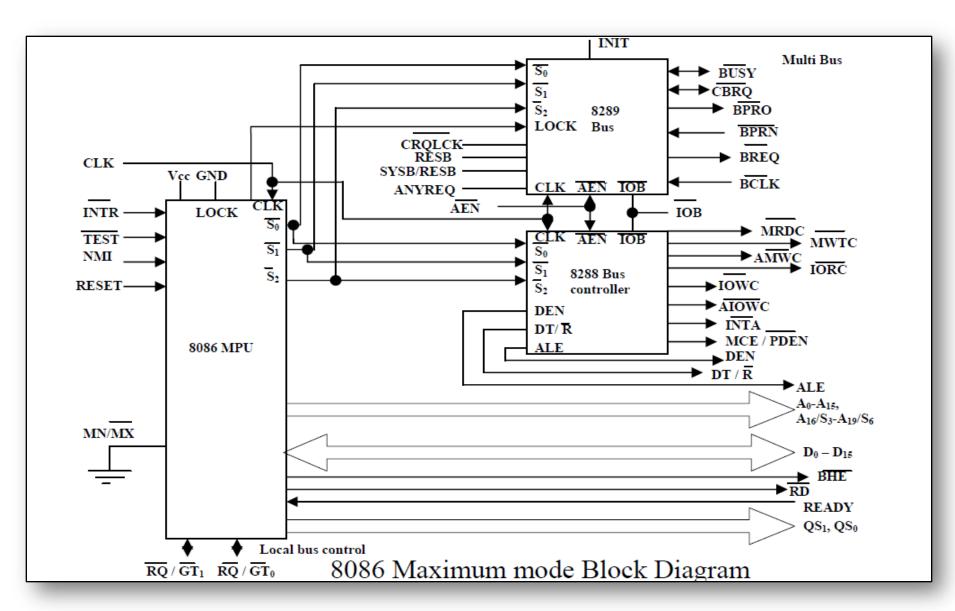

# Maximum mode operation of 8086

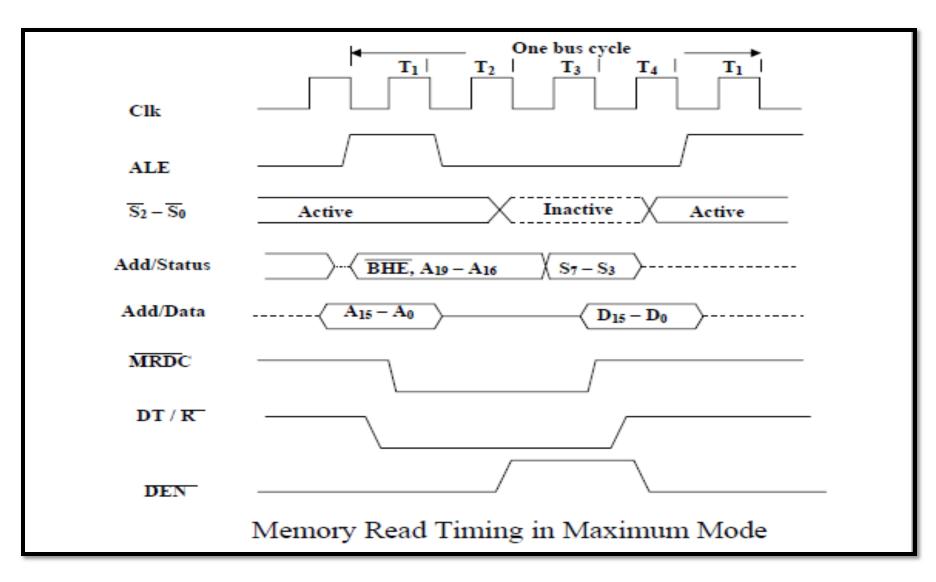

# Memory read timing in maximum mode

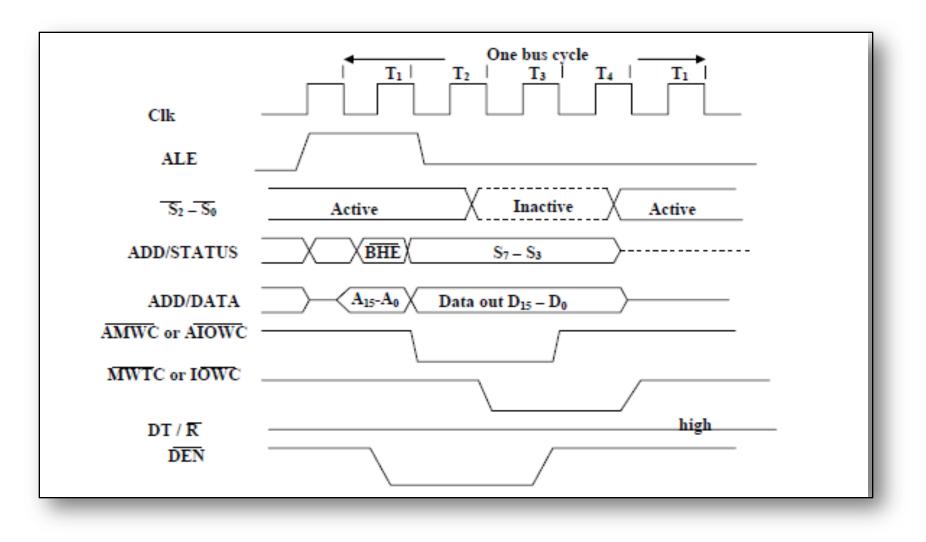

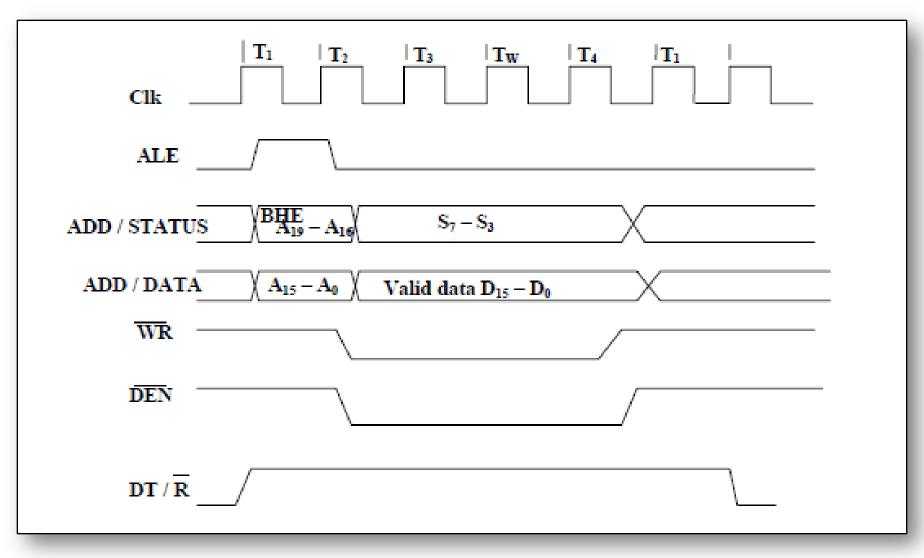

# Memory write timing in maximum mode

memory write timing in maximum mode

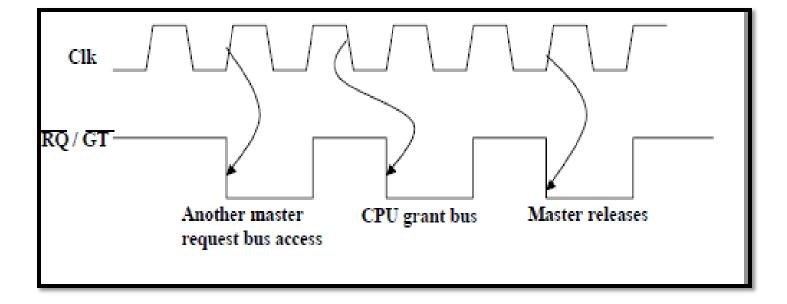

#### **RQ/GT** Timings in Maximum Mode.

## Minimum mode of operation

#### write cycle timing diagram for minimum mode

Figure: write cycle timing diagram for minimum mode

## 8086 Pin diagram

## Interrupts of 8086

> The processor has the following interrupts:

- INTR is a maskable hardware interrupt. The interrupt can be enabled/disabled using STI/CLI instructions or using more complicated method of updating the FLAGS register with the help of the POPF instruction.

- When an interrupt occurs, the processor stores FLAGS register into stack, disables further interrupts, fetches from the bus one byte representing interrupt type, and jumps to interrupt processing routine address of which is stored in location 4 \* <interrupt type>. Interrupt processing routine should return with the IRET instruction.

- NMI is a non-maskable interrupt. Interrupt is processed in the same way as the INTR interrupt. Interrupt type of the NMI is 2, i.e. the address of the NMI processing routine is stored in location 0008h. This interrupt has higher priority then the maskable interrupt.

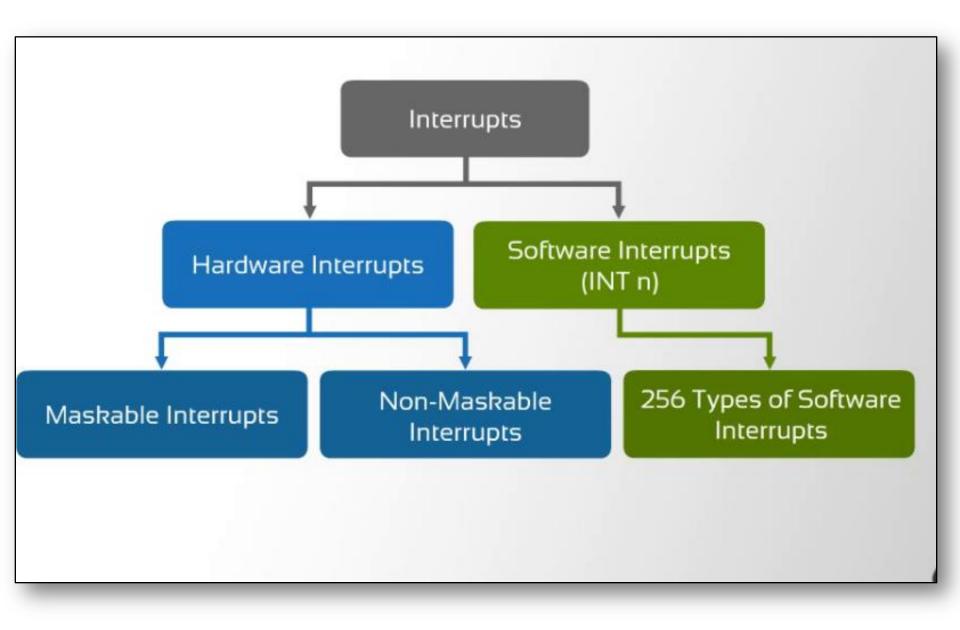

- > **Software interrupts** can be caused by:

- > INT instruction breakpoint interrupt. This is a type 3 interrupt.

- INT <interrupt number> instruction any one interrupt from available 256 interrupts.

- > INTO instruction interrupt on overflow

- Single-step interrupt generated if the TF flag is set. This is a type 1 interrupt. When the CPU processes this interrupt it clears TF flag before calling the interrupt processing routine.

- Processor exceptions: Divide Error (Type 0), Unused Opcode (type 6) and Escape opcode (type 7).

- Software interrupt processing is the same as for the hardware interrupts.

Assembly Language Programming Fundamentals

## Introduction To Programming Languages

- ➤ Machine Languages -"natural language" of a computer

- Low Level Languages-In low level language, instructions are coded using mnemonics

- High Level Languages

## Format of Assembly Language Instructions

[Label] Operation [Operands] [; Comment]

Example: Examples of instructions with varying numbers of fields.

[Label] Operation [Operands] [; Comment]

L1: cmp bx, cx ; Compare bx with cx all fields

present

add ax, 25 operation and 2

operands

inc bx operation and 1 operand

ret

operation field only

; Comment: whatever you wish !! comment field only

# Program syntax

| Type 1( MASM)                                                                                                                                                                                | TYPE 2(MASM)                                                                                                                                                                                                                                     | Kit                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| .model small<br>.data<br>Mes db 'HAI \$'<br>N1 db 20h<br>N2 db 30h<br>.code<br>Start:<br>Mov ax,@data<br>Mov ds,ax<br>Mov ds,ax<br>Mov ax,N1<br>Mov bx,N2<br>Add ax,bx<br>Int 3<br>End start | Assume CS:code segment, DS:Data segment<br>DATA SEGMENT<br>Mes db 'HAI\$'<br>N1 db 20h<br>N2 db 30h<br>DATA ENDS<br>CODE SEGMENT<br>Start:<br>Mov ax,data<br>Mov ds,ax<br>Mov ax,N1<br>Mov bx,N2<br>Add ax,bx<br>Int 3<br>CODE ENDS<br>End start | Mov ax,20<br>Mov bx,30<br>Add ax,bx<br>Int 3 |

## **Addressing Modes of 8086**

The addressing mode describes the types of operands and the way they are accessed for executing an instruction. According to the flow of instruction execution, the instructions may be categorized as

Sequential control flow instructions and

Control transfer instructions.

# Addressing Modes of 8086(Contd...)

Sequential control flow instructions are the instructions which after execution, transfer control to the next instruction appearing immediately after it (in the sequence) in the program. For example the arithmetic, logic, data transfer and processor control instructions are Sequential control flow instructions.

The control transfer instructions on the other hand transfer control to some predefined address or the address somehow specified in the instruction, after their execution. For example INT, CALL, RET & JUMP instructions fall under this category.

The addressing modes for Sequential and control flow instructions are explained as follows.

### **1. Immediate addressing mode:**

In this type of addressing, immediate data is a part of instruction, and appears in the form of successive byte or bytes.

#### Example: MOV AX, 0005H.

In the above example, 0005H is the immediate data. The immediate data may be 8-bit or 16-bit in size.

#### 2. Direct addressing mode:

In the direct addressing mode, a 16-bit memory address (offset) directly specified in the instruction as a part of it.

Example: MOV AX, [5000H].

#### 3. Register addressing mode:

In the register addressing mode, the data is stored in a register and it is referred using the particular register. All the registers, except IP, may be used in this mode.

**Example:** MOV BX, AX

### 4. Register indirect addressing mode:

Sometimes, the address of the memory location which contains data or operands is determined in an indirect way, using the offset registers. The mode of addressing is known as register indirect mode.

In this addressing mode, the offset address of data is in either BX or SI or DI Register. The default segment is either DS or ES. **Example:** MOV AX, [BX].

#### 5. Indexed addressing mode:

In this addressing mode, offset of the operand is stored one of the index registers. DS & ES are the default segments for index registers SI & DI respectively.

### Example: MOV AX, [SI]

Here, data is available at an offset address stored in SI in DS.

### **6. Register relative addressing mode:**

In this addressing mode, the data is available at an effective address formed by adding an 8-bit or 16-bit displacement with the content of any one of the register BX, BP, SI & DI in the default (either in DS & ES) segment.

### Example: MOV AX, 50H [BX]

#### 7. Based indexed addressing mode:

The effective address of data is formed in this addressing mode, by adding content of a base register (any one of BX or BP) to the content of an index register (any one of SI or DI). The default segment register may be ES or DS.

Example: MOV AX, [BX][SI]

#### 8. Relative based indexed:

The effective address is formed by adding an 8 or 16-bit displacement with the sum of contents of any of the base registers (BX or BP) and any one of the index registers, in a default segment.

### Example: MOV AX, 50H [BX] [SI]

#### Addressing Modes for control transfer instructions:

#### 1. Intersegment

- Intersegment direct

- Intersegment indirect

#### 2. Intrasegment

- Intrasegment direct

- Intrasegment indirect

### 1. Intersegment direct:

In this mode, the address to which the control is to be transferred is in a different segment. This addressing mode provides a means of branching from one code segment to another code segment. Here, the CS and IP of the destination address are specified directly in the instruction.

#### **Example:** JMP 5000H, 2000H;

Jump to effective address 2000H in segment 5000H.

## **2.** Intersegment indirect:

In this mode, the address to which the control is to be transferred lies in a different segment and it is passed to the instruction indirectly, i.e. contents of a memory block containing four bytes, i.e. IP(LSB), IP(MSB), CS(LSB) and CS(MSB) sequentially. The starting address of the memory block may be referred using any of the addressing modes, except immediate mode.

#### Example: JMP [2000H].

Jump to an address in the other segment specified at effective address 2000H in DS.

#### 3. Intrasegment direct mode:

In this mode, the address to which the control is to be transferred lies in the same segment in which the control transfers instruction lies and appears directly in the instruction as an immediate displacement value. In this addressing mode, the displacement is computed relative to the content of the instruction pointer.

#### **Example:** JMP SHORT LABEL.

#### 4. Intrasegment indirect mode:

In this mode, the displacement to which the control is to be transferred is in the same segment in which the control transfer instruction lies, but it is passed to the instruction directly. Here, the branch address is found as the content of a register or a memory location.

This addressing mode may be used in unconditional branch instructions.

**Example:** JMP [BX]; Jump to effective address stored in BX

# **INSTRUCTION SET OF 8086**

### **Classified into 10 categories:**

- 1] Data Transfer

- 2] Arithmetic

- 3] Bit manipulation instructions

- 4] string

- **5]Iteration Control Instructions**

- 6] program execution transfer instructions

- 7] Interrupt Control

- 8] high level language interface instructions

- 9] processor control instructions

- 10] External hardware instructions

## **Data Transfer instructions**

- These instructions are used to transfer the data from source operand to destination operand. All the store, move, load, exchange, input and output instructions belong to this group.

- > Note : Data Transfer Instructions do not affect any flags

## Data Transfer Instructions

### 1] MOV destination, source

- Note : source and destination cannot be memory location. Also source and destination must be same type.

- 2] **PUSH source :** *Copies word on stack.*

- 3] **POP destination:** Copies word from stack into dest. Reg.

- 4] IN acc, port : Copies 8 or 16 bit data from port to accumulator.

- a) Fixed Port

- b) Variable Port

- 5] OUT port, acc

### Data Transfer Instructions Cont...

- 6] **LES Reg, Mem:** *Load register and extra segment register with words from memory.*

- 7] LDS Reg, Mem: Load register and data segment

register with words from memory.

8] LEA Reg,Src: load Effective address.

(Offset is loaded in specified register)

- 9] **LAHF:** *Copy lower byte of flag register into AH register.*

- 10] SAHF: Copy AH register to lower byte of flag

### Data Transfer Instructions Cont ...

11] **XCHG destination, source:** *Exchange contents of source and destination.*

#### 12] XLAT: Translate a byte in AL.

This instruction replaces the byte in AL with byte pointed by BX. To point desired byte in look up table instruction adds contains of BX with AL (BX+AL). Goes to this location and loads into AL.

### **Arithmetic Instructions: ADD, ADC, INC, AAA, DAA**

| Mnemonic | Meaning                           | Format  | Operation                                   | Flags<br>affected |

|----------|-----------------------------------|---------|---------------------------------------------|-------------------|

| ADD      | Addition                          | ADD D,S | (S)+(D) → (D)<br>carry → (CF)               | ALL               |

| ADC      | Add with carry                    | ADC D,S | (S)+(D)+(CF) → (D)<br>carry → (CF)          | ALL               |

| INC      | Increment by<br>one               | INC D   | (D)+1 → (D)                                 | ALL but CY        |

| AAA      | ASCII adjust for addition         | AAA     | If the sum is >9, AH<br>is incremented by 1 | AF,CF             |

| DAA      | Decimal<br>adjust for<br>addition | DAA     | Adjust AL for decimal<br>Packed BCD         | ALL               |

#### Arithmetic Instructions – SUB, SBB, DEC, AAS, DAS, NEG

| Mnemonic | Meaning                              | Format  | Operation                                         | Flags<br>affected |

|----------|--------------------------------------|---------|---------------------------------------------------|-------------------|

| SUB      | Subtract                             | SUB D,S | (D) - (S) → (D)<br>Borrow → (CF)                  | All               |

| SBB      | Subtract<br>with<br>borrow           | SBB D,S | (D) - (S) - (CF) → (D)                            | All               |

| DEC      | Decrement<br>by one                  | DEC D   | (D) - 1 → (D)                                     | All but CF        |

| NEG      | Negate                               | NEG D   |                                                   | All               |

| DAS      | Decimal<br>adjust for<br>subtraction | DAS     | Convert the result in AL to packed decimal format | All               |

| AAS      | ASCII<br>adjust for<br>subtraction   | AAS     | (AL) difference<br>(AH) dec by 1 if borrow        | CY,AC             |

## **Multiplication and Division**

| Mnemonic | Meaning                        | Format | Operation                                                                                                                                                                                                                                              | Flags Affected                      |

|----------|--------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| MUL      | Multiply<br>(unsigned)         | MULS   | $\begin{array}{l} (AL) \cdot (S8) \rightarrow (AX) \\ (AX) \cdot (S16) \rightarrow (DX), (AX) \end{array}$                                                                                                                                             | OF, CF<br>SF, ZF, AF, PF undefined  |

| DIV      | Division<br>(unsigned)         | DIV S  | (1) Q((AX)/(S8)) → (AL)<br>R((AX)/(S8)) → (AH)                                                                                                                                                                                                         | OF, SF, ZF, AF, PF, CF<br>undefined |

|          |                                |        | (2) $Q((DX,AX)/(S16)) \rightarrow (AX)$<br>$R((DX,AX)/(S16)) \rightarrow (DX)$<br>If Q is FF <sub>16</sub> in case (1) or<br>FFFF <sub>16</sub> in case (2), then<br>type 0 interrupt occurs                                                           |                                     |

| IMUL     | Integer multiply<br>(signed)   | IMUL S | $(AL) \cdot (S8) \rightarrow (AX)$<br>$(AX) \cdot (S16) \rightarrow (DX), (AX)$                                                                                                                                                                        | OF, CF<br>SF, ZF, AF, PF undefined  |

| IDIV     | Integer divide<br>(signed)     | IDIV S | (1) Q((AX)/(S8)) → (AL)<br>R((AX)/(S8)) → (AH)                                                                                                                                                                                                         | OF, SF, ZF, AF, PF, CF<br>undefined |

|          |                                |        | <ul> <li>(2) Q((DX,AX)/(S16)) → (AX)<br/>R((DX,AX)/(S16)) → (DX)</li> <li>If Q is positive and exceeds</li> <li>7FFF<sub>16</sub> or if Q is negative<br/>and becomes less than</li> <li>8001<sub>16</sub>, then type 0 interupt<br/>occurs</li> </ul> |                                     |

| AAM      | Adjust AL for                  | ААМ    | Q((AL)/10) → (AH)                                                                                                                                                                                                                                      | SF, ZF, PF                          |

|          | multiplication                 |        | R((AL)/10) → (AL)                                                                                                                                                                                                                                      | OF, AF,CF undefined                 |

| AAD      | Adjust AX for<br>division      | AAD    | $(AH) \cdot 10 + (AL) \rightarrow (AL)$<br>$00 \rightarrow (AH)$                                                                                                                                                                                       | SF, ZF, PF<br>OF, AF, CF undefined  |

| CBW      | Convert byte to<br>word        | CBW    | (MSB of AL) $\rightarrow$ (All bits of AH)                                                                                                                                                                                                             | None                                |

| CWD      | Convert word to<br>double word | CWD    | (MSB of AX) $\rightarrow$ (All bits of DX)                                                                                                                                                                                                             | None                                |

(a)

# **Multiplication and Division**

| Multiplication<br>(MUL or IMUL) | Multiplicand | <b>Operand</b><br>(Multiplier) | Result   |

|---------------------------------|--------------|--------------------------------|----------|

| Byte*Byte                       | AL           | Register or memory             | AX       |

| Word*Word                       | AX           | Register or memory             | DX :AX   |

| Dword*Dword                     | EAX          | Register or memory             | EAX :EDX |

| Division<br>(DIV or IDIV) | Dividend | Operand<br>(Divisor)      | Quotient: Remainder |

|---------------------------|----------|---------------------------|---------------------|

| Word/Byte                 | AX       | <b>Register or Memory</b> | AL : AH             |

| Dword/Word                | DX:AX    | Register or Memory        | AX : DX             |

| Qword/Dword               | EDX: EAX | Register or Memory        | EAX : EDX           |

# **Bit manipulation instructions**

#### i) Logical Instructions

| Mne | monic                                   | Meaning                 |                                                                       | Fo | ormat              | C          | Operation                                     | Flags Affected                        |

|-----|-----------------------------------------|-------------------------|-----------------------------------------------------------------------|----|--------------------|------------|-----------------------------------------------|---------------------------------------|

| A   | ND                                      | Logical AND             |                                                                       | AN | DD,S               | <b>(S)</b> | $\cdot$ (D) $\rightarrow$ (D)                 | OF, SF, ZF, PF,<br>CF                 |

| C   | )R                                      | Logical Inclusive<br>OR |                                                                       | 0] | R D,S              | (S)-       | $(\mathbf{D}) \rightarrow (\mathbf{D})$       | AF undefined<br>OF, SF, ZF, PF,<br>CF |

| X   | OR                                      | Logical Exclusive<br>OR |                                                                       | XO | OR D,S             | (S)        | ( <b>D</b> )→( <b>D</b> )                     | AF undefined<br>OF, SF, ZF, PF,<br>CF |

| N   | ОТ                                      | LOGICAL NOT             |                                                                       | N  | OT D               |            | $(\mathbf{\bar{D}}) \rightarrow (\mathbf{D})$ | AF undefined<br>None                  |

|     | Desti                                   | nation                  | Source                                                                |    |                    |            |                                               |                                       |

|     | RegisterMeMemoryRegRegisterImmMemoryImm |                         | Register<br>Memory<br>Register<br>Immediate<br>Immediate<br>Immediate |    | De<br>Regis<br>Mem |            |                                               |                                       |

## Logical Instructions Cont...

#### CMP dest, source

CF, ZF and SF are used Ex. CMP CX,BX

|                                                      | CF | ZF | SF |

|------------------------------------------------------|----|----|----|

| $\succ$ CX = BX                                      | 0  | 1  | 0  |

| ≻ CX> BX                                             | 0  | 0  | 0  |

| ≻ CX <bx< td=""><td>1</td><td>0</td><td>1</td></bx<> | 1  | 0  | 1  |

# ii) Shift and Rotate Instructions

- > SHR/SAL: shift logical left/shift arithmetic left

- > SHR: shift logical right

- > SAR: shift arithmetic right

- > ROL: rotate left

- > ROR: rotate right

- > RCL: rotate left through carry

- > RCR: rotate right through carry

### **Rotate Instructions**

| Mnem<br>-onic | Meaning                             | Format      | Operation                                                                                                                                                             | Flags<br>Affected                     |

|---------------|-------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| ROL           | Rotate<br>Left                      | ROL D,Count | Rotate the (D) left by the<br>number of bit positions equal to<br>Count. Each bit shifted out from<br>the left most bit goes back into<br>the rightmost bit position. | CF<br>OF<br>undefined if<br>count ≠ 1 |

| ROR           | Rotate<br>Right                     | ROR D,Count | Rotate the (D) right by the<br>number of bit positions equal to<br>Count. Each bit shifted out from<br>the rightmost bit goes back into<br>the leftmost bit position. | CF<br>OF<br>undefined if<br>count ≠ 1 |

| RCL           | Rotate<br>Left<br>through<br>Carry  | RCL D,Count | Same as ROL except carry is attached to (D) for rotation.                                                                                                             | CF<br>OF<br>undefined if<br>count ≠ 1 |

| RCR           | Rotate<br>right<br>through<br>Carry | RCR D,Count | Same as ROR except carry is attached to (D) for rotation.                                                                                                             | CF<br>OF<br>undefined if<br>count ≠ 1 |

# **String**?

- > An array of bytes or words located in memory

- Supported String Operations

- Copy (move, load)

- Search (scan)

- Store

- Compare

# **String Instruction Basics**

- Source DS:SI, Destination ES:DI

- You must ensure DS and ES are correct

- You must ensure SI and DI are offsets into DS and ES respectively

- > Direction Flag (0 = Up, 1 = Down)

- CLD Increment addresses (left to right)

- STD Decrement addresses (right to left)

## **STRING CONTROL**

### 1) MOVS/ MOVSB/ MOVSW

Dest string name, src string name

This instn moves data byte or word from location in DS to location in ES.

### 2) REP / REPE / REPZ / REPNE / REPNZ

*Repeat string instructions until specified conditions exist.* This is prefix a instruction.

## STRING CONTROL Contd...

#### 3)CMPS / CMPSB / CMPSW

Compare string bytes or string words.

#### 4) SCAS / SCASB / SCASW

*Scan a string byte or string word.* Compares byte in AL or word in AX. String address is to be loaded in DI.

#### 5) STOS / STOSB / STOSW

*Store byte or word in a string.* Copies a byte or word in AL or AX to memory location pointed by DI.

#### 6) LODS / LODSB /LODSW

Load a byte or word in AL or AX

Copies byte or word from memory location pointed by SI into AL or AX register.

## **Iteration control instructions**

- These instructions are used to execute a series of instructions for certain number of times.

- ➤ LOOP :Loop through a sequence of instructions until CX=0

- LOOPE/LOOPZ : Loop through a sequence of instructions while ZF=1 and CX = 0

- LOOPNE/LOOPNZ : Loop through a sequence of instructions while ZF=0 and CX =0

- ➢ JCXZ : jump to specified address if CX=0

## **Program Execution Transfer instructions**

These instructions are similar to branching or looping instructions. These instructions include conditional & unconditional jump or loop instructions.

### > Unconditional transfer instructions

- > CALL : Call a procedure, save return address on stack

- ≻ RET : Return from procedure to the main program.

- > JMP : Goto specified address to get next instruction

## **Conditional transfer instructions**

| > JA/JNBE | :Jump if above / jump if not below or equal            |

|-----------|--------------------------------------------------------|

| > JAE/JNB | : Jump if above /jump if not below                     |

| > JBE/JNA | : Jump if below or equal/ Jump if not above            |

| > JC      | : jump if carry flag CF=1                              |

| > JE/JZ   | : jump if equal/jump if zero flag ZF=1                 |

| > JG/JNLE | : Jump if greater/ jump if not less than or equal      |

| > JGE/JNL | : jump if greater than or equal/ jump if not less than |

| > JL/JNGE | : jump if less than/ jump if not greater than or equal |

| > JLE/JNG | : jump if less than or equal/ jump if not greater than |

| > JNC     | : jump if no carry (CF=0)                              |

| > JNE/JNZ | : jump if not equal/ jump if not zero(ZF=0)            |

| > JNO     | : jump if no overflow(OF=0)                            |

| > JNP/JPO | : jump if not parity/ jump if parity odd(PF=0)         |

| > JNS     | : jump if not sign(SF=0)                               |

| > JO      | : jump if overflow flag(OF=1)                          |

| > JP/JPE  | : jump if parity/jump if parity even(PF=1)             |

| > JS      | : jump if sign(SF=1)                                   |

## **Interrupt instructions**

- INT : Interrupt program execution, call service procedure

- INTO : Interrupt program execution if OF=1

- IRET : Return from interrupt service procedure to main program

# **High level language interface instructions**

- > ENTER : enter procedure

- ➢ LEAVE :Leave procedure

- BOUND :Check if effective address within specified array bounds

## **Processor control instructions**

- Flag set/clear instructions

- ➤ STC : Set carry flag CF to 1

- ➤ CLC : Clear carry flag CF to 0

- > CMC : Complement the state of the carry flag CF

- > STD : Set direction flag DF to 1 (decrement string pointers)

- $\succ$  CLD : Clear direction flag DF to 0

- > STI : Set interrupt enable flag to 1(enable INTR input)

- > CLI : Clear interrupt enable Flag to 0 (disable INTR input)

### **External Hardware synchronization instructions**

- > HLT : Halt (do nothing) until interrupt or reset

- > WAIT : Wait (Do nothing) until signal on the test pin is low.

- $\geq$  ESC : Escape to external coprocessor such as 8087 or 8089.

- LOCK : An instruction prefix. Prevents another processor from taking the bus while the adjacent instruction executes.

# Assembler Directives

- > Assembler Directives are directions to the assembler.

- Assembler directives are the commands to the assembler that direct the assembly process.

- They indicate how an operand is treated by the assembler and how assembler handles the program.

- They also direct the assembler how program and data should be arranged in the memory.

# List of Assembler Directives

| ASSUME | DB     | DW      | DD     | DQ      |

|--------|--------|---------|--------|---------|

| DT     | END    | ENDP    | ENDS   | EQU     |

| EVEN   | EXTRN  | GLOBAL  | GROUP  | INCLUDE |

| LABEL  | LENGTH | NAME    | OFFSET | ORG     |

| PROC   | PTR    | SEGMENT | SHORT  | ТҮРЕ    |

# MACROS

- A macro is a group of repetitive instructions in a program which are codified only once and can be used as many times as necessary.

- > Macro with in a macro is a nested MACRO

- A macro can be defined anywhere in program using the directives MACRO and ENDM

Syntax of macro:

Read MACRO

mov ah,02h

int 21h

ENDM

Display MACRO mov dl,al Mov ah,01h int 21h ENDM

### Passing parameters to a macro

Display MACRO INF

mov dx, offset inf mov ah,09h int 21h

ENDM

The parameter MSG can be replaced by inf1 or inf2 while calling... Calling macro:

DISPLAY INF1 DISPLAY INF2

INF1 db "hai\$" INF2 db "Hello, How are you..? \$" Here parameter is INF

### **Procedures Vs Macros**

| Procedures                                                                              | Macros                                                                               |  |  |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| Accessed by CALL and RET mechanism during program execution                             | Accessed by name given to macro when defined during assembly                         |  |  |

| Machine code for instructions only put in memory once                                   | Machine code generated for instructions each time called                             |  |  |

| Parameters are passed in registers,<br>memory locations or stack                        | Parameters passed as part of statement which calls macro                             |  |  |

| Procedures uses stack                                                                   | Macro does not utilize stack                                                         |  |  |

| A procedure can be defined anywhere in program using the directives PROC and ENDP       | A macro can be defined anywhere in<br>program using the directives MACRO<br>and ENDM |  |  |

| Procedures takes huge memory for<br>CALL(3 bytes each time CALL is used)<br>instruction | Length of code is very huge if macro's are called for more number of times           |  |  |

# UINT III I/O INTERFACE

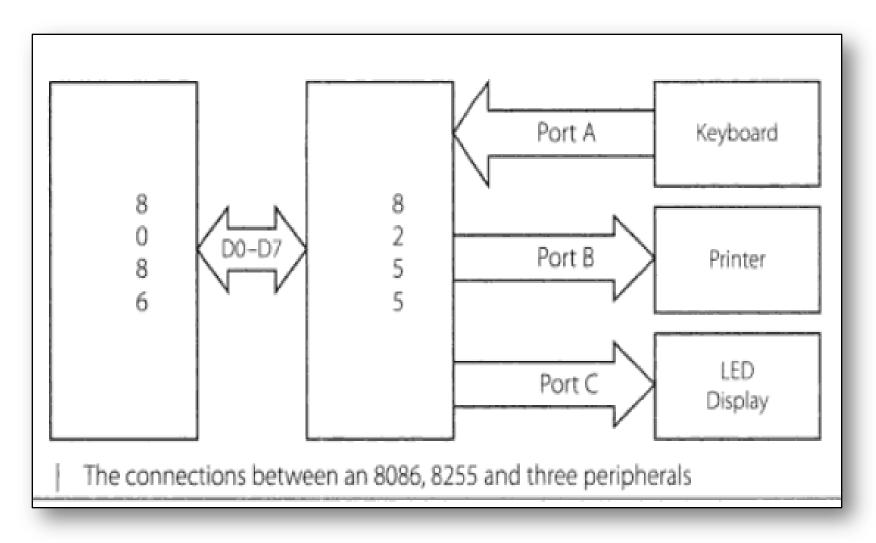

# 8255-PROGRAMMABLE PERIPHERAL INTERFACE

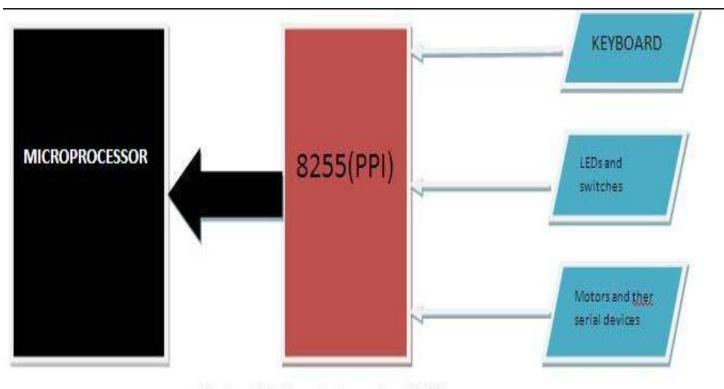

# Need of 8255 for I/O interfacing

There are two reasons for using 8255 between 8086 and I/O devices.

- 1) To achieve Speed compatibility between high speed microprocessor and slow I/O devices.

- 2) Reducing hardware complexity by interfacing the I/O devices through program.

# Purpose of 8255

### 8255

- ➤ It has 24 input/output lines

- ➤ 24 lines divided into 3 ports

- Port A(8 bit)

- Port B(8 bit)

- Port C upper(4 bit), Port C Lower (4 bit)

> All the above 3 ports can act as input or output ports

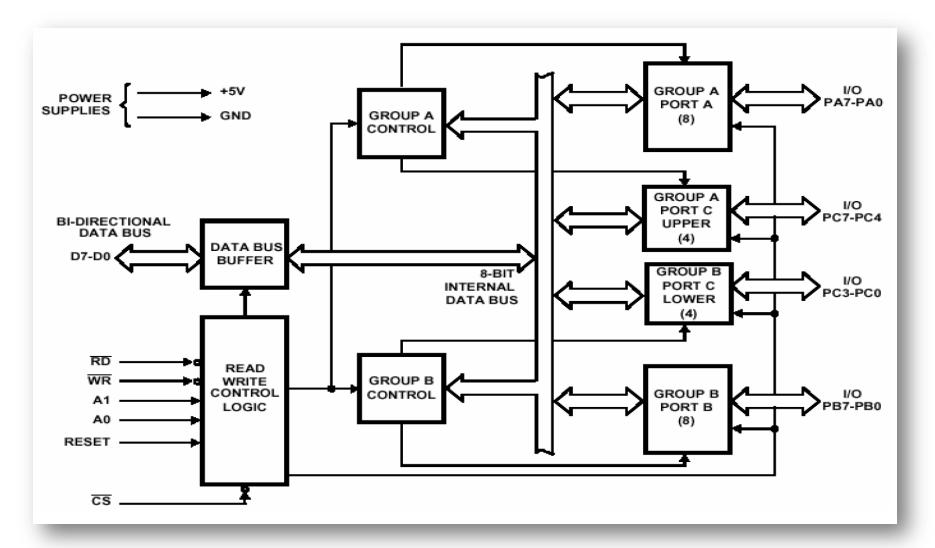

# **Block Diagram**

Figure: Block Diagram of 8255(PIC)

#### **Data Bus buffer**

- ➢ It is a 8-bit bidirectional Data bus.

- $\succ$  Used to interface between 8255 data bus with system bus.

- > The internal data bus and Outer pins  $D_0$ - $D_7$  pins are connected in internally.

- > The direction of data buffer is decided by Read/Control Logic.

### **Read/Write Control Logic**

- This is getting the input signals from control bus and Address bus

- $\succ$  Control signal are RD and WR.

- $\succ$  Address signals are A0, A1, and CS.

- $\geq$  8255 operation is enabled or disabled by CS.

#### Group A and Group B control:

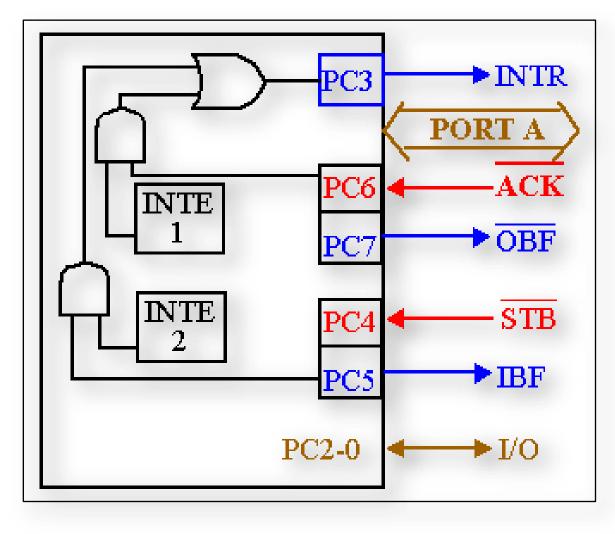

- ➢ Group A and B get the Control Signal from CPU and send the command to the individual control blocks.

- Group A send the control signal to port A and Port C (Upper) PC7-PC4.

- ➢ Group B send the control signal to port B and Port C (Lower) PC3-PC0.

### PORT A:

- This is a 8-bit buffered I/O latch.

- > It can be programmed by mode 0, mode 1, mode 2.

#### PORT B:

- ➤ This is a 8-bit buffer I/O latch.

- > It can be programmed by mode 0 and mode 1.

PORT C:

- > This is a 8-bit Unlatched buffer Input and an Output latch.

- $\succ$  It is spitted into two parts.

- ➢ It can be programmed by bit set/reset operation.

# 8255A pins

# **Pin** Description

PA7-PA0: These are eight port A lines that acts as either latched output or buffered input lines depending upon the control word loaded into the control word register.

PC7-PC4: Upper nibble of port C lines. They may act as either output latches or input buffers lines.

This port also can be used for generation of handshake lines in mode 1 or mode 2.

PC3-PC0: These are the lower port C lines, other details are the same as PC7-PC4 lines.

PB0-PB7: These are the eight port B lines which are used as latched output lines or buffered input lines in the same way as port A.

# **Pin Description(Contd...)**

> RD

$\succ$  WR

$\succ CS$

- : This is the input line driven by the microprocessor and should be low to indicate read operation to8255.

- : This is an input line driven by the microprocessor. A low on this line indicates write operation.

- : This is a chip select line. If this line goes low, it enables the 8255 to respond to RD and WR signals, otherwise RD and WR signal are neglected.

- A1-A0 : These are the address input lines and are driven by the microprocessor.

- **RESET** : The 8255 is placed into its reset state if this input line is a logical 1. All peripheral ports are set to the input mode.

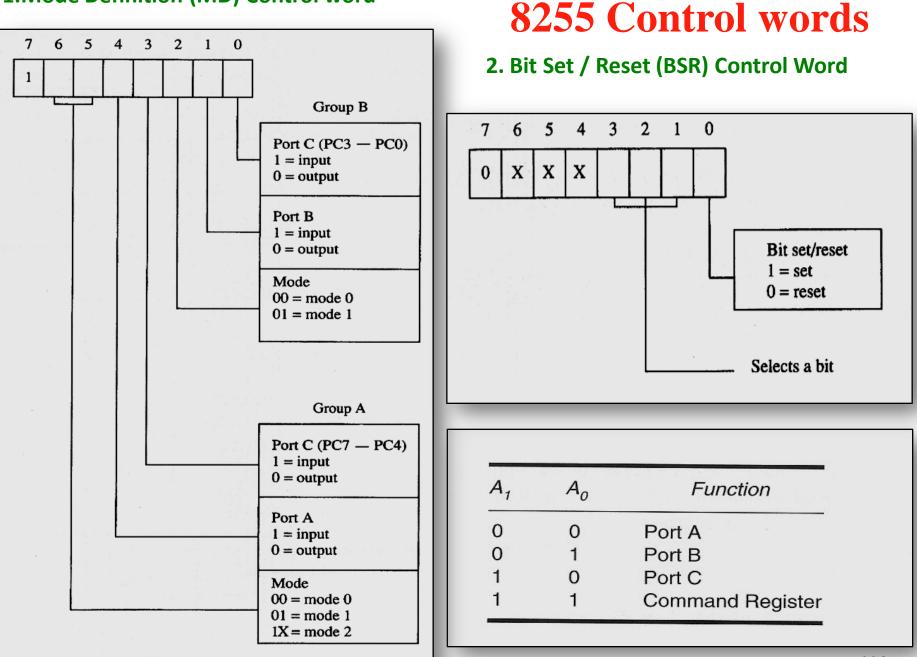

# **Operating Modes**

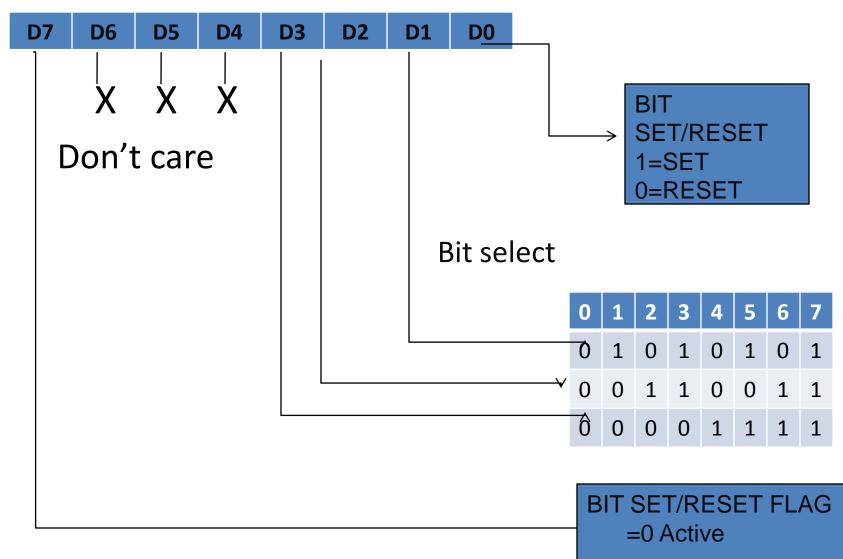

### **BIT SET/RESET MODE**

• The PORT C can be Set or Reset by sending OUT instruction to the CONTROL registers.

### I/O MODES:

MODE 0(Simple input / Output):

- In this mode , port A, port B and port C is used as individually (Simply).

- Ports do not have Handshake or interrupt capability.

MODE 1 :(Input/output with Hand shake)

In this mode, input or output is transferred by hand shaking Signals.

Handshaking signals is used to transfer data between whose data transfer is not same.

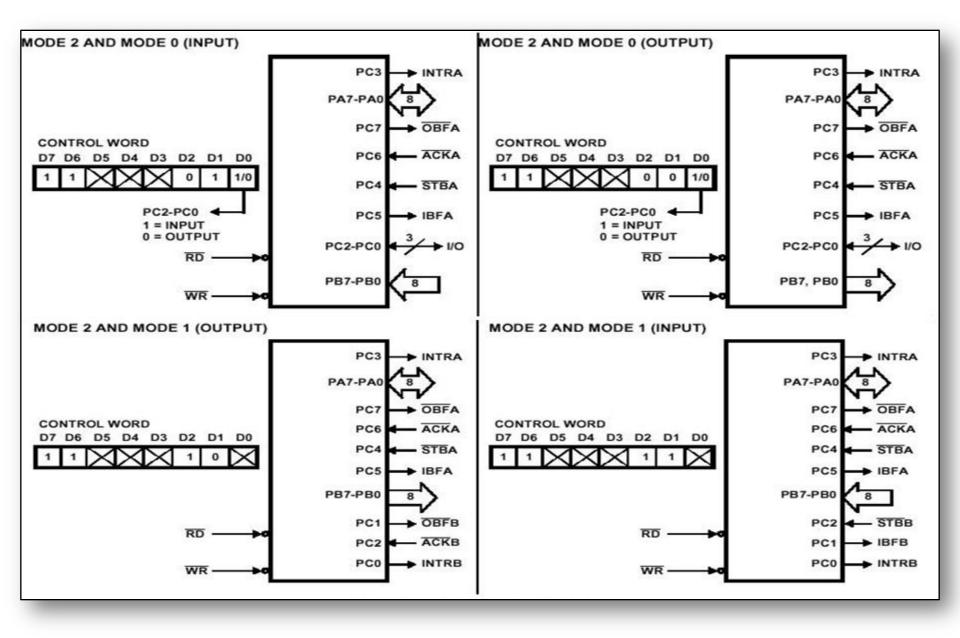

#### MODE 2:bi-directional I/O data transfer:

- This mode allows bidirectional data transfer over a single 8-bit data bus using handshake signals.

- > This feature is possible only Group A

- > Port A is working as 8-biy bidirectional.

- > PC3-PC7 is used for handshaking purpose.

- ➤ The data is sent by CPU through this port , when the peripheral request it.

# FOR BIT SET/RESET MODE:

• This is bit set/reset control word format.

- > PC0-PC7 is set or reset as per the status of D0.

- A BSR word is written for each bit Example:

- > PC3 is Set then control register will be 0XXX0111.

- > PC4 is Reset then control register will be 0XXX01000.

- $\succ$  X is a don't care.

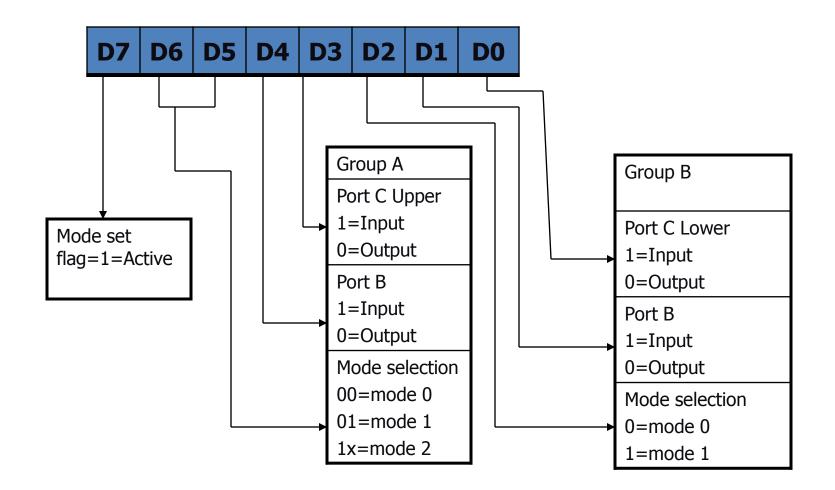

### FOR I/O MODE

### The mode format for I/O as shown in figure

- $\succ$  The control word for both modes is same.

- Bit D7 is used for specifying whether word loaded in to Bit set/reset mode or Mode definition word.

- ➤ D7=1=Mode definition mode.

- ➢ D7=0=Bit set/Reset mode.

### **8255 Operations**

Ines A1-A0 with RD, WR and CS form the following operations for 8255.

|                       |          |          | and the second |                  |                            |  |  |

|-----------------------|----------|----------|------------------------------------------------------------------------------------------------------------------|------------------|----------------------------|--|--|

| RD                    | WR       | CS       | $\mathbf{A}_{1}$                                                                                                 | $\mathbf{A}_{0}$ | Input (Read) cycle         |  |  |

| 0                     | 1        | 0        | 0                                                                                                                | 0                | Port A to Data bus         |  |  |

| 0                     | 1        | 0        | 0                                                                                                                | 1                | Port B to Data bus         |  |  |

| 0                     | 1        | 0        | 1                                                                                                                | 0                | Port C to Data bus         |  |  |

| 0                     | 1        | 0        | 1                                                                                                                | 1                | CWR to Data bus            |  |  |

| and the second        |          |          |                                                                                                                  | die Tal          |                            |  |  |

| RD                    | WR       | CS       | $\mathbf{A}_{1}$                                                                                                 | $\mathbf{A}_{0}$ | Output (Write) cycle       |  |  |

| 1                     | 0        | 0        | 0                                                                                                                | 0                | Data bus to Port A         |  |  |

| 1                     | 0        | 0        | 0                                                                                                                | 1                | Data bus to Port B         |  |  |

| 1                     | 0        | 0        | 1                                                                                                                | 0                | Data bus to Port C         |  |  |

| 1                     | 0        | 0        | 1                                                                                                                | 1                | Data bus to CWR            |  |  |

| 19 Barth              | 1957-197 |          |                                                                                                                  |                  |                            |  |  |

| RD                    | WR       | CS       | $\mathbf{A}_{1}$                                                                                                 | $\mathbf{A}_{0}$ | Function                   |  |  |

| X                     | X        | 1        | X                                                                                                                | X                | Data bus tristated         |  |  |

| 1                     | 1        | 0        | X                                                                                                                | X                | Data bus tristated         |  |  |

|                       |          | Con 1919 |                                                                                                                  |                  | Company and a state of the |  |  |

| Control Word Register |          |          |                                                                                                                  |                  |                            |  |  |

# **Programming 8255**

▶ 8255 has three operation modes: *mode 0, mode 1, and mode 2*

Mode 0 - Simple Input or Output mode

Mode 1 - Input or Output with Handshake mode

Mode 2 - Bidirectional Data Transfer mode

# **Mode 0 - Simple Input or Output**

- In this mode, ports A, B are used as two simple 8-bit I/O ports & port

C as two independent 4-bit ports.

- Each port can be programmed to function as simply an input port or an output port.

- > The **input/output features** in Mode 0 are as follows.

- 1. Outputs are latched.

- 2. Inputs are not latched.

- 3. Ports don't have handshake or interrupt capability.

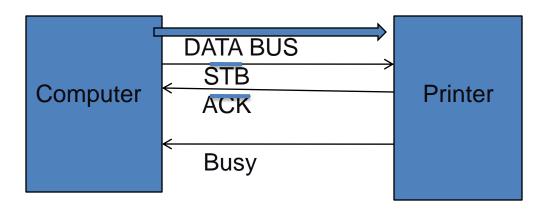

# Handshaking

- Many I/O devices accept or release information slower than the microprocessor.

- ➤ A method of I/O control called handshaking or polling, synchronizes the I/O device with the microprocessor.

- ➤ An example is a parallel printer that prints a few hundred characters per second (CPS).

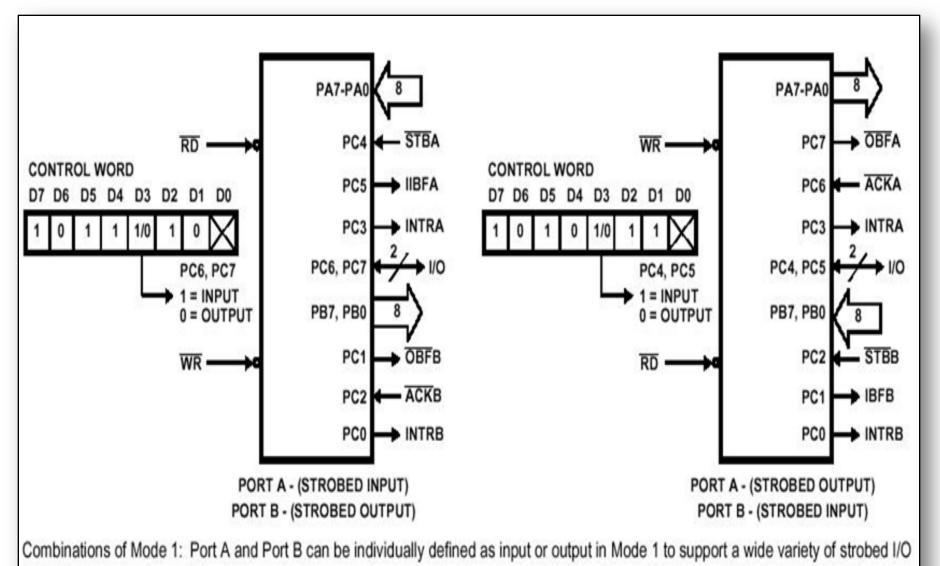

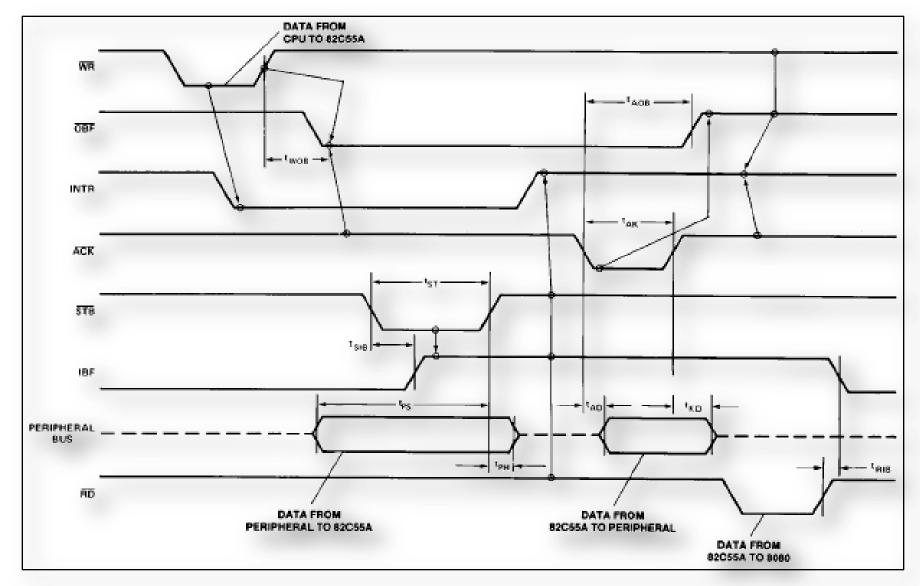

### Mode 1 - Input or Output with Handshake

- ➢ In this mode, handshake signals are exchanged between the MPU and peripherals prior to data transfer.

- > The **features** of the mode include the following:

- 1. Two ports (**A** and **B**) function as 8-bit I/O ports. They can be configured as either as input or output ports.

- 2. Each port uses **three lines from port C as handshake signals**. The remaining two lines of Port C can be used for simple I/O operations.

- 3. Input and Output data are latched.

- 4. Interrupt logic is supported.

### **Example:**

- The computer send the data to the printer large speed compared to the printer.

- When computer send the data according to the printer speed at the time only, printer can accept.

- ➤ If printer is not ready to accept the data then after sending the data bus, computer uses another handshaking signal to tell printer that valid data is available on the data bus.

- Each port uses three lines from port C as handshake signals

# **Mode 1 - Input or Output with Handshake**

applications.

.00

# 82C55: Mode 1 Strobed Input

- ➤ STB : The strobe input loads data into the port latch on a 0-to-1 transition.

- ➢ IBF : Input buffer full is an output indicating that the input latch contain information.

- > **INTR** : Interrupt request is an output that requests an interrupts.

- INTE : The interrupt enable signal is neither an input nor an output; it is an internal bit programmed via the PC4 (port A) or PC2 (port B) bits.

- PC7,PC6 : The port C pins 7 and 6 are general purpose I/O pings that are available for any purpose.

# 8255: Mode 1 Strobed Input

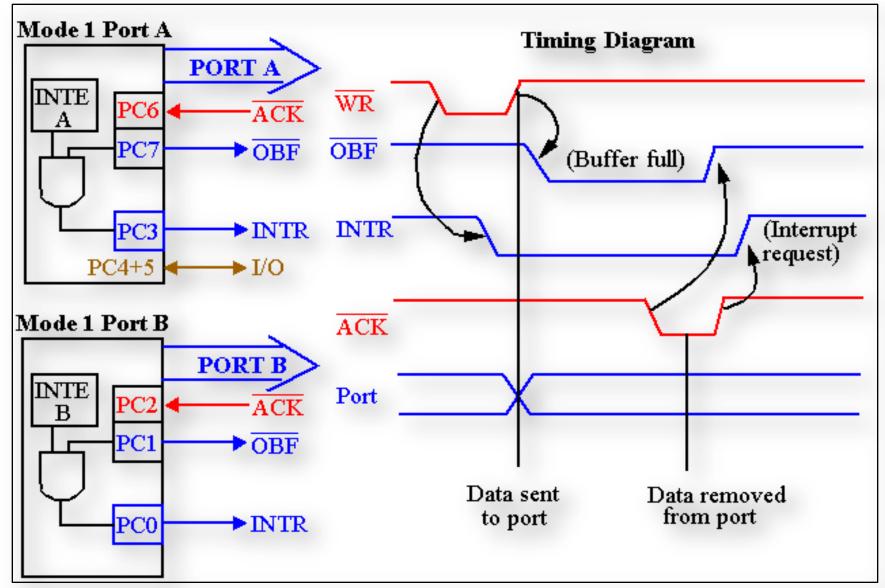

### 82C55 : Mode 1 Output

- ➢ OBF : Output buffer full is an output that goes low when data is latched in either port A or port B. Goes low on ∼ACK.

- ACK : The acknowledge signal causes the ~OBF pin return to 0. This is a response from an external device.

- > **INTR** : Interrupt request is an output that requests an interrupt.

- INTE : The interrupt enable signal is neither an input nor an output; it is an internal bit programmed via the PC6(Port A) or PC2(port B) bits.

- PC5,PC4 : The port C pins 5 and 4 are general-purpose I/O pins that are available for any purpose.

### 8255 : Mode 1 Output

### **Mode 2 - Bidirectional Data Transfer**

- This mode is used primarily in applications such as data transfer between two computers.

- In this mode, Port A can be configured as the bidirectional port, Port B either in Mode 0 or Mode 1.

- Port A uses five signals from Port C as handshake signals for data transfer.

- ➤ The remaining three signals from Port C can be used either as simple I/O or as handshake for port B.

**Figure: Mode 2 - Bidirectional Data Transfer**

### 8255: Mode 2 Bi-directional Operation

•Timing diagram is a combination of the Mode 1 Strobed Input and Mode 1 Strobed Output Timing diagrams.

### **Mode 2 Timing Diagram**

### 8255 Control Words

$\succ$  There are 2 control words in 8255.

- Mode Definition (MD) Control word and

- Bit Set / Reset (BSR) Control Word

- MD control word configures the ports of 8255 as input or output in Mode 0, 1, or 2.

- PCBSR control word is used to set to 1 or reset to 0 any one selected bit of Port C

#### **1.Mode Definition (MD) Control word**

# **Displays Interfacings**

- 1. LCD Interfacing

- 2. LED Interfacing

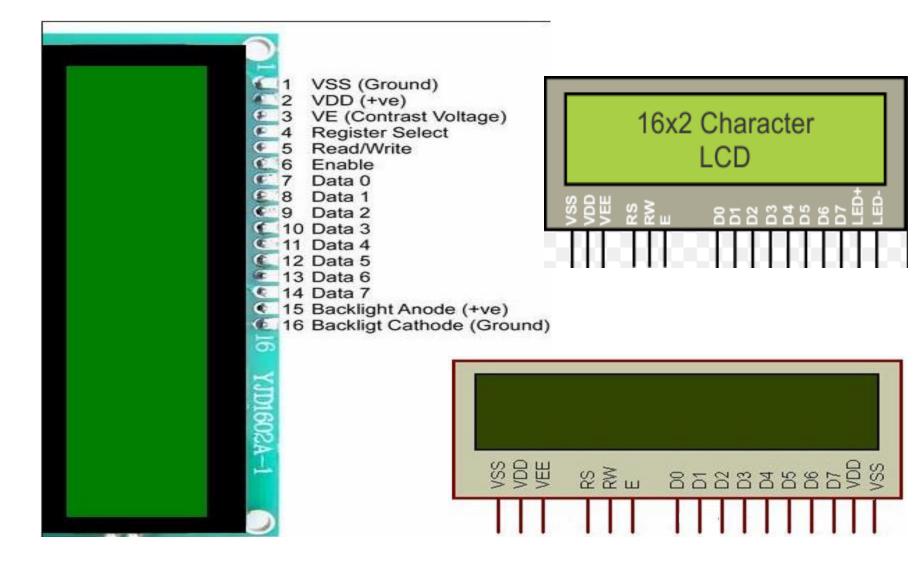

### **INTERFACING LCD MODULE TO 8086 Introduction:**

LCD or Liquid Crystal Display is an output device used in many processor based applications like calculators, Xerox machines, speedometers etc. The 8086 kit, which you use in the lab, also uses a LCD display to view the data entered into and coming out of the processor

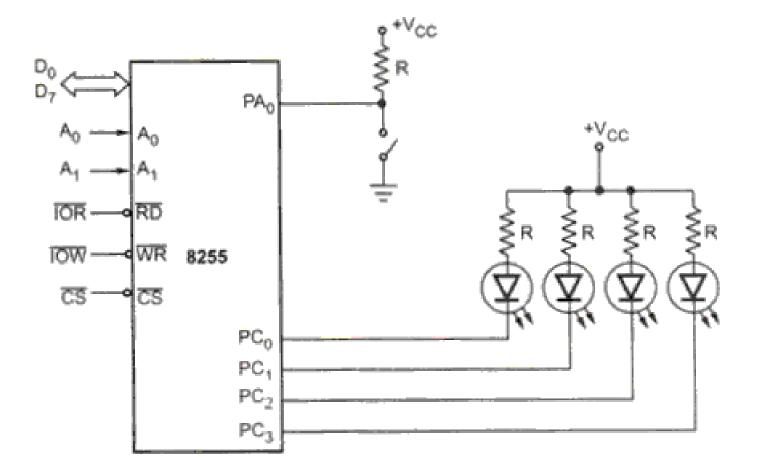

Fig 1.c (I/O interfacing using 8255)

# 16\*2 LCD Module

# 16\*2 LCD Pin Functions

| Pin No | Function                                                             | Name            |  |  |

|--------|----------------------------------------------------------------------|-----------------|--|--|

| 1      | Ground (0V)                                                          | Ground          |  |  |

| 2      | Supply voltage; 5V (4.7V –<br>5.3V)                                  | Vcc             |  |  |

| 3      | Contrast adjustment;<br>through a variable resistor                  | V <sub>EE</sub> |  |  |

| 4      | Selects command register<br>when low; and data register<br>when high | Register Select |  |  |

| 5      | Low to write to the register;<br>High to read from the<br>register   | Read/write      |  |  |

| 6      | Sends data to data pins<br>when a high to low pulse is<br>given      | Enable          |  |  |

| 7      |                                                                      | DB0             |  |  |

| 8      |                                                                      | DB1             |  |  |

| 9      |                                                                      | DB2             |  |  |

| 10     | 8-bit data pins                                                      | DB3             |  |  |

| 11     |                                                                      | DB4             |  |  |

| 12     |                                                                      | DB5             |  |  |

| 13     |                                                                      | DB6             |  |  |

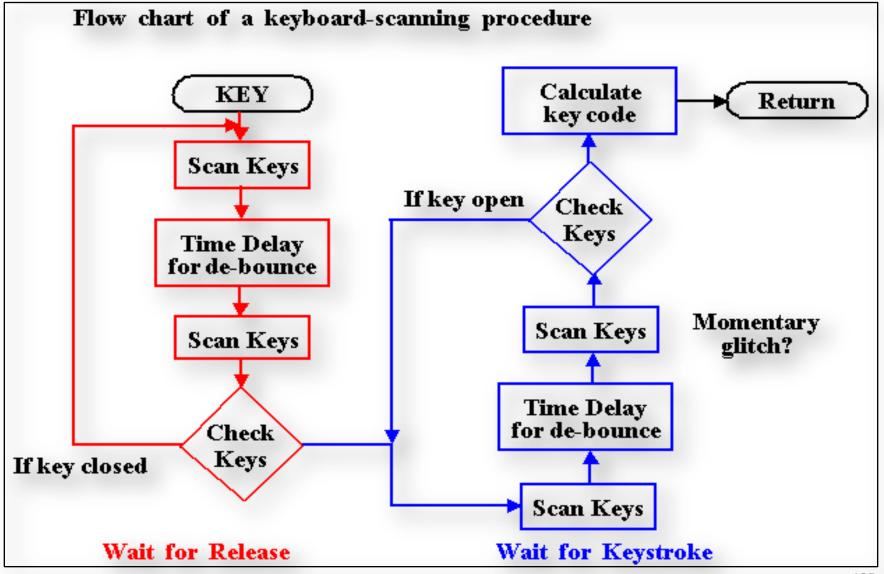

### **Keyboard Interface**

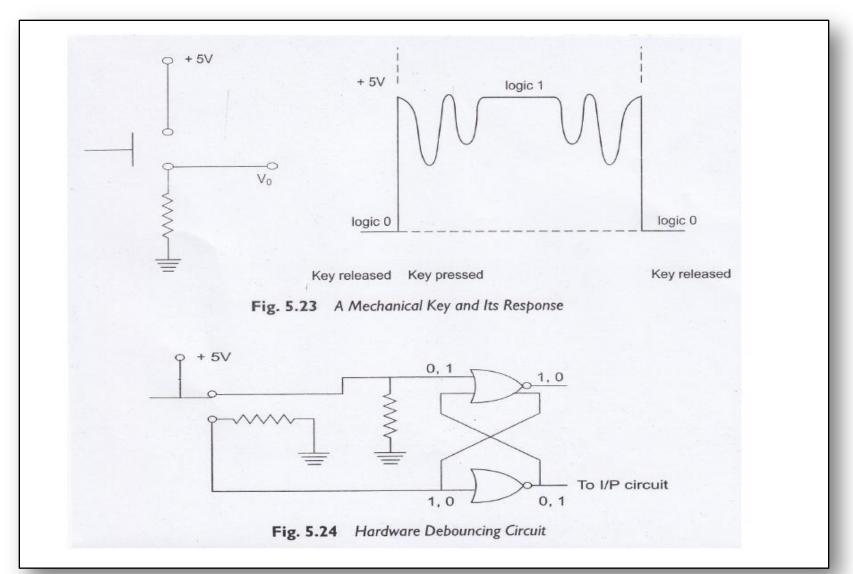

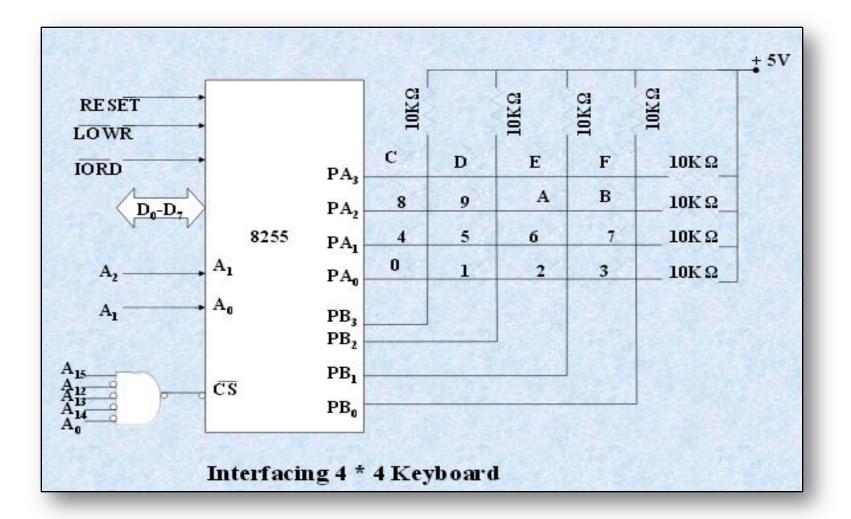

- ➢ In most keyboards, the key switches are connected in a matrix of Rows and Columns.

- Getting meaningful data from a keyboard requires three major tasks:

- Detect a key press

- Debounce the key press.

- Encode the key press (produce a standard code for the pressed key).

- $\succ$  Logic '0' is read by the microprocessor when the key is pressed.

#### **Key Debounce:**

Whenever a mechanical push-bottom is pressed or released once, the mechanical components of the key do not change the position smoothly; rather it generates a transient response. These may be interpreted as the multiple pressures and responded accordingly.

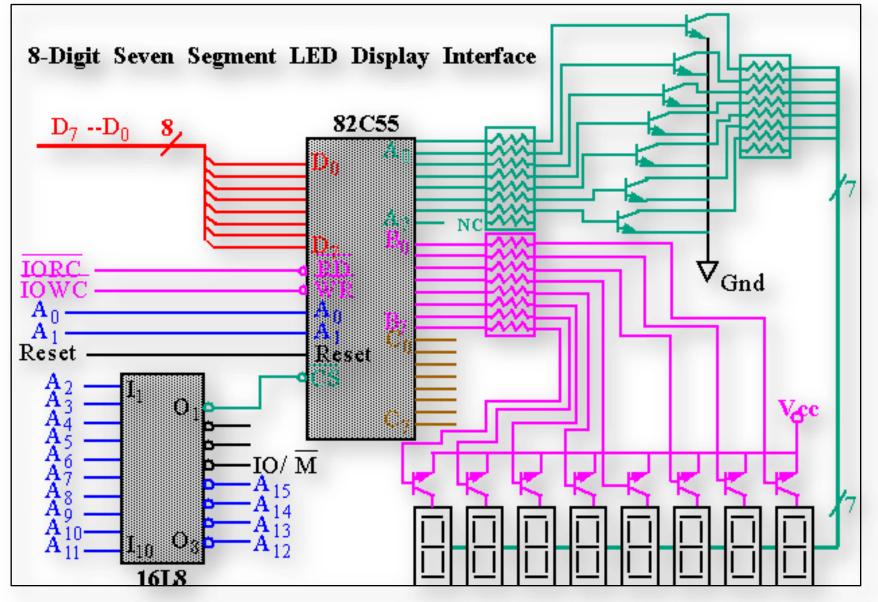

### Led interfacing with 8086 using 8255

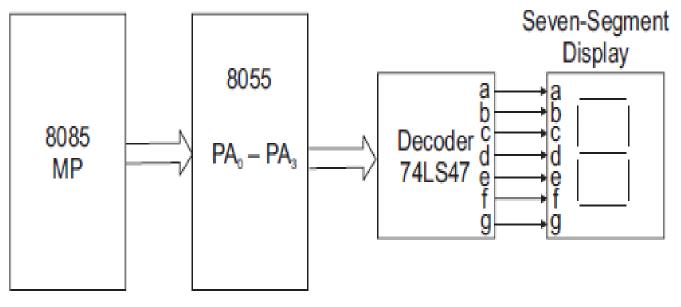

# Seven segment LED Interfacing

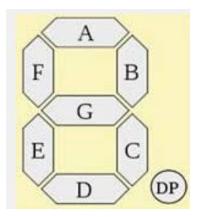

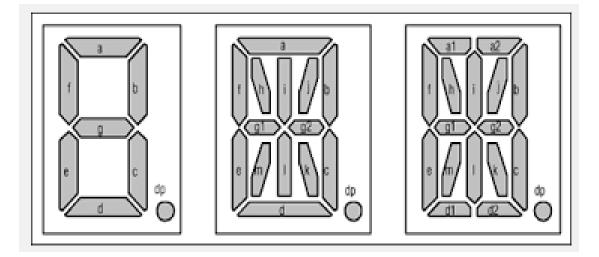

Block diagram of single-digit display

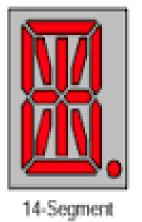

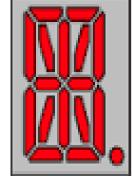

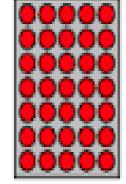

### 7, 14, 16 LED Segments

7-Segment plus DP

plus DP

16-Segment plus DP

5 x 7 Matrix

## Four seven segment displays

#### Four-Digit Display PA-PA Decoder 8085 8255 Seven-Seven-Seven-Seven-MP Segment Segment Segment ..... Segment Display Display Display Display \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* PB,-PB, MUX Block diagram of multi-digit display using multiplexer

### **8 Digit LED Display**

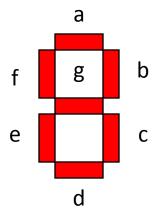

#### Seven-Segment Display

#### Table : Truth table for seven-segment display

| Decimal<br>Number | Inputs |   |   |   | Output |   |   |   |   |   |   |

|-------------------|--------|---|---|---|--------|---|---|---|---|---|---|

|                   | Α      | В | С | D | а      | b | с | d | е | f | g |

| 0                 | 0      | 0 | 0 | 0 | 1      | 1 | 1 | 1 | 1 | 1 | 0 |

| 1                 | 0      | 0 | 0 | 1 | 0      | 1 | 1 | 0 | 0 | 0 | 0 |

| 2                 | 0      | 0 | 1 | 0 | 1      | 1 | 0 | 1 | 1 | 0 | 1 |

| 3                 | 0      | 0 | 1 | 1 | 1      | 1 | 1 | 1 | 0 | 0 | 1 |

| 4                 | 0      | 1 | 0 | 0 | 0      | 1 | 1 | 0 | 0 | 1 | 1 |

| 5                 | 0      | 1 | 0 | 1 | 1      | 0 | 1 | 1 | 0 | 1 | 1 |

| 6                 | 0      | 1 | 1 | 0 | 0      | 0 | 1 | 1 | 1 | 1 | 1 |

| 7                 | 0      | 1 | 1 | 1 | 1      | 1 | 1 | 0 | 0 | 0 | 0 |

| 8                 | 1      | 0 | 0 | 0 | 1      | 1 | 1 | 1 | 1 | 1 | 1 |

| 9                 | 1      | 0 | 0 | 1 | 1      | 1 | 1 | 0 | 0 | 1 | 1 |

### 7 segment display

| Digit-abcdefg-hex |              |  |  |  |  |

|-------------------|--------------|--|--|--|--|

| 0-1111110-7E      | 1-0110000-30 |  |  |  |  |

| 2-1101101-6D      | 3-1111001-79 |  |  |  |  |

| 4-0110011-33      | 5-1011011-5B |  |  |  |  |

| 6-1011111-5F      | 7-1110000-70 |  |  |  |  |

| 8-111111-7F       | 9-1111011-7B |  |  |  |  |

| A-1110111-77      | B-0011111-1F |  |  |  |  |

| C-1001110-4E      | D-0111101-3D |  |  |  |  |

| E-1001111-4F      | F-1000111-47 |  |  |  |  |

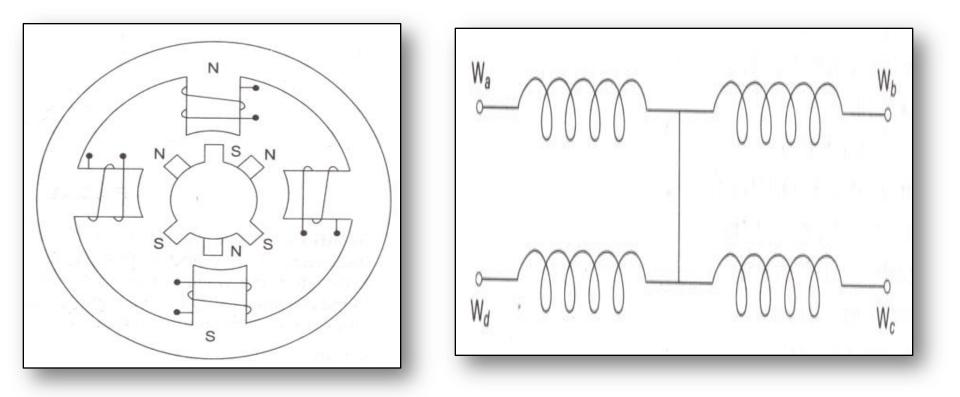

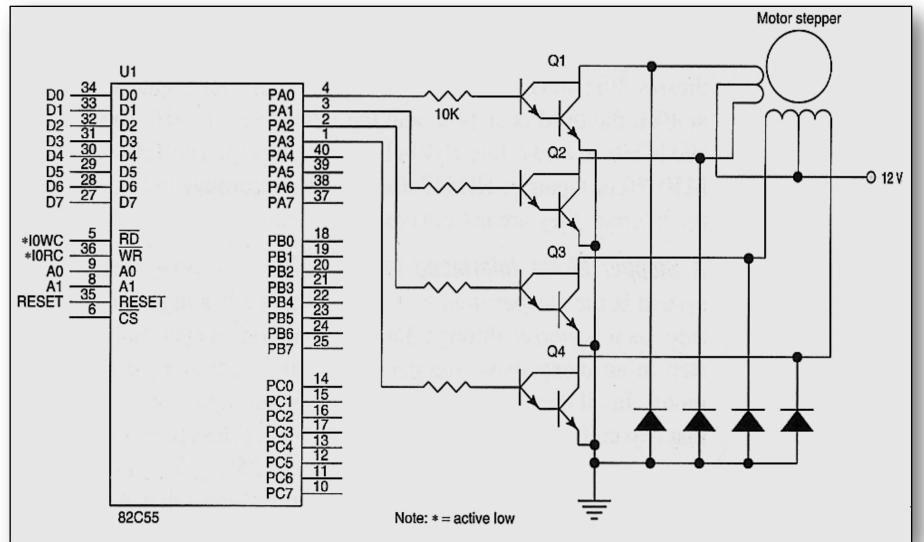

### **Stepper Motor Interface**

Fig.1 Internal schematic of a four winding stepper motor

Fig.2 Winding arrangement of a stepper motor.

### **Stepper Motor Interface**

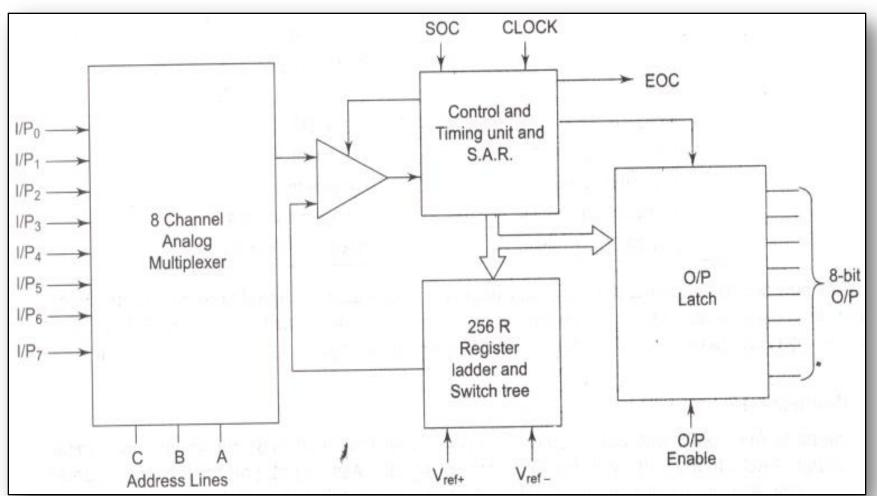

#### General algorithm for ADC interfacing contains the following steps:

- Ensure the stability of analog input, applied to the ADC.

- ➢ Issue start of conversion pulse to ADC

- $\blacktriangleright$  Read end of conversion signal to mark the end of conversion processes.

- ➢ Read digital data output of the ADC as equivalent digital output.

- Analog input voltage must be constant at the input of the ADC right from the start of conversion till the end of the conversion to get correct results. This may be ensured by a sample and hold circuit which samples the analog signal and holds it constant for specific time duration. The microprocessor may issue a hold signal to the sample and hold circuit.

- If the applied input changes before the complete conversion process is over, the digital equivalent of the analog input calculated by the ADC may not be correct.

Fig.1 Block Diagram of ADC 0808/0809

| 10000                   |    |                       |    | 1 |                    |                                         |                                                                     |

|-------------------------|----|-----------------------|----|---|--------------------|-----------------------------------------|---------------------------------------------------------------------|

| $I/P_3 \rightarrow$     | 1  |                       | 28 | * | I/P2               |                                         |                                                                     |

| $I/P_4 \rightarrow$     | 2  |                       | 27 | * | I/P1               |                                         |                                                                     |

| $I/P_5 \rightarrow$     | 3  | n na naw<br>'n nyn ei | 26 | + | I/Po               | I/P <sub>0</sub> - I/P <sub>7</sub>     | Analog inputs                                                       |

| $I/P_6 \rightarrow$     | 4  |                       | 25 | * | ADD A              | ADD A, B, C                             | Address lines for selecting analog inputs                           |

| $I/P_7 \rightarrow$     | 5  |                       | 24 | + | ADD B              | O <sub>7</sub> - O <sub>0</sub>         | Digital 8-bit output with $\mathrm{O}_7$ MSB and $\mathrm{O}_0$ LSB |

| SOC→                    | 6  |                       | 23 | * | ADD C              | SOC                                     | Start of conversion signal pin                                      |

| EOC→                    | 7  | ADC 0808              | 22 | * | ALE                | EOC                                     | End of conversion signal pin                                        |

| $O_3 \rightarrow$       | 8  | ADC 0809              | 21 | * | O7MSB              | OE                                      | Output latch enable pin, if high enable output                      |

| OE →                    | 9  |                       | 20 | * | O <sub>6</sub>     | CLK                                     | Clock input for ADC                                                 |

| CLK→                    | 10 |                       | 19 | * | O <sub>5</sub>     | V <sub>CC</sub> , GND                   | Supply pins +5V and GND                                             |

| $V_{CC} \rightarrow$    | 11 |                       | 18 | + | O <sub>4</sub>     | V <sub>ref+</sub> and V <sub>ref-</sub> | Reference voltage positive (+5 Volts maximum)                       |

| $V_{ref^+} \rightarrow$ | 12 |                       | 17 | * | O <sub>0</sub> LSB |                                         | and Reference voltage negative (0V minimum)                         |

| GND→                    | 13 |                       | 16 | * | V <sub>ref</sub> - |                                         |                                                                     |

| $0_1 \rightarrow$       | 14 |                       | 15 | * | O <sub>2</sub>     |                                         |                                                                     |

| l                       |    |                       | 1  |   |                    |                                         |                                                                     |

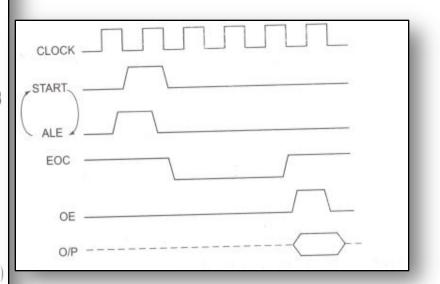

# Fig.3 Timing Diagram Of ADC 0808.

# Fig.2 Pin Diagram of ADC 0808/0809

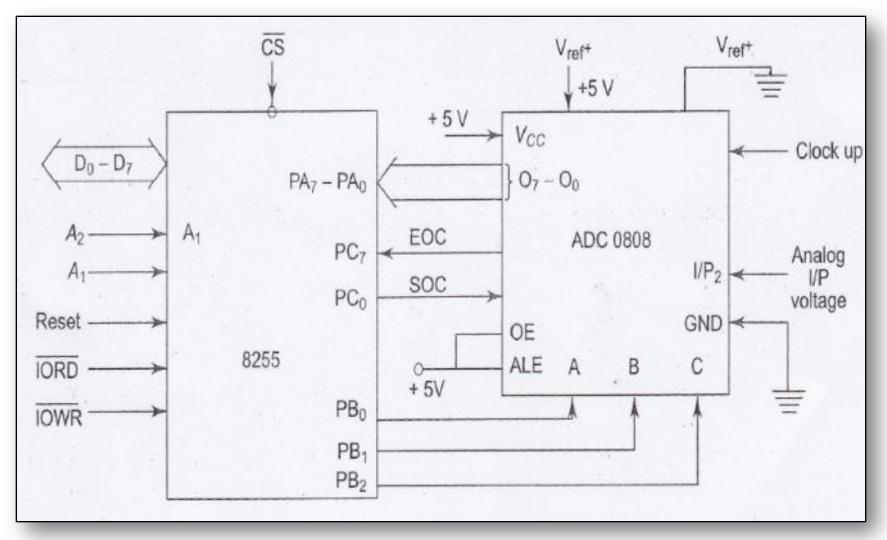

Fig: Interfacing ADC0808 with 8086

### **Interfacing Digital To Analog Converters**

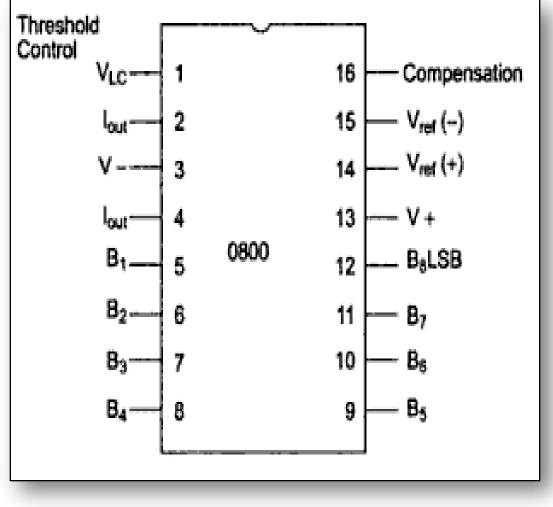

Pin Diagram of DAC 0800

### **Interfacing Digital To Analog Converters**

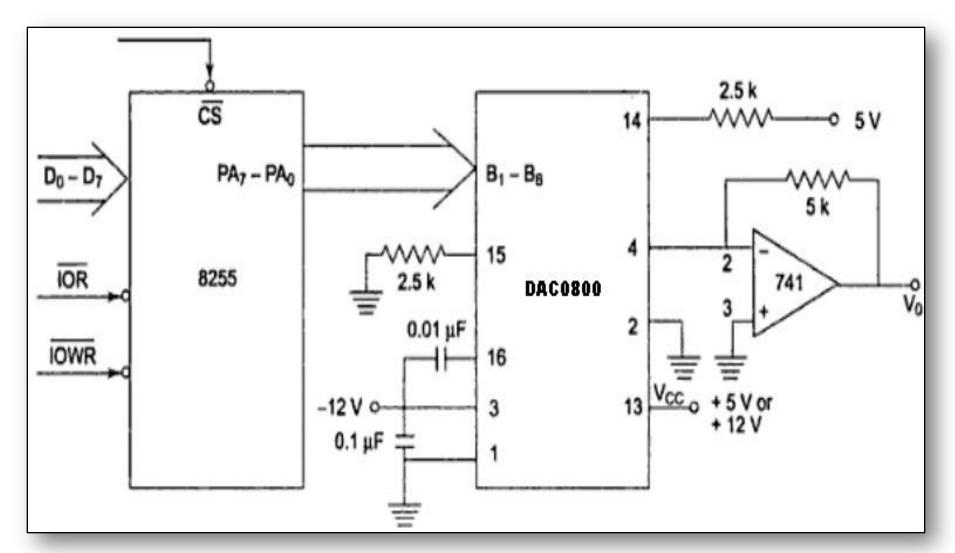

Fig:Interfacing DAC0800 with 8086

# Interfacing with advanced devices

### **Bus Architecture**

- > Address:

- ≻ If I/O, a value between 0000H and FFFFH is issued.

- $\succ$  If memory, it depends on the architecture:

- 20 -bits (8086/8088)

- 24 -bits (80286/80386SX)

- 25 -bits (80386SL/SLC/EX)

- 32 -bits (80386DX/80486/Pentium)

- 36 -bits (Pentium Pro/II/III)

### **Bus Architecture**

- Data:

- 8 -bits (8085)

- 16 -bits (8086/80286/80386SX/SL/SLC/EX)

- 32 -bits (80386DX/80486/Pentium)

- 64 -bits (Pentium/Pro/II/III)

- ➤ Control:

- Most systems have at least 4 control bus connections (active low).

- MRDC (Memory Read Control), MWRC , IORC (I/O Read Control), IOWC

# Memory Types

- > Two basic types:

- ROM: Read-only memory

- RAM: Read-Write memory

- Four commonly used memories:

- ROM

- Flash (EEPROM)

- Static RAM (SRAM)

- Dynamic RAM (DRAM)

# Memory Chips

- ➤ The data pins are typically bi-directional in read-write memories.

- The number of data pins is related to the size of the memory location. For example, an 8-bit wide (byte-wide) memory device has 8 data pins.

- Each memory device has at least one chip select (CS) or chip enable (CE) or select (S) pin that enables the memory device.

- This enables read and/or write operations.

- If more than one are present, then all must be 0 in order to perform a read or write.

### SRAM vs. DRAM

### > SRAMs

- SRAMs used for caches have access times as low as 10ns.

## > DRAMs

- SRAMs are limited in size (up to about 128Kb).

- DRAMs are available in much larger sizes, e.g., 64M X 1.

- DRAMs MUST be refreshed every 2 to 4 ms

- Since they store their value on an integrated capacitor that loses charge over time.

# Memory Address Decoding

# Memory Address Decoding

- The processor can usually address a memory space that is much larger than the memory space covered by an individual memory chip.

- In order to splice a memory device into the address space of the processor, decoding is necessary.

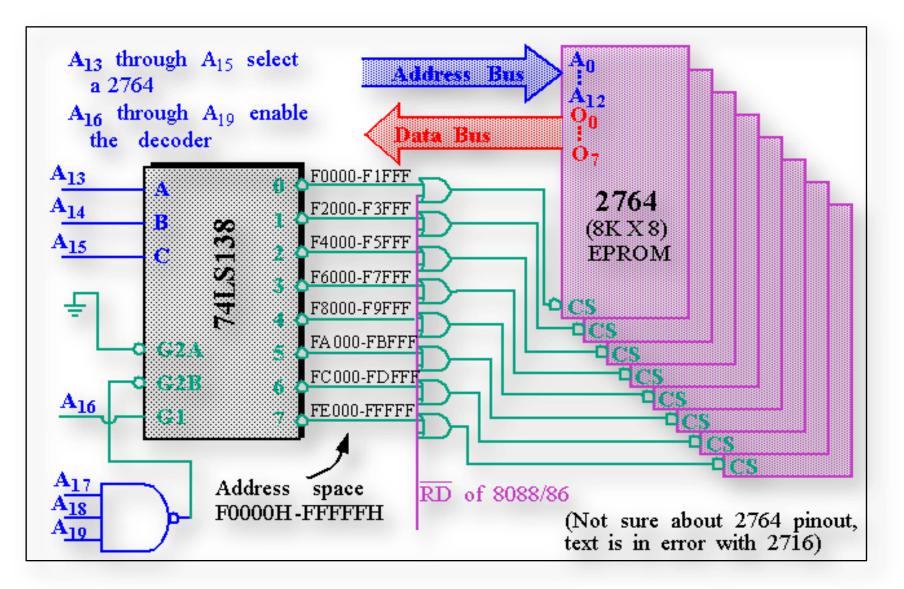

- For example, the 8088 issues 20-bit addresses for a total of 1MB of memory address space.

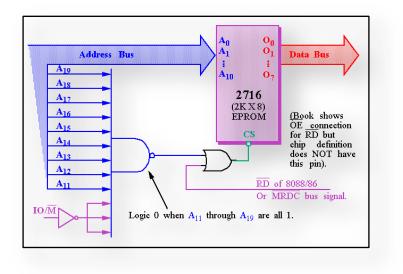

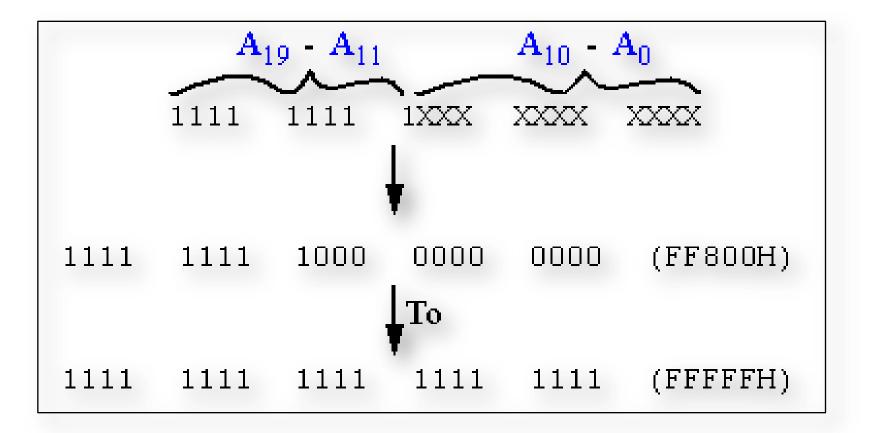

Ex. Memory Address Decoding

➤ The BIOS on a 2716 EPROM has only 2KB of memory and 11 address pins.

A decoder can be used to decode the additional 9 address pins and allow the EPROM to be placed in any 2KB section of the 1MB address space.

#### **Figure: Memory Address Decoding**

Ex. Memory Address Decoding

$\succ$  To determine the address range that a device is mapped into:

Ex. Memory Address Decoding

This 2KB memory segment maps into the reset location of the 8086/8088 (FFFF0H).

➢ NAND gate decoders are not often used. Rather the 3-to-8 Line Decoder (74LS138) is more common.

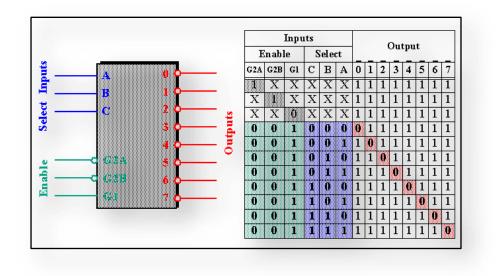

# 3-to-8 Line Decoder

- ≻ G2A, G2B, and G1 must be active.

- Each output of the decoder can be attached to an 2764 EPROM (8K X 8).

# EPROM 2764 x 8

Figure: EPROM 2764 x 8

| 19       | 9 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|------|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| £0000: 1 | 1 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| fffff: : | 1 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| ROMx:    |      |    |    |    |    |    | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|          |      |    |    |    |    |    | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| ROM1:    | 11   | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|          |      |    |    | 0  | 0  | 0  | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| ROM2:    | 11   | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|          |      |    |    | 0  | 0  | 1  | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| ROM3:    | 1 1  | 1  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|          |      |    |    | 0  | 1  | 0  | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| ROM8:    | 11   | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|          |      |    |    | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

# MEMORY INTERFACING WITH 8086

- ➤ The semi conductor memories are of two types:

- Static RAM

- Dynamic RAM

- The semiconductor memories are organized as twodimensional arrays of memory locations.

- ➢ For Ex: 4K\*8 or 4K byte memory contains 8-bit data and only one o the 4096 locations can be selected at a time.

- ➢ For addressing 4k bytes of memory, 12 address lines are required.

- For N memory locations, n address lines are required where n  $= Log2^{N}$

- > For 4096 Locations,  $n = \log 2^{4096}$

#### N=12

# **INTERRUPT STRUCTURE OF 8086**

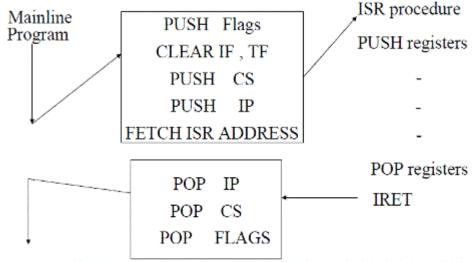

- While the CPU is executing a program, an interrupt breaks the normal sequence of execution of instructions, diverts its execution to some other program called "Interrupt Service Routine (ISR).

- •After executing ISR, the control is transferred back again to the main program which was being executed at the time of interruption.

#### **Interrupt Response**

- ➢ While the CPU is executing a program, an interrupt breaks the normal sequence of execution of instructions, diverts its execution to some other program called "Interrupt Service Routine (ISR).

- After executing ISR, the control is transferred back again to the main program which was being executed at the time of interruption.

- > Nested interrupts.

- ➤ In 8086, there are two interrupts pins: 1. NMI 2. INTR

- NMI : Non Maskable Interrupt input pin which means that any interrupt request at NMI input cannot to masked or disabled by any means.

- ➤ INTR: It can be masked using the Interrupt Flag (IF).

- ➢ If more than one type of INTR interrupt occurs at a time, then an external chip called programmable interrupt controller is required to handle them. (eg: 8259 interrupt controller).

- > There are two types of interrupts

### **1. External interrupts**

These interrupts are generated by external devices i.e out side the processor (using NMI, INTR pins). Eg: Keyboard interrupt.

### **1. Internal interrupts**

It is generated internally by the process circuit or by the execution of an interrupt instruction. Eg: INT instruction, overflow interrupt, divide by zero. At the end of each instruction cycle, the 8086 checks to see if any interrupts have been requested.

# **Types of interrupts**

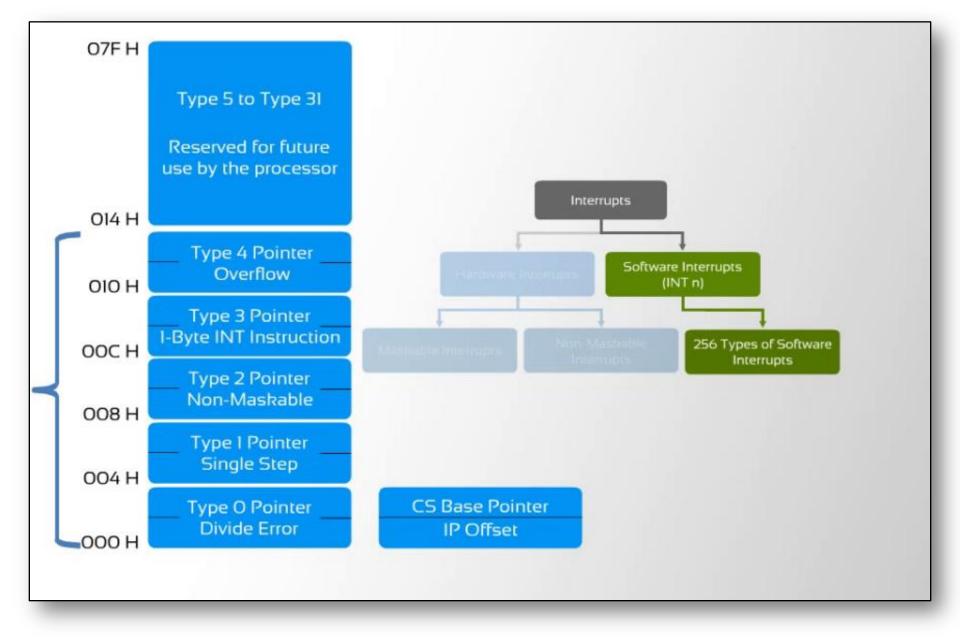

## **8086 Interrupt Vector Table**

- The first 1Kbyte of memory of 8086 (00000 to 003FF) is set aside as a table for storing the starting addresses of Interrupt Service Procedures (ISP).

- Since 4-bytes are required for storing starting addresses of ISPs, the table can hold 256 Interrupt procedures.

- The starting address of an ISP is often called the Interrupt Vector or Interrupt Pointer. Therefore the table is referred as Interrupt Vector Table.

- In this table, IP value is put in as low word of the vector & CS is put in high vector.

# **Structure of interrupt vector table**

| Interrupt Type    | Content (16-bit)                      | Address                                  | Comments                                                                                                       |  |  |  |  |

|-------------------|---------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Time 0            | ISR IP                                | 0000:0000                                | Reserved for divide by Zero                                                                                    |  |  |  |  |

| Type 0            | ISR CO                                | 0000:0002 _ i                            | nterrupt                                                                                                       |  |  |  |  |

| Type 1            | ISR IP                                | 0000:0004 - F                            | Reserved for single step                                                                                       |  |  |  |  |

|                   | ISR CS                                | 0000:0006 ii                             | nterrupt                                                                                                       |  |  |  |  |

| Type 2            | ISR IP                                | 0000:0008 -                              |                                                                                                                |  |  |  |  |

| JPC2 L            | ISR CS                                | 0000:000A                                | Reserved for NMI                                                                                               |  |  |  |  |

| Туре 3            | ISR IP                                | 0000:000C - F                            | Reserved for INT single byte                                                                                   |  |  |  |  |

| 1900 7            | ISR CS                                | 0000:000E ir                             | struction                                                                                                      |  |  |  |  |

| Time I            | ISR IP                                | 0000:0010 -                              | and the second second second                                                                                   |  |  |  |  |

| Type 4            | ISR CS                                | 0000:0012 - Reserved for INTO instructio |                                                                                                                |  |  |  |  |

| the growth of the | Let a set a set                       | 0000:0014                                | 1                                                                                                              |  |  |  |  |

|                   |                                       | 0000:0016                                | Same and shares                                                                                                |  |  |  |  |

| and the second    | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 1 1 1 A                                  | a la serve d'ad                                                                                                |  |  |  |  |

| Type N            | ISR IP                                | 0000:004N                                | Reserved for two byte                                                                                          |  |  |  |  |

|                   | ISR CS                                | 0000:(004N+2)                            | instruction INT TYPE                                                                                           |  |  |  |  |

|                   |                                       | 0000:03FC                                | 19 1. 19 1. 19 1. 19 1. 19 1. 19 1. 19 1. 19 1. 19 1. 19 1. 19 1. 19 1. 19 1. 19 1. 19 1. 19 1. 19 1. 19 1. 19 |  |  |  |  |

| ype FFH           | ISR IP                                | 0000:03FE                                | and the second                                                                                                 |  |  |  |  |

|                   | ISR CS                                | 0000:03FF                                | and the second second                                                                                          |  |  |  |  |

Figure: Structure of interrupt vector table

#### **Figure: 8086 Interrupts**

### **Special type interrupts**

## TYPE 0

The divide error : whenever the results from a division overflows or an attempt is made to divide by zero.

#### Type 1: Single-Step Interrupts

When bit 8 of the FLAGS register (trap flag) is set to 1, an interrupt number 1 is generated after the execution of every instruction. When the microprocessor enters the interrupt service routine, the T flag is automatically cleared (otherwise it would not be able to go beyond the first instruction of the interrupt service routine!).

## Type 2

The non-maskable interrupt occurs when a logic 1 is placed on the NMI input pin to the microprocessor. non-maskable—it cannot be disabled

### Type 3

A special one-byte instruction (INT 3) that uses this vector to access its interrupt-service procedure. often used to store a breakpoint in a program for debugging.

### TYPE 4

**Overflow** is a special vector used with the INTO instruction. The INTO instruction interrupts the program if an overflow condition exists.

4. Interrupt Mask Register (IMR):

This register stores the bits required to mask the interrupts inputs. IMR operates on IRR at the direction of the Priority Resolver.

- 5. Interrupt Control logic:

- This block manages the interrupt and interrupt acknowledge signals to be sent to the CPU for serving one of the 8 interrupt requests.

- This also accepts the interrupt acknowledge (INTA) signal from CPU that causes the 8259A to release vector address on to the data bus.

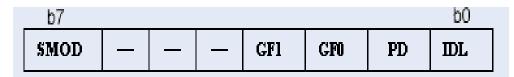

### 6. Data Bus Buffer:-

- This Tri-state bidirectional buffer interfaces internal 8259A bus the microprocessor data bus.