# DIGITAL SYSTEM DESIGN LABORATORY

### LAB MANUAL

Academic Year : 2017 - 2018

Course Code : AEC103

**Regulations**: IARE - R16

Class : IV SEMESTER

Branch : ECE

# Prepared by

K. Sudhakar Reddy Asst. Professor

K. Arun sai Asst. Professor

# Department of Electronics & Communication Engineering INSTITUTE OF AERONAUTICAL ENGINEERING

(Autonomous) Dundigal, Hyderabad – 500 043

# IARE

#### INSTITUTE OF AERONAUTICAL ENGINEERING

#### (Autonomous) Dundigal, Hyderabad – 500 043

**Electronics & Communication Engineering**

#### Vision

To produce professionally competent Electronics and Communication Engineers capable of effectively and efficiently addressing the technical challenges with social responsibility.

#### Mission

The mission of the Department is to provide an academic environment that will ensure high quality education, training and research by keeping the students abreast of latest developments in the field of Electronics and Communication Engineering aimed at promoting employability, leadership qualities with humanity, ethics, research aptitude and team spirit.

#### **Quality Policy**

Our policy is to nurture and build diligent and dedicated community of engineers providing a professional and unprejudiced environment, thus justifying the purpose of teaching and satisfying the stake holders.

A team of well qualified and experienced professionals ensure quality education with its practical application in all areas of the Institute.

#### Philosophy

The essence of learning lies in pursuing the truth that liberates one from the darkness of ignorance and Institute of Aeronautical Engineering firmly believes that education is for liberation.

Contained therein is the notion that engineering education includes all fields of science that plays a pivotal role in the development of world-wide community contributing to the progress of civilization. This institute, adhering to the above understanding, is committed to the development of science and technology in congruence with the natural environs. It lays great emphasis on intensive research and education that blends professional skills and high moral standards with a sense of individuality and humanity. We thus promote ties with local communities and encourage transnational interactions in order to be socially accountable. This accelerates the process of transfiguring the students into complete human beings making the learning process relevant to life, instilling in them a sense of courtesy and responsibility.

# **INSTITUTE OF AERONAUTICAL ENGINEERING**

(Autonomous)

Dundigal, Hyderabad – 500 043

### **Department of Electronnics and Communication Engineering**

|      | Program Outcomes                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| PO1  | <b>Engineering knowledge</b> : Apply the knowledge of mathematics, science, engineeringfundamentals, and an engineering specialization to the solution of complex engineering problems.                                                                                                                   |  |  |  |  |  |  |

| PO2  | <b>Problem analysis</b> : Identify, formulate, review research literature, and analyze complexengineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.                                                                  |  |  |  |  |  |  |

| PO3  | <b>Design/development of solutions</b> : Design solutions for complex engineering problems anddesign system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.          |  |  |  |  |  |  |

| PO4  | <b>Conduct investigations of complex problems</b> : Use research-based knowledge and researchmethods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.                                                                 |  |  |  |  |  |  |

| PO5  | <b>Modern tool usage</b> : Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.                                                                 |  |  |  |  |  |  |

| PO6  | <b>The engineer and society</b> : Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.                                                               |  |  |  |  |  |  |

| PO7  | <b>Environment and sustainability</b> : Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.                                                                                   |  |  |  |  |  |  |

| PO8  | <b>Ethics</b> : Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.                                                                                                                                                                    |  |  |  |  |  |  |

| PO9  | <b>Individual and team work</b> : Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.                                                                                                                                                   |  |  |  |  |  |  |

| PO10 | <b>Communication</b> : Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions. |  |  |  |  |  |  |

| PO11 | <b>Project management and finance</b> : Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.                                               |  |  |  |  |  |  |

| PO12 | <b>Life-long learning</b> : Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.                                                                                                                 |  |  |  |  |  |  |

|      | Program Specific Outcomes                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| PSO1 | <b>Professional Skills:</b> The ability to research, understand and implement computer programs in the areas related to algorithms, system software, multimedia, web design, big data analytics, and networking for efficient analysis and design of computer-based systems of varying complexity.        |  |  |  |  |  |  |

| PSO2 | <b>Problem-Solving Skills:</b> The ability to apply standard practices and strategies in software project development using open-ended programming environments to deliver a quality product for business success.                                                                                        |  |  |  |  |  |  |

| PSO3 | <b>Successful Career and Entrepreneurship:</b> The ability to employ modern computer languages, environments, and platforms in creating innovative career paths, to be an entrepreneur, and a zest for higher studies.                                                                                    |  |  |  |  |  |  |

# **INSTITUTE OF AERONAUTICAL ENGINEERING**

(Autonomous) Dundigal, Hyderabad - 500 043

# ATTAINMENT OF PROGRAM OUTCOMES & PROGRAM SPECIFIC OUTCOMES

| Exp.<br>No. | Experiment                                                                                            | Program<br>Outcomes<br>Attained | Program<br>Specific<br>Outcomes<br>Attained |  |  |

|-------------|-------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------|--|--|

|             | ECAD Programs                                                                                         |                                 |                                             |  |  |

|             | Realization of a Boolean function                                                                     | DO1 DO2                         | PGO1                                        |  |  |

| 1           | Design and simulate the HDL code to realize three and four variable Boolean functions                 | PO1, PO2                        | PSO1                                        |  |  |

|             | Design of decoder and encoder                                                                         |                                 | PSO1                                        |  |  |

| 2           | Design and simulate the HDL code for the following combinational circuits                             | DO1 DO2                         |                                             |  |  |

| 2           | a) 3 to 8 Decoder                                                                                     | PO1, PO2                        |                                             |  |  |

|             | b) 8 to 3 Encoder (With priority and without priority)                                                |                                 |                                             |  |  |

|             | Design of multiplexer and de multiplexer                                                              |                                 |                                             |  |  |

|             | Design and simulate the HDL code for the following                                                    |                                 | PSO1                                        |  |  |

| 3           | combinational circuits                                                                                | PO1, PO2                        |                                             |  |  |

|             | a) Multiplexer                                                                                        |                                 |                                             |  |  |

|             | b) De-multiplexer                                                                                     |                                 |                                             |  |  |

|             | Design of code converters  Design and simulate the HDL code for the following                         |                                 |                                             |  |  |

|             | combinational circuits                                                                                |                                 | PSO1                                        |  |  |

| 4           | a) 4- Bit binary to gray code converter                                                               | PO1, PO2                        |                                             |  |  |

|             | b) 4- Bit gray to binary code converter                                                               |                                 |                                             |  |  |

|             | c) Comparator                                                                                         |                                 |                                             |  |  |

|             | Full adder and full subtractor design modeling                                                        | PO1, PO2                        |                                             |  |  |

| 5           | Write a HDL code to describe the functions of a full Adder                                            |                                 | PSO1                                        |  |  |

|             | and subtractor Using three modeling styles                                                            |                                 |                                             |  |  |

| 6           | Design of 8-bit Arithmetic logic unit                                                                 | PO1, PO2                        | PSO1                                        |  |  |

|             | Design a model to implement 8-bit ALU functionality                                                   | 101,102                         | 1501                                        |  |  |

| 7           | HDL model for flip flops                                                                              | PO1, PO2                        | PSO1                                        |  |  |

| ,           | Write HDL codes for the flip-flops - SR, D, JK, T                                                     | 101,102                         | 1501                                        |  |  |

|             | Design of counters                                                                                    |                                 |                                             |  |  |

| 8           | Write a HDL code for the following counters                                                           | PO1, PO2                        | PSO1                                        |  |  |

|             | <ul><li>a) Binary counter</li><li>b) BCD counter (Synchronous reset and asynchronous reset)</li></ul> |                                 |                                             |  |  |

|             | HDL code for universal shift register                                                                 |                                 |                                             |  |  |

| 9           | Design and simulate the HDL code for universal shift register                                         | PO1, PO2                        | PSO1                                        |  |  |

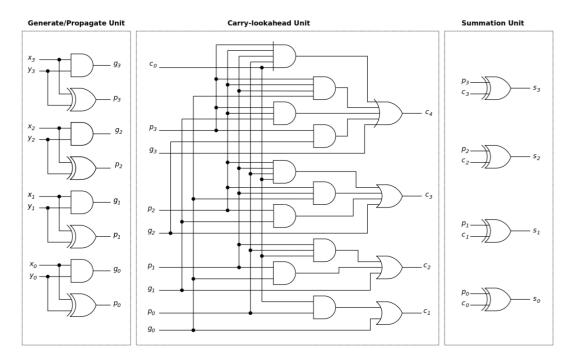

|             | HDL code for carry look ahead adder                                                                   |                                 | PSO1                                        |  |  |

| 10          | Design and simulate the HDL code for carry look ahead adder                                           | PO1, PO2                        |                                             |  |  |

|             | HDL code to detect a sequence                                                                         | DO1 DO2                         | PSO1                                        |  |  |

| 11          | Write a HDL code to detect the sequence 1010101                                                       | PO1, PO2 P                      |                                             |  |  |

| 12          | Chess clock controller FSM using HDL                                                                  | PO3,PO6                         | PSO1                                        |  |  |

|             | Design a traffic light controller using HDL                                                           | 1 00,1 00                       | 1501                                        |  |  |

| Exp.<br>No.            | Experiment                                                                       | Program<br>Outcomes<br>Attained | Program Specific Outcomes Attained |  |  |  |

|------------------------|----------------------------------------------------------------------------------|---------------------------------|------------------------------------|--|--|--|

| Content Beyond Syllabi |                                                                                  |                                 |                                    |  |  |  |

| 13                     | Traffic light controller using HDL Design a chess clock controller FSM using HDL | PO3,PO6                         | PSO1                               |  |  |  |

| 14                     | Elevator design using HDL code Write HDL code to simulate Elevator operations    | PO3,PO6                         | PSO1                               |  |  |  |

# SUCALITY OF THE PARTY OF THE PA

# **INSTITUTE OF AERONAUTICAL ENGINEERING**

(Autonomous) Dundigal, Hyderabad – 500 043

# **Certificate**

| bearing the Roll No.     | ofClass                |

|--------------------------|------------------------|

|                          | Branch                 |

| in the                   | laboratory             |

| during the Academic year | under our supervision. |

| Head of the Department   | Lecture In-Charge      |

| External Examiner        | Internal Examiner      |

#### INSTITUTE OF AERONAUTICAL ENGINEERING

(Autonomous)

Dundigal, Hyderabad – 500 043

#### **Electronics & Communication Engineering**

#### **Course Overview:**

This course gives knowledge about the design, analysis, simulation of circuits used as building blocks in Very Large Scale Integration (VLSI) devices. Students can apply the concepts learnt in the lectures towards design of actual VLSI subsystem all the way from specification, modeling, synthesis and physical design. This lab provides hands-on experience on implementation of digital circuit designs using HDL language, which are required for development of various projects and research work.

#### **Objectives:**

The course should enable the students to:

- 1. The ability to code and simulate any digital function in Verilog HDL.

- 2. Know the difference between synthesizable and non-synthesizable code.

- 3. Understand library modeling, behavioral code and the differences between them.

- 4. Understand the differences between simulator algorithms.

- 5. Learn good coding techniques per current industrial practices.

- 6. Understand logic verification using Verilog simulation.

#### **Course Outcomes:**

After completion of the course, the student will be able to:

- 1. Describe Verilog hardware description languages (HDL).

- 2. Design Digital Circuits in Verilog HDL.

- 3. Write behavioral models of digital circuits.

- 4. Write Register Transfer Level (RTL) models of digital circuits.

- 5. Verify behavioral and RTL models.

- 6. Describe standard cell libraries and FPGAs.

- 7. Synthesize RTL models to standard cell libraries and FPGAs.

- 8. Implement RTL models on FPGAs and Testing & Verification.

# INSTIT

#### INSTITUTE OF AERONAUTICAL ENGINEERING

(Autonomous)

Dundigal, Hyderabad – 500 043

**Electronics & Communication Engineering**

#### INSTRUCTIONS TO THE STUDENTS

- 1. Students should come with thorough preparation for the experiment to be conducted.

- 2. Students should take prior permission from the concerned faculty before availing the leave.

- 3. Students should come with formals and to be present on time in the laboratory.

- 4. Students will not be permitted to attend the laboratory unless they bring the practical record fully completed in all respects pertaining to the experiment conducted in the previous class.

- 5. Students will be permitted to attend laboratory unless they bring the observation book fully completed in all respects pertaining to the experiment conducted in the present class.

- 6. They should obtain the signature of the staff-in-charge in the observation book after completing each experiment.

- 7. Practical record and observation book should be maintained neatly.

# IARE OLIVER

# **INSTITUTE OF AERONAUTICAL ENGINEERING**

(Autonomous)

Dundigal, Hyderabad – 500 043

### DIGITAL SYSTEM DESIGN LAB SYLLABUS

| S. No.        | List of Experiments                            | Page No. |  |  |  |  |

|---------------|------------------------------------------------|----------|--|--|--|--|

| ECAD Programs |                                                |          |  |  |  |  |

| 1             | Realization of a Boolean function              | 29       |  |  |  |  |

| 2             | Design of decoder and encoder                  | 32       |  |  |  |  |

| 3             | Design of multiplexer and de multiplexer       | 37       |  |  |  |  |

| 4             | Design of code converters                      | 41       |  |  |  |  |

| 5             | Full adder and full subtractor design modeling | 45       |  |  |  |  |

| 6             | Design of 8-bit Arithmetic logic unit          | 48       |  |  |  |  |

| 7             | HDL model for flip flops                       | 52       |  |  |  |  |

| 8             | Design of counters                             | 56       |  |  |  |  |

| 9             | HDL code for universal shift register          | 61       |  |  |  |  |

| 10            | HDL code for carry look ahead adder            | 65       |  |  |  |  |

| 11            | HDL code to detect a sequence                  | 70       |  |  |  |  |

| 12            | Chess clock controller FSM using HDL           | 75       |  |  |  |  |

| 13            | * Traffic light controller using HDL           | 80       |  |  |  |  |

| 14            | * Elevator design using HDL code               | 84       |  |  |  |  |

<sup>\*</sup>Experiments beyond the prescribed syllabi

#### INSTITUTE OF AERONAUTICAL ENGINEERING

(Autonomous)

Dundigal, Hyderabad – 500 043

#### ELECTRONICS AND COMMUNICATION ENGINEERING

Electronic design automation (EDA) or electronic computer-aided design software (ECAD) designs and develops electronic systems such as printed circuit boards (PCBs) and integrated circuits (ICs). It allows designers to build out different alternatives and options and compare them to each other. It also generates manufacturing documentation as part of the specification used to source, fabricate, and produce PCBs.

The rapidly growing EDA industry is best understood by looking at the definition of EDA.

**Electronics** includes anything electronic, from computer chips and cell phones to controls for automobiles, etc. Everything made by the electronics industry results from designers using EDA tools and services.

**Design** is the part of the production cycle where creativity, ingenuity, and new ideas are most valued. Designers build models to understand the behavior and complex interactions of millions of constituent parts in their designs to ensure completeness, correctness, and manufacturability of the final product. Many of the designers in this field include electrical and software engineers.

**Automation** demonstrates the increasing complexity in the electronics industry today. This complexity is enabled by Moore's Law (which states that the number of transistors in integrated circuits doubles every 18 months), which drives the need for automation. Engineers need to validate their concepts, model and analyze their designs, and identify and eliminate problems before making production commitments. EDA helps ensure correct designs.

#### **Very Large Scale Integration (VLSI)**

VLSI is the process of creating an integrated circuit (IC) by combining thousands of transistors into a single chip. VLSI began in the 1970s when complex semiconductor and communication technologies were being developed. Before the introduction of VLSI technology most ICs had a limited set of functions they could perform.

The functionality of electronics equipment's and gadgets has achieved a phenomenal while their physical sizes and weights have come down drastically. The major reason is due to the rapid advances in integration technologies, which enables fabrication of millions of transistors in a single Integrated Circuit (IC) or chip. IC is a device having multiple transistors with interconnects manufactured on a single silicon substrate. Integration with a complexity of 10's of transistors is called Small Scale Integration, with 100's is Medium Scale Integration (MSI), with 1000's is Large Scale Integration (LSI), with 10,000 it is Very Large Scale Integration (VLSI) Systems of systems can

be implemented in a VLSI IC. However, with this rise in functionality of VLSI ICs, design problem has become huge and complex.

To address this complexly issue, after the design specifications are complete almost all the other steps are automated using CAD tools. However, even designs automated using CAD tools may have bugs. Also, due to extremely large size of the design space it is not possible to verify correctness of the design under all possible situations. So technique are required that can verify, without exercising exhaustive input-output combinations, that the design meets all the input specifications; this technique is called formal verification. In VLSI designs millions of transistors are packed into a single chip. This leads to manufacturing defects and all the chips need to be physically tested by giving input signals from a pattern generator and comparing responses using a logic analyzer; this process is called Testing. So, in the process of manufacturing a VLSI IC there are three broad steps: **Design-Verification-Test**.

VLSI ICs can be divided into analog, digital or mixed-signal (both analog and digital on the same chip) based on their functionality.

- Digital ICs can contain logic gates, flip-flops, multiplexers. Work using binary mathematics to process "one" and "zero" signals.

- Analog ICs, such as current mirrors, voltage followers, filters, OPAMPs etc. work by processing continuous signals.

- When single IC has both analog and digital components it is called mixed signal IC e.g, Analog to Digital Converter (ADC).

The automation algorithms and CAD tools are mainly available for digital ICs because transformation of design specifications to silicon implementation can be accomplished using logical procedures (which can be converted to algorithms and tools). However, most of the analog circuits design is like an "art" which is best performed by designers with "aid" of some CAD tools (which provides feedback to designer if the manual design is progressing fine etc.)

#### **VLSI Design flow**

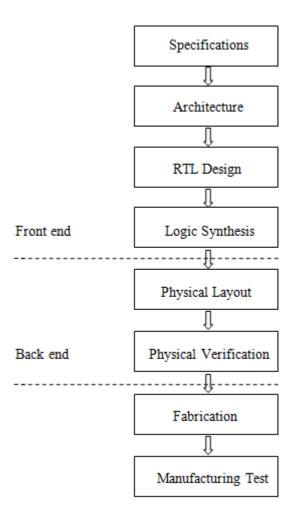

The VLSI IC circuits design flow is shown in the figure below.

- Specifications comes first, they describe abstractly the functionality, interface, and the architecture of the digital IC circuit to be designed.

- Architectural design is then created to analyze the design in terms of functionality, performance, compliance to given standards, and other specifications.

- RTL Description is done using HDLs. This RTL Description is simulated to test functionality. From here onwards we need the help of EDA tools.

- RTL Description is then converted to a gate-level netlist using logic synthesis tools. A gate-level net list is a Description of the circuit in terms of gates and connections between them, which are made in such a way that they meet the timing, power and area specifications.

- Finally a physical layout is made, which will be verified and then sent to fabrication.

The Figure provides a more simplified view of the VLSI design flow, taking into account the various representations, or abstractions of design - behavioral logic, circuit and mask layout. Note that the verification of design plays a very important role in every step during this process. The failure to properly verify a design in its early phases typically causes significant and expensive re-design at a later stage, which ultimately increases the time-to-market.

Figure 1 VLSI Design Flow

In the following, we will examine design methodologies and structured approaches which have been developed over the years to deal with both complex hardware and software projects. Regardless of the actual size of the project, the basic principles of structured design will improve the prospects of success. Some of the classical techniques for reducing the complexity of IC design are: Hierarchy, regularity, modularity and locality.

#### **DESIGN STYLES**

In 1980s when industry observed the possibility of automating the VLSI physical design using CAD tools, a new design methodology has been introduced. This new design methodology was called semi-custom VLSI design, where the design on silicon is customized as per the required application, reducing the design time and cost involved.

In comparison with full custom VLSI where the complete layout will be hand drawn and every cell is designed as per the requirements the semi-custom has the following advantages.

- Separated design approach, front end and back end

- Reduced cost as the basic cells are reused

- Less design turnaround time.

In today ASIC industry the design is portioned into front end and back end as explained below.

#### 1. Front end

- a. Enter the design in one standard format (which EDA tools can understand)

- b. Analyzing the requirements and high level design (identifying various blocks in design)

- c. RTL design evolving the necessary micro architecture for the each block

- d. VHDL, Verilog, other HDLs, Netlist etc.

- e. Developing necessary test benches for functional verification.

- f. Simulation and model verification using standard simulators

- g. Integration of all the blocks and top level simulation.

#### 2. Back end

- a. Synthesizing the design, fixing any bugs (if any part of code is not synthesizable)

- b. Floor planning as the targeted silicon area

- c. Invoking the ASIC back end tools (Mapping extracted Netlist cells to technology specific cells)

- d. Place and root as per the required timing and clock constraints

- e. Extraction of models from synthesis outputs

- f. Timing simulation and functional verification

- g. Sending the design to the FAB and getting the chip manufactured

#### **Introduction to HDL**

This section is a brief introduction to hardware design using a Hardware Description Language (HDL). A language describing hardware is quite different from C, Pascal, or other software languages. A computer program is dynamic, i.e., sharing the same resources, allocating resources when needed and not always optimized for maximum speed, optimal memory management, or lowest resource requirements. The main focus is functionality, but it is still not uncommon that software programs can behave quite unexpected. When problems arise, new versions of the programs are distributed

by the vendor, usually with a new version number and a higher price tag. The demands on hardware design are high compared to software. Often it is not possible, or at least very tricky, to patch hardware after fabrication. Clearly, the functionality must be correct and in addition how the code is written will affect the size and speed of the resulting hardware. Each mm2 of a chip costs money, lots of money. The amount of logic cells, memory blocks and input/output connections will affect the size of the design and therefore also the manufacturing cost. A software designer using a HDL has to be careful. The degrees of freedom compared with software design have dramatically increased and must be taken into account.

Hardware description languages such as Verilog differ from software programming languages because they include ways of describing the propagation time and signal strengths (sensitivity). There are two types of assignment operators; a blocking assignment (=), and a non-blocking (<=) assignment. The non-blocking assignment allows designers to describe a state-machine update without needing to declare and use temporary storage variables. Since these concepts are part of Verilog's language semantics, designers could quickly write descriptions of large circuits in a relatively compact and concise form. At the time of Verilog's introduction (1984), Verilog represented a tremendous productivity improvement for circuit designers who were already using graphical schematic capture software and specially written software programs to document and simulate electronic circuits.

The designers of Verilog wanted a language with syntax similar to the C programming language, which was already widely used in engineering software development. Like C, Verilog is case-sensitive and has a basic preprocessor (though less sophisticated than that of ANSI C/C++). Its control flow keywords (if/else, for, while, case, etc.) are equivalent, and its operator precedence is compatible with C. Syntactic differences include: required bit-widths for variable declarations, demarcation of procedural blocks (Verilog uses begin/end instead of curly braces {}), and many other minor differences. Verilog requires that variables be given a definite size. In C these sizes are assumed from the 'type' of the variable (for instance an integer type may be 8 bits).

A Verilog design consists of a hierarchy of modules. Modules encapsulate design hierarchy, and communicate with other modules through a set of declared input, output, and bidirectional ports. Internally, a module can contain any combination of the following: net/variable declarations (wire, reg, integer, etc.), concurrent and sequential statement blocks, and instances of other modules (sub-hierarchies). Sequential statements are placed inside a begin/end block and executed in sequential order within the block. However, the blocks themselves are executed concurrently, making Verilog a dataflow language.

Verilog's concept of 'wire' consists of both signal values (4-state: "1, 0, floating, undefined") and signal strengths (strong, weak, etc.). This system allows abstract modeling of shared signal lines, where multiple sources drive a common net. When a wire has multiple drivers, the wire's (readable) value is resolved by a function of the source drivers and their strengths.

A subset of statements in the Verilog language is synthesizable. Verilog modules that conform to a synthesizable coding style, known as RTL (register-transfer level), can

be physically realized by synthesis software. Synthesis software algorithmically transforms the (abstract) Verilog source into a netlist, a logically equivalent description consisting only of elementary logic primitives (AND, OR, NOT, flipflops, etc.) that are available in a specific FPGA or VLSI technology. Further manipulations to the netlist ultimately lead to a circuit fabrication blueprint (such as a photo mask set for an ASIC or a bitstream file for an FPGA).

**HDL** simulators are better than gate level simulators for 2 reasons: portable model development, and the ability to design complicated test benches that react to outputs from the model under test. Finding a model for a unique component for your particular gate level simulator can be a frustrating task; with an HDL language you can always write your own model. Also most gate level simulators are limited to simple waveform based test benches which complicate the testing of bus and microprocessor interface circuits.

- ❖ Verilog is a great low level language. Structural models are easy to design and Behavioral RTL code is pretty good. The syntax is regular and easy to remember. It is the fastest HDL language to learn and use. However Verilog lacks user defined data types and lacks the interface-object separation of the VHDL's entity-architecture model.

- ❖ VHDL is good for designing behavioral models and incorporates some of the modern object oriented techniques. It's syntax is strange and irregular, and the language is difficult to use. Structural models require a lot of code that interferes with the readability of the model.

#### Xilinx Manual:

#### 1. Introduction

Xilinx Tools is a suite of software tools used for the design of digital circuits implemented using Xilinx *Field Programmable Gate Array* (*FPGA*) or *Complex Programmable Logic Device* (*CPLD*). The design procedure consists of (a) design entry, (b) synthesis and implementation of the design, (c) functional simulation and (d) testing and verification. Digital designs can be entered in various ways using the above CAD tools: using a schematic entry tool, using a hardware description language (HDL) – Verilog or VHDL or a combination of both. In this lab we will only use the design flow that involves the use of VerilogHDL.

The CAD tools enable you to design combinational and sequential circuits starting with Verilog HDL design specifications. The steps of this design procedure are listed below:

- 1. Create Verilog design input file(s) using template driveneditor.

- 2. Compile and implement the Verilog designfile(s).

- 3. Create the test-vectors and simulate the design (functional simulation) without using a PLD (FPGA or CPLD).

- 4. Assign input/output pins to implement the design on a targetdevice.

- 5. Download bitstream to an FPGA or CPLDdevice.

- 6. Test design on FPGA/CPLDdevice

A Verilog input file in the Xilinx software environment consists of the following segments:

- 1. *Header:* module name, list of input and output ports.

- 2. **Declarations:** input and output ports, registers and wires.

- 3. *Logic Descriptions:* equations, state machines and logic functions.

- 4. *End:* endmodule

All your designs for this lab must be specified in the above Verilog input format. Note that the *state diagram* segment does not exist for combinational logic designs.

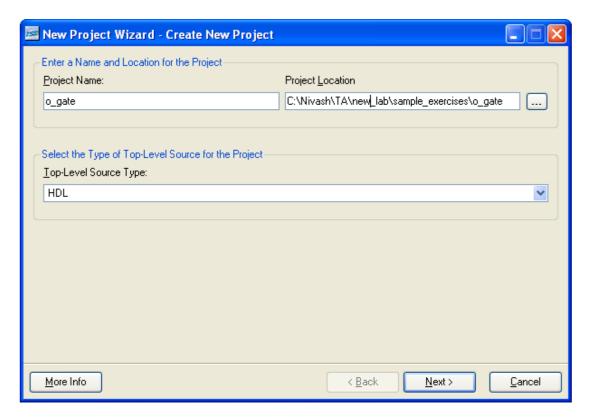

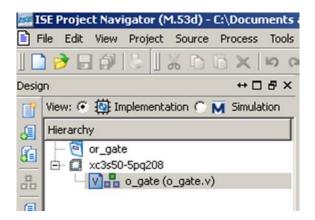

#### 2. Creating a NewProject

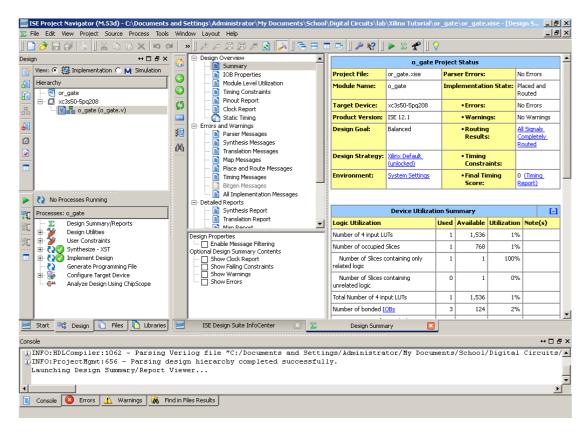

Xilinx Tools can be started by clicking on the Project Navigator Icon on the Windows desktop. This should open up the Project Navigator window on your screen. This window shows (see Figure 1) the last accessed project.

Figure 2: Xilinx Project Navigator window (snapshot from Xilinx ISE software)

#### 2.1 Openinga project

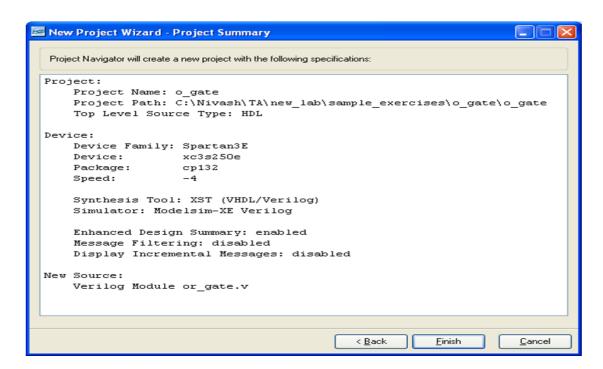

Select **File->New Project** to create a new project. This will bring up a new project window (Figure 2) on the desktop. Fill up the necessary entries as follows:

- **ProjectName**: Write the name of your newproject

- Project Location: The directory where you want to store the new project (Note: DO NOT specify the project location as a folder on Desktop or a folder in the Xilinx\bin directory. Your H: drive is the best place to put it. The project location path is NOT to have any spaces in it eg: C:\Nivash\TA\new lab\sample exercises\o\_gate is NOT to be used)

Leave the top level module type as HDL.

Example: If the project name were "o\_gate", enter "o\_gate" as the project name and then click "Next".

Figure 2: New Project Initiation window (snapshot from Xilinx ISE software)

Clicking on NEXT should bring up the following window:

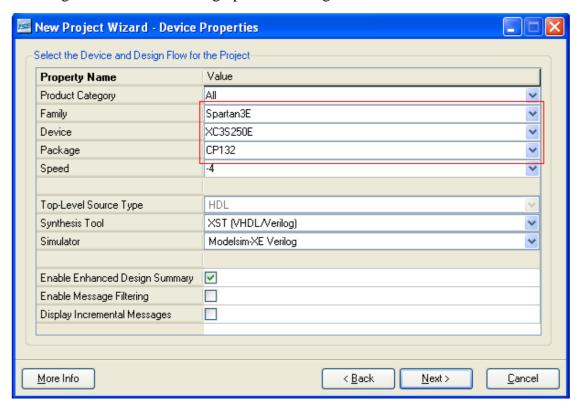

Figure 3: Device and Design Flow of Project (snapshot from Xilinx ISE software)

For each of the properties given below, click on the 'value' area and select from the list of values that appear.

- **Device Family**: Family of the FPGA/CPLD used. In this laboratory we will be using the Spartan3EFPGA's.

- Device: The number of the actual device. For this lab you may enter XC3S250E

- (this can be found on the attached prototyping board)

- **Package**: The type of package with the number of pins. The Spartan FPGA used in this lab is packaged in CP132package.

- **Speed Grade**: The Speed grade is "-4".

- **Synthesis Tool**: **XST**[VHDL/Verilog]

- **Simulator:** The tool used to simulate and verify the functionality of the design. Modelsim simulator is integrated in the Xilinx ISE. Hence choose "Modelsim-XE Verilog" as the simulator or even Xilinx ISE Simulator can be used.

- Then click on **NEXT** to save theentries.

All project files such as schematics, netlists, Verilog files, VHDL files, etc., will be stored in a subdirectory with the project name. A project can only have one top level HDL source file (or schematic). Modules can be added to the project to create a modular, hierarchical design.

In order to open an existing project in Xilinx Tools, select **File->Open Project** to show the list of projects on the machine. Choose the project you want and click **OK**.

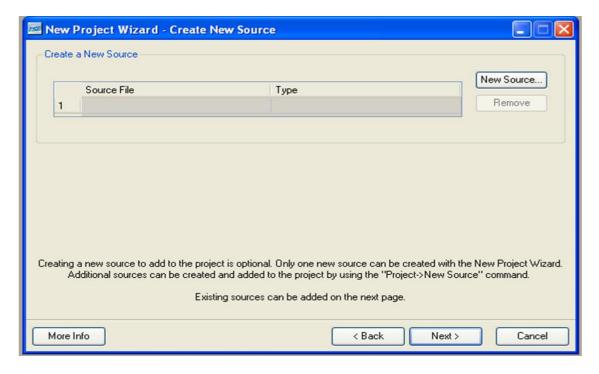

Clicking on NEXT on the above window brings up the following window:

Figure 4: Create new source window (snapshot from Xilinx ISE software)

If creating a new source file, Click on the NEW SOURCE.

#### 2.2 Creating a Verilog HDL input file for a combinational logic design

In this lab we will enter a design using a structural or RTL description using the Verilog HDL. You can create a Verilog HDL input file (.v file) using the HDL Editor available in the Xilinx ISE Tools (or any text editor).

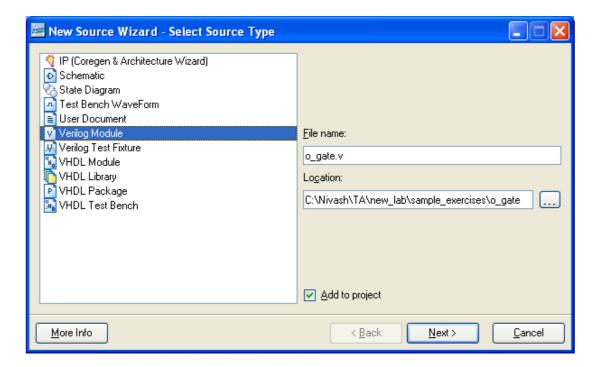

In the previous window, click on the NEW SOURCE

A window pops up as shown in Figure 4. (Note: "Add to project" option is selected by default. If you do not select it then you will have to add the new source file to the project manually.)

Figure 5: Creating Verilog-HDL source file (snapshot from Xilinx ISE software)

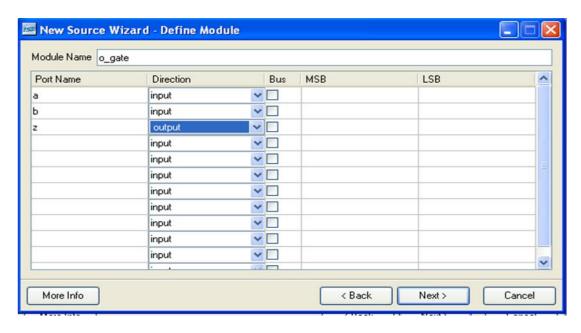

Select Verilog Module and in the "File Name:" area, enter the name of the Verilog source file you are going to create. Also make sure that the option Add to project is selected so that the source need not be added to the project again. Then click on Next to accept the entries. This pops up the following window (Figure 5).

In the **Port Name** column, enter the names of all input and output pins and specify the **Direction** accordingly. A Vector/Bus can be defined by entering appropriate bit numbers in the **MSB/LSB** columns. Then click on **Next**>to get a window showing all the new source information (Figure 6). If any changes are to be made, just click on **<Back** to go back and make changes. If everything is acceptable, click on **Finish** > **Next** > **Next** > **Finish** tocontinue.

Figure 6: Define Verilog Source window (snapshot from Xilinx ISE software)

Figure 7: New Project Informationwindow(snapshot from Xilinx ISE software)

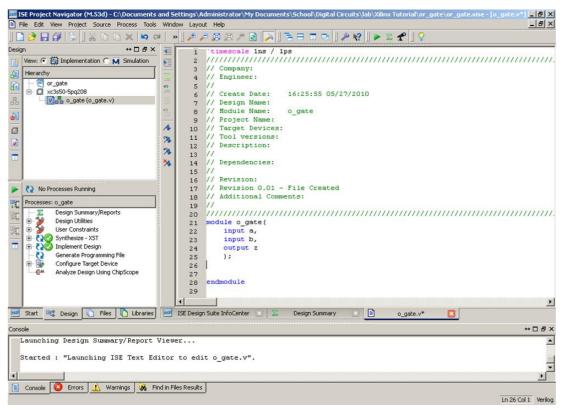

Once you click on **Finish**, the source file will be displayed in the sources window in the **Project Navigator** (Figure 1).

If a source has to be removed, just right click on the source file in the **Sources in Project window** in the **Project Navigator** and select **Remove**in that. Then select **Project -> Delete Implementation Data** from the Project Navigator menu bar to remove any relatedfiles.

#### 2.3 Editing the Verilog source file

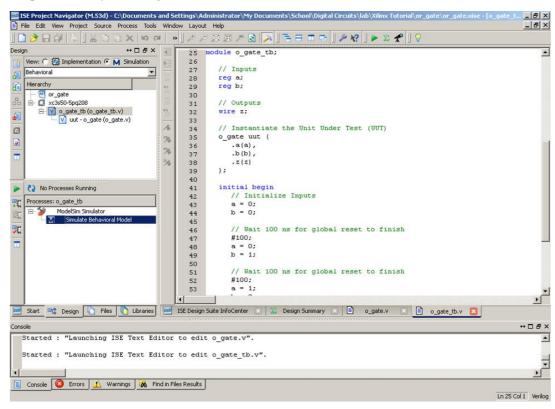

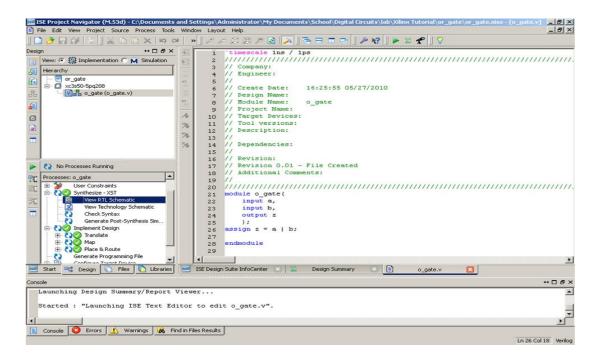

The source file will now be displayed in the **Project Navigator** window (Figure 8). The source.

Filewindowcanbeusedasatexteditortomakeanynecessarychangestothesourcefile. Allthe input/output pins will be displayed. Save your Verilog program periodically by selecting the **File->Save** from the menu. You can also edit Verilog programs in any text editor and add them to the project directory using "Add Copy Source".

Figure 8: Verilog Source code editor window in the Project Navigator (from Xilinx ISE software)

#### 3. Functional Simulation of CombinationalDesigns

#### 3.1 Adding the test vectors

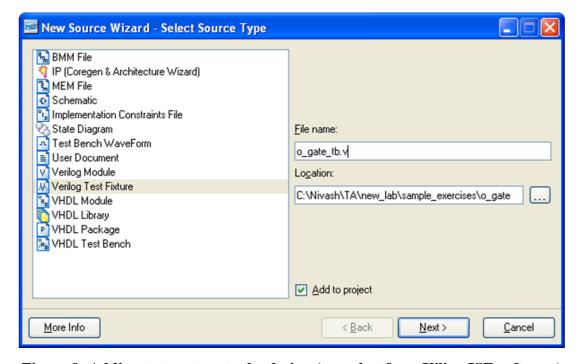

To check the functionality of a design, we have to apply test vectors and simulate the circuit. In order to apply test vectors, a test bench file is written. Essentially it will supply all the inputs to the module designed and will check the outputs of the module. Example: For the 2 input OR Gate, thesteps to generate the test bench are as follows:

In the Sources window (top left corner) right click on the file that you want to generate the test bench for and select 'New Source'

Provide a name for the test bench in the file name text box and select 'Verilog test fixture' among the file types in the list on the right side as shown in figure 9.

Figure 9: Adding test vectors to the design (snapshot from Xilinx ISE software)

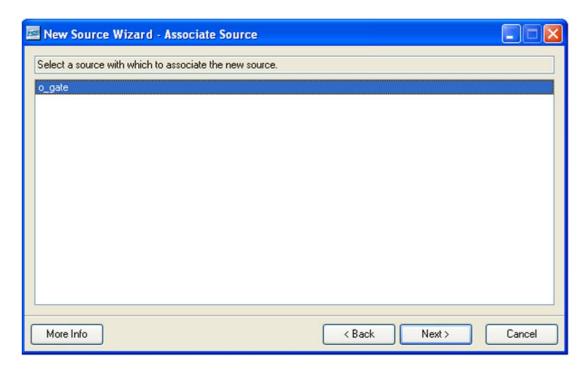

Click on 'Next' to proceed. In the next window select the source file with which you want to associate the test bench.

Figure 10: Associating a module to a testbench (snapshot from Xilinx ISE software)

Click on Next to proceed. In the next window click on Finish. You will now be provided with a template for your test bench. If it does not open automatically click the radio button next to **Simulation**.

You should now be able to view your test bench template.

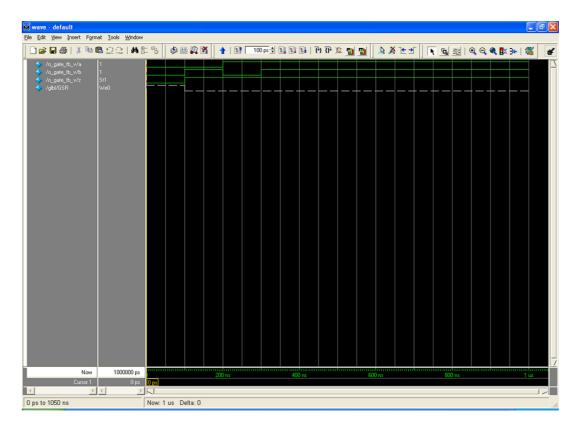

#### 3.2 Simulating and Viewing the OutputWaveforms

Now under the **Processes window** (making sure that the test bench file in the **Sources window** is selected) expand the **ModelSim simulator Tab** by clicking on the add sign next to it. Double Click on **Simulate Behavioral Model**. You will probably receive a complier error. This is nothing to worry about – answer "No" when asked if you wish to abort simulation. This should cause ModelSim to open. Wait for it to

complete execution. If you wish to not receive the compiler error, right click on **Simulate Behavioral Model** and select process properties. Mark the checkbox next to "Ignore Pre-Complied Library Warning Check".

Figure 11: Simulating the design (snapshot from Xilinx ISE software)

#### 3.3 Saving the simulation results

To save the simulation results, Go to the waveform window of the Modelsim simulator, Click on File -> Print to Postscript -> give desired filename and location.

Note that by default, the waveform is "zoomed in" to the nanose condlevel. Use the zoom controls to display the entire waveform.

Else a normal print screen option can be used on the waveform window and subsequently stored in Paint.

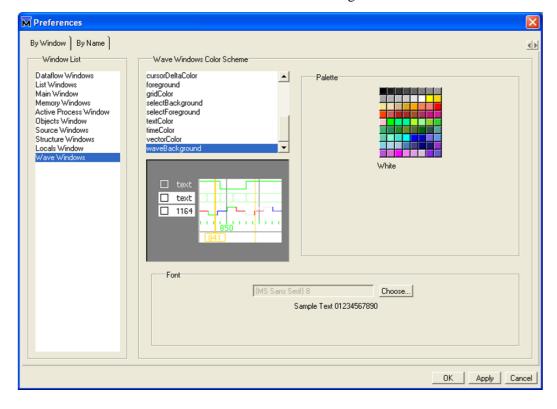

Figure 12: Behavioral Simulation output Waveform (Snapshot from ModelSim)

For taking printouts for the lab reports, convert the black background to white in Tools -> Edit Preferences. Then click Wave Windows -> Wave Background attribute.

Figure 13: Changing Waveform Background in ModelSim

#### 4. Synthesis and Implementation of the Design

The design has to be synthesized and implemented before it can be checked for correctness, by running functional simulation or downloaded onto the prototyping board. With the top-level Verilog file opened (can be done by double-clicking that file) in the HDL editor window in the right half of the Project Navigator, and the view of the project being in the **Module view**, the **implement design** option can be seen in the **process view**. **Design entry utilities** and **Generate Programming File** options can also be seen in the process view. The former can be used to include user constraints, if any and the latter will be discussed later.

To synthesize the design, double click on the **Synthesize Design** option in the **Processes window**.

To implement the design, double click the Implement design option in the Processes window. It will go through steps like Translate, Map and Place & Route. If any of these steps could not be done or done with errors, it will place a X mark in front of that, otherwise a tick mark will be placed after each of them to indicate the successful completion. If everything is done successfully, a tick mark will be placed before the Implement Design option. If there are warnings, one can see I mark in front of the option indicating that there are some warnings. One can look at the warnings or errors in the Console window present at the bottom of the Navigator window. Every time the design file is saved; all these marks disappear asking for a freshcompilation.

Figure 14: Implementing the Design (snapshot from Xilinx ISE software)

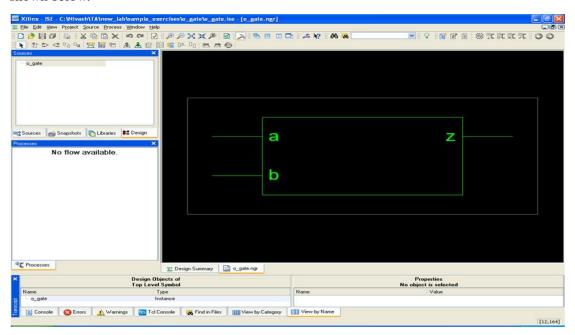

The schematic diagram of the synthesized verilog code can be viewed by double clicking View RTL Schematic under Synthesize-XST menu in the Process Window. This would be a handy way to debug the code if the output is not meeting our specifications in the proto type board.

By double clicking it opens the top level module showing only input(s) and output(s) as shown below.

Figure 15: Top Level Hierarchy of the design

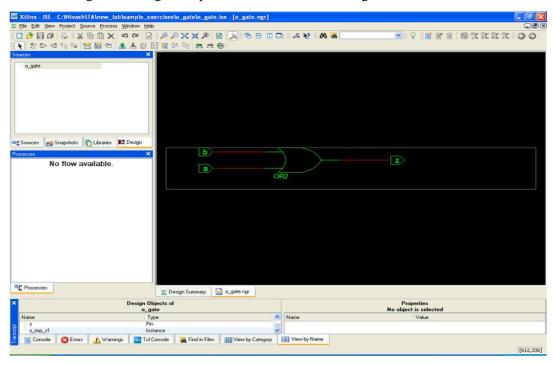

By double clicking the rectangle, it opens the realized internal logic asshown below.

Figure 16: Realized logic by the XilinxISE for the verilog code

#### EXPERIMENT 1

#### REALIZATION OF A BOOLEAN FUNCTION

#### 1.1. OBJECTIVE

Design and simulate the HDL code to realize three and four variable Boolean functions

#### 1.2. RESOURCES

PC installed with Xilinx tool

#### 1.3. PROGRAM LOGIC

A multi variable Boolean function can be implemented through Verilog HDL in two ways. First one is using primitive gates and the second one is using assign statements.

Gate primitives are predefined in Verilog, which are ready to use. They are instantiated like modules. There are two classes of gate primitives: Multiple input gate primitives and Single input gate primitives. Multiple input gate primitives include and, nand, or, nor, xor, and xnor. These can have multiple inputs and a single output. Single input gate primitives include not, buf, notif1, bufif1, notif0, and bufif0. These have a single input and one or more outputs.

Assign statements are used to define signal values as Boolean expressions. In the example: out = AS' + BS, out is defined by the function AS' + BS, but must be written in Verilog using the AND operator ("&"), OR operator ("|"), the XOR operator ("\") and the NOT operator ("\"). It is important to remember that an assignment statement is identical to the corresponding schematic with gates wired to the inputs and outputs to define the Boolean function. In fact, assign statements are known as "continuous assignments" because, unlike assignment statements in a regular programming language, they are executed continuously, just like the corresponding gates in a schematic.

#### 1.4. PROCEDURE

- 1. Create a module with required number of variables and mention it's input/output.

- 2. Write the description of given Boolean function using operators or by using the built in primitive gates.

- 3. Create another module referred as test bench to verify the functionality.

- 4. Follow the steps required to simulate the design and compare the obtained output with the corresponding truth table.

#### 1.5. CODE

```

// logic gates

module p1(c,a,b);

input a;

input b;

output [0:6] c;

assign c[0]=a \& b;

assign c[1]=a \mid b;

assign c[2] = \sim (a \& b);

assign c[3] = \sim (a \mid b);

assign c[4]=a \wedge b;

assign c[5] = \sim (a \wedge b);

assign c[6] = \sim a;

endmodule

//boolean function

module p1(a,b,c,f1,f2);

input a,b,c;

output f1,f2;

assign f1=(-a)\&b|a\&(-b)\&(-c)|a\&(-b)\&c;

assign f2=((\sim a)|b)&(a|b|(\sim c))&(a|(\sim b)|c);

endmodule

```

#### 1.6. PRE LAB QUESTIONS

- 1. Expand "VERILOG".

- 2. What are the different ways of modeling in Verilog?

- 3. What is the difference between main module and test bench module?

- 4. What are the different tools available for simulation?

- 5. What is meant by universal gate? List them.

#### 1.7. LAB ASSIGNMENT

- 1. Realize all basic gates using NAND gate.

- 2. Realize all basic gates using NOR gate.

- 3. Write structural level program for a simple gate level circuit.

- 4. Write code to simulate the following expression in dataflow and structural modeling.

```

F(w,x,y,z) = \Sigma(1,5,8,9,12,13,14)

```

#### 1.8. POST LAB QUESTIONS

- 1. What are the two main data types in Verilog HDL?

- 2. Name two logic primitive gates.

- 3. What statement is primarily used to describe a design in the dataflow style?

- 4. What is the difference between unary and logical operators?

- 5. Write the different types of port modes.

#### **EXPERIMENT 2**

#### DESIGN OF DECODER AND ENCODER

#### 2.1. OBJECTIVE

To design and simulate the HDL code for the following combinational circuits

- a. 3 to 8 Decoder

- b. 8 to 3 Encoder (With priority and without priority)

#### 2.2. RESOURCES

PC installed with Xilinx tool

#### 2.3. PROGRAM LOGIC

#### a. Program logic for Decoder

A decoder is a multiple-input, multiple-output logic circuit which converts coded inputs into coded outputs, where the input and output codes are different. The input code generally has fewer bits than the output code. Each input code word produces a different output code word, i.e., there is one-to-one mapping from input code words into output code words. This one-to-one mapping can be expressed in a truth table.

The most common decoder circuit is an n-to-2<sup>n</sup> decoder or binary decoder. Such a decoder has an n-bit binary input code and a 1-out-of-2<sup>n</sup> output code. A binary decoder is used when you need to activate exactly one of 2<sup>n</sup>outputs based on an n-bit input value.

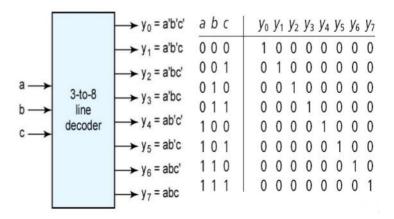

Figure 2.1 shows the general structure of the 3 to 8 decoder circuit and its truth table.

Figure 2.1: General Structure of 3 to 8 Decoder and its truth table

#### b. Program logic for Encoder

An encoder has M input and N output lines. Out of M input lines only one is activated at a time and produces equivalent code on output N lines. If a device output code has fewer bits than the input code has, the device is usually called an encoder. Example Octal-to-Binary take 8 inputs and provides 3 outputs. For an 8-to-3 binary encoder with inputs D0-D7 the logic expressions of the outputs XYZ are obtained by using the Table 3.1.

$$X = D4 + D5 + D6 + D7$$

$Y = D2 + D3 + D6 + D7$

$Z = D1 + D3 + D5 + D7$

Table 3.1: Truth Table for 8-3 Encoder with D7-D0 inputs

| INPUTS         |           |           |           |           |           |           | OUTPUTS   |   |   |              |

|----------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|---|---|--------------|

| <b>D7</b>      | <b>D6</b> | <b>D5</b> | <b>D4</b> | <b>D3</b> | <b>D2</b> | <b>D1</b> | <b>D0</b> | X | Y | $\mathbf{Z}$ |

| $O_0$          | 0         | 0         | 0         | 0         | 0         | 0         | 1         | 0 | 0 | 0            |

| $^{n}0$        | 0         | 0         | 0         | 0         | 0         | 1         | 0         | 0 | 0 | 1            |

| e 0            | 0         | 0         | 0         | 0         | 1         | 0         | 0         | 0 | 1 | 0            |

| 0              | 0         | 0         | 0         | 1         | 0         | 0         | 0         | 0 | 1 | 1            |

| o0             | 0         | 0         | 1         | 0         | 0         | 0         | 0         | 1 | 0 | 0            |

| f 0            | 0         | 1         | 0         | 0         | 1         | 0         | 0         | 1 | 0 | 1            |

| 0              | 1         | 0         | 0         | 0         | 0         | 1         | 0         | 1 | 1 | 0            |

| O <sub>1</sub> | 0         | 0         | 0         | 0         | 0         | 0         | 1         | 1 | 1 | 1            |

One of the main disadvantages of standard digital encoders is that they can generate the wrong output code when there is more than one input present at logic level "1".

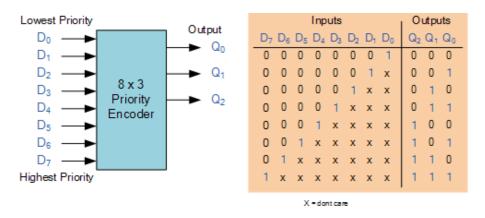

The Priority Encoder solves the problems mentioned above by allocating a priority level to each input. The priority encoders output corresponds to the currently active input which has the highest priority. So when an input with a higher priority is present, all other inputs with a lower priority will be ignored. The priority encoder comes in many different forms with an example of an 8-input priority encoder along with its truth table shown in Figure 2.2

Figure 2.2: General Structure of 3 to 8 Decoder and its truth table

Decoder or encoder can be designed using HDL through its truth table in two ways: one is using gate level modeling and another is by behavioral model.

#### 2.4. PROCEDURE

- 1. Create a module with required number of variables and mention it's input/output.

- 2. Implement the logic for decoder or encoder using behavioral or gate level model.

- 3. Create another module referred as test bench to verify the functionality.

- 4. Follow the steps required to simulate the design and compare the obtained output with the corresponding truth table.

#### 2.5. CODE

```

// 8 to 3 Encoder without priority

module p2(d,e);

input [7:0] d;

output [2:0]e;

assign e[2] = d[4] | d[5] | d[6] | d[7];

assign e[1] = d[2] | d[3] | d[6] | d[7];

assign e[0] = d[1] | d[3] | d[5] | d[7];

endmodule

// 8 to 3 Encoder with priority

module p4(din, dout);

input [7:0] din;

output [2:0] dout;

reg [2:0] dout;

always @(din)

begin

if (din[7]==1'b1) dout=3'b111;

```

```

else if (din[6]==1'b1) dout=3'b110;

else if (din[5]==1'b1) dout=3'b101;

else if (din[4]==1'b1) dout=3'b100;

else if (din[3]==1'b1) dout=3'b011;

else if (din[2]==1'b1) dout=3'b010;

else if (din[1]==1'b1) dout=3'b001;

else if (din[0]==1'b1) dout=3'b000;

else dout=3'bXXX;

end

endmodule

// 3 to 8 decoder

module p3(i,d);

input [2:0]i;

output [7:0]d;

assign d[0]=(\sim i[2])\&(\sim i[1])\&(\sim i[0]);

assign d[1]=(\sim i[2])\&(\sim i[1])\&(i[0]);

assign d[2]=(\sim i[2])\&(i[1])\&(\sim i[0]);

assign d[3]=(\sim i[2])\&(i[1])\&(i[0]);

assign d[4]=(i[2])&(\sim i[1])&(\sim i[0]);

assign d[5]=(i[2])&(\sim i[1])&(i[0]);

assign d[6]=(i[2])&(i[1])&(\sim i[0]);

assign d[7]=(i[2])&(i[1])&(i[0]);

endmodule

```

#### 2.6. PRE LAB QUESTIONS

- 1. What is a decoder?

- 2. What for enable inputs are used in decoder?

- 3. What are the applications of decoder?

- 4. What is an encoder?

- 5. What is a priority encoder?

- 6. How many input and output lines are there for a 128x7 encoder.

#### 2.7. LAB ASSIGNMENT

- 1. Implement full adder circuit using decoder and two OR gates.

- 2. Implement 3x8 decoder using 2x4 decoder and additional logic.

- 3. Construct a 4x16 decoder using two 3x8 decoder and additional logic. Show the schematic diagram neatly?

- 4. Design 2-to-4 decoder using only NOR gates.

- 5. Construct a 5 x 32 decoder with four 3x 8 decoders with enable and one 2 x 4 decoder.

- 6. Write a Verilog code to implement Octal-to-Binary Encoder?

- 7. Write a Verilog code to implement a 8x3 Priority Encoder?

- 8. Write a Verilog code to implement Decimal-to-BCD Encoder?

## 2.8. POST LAB QUESTIONS

- 1. What is the key difference between an initial statement and an always statement?

- 2. Name two kinds of assignments that you can have in a Verilog HDL model.

- 3. Create a Verilog module named h6to64 that represents a 6-to-64 binary decoder. Use the treelike structure in which the 6-to-64 decoder is built using nine instances of the 3to8 decoder.

- 4. Write code for a parallel encoder and a priority encoder.

- 5. What is the difference between wire and reg data type?

- 6. What is the difference between the following two lines of Verilog code?

$$#5 a = b;$$

$a = #5 b;$

7. What is the use of Priority Encoder?

# DESIGN OF MULTIPLEXER AND DEMULTIPLEXER

### 3.1. OBJECTIVE

To write HDL codes for an 8X1 multiplexer and 1X8 demultiplexerand verify its functionality.

### 3.2. RESOURCES

PC installed with Xilinx tool

### 3.3. PROGRAM LOGIC

In the large-scale-digital systems, a single line is required to carry on two or more digital signals – and, of course! At a time, one signal can be placed on the one line. But, what is required is a device that will allow us to select; and, the signal we wish to place on a common line, such a circuit is referred to as multiplexer.

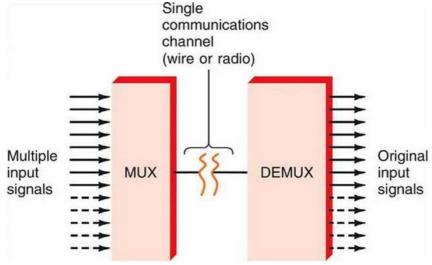

The function of a multiplexer is to select the input of any 'n' input lines and feed that to one output line. The function of a de-multiplexer is to inverse the function of the multiplexer and the shortcut forms of the multiplexer. The de-multiplexers are mux and demux. Some multiplexers perform both multiplexing and de-multiplexing operations. The main function of the multiplexer is that it combines input signals, allows data compression, and shares a single transmission channel.

Figure 3.1 Multiplexer and De-multiplexer

The output value of a 8x1 multiplexer can be represented using the equation (3.1)

$$Y = \overline{S_2} \overline{S_1} \overline{S_0} I_o + \overline{S_2} \overline{S_1} S_0 I_1 + \overline{S_2} S_1 \overline{S_0} I_2 + \overline{S_2} S_1 S_0 I_3 + S_2 \overline{S_1} \overline{S_0} I_4 + S_2 \overline{S_1} S_0 I_5 + S_2 S_1 \overline{S_0} I_6 + S_2 S_1 S_0 I_7$$

$$\dots (3.1)$$

For the combination of selection input, the data line is connected to the output line. The 8x1 multiplexer requires 8 AND gates, one OR gate and 3 selection lines. As an input, the combination of selection inputs are giving to the AND gate with the corresponding input data lines.

In a similar fashion, all the AND gates are given connection. In this 8x1 multiplexer, for any selection line input, one AND gate gives a value of 1 and the remaining all AND gates give 0. And, finally, by using OR gate, all the AND gates are added; and, this will be equal to the selected value.

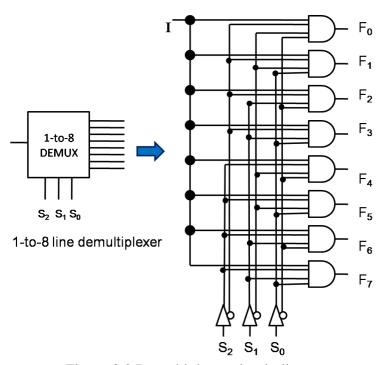

The demultiplexer is also called as data distributors as it requires one input, 3 selected lines and 8 outputs. De-multiplexer takes one single input data line, and then switches it to any one of the output line. 1-to-8 demultiplexer circuit diagram is shown below; it uses 8 AND gates for achieving the operation. The input bit is considered as data D and it is transmitted to the output lines.

Figure 3.2 Demultiplexer circuit diagram

#### 3.4. PROCEDURE

- 1. Create a module with required number of variables and mention it's input/output.

- 2. Write the description of the multiplexer or demultiplexer using data flow model or gate level model

- 3. Create another module referred as test bench to verify the functionality.

- 4. Follow the steps required to simulate the design and compare the obtained output with the corresponding truth table.

### **3.5. CODE**

```

// 8:1 multiplexer

module p5(s,i,y);

input [7:0]i;

input [2:0]s;

output y;

wire [2:0]sb;

not(sb[0],s[0]);

not(sb[1],s[1]);

not(sb[2],s[2]);

assign y = (sb[2]\&sb[1]\&sb[0]\&i[0]) | (sb[2]\&sb[1]\&s[0]\&i[1]) |

(sb[2]&s[1]&sb[0]&i[2]) | (sb[2]&s[1]&s[0]&i[3]) | (s[2]&sb[1]&sb[0]&i[4]) |

(s[2]\&sb[1]\&s[0]\&i[5]) | (s[2]\&s[1]\&sb[0]\&i[6]) | (s[2]\&s[1]\&s[0]\&i[7]);

endmodule

//1:8 Demultiplexer

module p6(din,s,dout);

output [7:0]dout;

input din;

input [2:0]s;

assign dout[7] = din & (s[2]) & (s[1]) & (s[0]);

assign dout[6] = din & (s[2]) & (s[1]) & (\sim s[0]);

assign dout[5] = din & (s[2]) & (\sims[1]) & (s[0]);

assign dout[4] = din & (s[2]) & (\sims[1]) & (\sims[0]);

assign dout[3] = din & (\sims[2]) & (s[1]) & (s[0]);

assign dout[2] = din & (\sims[2]) & (s[1]) & (\sims[0]);

assign dout[1] = din & (\sims[2]) & (\sims[1]) & (s[0]);

assign dout[0] = din & (\sims[2]) & (\sims[1]) & (\sims[0]);

endmodule

```

### 3.6. PRE LAB QUESTIONS

- 1. What is a multiplexer?

- 2. What is the relationship between input lines and select lines?

- 3. Why a multiplexer is called a data selector?

- 4. Mention the applications of multiplexer and demultiplexer.

### 3.7. LAB ASSIGNMENT

- 1. Implement a full adder with two 4x1 multiplexers.

- 2. Implement 2 to 4 decoder using 1x4 demultiplexer.

- 3. Implement a full subtractor with two 4x1 multiplexers.

- 4. Realize 8x1 mux using 4x1 multiplexer.

- 5. Implement half adder using 2x1 multiplexer.

- 6.  $F(W, X, Y, Z) = \prod_{m} (0,1,3,5,7)$  using 8x1 multiplexer.

- 7. Write code for 1x4 Multiplexer using different coding methods.

- 1. Can a multiplexer be used to realize a logic function?

- 2. Differentiate between decoder and demultiplexer.

- 3. What are the applications of multiplexers?

- 4. Design an OR gate from 2:1 MUX.

- 5. Design a D and T flip flop using 2:1 multiplexer

- 6. Implement the function  $f(A,B,C) = \Sigma m(0,1,3,5,7)$  by using multiplexer

### DESIGN OF CODE CONVERTERS

### 4.1. OBJECTIVE

To Design and simulate the HDL code for the following combinational circuits

- a. 4 Bit binary to gray code converter

- b. 4 Bit gray to binary code converter

- c. Comparator

### 4.2. RESOURCES

PC installed with Xilinx tool

### 4.3. PROGRAM LOGIC

### Binary to gray code converter logic

This conversion method strongly follows the EX-OR gate operation between binary bits. The steps to perform binary to grey code conversion are given bellow.

- a. To convert binary to grey code, bring down the most significant digit of the given binary number, because, the first digit or most significant digit of the grey code number is same as the binary number.

- b. To obtain the successive grey coded bits to produce the equivalent grey coded number for the given binary, add the first bit or the most significant digit of binary to the second one and write down the result next to the first bit of grey code, add the second binary bit to third one and write down the result next to the second bit of grey code, follow this operation until the last binary bit and write down the results based on EX-OR logic to produce the equivalent grey coded binary.

### Gray to binary code converter logic

This conversion method also follows the EX-OR gate operation between grey & binary bits. The steps to perform grey code to binary conversion are given below.

a. To convert grey code to binary, bring down the most significant digit of the given grey code number, because, the first digit or the most significant digit of the grey code number is same as the binary number.

- b. To obtain the successive second binary bit, perform the EX-OR operation between the first bit or most significant digit of binary to the second bit of the given grey code.

- c. To obtain the successive third binary bit, perform the EX-OR operation between the second bit or most significant digit of binary to the third MSD (most significant digit) of grey code and so on for the next successive binary bits conversion to find the equivalent.

### 4.4. PROCEDURE

- 1. Create a module with required number of variables and mention it's input/output.

- 2. Write the description of the code converter using data flow model or gate level model.

- 3. Create another module referred as test bench to verify the functionality.

- 4. Follow the steps required to simulate the design and compare the obtained output with the required one.

### 4.5. CODE

```

// binary to gray code converter

module p7(b,g);

input [3:0] b;

output [3:0] g;

reg [3:0] g;

always@(b)

begin

g[3]=b[3];

g[2]=b[3]^b[2];

g[1]=b[2]^b[1];

g[0]=b[1]^b[0];

end

endmodule

//gray to binary converter

module p8(g,b);

input [3:0] g;

output [3:0] b;

reg [3:0] b;

always@(g)

begin

b[3]=g[3];

```

```

b[2]=b[3]^g[2];

b[1]=b[2]^g[1];

b[0]=b[1]^g[0];

end

endmodule

// 4 bit comparator

module p9(a,b,g,l,e);

input [3:0]a;

input [3:0]b;

output g,l,e;

reg g,l,e;

always@(a,b)

begin

if (a<b)

begin

e = 0; 1 = 1; g = 0;

end

else if (a==b)

begin

e = 1; 1 = 0; g = 0;

end

else

begin

e = 0; 1 = 0; g = 1;

end

end

endmodule

```

# **4.6. PRE LAB QUESTIONS**

- 1. What is a code converter? List some of the code converters.

- 2. What are the typical applications of gray code?

- 3. Distinguish between the weighted and non-weighted codes. Give examples.

- 4. Realize the Boolean expressions for binary to gray code conversion

- 5. Realize the Boolean expressions for gray to binary code conversion

# 4.7. LAB ASSIGNMENT

- 1. Design BCD to Excess-3 code converter.

- 2. Design a BCD to seven segment code converter.

- 3. Design octal to binary code converter.

- 1. What is the difference between blocking and nonblocking assignments?

- 2. What is the difference between casex and case statements?

- 3. What is this `timescale compiler directive?

- 4. What is sensitivity list?

### FULL ADDER AND FULL SUBTRACTOR DESIGN MODELING

### 5.1. OBJECTIVE

To write a HDL code to describe the functions of a full Adder and subtractor.

#### 5.2. RESOURCES

PC installed with Xilinx tool

### **5.3. PROGRAM LOGIC**

A full adder consists of 3 inputs and 2 outputs. Fig 7.1 shows truth table of full adder. Use "assign" keyword to represent design in dataflow style. The output signal expressions can be obtained from the truth table using K-maps.

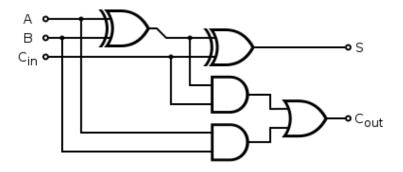

Figure 5.1 Logic diagram for 1-bit full adder

| Inputs |   |          | Outputs |           |

|--------|---|----------|---------|-----------|

| A      | В | $C_{in}$ | Sum     | $C_{out}$ |

| 0      | 0 | 0        | 0       | 0         |

| 0      | 0 | 1        | 1       | 0         |

| 0      | 1 | 0        | 1       | 0         |

| 0      | 1 | 1        | 0       | 1         |

| 1      | 0 | 0        | 1       | 0         |

| 1      | 0 | 1        | 0       | 1         |

| 1      | 1 | 0        | 0       | 1         |

| 1      | 1 | 1        | 1       | 1         |

Table 5.1 Truth table for 1-bit full adder

This is not practical to perform subtraction only between two single bit binary numbers. Instead binary numbers are always multibits. The subtraction of two binary numbers is performed bit by bit from right (LSB) to left (MSB). During subtraction of same significant bit of minuend and subtrahend, there may be one borrow bit along

with difference bit. This borrow bit (either 0 or 1) is to be added to the next higher significant bit of minuend and then next corresponding bit of subtrahend to be subtracted from this. It will continue up to MSB. The combinational logic circuit performs this operation is called full subtractor. Hence, full subs tractor is similar to half subs tractor but inputs in full subs tractor are three instead of two.

Two inputs are for the minuend and subtrahend bits and third input is for borrowed which comes from previous bits subtraction. The outputs of full adder are similar to that of half adder, these are difference (D) and borrow (b).

The combination of minuend bit (A), subtrahend bit (B) and input borrow (bi) and their respective differences (D) and output borrows (b) are represented in a truth table 5.2. The output signal expressions can be obtained from the truth table using K-maps.

| Inputs |   | Outputs       |            |            |

|--------|---|---------------|------------|------------|

| Α      | В | C (Borrow in) | Difference | Borrow out |

| 0      | 0 | 0             | 0          | 0          |

| 0      | 0 | 1             | 1          | 1          |

| 0      | 1 | 0             | 1          | 1          |

| 0      | 1 | 1             | 0          | 1          |

| 1      | 0 | 0             | 1          | 0          |

| 1      | 0 | 1             | 0          | 0          |

| 1      | 1 | 0             | 0          | 0          |

| 1      | 1 | 1             | 1          | 1          |

Table 5.1 Truth table for 1-bit subtractor adder

### **5.4. PROCEDURE**

- 1. Create a module with required number of variables and mention it's input/output.

- 2. Write the description of the full adder in 3 styles.

- 3. Create another module referred as test bench to verify the functionality.

- 4. Follow the steps required to simulate the design and compare the obtained output with the required one.

### 5.5. CODE

```

// full adder

module p10(a,b,c,sum,carry);

output sum,carry;

input a,b,c;

wire y0,y1,y2;

xor g1(y0,a,b);

and g2(y1,a,b);

```

```

xor g3(sum,y0,c); and g4(y2,y0,c); or g5(carry,y2,y1); endmodule

//full subtractor

module p11(a ,b ,c ,diff ,borrow ); output diff, borrow ; input a,b,c; assign diff = a ^b c; assign borrow = ((^a) & b) | (b & c) | (c & (^a)); endmodule

```

# **5.6. PRE LAB QUESTIONS**

- 1. What is a half adder?

- 2. Write the sum and carry expression for half adder.

- 3. What is a full adder?

- 4. Write the sum and carry expression for 1-bit full adder.

- 5. Write the difference and barrow out expressions for 1-bit subtractor

- 6. What is a parallel adder/subtractor?

### 5.7. LAB ASSIGNMENT

- 1. Design a 4-bit ripple carry adder using full adders.

- 2. Implement full adder using decoder.

- 3. Implement full subtractor using decoder.

- 4. Implement a 4-bit adder/subtractor.

- 5. Design a full adder using minimum number of NAND gates.

- 1. Realize a full adder using two half adders.

- 2. What is the amount of delay involved in ripple carry adder?

- 3. Compare serial adder and parallel adder with respect to speed and complexity.

- 4. Implement a single circuit which can perform both addition and subtraction operations on binary input bits.

### **DESIGN OF 8-BIT ARITHMETIC LOGIC UNIT**

#### 6.1. OBJECTIVE

To design a model to implement 8-bit ALU functionality

#### 6.2. RESOURCES

PC installed with Xilinx tool

### 6.3. PROGRAM LOGIC

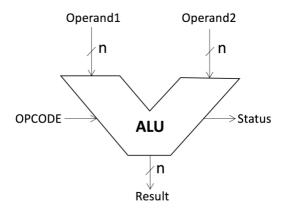

An arithmetic logic unit (ALU) is a combinational digital electronic circuit that performs arithmetic and bitwise operations on integer binary numbers. This is in contrast to a floating-point unit (FPU), which operates on floating point numbers. An ALU is a fundamental building block of many types of computing circuits, including the central processing unit (CPU) of computers, FPUs, and graphics processing units (GPUs). A single CPU, FPU or GPU may contain multiple ALUs.

Figure 6.1 Arithmetic logic unit block diagram

The inputs to an ALU are the data to be operated on, called operands, and a code (opcode) indicating the operation to be performed and, optionally, status information from a previous operation; the ALU's output is the result of the performed operation. In many designs, the ALU also exchanges additional information with a status register, which relates to the result of the current or previous operations

A number of basic arithmetic and bitwise logic functions are commonly supported by ALUs. Basic, general purpose ALUs typically includes these operations in their repertoires:

- Arithmetic operations

- Bitwise logical operations

- Bit shift operations

In this lab, students have to design an 8-bit ALU to implement the following operations:

Table 1: ALU Instructions

| Control | Instruction | Operation                       |

|---------|-------------|---------------------------------|

| 000     | Add         | Ouput<= A+B+Cin (Cout is carry) |

| 001     | Sub         | Output <= A-B-C (Cou is barrow) |

| 010     | Or          | Output <= A or B                |

| 011     | And         | Output <= A and B               |

| 100     | Shl         | Output <= A[7:0] & '0'          |

| 101     | Shr         | Output <= '0' & A[7:1]          |

| 110     | Rol         | Output <= A[2:0] & A[7]         |

| 111     | Ror         | Output <= A[0] & A[7:1]         |

Table 1 also illustrates the encoding of the control input

The 4 - bit ALU has the following inputs:

A: 8-bit inputB: 8-bit input

• Cin: 1-bit input

• Output: 8-bit output

• Cout: 1-bit output

• Control: 3-bit control input

The following points should be taken care of:

- Use a case statement (or a similar 'combinational' statement) that checks the input combination of "Code" and acts on A, B, and Cin as described in Table 1.

- The above circuit is completely combinational. The output should change as soon as the code combination or any of the input changes.

- You can use arithmetic and logical operators to realize your design.

### **6.4. PROCEDURE**

- 1. Create a module with required number of variables and mention it's input/output.

- 2. Write the description of the ALU by using case statements.

- 3. Create another module referred as test bench to verify the functionality.

4. Follow the steps required to simulate the design and compare the obtained output with the required one.

### **6.5. CODE**

```

//8 bit ALU

module p13(z,a,b,sel);

input [7:0]a,b;

input [3:0]sel;

output [7:0]z;

reg [7:0]z;

always@(sel,a,b)

begin

case(sel)

4'b0000: z=a+b;

4'b0001: z=a-b;

4'b0010: z=b-1;

4'b0011: z=a*b;

4'b0100: z=a&&b;

4'b0101: z=a||b|;

4'b0110: z=!a;

4'b0111: z=~a;

4'b1000: z=a&b:

4'b1001: z=a|b;

4'b1010: z=a^b;

4'b1011: z=a<<1;

4'b1100: z=a>>1;

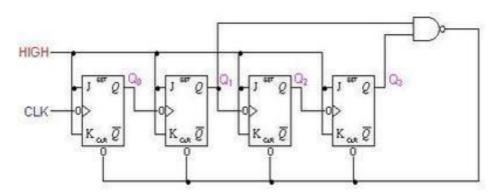

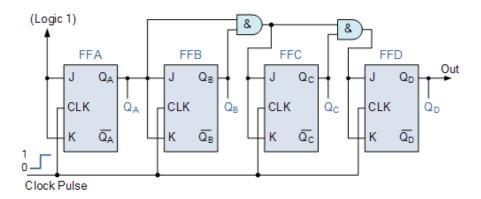

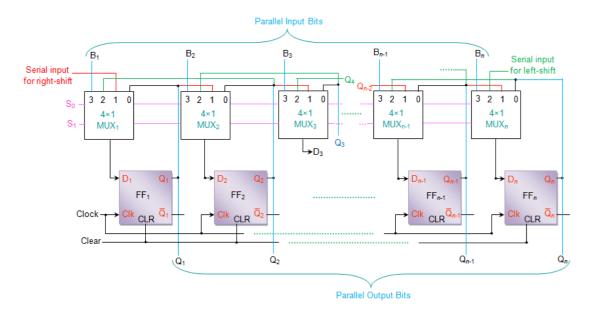

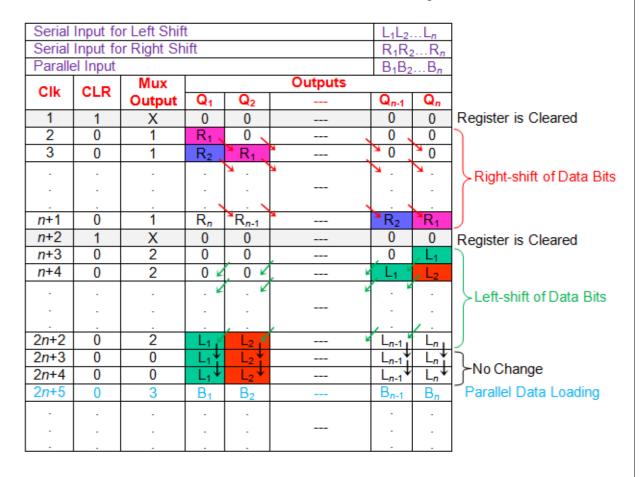

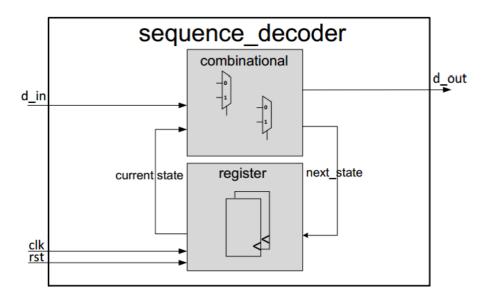

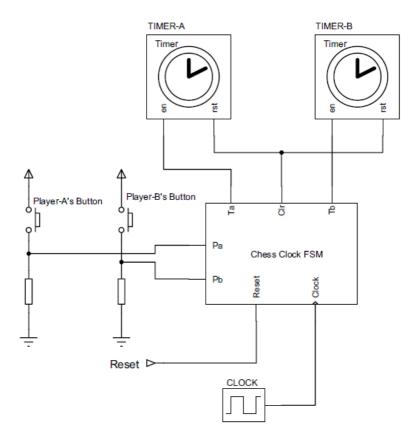

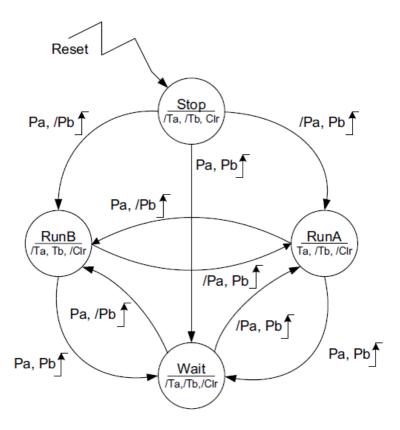

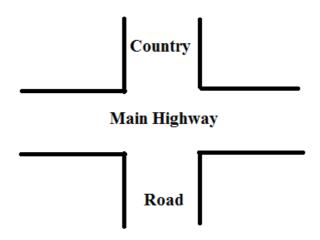

4'b1101: z=a+1;