## **LECTURE NOTES**

# ON

# DIGITAL AND PULSE CIRCUITS 2018-2019

**B.TECH IV Semester(IARE-R16)**

Dr.V.Vijay vallabhuni Mrs.V.Bindusree

### ELECTRICAL AND ELECTRONICS ENGINEERING

INSTITUTE OF AERONAUTICAL ENGINEERING (AUTONOMOUS) DUNDIGAL, HYDERABAD – 500043

### UNIT 1

### **BOOLEAN ALGEBRA AND SWITCHING FUNCTIONS**

- Philosophy of number systems

- Complement representation of negative numbers

- Binary arithmetic

- Binary codes

- Error detecting & error correcting codes Hamming codes\_

### HISTORY OF THE NUMERAL SYSTEMS:

A numeral system (or system of numeration) is a linguistic system and mathematical notation for representing numbers of a given set by symbols in a consistent manner. For example, It allows the numeral "11" to be interpreted as the binary numeral for *three*, the decimal numeral for *eleven*, or other numbers in different bases. Ideally, a numeral system will:

- Represent a useful set of numbers (e.g. all whole numbers, integers, or real numbers)

- Give every number represented a unique representation (or at least a standard representation) Reflect the algebraic and arithmetic structure of the numbers.

For example, the usual decimal representation of whole numbers gives every whole number a unique representation as a finite sequence of digits, with the operations of arithmetic (addition, subtraction, multiplication and division) being present as the standard algorithms of arithmetic. However, when decimal representation is used for the rational or real numbers, the representation is no longer unique: many rational numbers have two numerals, a standard one that terminates, such as 2.31, and another that recurs, such as 2.309999999... Numerals which terminate have no non-zero digits after a given position. For example, numerals like 2.31 and 2.310 are taken to be the same, except in the experimental sciences, where greater precision is denoted by the trailing zero.

The most commonly used system of numerals is known as Hindu-Arabic numerals.Great Indian mathematicians Aryabhatta of Kusumapura (5th Century) developed the place value notation.

Brahmagupta (6th Century) introduced the symbol zero.

### BINARY

The ancient Indian writer Pingala developed advanced mathematical concepts for describing prosody, and in doing so presented the first known description of a binary numeral system. A full set of 8 trigrams and 64 hexagrams, analogous to the 3-bit and 6-bit binary numerals, were known to the ancient Chinese in the classic text *I Ching*. An arrangement of the hexagrams of the *I Ching*, ordered according to the values of the corresponding binary numbers (from 0 to 63), and a method for

generating thesame, was developed by the Chinese scholar and philosopher Shao Yong in the 11th century

In 1854, British mathematician George Boole published a landmark paper detailing an algebraic system of logic that would become known as Boolean algebra. His logical calculus was to become instrumental in the design of digital electronic circuitry. In 1937, Claude Shannon produced his master's thesis at MIT that implemented Boolean algebra and binary arithmetic using electronic relays and switches for the first time in history. Entitled *A SymbolicAnalysis of Relay and Switching Circuits*, Shannon's thesis essentially founded practical digital circuit design.

Binary codes

Binary codes are codes which are represented in binary system with modification from the original ones.

- Weighted Binary codes

- Non Weighted Codes

Weighted binary codes are those which obey the positional weighting principles, each position of the number represents a specific weight. The binary counting sequence is an example.

| Decimal | BCD<br>8421 | Excess-3 | 84-2-1 | 2421 | 5211 | Bi-Quinary<br>5043210 | 434 | <b>8</b> 2 6 | 5 | 0 | 4 | 3 | 2 | 1 | 0 |

|---------|-------------|----------|--------|------|------|-----------------------|-----|--------------|---|---|---|---|---|---|---|

| 0       | 0000        | 0011     | 0000   | 0000 | 0000 | 0100001               |     | 0            |   | Х |   |   |   |   | Х |

| 1       | 0001        | 0100     | 0111   | 0001 | 0001 | 0100010               |     | 1            |   | Х |   |   |   | Х |   |

| 2       | 0010        | 0101     | 0110   | 0010 | 0011 | 0100100               |     | 2            |   | Х |   |   | х |   |   |

| 3       | 0011        | 0110     | 0101   | 0011 | 0101 | 0101000               |     | 3            |   | Х |   | Х |   |   |   |

| 4       | 0100        | 0111     | 0100   | 0100 | 0111 | 0110000               |     | 4            | - | Х | Х |   |   |   |   |

| 5       | 0101        | 1000     | 1011   | 1011 | 1000 | 1000001               |     | 5            | Х |   |   |   |   |   | Х |

| 6       | 0110        | 1001     | 1010   | 1100 | 1010 | 1000010               |     | 6            | Х |   |   |   |   | х |   |

| 7       | 0111        | 1010     | 1001   | 1101 | 1100 | 1000100               |     | 7            | Х |   |   |   | Х |   |   |

| 8       | 1000        | 1011     | 1000   | 1110 | 1110 | 1001000               |     | 8            | Х |   |   | Х |   |   | 4 |

| 9       | 1001        | 1111     | 1111   | 1111 | 1111 | 1010000               |     | 9            | Х |   | Х |   |   |   |   |

### Reflective Code

A code is said to be reflective when code for 9 is complement for the code for 0, and so is for 8 and 1 codes, 7 and 2, 6 and 3, 5 and 4. Codes 2421, 5211, and excess-3 are reflective, whereas the 8421 code is not.

### Sequential Codes

A code is said to be sequential when two subsequent codes, seen as numbers in binary

representation, differ by one. This greatly aids mathematical manipulation of data. The 8421 and Excess-3 codes are sequential, whereas the 2421 and 5211 codes are not.

Non weighted codes

Non weighted codes are codes that are not positionally weighted. That is, each position within the binary number is not assigned a fixed value. Ex: Excess-3 code

### Excess-3 Code

Excess-3 is a non weighted code used to express decimal numbers. The code derives its name from the fact that each binary code is the corresponding 8421 code plus 0011(3).

### Gray Code

The gray code belongs to a class of codes called minimum change codes, in which only one bit in the code changes when moving from one code to the next. The Gray code is non-weighted code, as the position of bit does not contain any weight. The gray code is a reflective digital code which has the special property that any two subsequent numbers codes differ by only one bit. This is also called a unitdistance code. In digital Gray code has got a special place.

| Decimal<br>Number | Binary<br>Code | Gray Code | Decimal<br>Number | Binary<br>Code | Gray Code |

|-------------------|----------------|-----------|-------------------|----------------|-----------|

| 0                 | 0000           | 0000      | 8                 | 1000           | 1100      |

| 1                 | 0001           | 0001      | 9                 | 1001           | 1101      |

| 2                 | 0010           | 0011      | 10                | 1010           | 1111      |

| 3                 | 0011           | 0010      | 11                | 1011           | 1110      |

| 4                 | 0100           | 0110      | 12                | 1100           | 1010      |

| 5                 | 0101           | 0111      | 13                | 1101           | 1011      |

| 6                 | 0110           | 0101      | 14                | 1110           | 1001      |

| 7                 | 0111           | 0100      | 15                | 1111           | 1000      |

Binary to Gray Conversion

- Gray Code MSB is binary code MSB.

- Gray Code MSB-1 is the XOR of binary code MSB and MSB-1.

- MSB-2 bit of gray code is XOR of MSB-1 and MSB-2 bit of binary code.

- MSB-N bit of gray code is XOR of MSB-N-1 and MSB-N bit of binary code.Error detection codes

### 1)Parity bits

A parity bit is a bit that is added to a group of source bits to ensure that the number of set bits (i.e., bits with value

1) in the outcome is even or odd. It is a very simple scheme that can be used to detect single or any other odd number (i.e., three, five, etc.) of errors in the output. An even number of flipped bits will make the parity bit appear correct even though the data is erroneous.

### 2)Checksums

A checksum of a message is a modular arithmetic sum of message code words of a fixed word length (e.g.,byte values). The sum may be negated by means of a one's-complement prior to transmission to detect errorsresulting in all-zero messages. Checksum schemes include parity bits, check digits, and longitudinal redundancy checks. Some checksum schemes, such as the Luhn algorithm and the Verhoeff algorithm, are specifically designed to detect errorscommonly introduced by humans in writing down or remembering identification numbers.

2. Cyclic redundancy checks (CRCs)

A cyclic redundancy check (CRC) is a single-burst-error-detecting cyclic code and non-secure hash function designed to detect accidental changes to digital data in computer networks. It is characterized by specification of a so-called *generator polynomial*, which is used as the divisor in a polynomial long division over a finite field, taking the input data as the dividend, and where the remainder becomes the result.Cyclic codes have favorable properties in that they are well suited for detecting burst errors. CRCs are particularly easy to implement in hardware, and are therefore commonly used in digital networks and storage devices such as hard disk drives.Even parity is a special case of a cyclic redundancy check, where the single-bit CRC is generated by the divisor x+1.

### NUMBER BASE CONVERSIONS

Any number in one base system can be converted into another base system Types

- 1) decimal to any base

- 2) Any base to decimal

- 3) Any base to Any base

### Decimal number: $123.45 = 110^{2} + 210^{1} + 310^{0} + 410^{-1} + 510^{-2}$ .

Base *b* number:  $N = a_{q-1}b^{q-1} + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ... + ..$

Binary number (b=2):  $1101.01 = 12^3 + 12^2 + 02^1 + 12^0 + 02^1 + 12^2$

Representing number N in base b: (N)<sub>b</sub> • • • • •

Complement of digit a: a' = (b-1)-a Decimal system: 9's complement of 3 = 9-3 = 6 Binary system: 1's complement of 1 = 1-1 = 0

Fractional number:

$$(N)_{b_1} = a_{-1}b_2^{-1} + a_{-2}b_2^{-2} + \dots + a_{-p}b_2^{-p}$$

$$b_2 \cdot (N)_{b_1} = a_{-1} + a_{-2}b_2^{-1} + \dots + a_{-p}b_2^{-p+1}$$

Example: Convert (0.3125)<sub>10</sub> to base 8

0.3125 8 = 2.5000 hence a<sub>-1</sub> = 2 0.5000 8 = 4.0000 hence a<sub>-2</sub> = 4

Thus,  $(0.3125)_{10} = (0.24)_8$

Decimal to Binary

### Example: Convert (432.354)<sub>10</sub> to binary

| $O_i$ | T;                         |                 |                    |

|-------|----------------------------|-----------------|--------------------|

| 216   | $0 = a_0$                  | 0.354 2 = 0.708 | hence $a_1 = 0$    |

| 108   | $0 = a_1$                  | 0.708 2 = 1.416 |                    |

| 54    | $0 = a_2$                  | 0.416 2 = 0.832 | 900 K              |

| 27    | $0 = a_3$                  | 0.832 2 = 1.664 | hence $a_4 = 1$    |

| 13    | $1 = a_4$                  | 0.664 2 = 1.328 | hence $a_5 = 1$    |

| 6     | $1 = a_5$                  | 0.328 2 = 0.656 | hence $a_{-6} = 0$ |

| 3     | $0 = a_6$                  |                 | a_7=1              |

| 1     | $1 - a_{5}$                |                 | etc.               |

|       | $1 = a_{1}$<br>$1 = a_{8}$ |                 |                    |

Thus,  $(432.354)_{10} = (110110000.0101101...)_2$

Octal To Binary

Example: Convert  $(123.4)_8$  to binary  $(123.4)_8 = (001\ 010\ 011.100)_2$

## Example: Convert $(1010110.0101)_2$ to octal $(1010110.0101)_2 = (001\ 010\ 110.010\ 100)_2 = (126.24)_8$

Error Detection and Correction Codes

- · No communication channel or storage device is completely error-free

- As the number of bits per area or the transmission rate increases, more errors occur.

Impossible to detect or correct 100% of the errors

Hamming Codes

- 1. One of the most effective codes for error-recovery

- 2. Used in situations where random errors are likely tooccur

Error detection and correction increases in proportion to the number of parity bits (error- checking bits) added to the end of the

informationbits

code word = information bits + parity bits

Hamming distance: the number of bit positions in which two code words differ.

10001001

10110001

\* \* \*

Minimum Hamming distance or D(min) : determines its error detecting and correcting capability.

| 1.Hamming codes can always detect D(min) – 1 errors, but can only correct half of those errors. |

|-------------------------------------------------------------------------------------------------|

|                                                                                                 |

| EX. | Data        | Parity | Code |      |      |

|-----|-------------|--------|------|------|------|

|     | <u>Bits</u> | Bit    | Word |      |      |

|     | 00          | 0      | 000  |      |      |

|     | 01          | 1      | 011  |      |      |

|     | 10          | 1      | 101  |      |      |

|     | 11          | 0      | 110  |      |      |

|     |             |        |      | 000* | 100  |

|     |             |        |      | 001  | 101* |

|     |             | 13     |      | 010  | 110* |

|     |             |        |      | 011* | 111  |

1. Single parity bit can only detect error, not correct it

2. Error-correcting codes require more than a single parity bit EX. 00000

01011

$1 \ 0 \ 1 \ 1 \ 0$

11101

Minimum Hamming distance = 3

Can detect up to 2 errors and correct 1 error Cyclic Redundancy Check

- 1. Let the information byte F = 1001011

- 2. The sender and receiver agree on an arbitrary binary pattern P. Let P = 1011.

- 3. Shift F to the left by 1 less than the number of bits in P. Now, F = 1001011000.

- 4. Let F be the dividend and P be the divisor. Perform -modulo 2 divisionl.

5. After performing the division, we ignore the quotient. We got 100 for the remainder, which becomes the actual CRC checksum.

5.Add the remainder to F, giving the message M: 1001011 + 100 = 1001011100 = M

M is decoded and checked by the message receiver using the reverse process.

| der |

|-----|

|     |

### UNIT-II

### MINIMIZATION TECHNIQUES AND DESIGN OF MSI

- · Fundamental postulates of Boolean algebra

- · Basic theorems and properties

- Switching functions

- Canonical and Standard forms

- · Algebraic simplification digital logic gates, properties of XOR gates

- Universal gates

- Multilevel NAND/NOR realizations

Boolean Algebra: Boolean algebra, like any other deductive mathematical system, may be defined with aset of elements, a set of operators, and a number of unproved axioms or postulates. A *set* of elements is anycollection of objects having a common property. If S is a set and x and y are certain objects, then x Î Sdenotes that x is a member of the set S, and y ÏS denotes that y is not an element of S. A set with adenumerable number of elements is specified by braces:  $A = \{1,2,3,4\}$ , *i.e.* the elements of set A are thenumbers 1, 2, 3, and 4. A *binary operator* defined on a set S of elements is a rule that assigns to each pair of elements from S a unique element from S.\_ Example: In a\*b=c, we say that \* is a binary operator if it specifies a rule for finding c from the pair (a,b) and also if a, b, c Î S.

CLOSURE: The Boolean system is *closed* with respect to a binary operator if for every pair of Boolean values, it produces a Boolean result. For example, logical AND is closed in the Boolean system because it accepts only Boolean operands and produces only Boolean results.

\_ A set S is closed with respect to a binary operator if, for every pair of elements of S, the binary operator specifies a rule for obtaining a unique element of S.

\_ For example, the set of natural numbers N = {1, 2, 3, 4, ... 9} is closed with respect to the binary operator plus (+) by the rule of arithmetic addition, since for any a, b Î N we obtain a unique c Î N by the operation a + b = c.

### ASSOCIATIVE LAW:

A binary operator \* on a set *S* is said to be associative whenever (x \* y) \* z = x \* (y \* z) for all *x*, *y*, *z* Î S, for all Boolean values x, y and z.

COMMUTATIVE LAW: A binary operator \* on a set S is said to be commutative whenever x \* y = y \* x for all x, y, z  $\in$  S

IDENTITY ELEMENT: A set *S* is said to have an identity element with respect to a binary operation \* on S if there exists an element  $e \in S$  with the property e \* x = x \* e = x for every  $x \in S$

### BASIC IDENTITIES OF BOOLEAN ALGEBRA

• Postulate 1(Definition): A Boolean algebra is a closed algebraic system containing a set *K* of two or more elements and the two operators  $\cdot$  and + which refer to logical AND and logical OR  $\bullet x + 0 = x$

- $x \cdot 0 = 0$

- x + 1 = 1

- $x \cdot l = l$

- x + x = x

- $x \cdot x = x$

- x + x' = x

- $x \cdot x' = 0$

- x + y = y + x

- xy = yx

- x + (y + z) = (x + y) + z

- x(yz) = (xy) z

- x(y+z) = xy + xz

- x + yz = (x + y)(x + z)

- (x+y)' = x'y'

- (xy)' = x' + y'

- (x')' = x

### DeMorgan's Theorem

(a) (a + b)' = a'b'(b) (ab)' = a' + b'

Generalized DeMorgan's Theorem (a) (a + b + ... z)' = a'b' ... z' (b) (a.b)

$(... z)' = a' + b' + ... z_{-}$

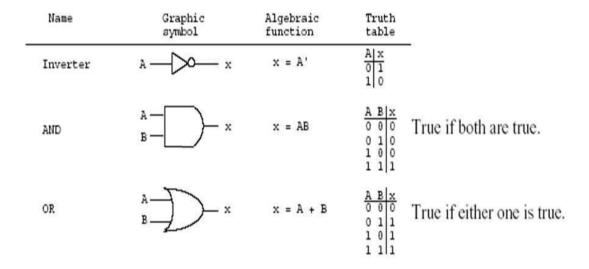

### LOGIC GATES

Formal logic: In formal logic, a statement (proposition) is a declarative sentence that is either true(1) or false (0). It is easier to communicate with computers using formal logic.

- Boolean variable: Takes only two values either true (1) or false (0). They are used as basic units of formal logic.

- Boolean algebra: Deals with binary variables and logic operations operating on those variables.

• Logic diagram: Composed of graphic symbols for logic gates. A simple circuit sketch that represents inputs and outputs of Boolean functions

| <ul> <li>Other commor<br/>Name</li> </ul> | n gates include:<br>Graphic<br>symbol | Algebraic<br>function                                                                                                            | Truth<br>table                                   |                                         |

|-------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------|

| Exclusive-OR<br>(XOR)                     |                                       | $ \begin{array}{l} \mathbf{x} \ = \ \mathbf{A} \oplus \ \mathbf{B} \\ = \ \mathbf{A}'\mathbf{B} \ + \ \mathbf{AB'} \end{array} $ | <u>A B x</u><br>0 0 0<br>0 1 1<br>1 0 1<br>1 1 0 | Parity check: True if only one is true. |

| NAND                                      | А-<br>ВО- х                           | x = (AB)'                                                                                                                        | <u>A B x</u><br>0 0 1<br>0 1 1<br>1 0 1<br>1 1 0 | Inversion of AND.                       |

| NOR                                       |                                       | x = A + B                                                                                                                        | A B x<br>0 0 1<br>0 1 0<br>1 0 0<br>1 1 0        | Inversion of OR.                        |

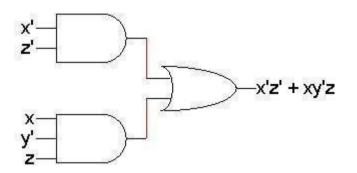

Minimization of switching functions is to obtain logic circuits with least circuit complexity. This goal is very difficult since how a minimal function relates to the implementation technology is important. For example, If we are building a logic circuit that uses discrete logic made of small scale Integration ICs(SSIs) like 7400 series, in which basic building block are constructed and are available for use. The goal of minimization would be to reduce the number of ICs and not the logic gates. For example, If we require two 6 and gates and 5 Or gates, we would require 2 AND ICs(each has 4 AND gates) and one OR IC. (4 gates). On the other hand if the same logic could be implemented with only 10 nand gates, we require only 3 ICs. Similarly when we design logic on Programmable device, we may implement the design with certain number of gates and remaining gates may not be used.

Whatever may be the criteria of minimization we would be guided by the following:

- · Boolean algebra helps us simplify expressions and circuits

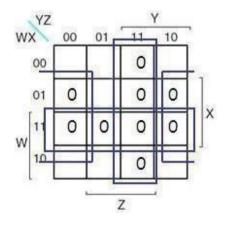

- Karnaugh Map: A graphical technique for simplifying a Boolean expression into eitherform:

- minimal sum of products (MSP)

- o minimal product of sums (MPS)

- Goal of thesimplification.

- There are a minimal number of product/sum terms oEach term has a minimal number of literals

- Circuit-wise, this leads to a minimal two-levelimplementation

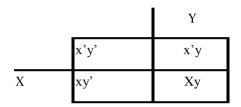

A Two-Variable Karnaugh Map

• A two-variable function has four possible minterms. We can re-arrange these minterms into a Karnaugh map

| x y minterm |  |

|-------------|--|

|-------------|--|

| X<br>0 | Y<br>0 | xʻyʻ |

|--------|--------|------|

| 0      | 1      | xʻy  |

| 1      | 0      | xyʻ  |

| 1      | 1      | xy   |

| xʻyʻ | x'y |

|------|-----|

| xyʻ  | xy  |

0

1

Now we can easily see which minterms contain common literals

- Minterms on the left and right sides contain y' and y respectively

- Minterms in the top and bottom rows contain x' and xrespectively XY

Simplification

- Imagine a two-variable sum of minterms x'y' + x'y

- Both of these minterms appear in the top row of a Karnaugh map, which means that they both contain the literal x'

- What happens if you simplify this expression using Boolean algebra?

- x'y' + x'y = x'(y' + y) [Distributive]

- For a three-variable expression with inputs x, y, z, the arrangement of minterms is more tricky:

|     | ΥZ |        |       |      | YZ    |     |                               |                |                |                |

|-----|----|--------|-------|------|-------|-----|-------------------------------|----------------|----------------|----------------|

|     |    | 00     | 01    | 11   | 10    |     | 00                            | 01             | 11             | 10             |

| _ O | 0  | ×'y'z' | ×′y′z | хʻуz | ×'yz' | ~ 0 | m <sub>0</sub>                | m <sub>1</sub> | m <sub>3</sub> | m <sub>2</sub> |

| Х   | 1  | ×y′z′  | ×y′z  | ×yz  | ×yz'  | ^ 1 | m <sub>0</sub> m <sub>4</sub> | m <sub>5</sub> | m7             | m <sub>6</sub> |

Another way to label the K-map (use whichever you like):

|   |       |      |      | Y     |   |                |    | [ ] | Y              |

|---|-------|------|------|-------|---|----------------|----|-----|----------------|

|   | ×ý′z′ | בy'z | х′уz | ×'yz' |   | m <sub>0</sub> | m1 | m3  | m <sub>2</sub> |

| Х | ×y′z′ | ×y′z | xyz  | ×yz'  | X | m4             | m5 | m7  | m <sub>6</sub> |

|   |       | Z    | Z    | C     |   |                | 2  | Ζ   |                |

• With this ordering, any group of 2, 4 or 8 adjacent squares on the map contains common literals that can be factored out

|   |       |      |     | Y     |   | x'y'z + x'yz |

|---|-------|------|-----|-------|---|--------------|

|   | בy'z' | ×ý⁄z | XÝZ | ×'yz' | = | x'z(y'+y)    |

| X | ×y′z′ | ×y′z | xyz | ×yz′  |   | x'z•1        |

|   |       | Z    | 2   |       | Ξ | x'z          |

• "Adjacency" includes wrapping around the left and right sides:

|    |       |      | Î i  | Y     | x'y'z' + xy'z' + x'yz' + xyz' |

|----|-------|------|------|-------|-------------------------------|

|    | בy'z' | ×ý′z | ху́z | ×'yz' | = z'(x'y' + xy' + x'y + xy)   |

| ×. | ×y′z′ | xy'z | xyz  | ×yz′  | = z'(y'(x'+x) + y(x'+x))      |

|    |       | Z    | Z    | a.    | = z(y+y)<br>= z'              |

- We'll use this property of adjacent squares to do our simplifications.

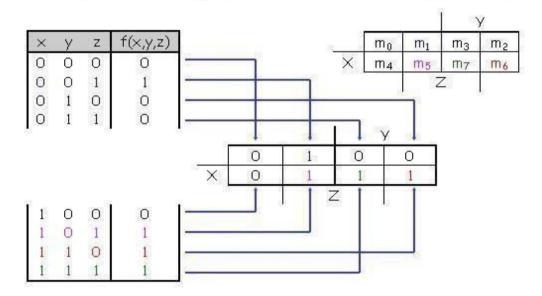

- We can fill in the K-map directly from a truth table

- The output in row i of the table goes into square m, of the K-map

- Remember that the rightmost columns of the K-map are "switched"

K-maps From Truth Tables

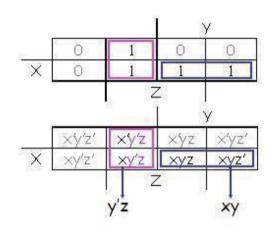

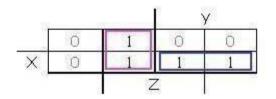

Reading the MSP from the K-map

- You can find the minimal SoP expression

- Each rectangle corresponds to one product term

- The product is determined by finding the common literals in that rectangle

F(x,y,z)=y'z+xy

- The most difficult step is grouping together all the 1s in the K-map

- Make rectangles around groups of one, two, four or eight 1s

- All of the 1s in the map should be included in at least one rectangle

- Do not include any of the Os

- Each group corresponds to one product term

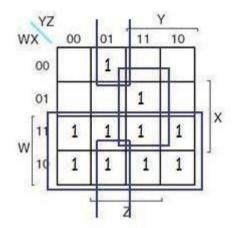

Simplify  $m_0 + m_2 + m_5 + m_8 + m_{10} + m_{13}$

K-map Simplification of SoP Expressions

- Let's consider simplifying f(x, y, z) = xy + y'z + xz

- · You should convert the expression into a sum of minterms form,

- The easiest way to do this is to make a truth table for the function, and then read off the minterms

- You can either write out the literals or use the minterm shorthand

- Here is the truth table and sum of minterms for our example:

| $\times$                                | у | Z | f(x,y,z) |

|-----------------------------------------|---|---|----------|

| 0                                       | 0 | 0 | Ö        |

| 000000000000000000000000000000000000000 | 0 | 1 | 1        |

| 0                                       | 1 | 0 | 0        |

| 0                                       | 1 | 1 | 0        |

| 1                                       | 0 | 0 | 0        |

| 1                                       | 0 | 1 | 1        |

| 1                                       | 1 | 0 | 1        |

| 1                                       | 1 | 1 | 1        |

$$f(x,y,z) = x'y'z + xy'z + xyz' + xyz' = m_1 + m_5 + m_6 + m_7$$

- You can also convert the expression to a sum of <u>minterms</u> with Boolean algebra

- Apply the distributive law in reverse to add in missing variables.

- Very few people actually do this, but it's occasionally useful.

$$xy + y'z + xz = (xy \cdot 1) + (y'z \cdot 1) + (xz \cdot 1)$$

= (xy \cdot (z' + z)) + (y'z \cdot (x' + x)) + (xz \cdot (y' + y))

= (xyz' + xyz) + (x'y'z + xy'z) + (xy'z + xyz)

= xyz' + xyz + x'y'z + xy'z

= m\_1 + m\_5 + m\_6 + m\_7

- In both cases, we're actually "unsimplifying" our example expression

- The resulting expression is larger than the original one!

- But having all the individual minterms makes it easy to combine them together with the K-map

Simplify  $m_0 + m_2 + m_5 + m_8 + m_{10} + m_{13}$

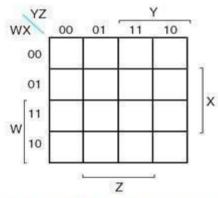

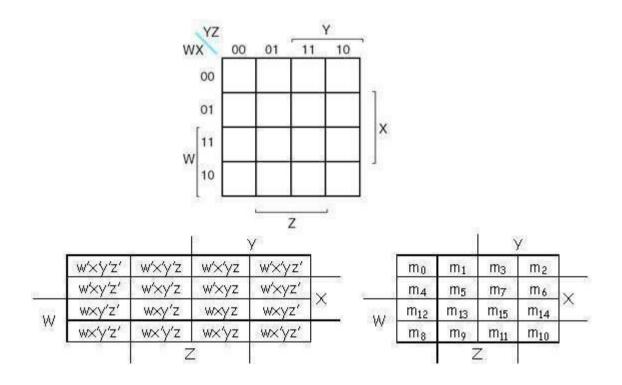

- We can do four-variable expressions too!

- The minterms in the third and fourth columns, *and* in the third and fourth rows, are switched around.

- Again, this ensures that adjacent squares have common literals

- Grouping minterms is similar to the three-variable case, but:

- You can have rectangular groups of 1, 2, 4, 8 or 16 minterms

- You can wrap around all foursides

Simplify  $m_0 + m_2 + m_5 + m_8 + m_{10} + m_{13}$

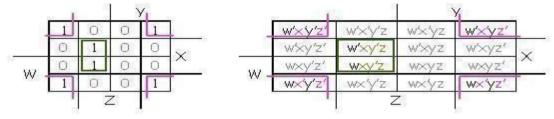

• The expression is already a sum of minterms, so here's the K-map:

|   | 1 | 0 | 0 | 1 |      | m <sub>0</sub>  | m <sub>1</sub>  | m <sub>3</sub>  | m <sub>2</sub>  |        |

|---|---|---|---|---|------|-----------------|-----------------|-----------------|-----------------|--------|

|   | 0 | 1 | 0 | 0 |      | $m_4$           | m <sub>5</sub>  | m <sub>7</sub>  | m <sub>6</sub>  |        |

| I | 0 | 1 | 0 | 0 | 3.00 | m <sub>12</sub> | m <sub>13</sub> | m <sub>15</sub> | m <sub>14</sub> | $]^{}$ |

| 1 |   | 0 | 0 | 1 | W    | m <sub>8</sub>  | m9              | m11             | m <sub>10</sub> |        |

• We can make the following groups, resulting in the MSP x'z' + xy'z

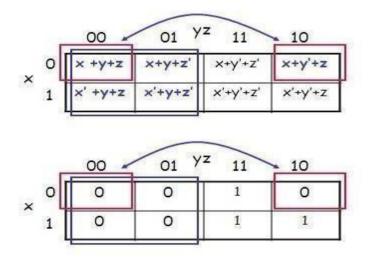

**PoS Optimization**

Maxterms are grouped to find minimal PoS expression

|     |         | >       | /Z       |         |

|-----|---------|---------|----------|---------|

|     | 00      | 01      | 11       | 10      |

| 0   | x +y+z  | x+y+z'  | x+y'+z'  | х+у'+z  |

| × 1 | x' +y+z | x'+y+z' | x'+y'+z' | x'+y'+z |

F(W,X,Y,Z)= ∏ M(0,1,2,4,5)

F(W,X,Y,Z)=Y.(X+Z)

SoP Optimization from PoS

$$F(W,X,Y,Z) = \prod M(0,2,3,4,5,6)$$

=  $\Sigma m(1,7,8,9,10,11,12,13,14,15)$

F(W,X,Y,Z) = W + XYZ + X'Y'Z

PoS Optimization from SoP

$F(W,X,Y,Z) = \Sigma m(0,1,2,5,8,9,10)$ =  $\Pi M(3,4,6,7,11,12,13,14,15)$

F(W,X,Y,Z)=(W' + X')(Y' + Z')(X' + Z)Or, F(W,X,Y,Z)=X'Y' + X'Z' + W'Y'ZWhich one is the minimal one? Don't care

- You don't always need all 2<sup>n</sup> input combinations in an n-variable function

- If you can guarantee that certain input combinations never occur

- If some outputs aren't used in the rest of the circuit

- We mark don't-care outputs in truth tables and K-maps with Xs.

| $\times$ | У      | z | f(x,y,z) |

|----------|--------|---|----------|

| 0        | 0      | 0 | 0        |

| 0        | 0<br>0 | 1 | 1        |

| 0        | 1      | 0 | ×        |

| 0        | 1      | 1 | 0        |

| 1        | 0      | О | 0        |

| 1        | 0<br>0 | 1 | 1        |

| 1        | 1      | 0 | ×        |

| 1        | 1      | 1 | 1        |

- Within a K-map, each X can be considered as either 0 or 1. You should pick the interpretation that allows for the most simplification.

- Find a MSP for

$f(w,x,y,z) = \Sigma m(0,2,4,5,8,14,15), d(w,x,y,z) = \Sigma m(7,10,13)$

This notation means that input combinations wxyz = 0111, 1010 and 1101 (corresponding to minterms  $m_7$ ,  $m_{10}$  and  $m_{13}$ ) are unused.

| 8 |   | 0 | 0 | y<br>  . | ì |

|---|---|---|---|----------|---|

| 3 | 1 | 0 | 0 | 1        |   |

| 0 | 1 | 1 | × | 0        | V |

| w | 0 | × | 1 | 1        | ^ |

|   | 1 | 0 | 0 | ×        |   |

### K-map Summary

K-maps are an alternative to algebra for simplifying expressions

The result is a MSP/MPS, which leads to a minimal two-level circuit

It's easy to handle don't-care conditions

K-maps are really only good for manual simplification of small expressions...

Things to keep in mind:

Remember the correct order of minterms/maxterms on the K-map

When grouping, you can wrap around all sides of the K-map, and your groups can overlap

Make as few rectangles as possible, but make each of them as large as possible. This leads to fewer, but simpler, product terms

There may be more than one valid solution

### **UNIT-III**

### SEQUENTIAL CIRCUITS DESIGN

**Combinational Logic**

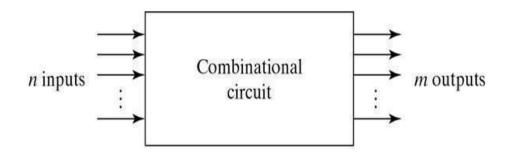

- Logic circuits for digital systems may be combinational or sequential.

- A combinational circuit consists of input variables, logic gates, and output variables.

For n input variables, there are 2<sup>n</sup> possible combinations of binary input variables .For each possible input Combination , there is one and only one possible output combination. A combinational circuit can be described by m Boolean functions one for each output variables. Usually the input s comes from flip-flops and outputs goto flip-flops.

**Design Procedure:**

1. The problem is stated

2. The number of available input variables and required output variables is determined.

3. 3. The input and output variables are assigned letter symbols.

4. The truth table that defines the required relationship between inputs and outputs is derived.

5. The simplified Boolean function for each output is obtained.

6. The logic diagram is drawn.

Adders:

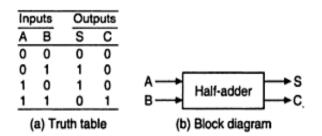

Digital computers perform variety of information processing tasks, the one is arithmetic operations. And the most basic arithmetic operation is the addition of two binary digits.i.e, 4 basic possible operations are:

0+0=0,0+1=1,1+0=1,1+1=10

The first three operations produce a sum whose length is one digit, but when augends and addend bits are equal to 1, the binary sum consists of two digits. The higher significant bit of this result is called a carry. A combinational circuit that performs the addition of two bits is called a half- adder. One that performs the addition of 3 bits (two significant bits & previous carry) is called a full adder.& 2 half adder can employ as a full-adder.

The Half Adder: A Half Adder is a combinational circuit with two binary inputs (augends and addend bits and two binary outputs (sum and carry bits.) It adds the two inputs (A and B) and produces the sum

(S) and the carry (C) bits. It is an arithmetic operation of addition of two single bit words.

The Sum(S) bit and the carry (C) bit, according to the rules of binary addition, the sum (S) is the X-OR of A and B (It represents the LSB of the sum). Therefore,

### S=A+ **A ⊕ B**

The carry (C) is the AND of A and B (it is 0 unless both the inputs are 1). Therefore, C=AB A half-adder can

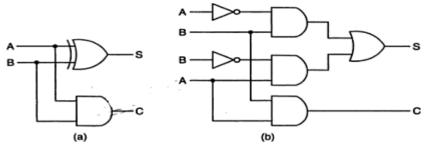

be realized by using one X-OR gate and one AND gate a

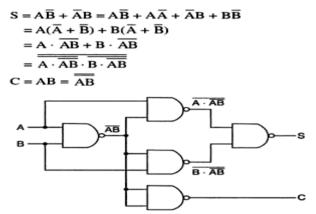

Logic diagrams of half-adder

NAND LOGIC:

Logic diagram of a half-adder using only 2-input NAND gates.

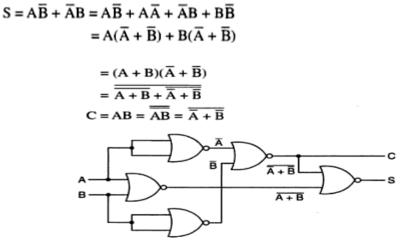

NOR Logic:

Logic diagram of a half-adder using only 2-input NOR gates.

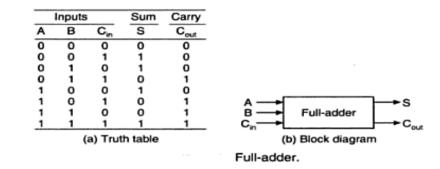

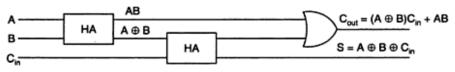

The Full Adder:

A Full-adder is a combinational circuit that adds two bits and a carry and outputs a sum bit and a carry bit. To add two binary numbers, each having two or more bits, the LSBs can be added by using a half-adder.

The carry resulted from the addition of the LSBs is carried over to the next significant column and added to the two bits in that column. So, in the second and higher columns, the two data bits of that column and the carry bit generated from the addition in the previous column need to be added.

The full-adder adds the bits A and B and the carry from the previous column called the carry-in Cin and outputs the sum bit S and the carry bit called the carry-out  $C_{out}$ . The variable S gives the value of the least significant bit of the sum. The variable  $C_{out}$  gives the output carry.The

eight rows under the input variables designate all possible combinations of 1s and 0s that these variables may have. The 1s and 0s for the output variables are determined from the arithmetic sum of the input bits. When all the bits are 0s, the output is 0. The S output is equal to 1 when only 1 input is equal to 1 or when all the inputs are equal to 1. The  $C_{out}$  has a carry of 1 if two

or three inputs are equal to 1.

From the truth table, a circuit that will produce the correct sum and carry bits in response to every possible combination of A,B and  $C_{in}$  is described by

$S \square ABCin \square ABCin \square ABCin \square ABCin \square ABCin Cout \square ABCin \square ABCin \square ABCin \square ABCin$

and

$S \square A \square B \square Cin$  $Cout \square ACin \square BCin \square AB$

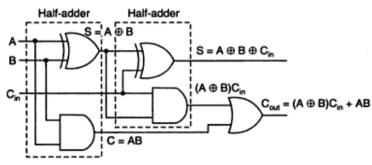

The sum term of the full-adder is the X-OR of A,B, and  $C_{in}$ , i.e, the sum bit the modulo sum of the data bits in that column and the carry from the previous column. The logic diagram of the full-adder using two X-OR gates and two AND gates (i.e, Two half adders) and one OR gate is

Logic diagram of a full-adder using two half-adders.

The block diagram of a full-adder using two half-adders is

Block diagram of a full-adder using two half-adders.

Even though a full-adder can be constructed using two half-adders, the disadvantage is that the bits must propagate through several gates in accession, which makes the total propagation delay greater than that of the full-adder circuit using AOI logic.

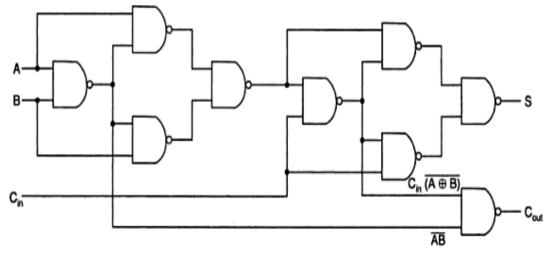

The Full-adder neither can also be realized using universal logic, i.e., either only NAND gates or only NOR gates as

$$A \oplus B = \overline{\overline{A \cdot \overline{AB}} \cdot \overline{B \cdot \overline{AB}}}$$

Then

$$S = A \oplus B \oplus C_{in} = \overline{(\overline{A \oplus B}) \cdot (\overline{A \oplus B})C_{in}} \cdot \overline{C_{in} \cdot (\overline{A \oplus B})C_{in}}$$

NAND Logic:

$C_{out} = C_{in}(A \oplus B) + AB = \overline{C_{in}(A \oplus B)} \cdot \overline{AB}$

Sum and carry bits of a full-adder using AOI logic.

Logic diagram of a full-adder using only 2-input NAND gates.

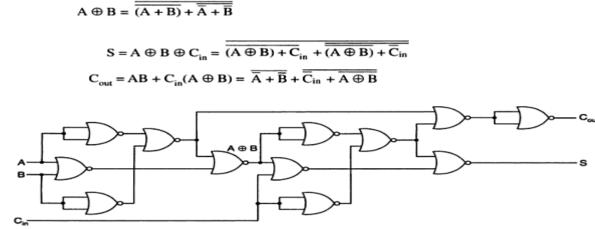

NOR Logic:

Logic diagram of a full-adder using only 2-input NOR gates.

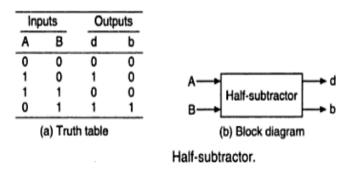

Subtractors:

Then

The subtraction of two binary numbers may be accomplished by taking the complement of the subtrahend and adding it to the minuend. By this, the subtraction operation becomes an addition operation and instead of having a separate circuit for subtraction, the adder itself can be used to perform subtraction. This results in reduction of hardware. In subtraction, each subtrahend bit of the number is subtracted from its corresponding significant minuend bit to form a difference bit. If the minuend bit is smaller than the subtrahend bit, a 1 is borrowed from the next significant position., that has been borrowed must be conveyed to the next higher pair of bits by means of a signal coming out (output) of a given stage and going into (input) the next higher stage.

The Half-Subtractor:

A Half-subtractor is a combinational circuit that subtracts one bit from the other and produces the difference. It also has an output to specify if a 1 has been borrowed. . It is used to subtract the LSB of the subtrahend from the LSB of the minuend when one binary number is subtracted from the other.

A Half-subtractor is a combinational circuit with two inputs A and B and two outputs d and b. d indicates the difference and b is the output signal generated that informs the next stage that a 1 has been borrowed. When a bit B is subtracted from another bit A, a difference bit (d) and a borrow bit (b) result according to the rules given as

The output borrow b is a 0 as long as A $\geq$ B. It is a 1 for A=0 and B=1. The d output is the result of the arithmetic operation2b+A-B.

A circuit that produces the correct difference and borrow bits in response to every possible combination of the two 1-bit numbers is , therefore ,

d=A+

$\mathbf{A} \oplus \mathbf{B}$  and  $\mathbf{b}=\mathbf{B}$

That is, the difference bit is obtained by X-OR ing the two inputs, and the borrow bit is obtained by ANDing the complement of the minuend with the subtrahend.Note that logic for this exactly the same as the logic for output S in the half-adder.

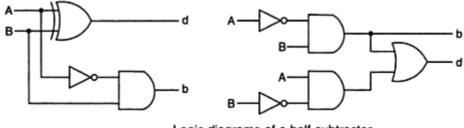

Logic diagrams of a half-subtractor.

A half-substractor can also be realized using universal logic either using only NAND gates or using NOR gates as:

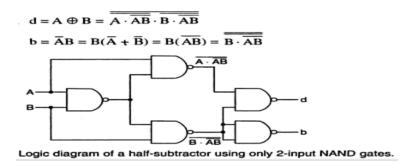

NAND Logic:

NOR Logic:

$$d = A \oplus B = A\overline{B} + \overline{A}B = A\overline{B} + B\overline{B} + \overline{A}B + A\overline{A}$$

$$= \overline{B}(A + B) + \overline{A}(A + B) = \overline{B + \overline{A + B}} + \overline{A + \overline{A + B}}$$

$$d = \overline{A}B = \overline{A}(A + B) = \overline{\overline{A}(A + B)} = \overline{\overline{A} + (\overline{A + B})}$$

Logic diagram of a half-subtractor using only 2-input NOR gates.

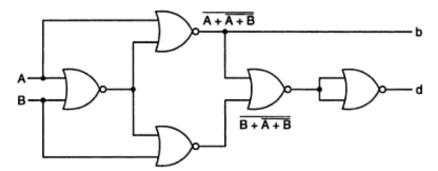

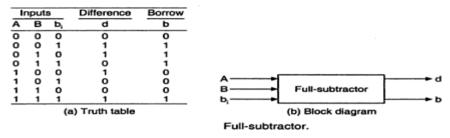

The Full-Subtractor:

The half-subtractor can be only for LSB subtraction. IF there is a borrow during the subtraction of the LSBs, it affects the subtraction in the next higher column; the subtrahend bit is subtracted from the minuend bit, considering the borrow from that column used for the subtraction in the preceding column. Such a subtraction is performed by a full-subtractor. It subtracts one bit (B) from another bit (A), when already there is a borrow bi from this column for the subtraction in the preceding column, and outputs the difference bit (d) and the borrow bit(b) required from the next d and b. The two outputs present the difference and output borrow. The 1s and 0s for the output variables are determined from the subtraction of A-B-b<sub>i</sub>.

From the truth table, a circuit that will produce the correct difference and borrow bits in response to every possible combinations of A, B and  $b_i$  is

$$\begin{aligned} \mathbf{d} &= \overline{\mathbf{A}} \overline{\mathbf{B}} \mathbf{b}_i + \overline{\mathbf{A}} \mathbf{B} \,\overline{\mathbf{b}}_i + \mathbf{A} \overline{\mathbf{B}} \,\overline{\mathbf{b}}_i + \mathbf{A} \mathbf{B} \mathbf{b}_i \\ &= \mathbf{b}_i (\mathbf{A} \mathbf{B} + \overline{\mathbf{A}} \overline{\mathbf{B}}) + \overline{\mathbf{b}}_i (\mathbf{A} \overline{\mathbf{B}} + \overline{\mathbf{A}} \mathbf{B}) \\ &= \mathbf{b}_i (\overline{\mathbf{A} \oplus \mathbf{B}}) + \overline{\mathbf{b}}_i (\mathbf{A} \oplus \mathbf{B}) = \mathbf{A} \oplus \mathbf{B} \oplus \mathbf{b}_i \\ \mathbf{b} &= \overline{\mathbf{A}} \overline{\mathbf{B}} \mathbf{b}_i + \overline{\mathbf{A}} \mathbf{B} \,\overline{\mathbf{b}}_i + \overline{\mathbf{A}} \mathbf{B} \mathbf{b}_i + \mathbf{A} \mathbf{B} \mathbf{b}_i = \overline{\mathbf{A}} \mathbf{B} (\mathbf{b}_i + \overline{\mathbf{b}}_i) + (\mathbf{A} \mathbf{B} + \overline{\mathbf{A}} \overline{\mathbf{B}}) \mathbf{b}_i \\ &= \overline{\mathbf{A}} \mathbf{B} + (\overline{\mathbf{A} \oplus \mathbf{B}}) \mathbf{b}_i \end{aligned}$$

and

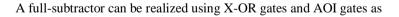

Logic diagram of a full-subtractor.

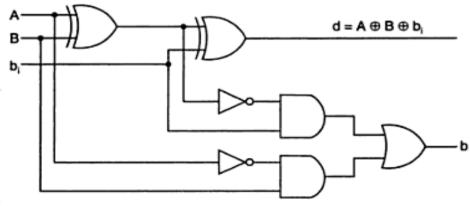

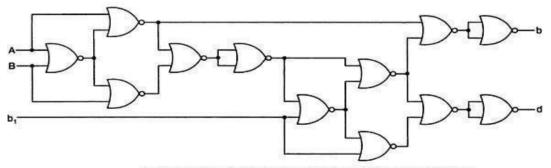

The full subtractor can also be realized using universal logic either using only NAND gates or using NOR gates as: NAND Logic:

Logic diagram of a full-subtractor using only 2-input NAND gates.

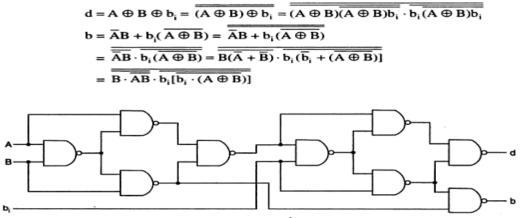

NOR Logic:

$$d = A \oplus B \oplus b_{i} = \overline{(A \oplus B) \oplus b_{i}}$$

$$= \overline{(A \oplus B)b_{i} + (\overline{A \oplus B})\overline{b}_{i}}$$

$$= \overline{[(A \oplus B) + (\overline{A \oplus B})\overline{b}_{i}][b_{i} + (\overline{A \oplus B})\overline{b}_{i}]}$$

$$= \overline{(A \oplus B) + (\overline{A \oplus B}) + \overline{b}_{i}} + \overline{b_{i} + (\overline{A \oplus B}) + \overline{b}_{i}}$$

$$= \overline{(A \oplus B) + (\overline{A \oplus B}) + \overline{b}_{i}} + \overline{b_{i} + (\overline{A \oplus B}) + \overline{b}_{i}}$$

$$= \overline{(A \oplus B) + (\overline{A \oplus B}) + \overline{b}_{i}} + \overline{b_{i} + (\overline{A \oplus B}) + \overline{b}_{i}}$$

$$= \overline{AB} + b_{i}(\overline{A \oplus B})$$

$$= \overline{A(A + B) + (\overline{A \oplus B})[(A \oplus B) + b_{i}]}$$

$$= \overline{\overline{A} + (\overline{A + B}) + (\overline{A \oplus B}) + (\overline{A \oplus B}) + \overline{b}_{i}}$$

Logic diagram of a full subtractor using only 2-input NOR gates.

Binary Parallel Adder:

A binary parallel adder is a digital circuit that adds two binary numbers in parallel form and produces the arithmetic sum of those numbers in parallel form. It consists of full adders connected in a chain , with the output carry from each full-adder connected to the input carry of the next full-adder in the chain.

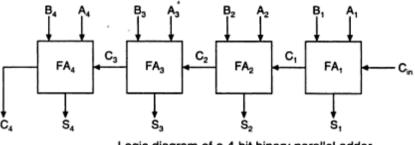

The interconnection of four full-adder (FA) circuits to provide a 4-bit parallel adder. The augends bits of A and addend bits of B are designated by subscript numbers from right to left, with subscript 1 denoting the lower –order bit. The carries are connected in a chain through the full-adders. The input carry to the adder is  $C_{in}$  and the output carry is  $C_4$ . The S output generates the required sum bits. When the 4-bit full- adder circuit is enclosed within an IC package, it has four terminals for the augends bits, four terminals for the addend bits, four terminals for the sum bits, and two terminals for the input and output carries. AN n-bit parallel adder requires n-full adders. It can be constructed from 4-bit, 2-bit and 1-bit full adder ICs by cascading several packages. The output carry from one package must be connected to the input carry of the one with the next higher –order bits. The 4-bit full adder is a typical example of an MSI function.

Logic diagram of a 4-bit binary parallel adder.

Ripple carry adder:

In the parallel adder, the carry –out of each stage is connected to the carry-in of the next stage. The sum and carry-out bits of any stage cannot be produced, until sometime after the carry-in of that stage occurs. This is due to the propagation delays in the logic circuitry,

which lead to a time delay in the addition process. The carry propagation delay for each full- adder is the time between the application of the carry-in and the occurrence of the carry-out.

The 4-bit parallel adder, the sum  $(S_1)$  and carry-out  $(C_1)$  bits given by  $FA_1$  are not valid, until after the propagation delay of  $FA_1$ . Similarly, the sum  $S_2$  and carry-out  $(C_2)$  bits given by  $FA_2$  are not valid until after the cumulative propagation delay of two full adders  $(FA_1 \text{ and } FA_2)$ , and so on. At each stage ,the sum bit is not valid until after the carry bits in all the preceding stages are valid. Carry bits must propagate or ripple through all stages before the most significant sum bit is valid. Thus, the total sum (the parallel output) is not valid until after the cumulative delay of all the adders.

The parallel adder in which the carry-out of each full-adder is the carry-in to the next most significant adder is called a ripple carry adder.. The greater the number of bits that a ripple carry adder must add, the greater the time required for it to perform a valid addition. If two numbers are added such that no carries occur between stages, then the add time is simply the propagation time through a single full-adder.

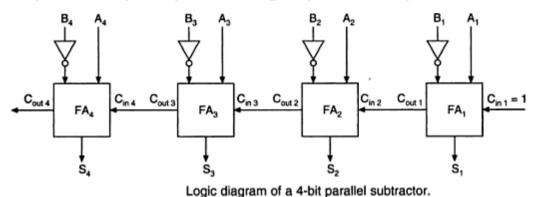

4-Bit Parallel Subtractor:

The subtraction of binary numbers can be carried out most conveniently by means of complements, the subtraction A-B can be done by taking the 2\_s complement of B and adding it to A. The 2\_s complement can be obtained by taking the 1\_s complement and adding 1 to the least significant pair of bits. The 1\_s complement can be implemented with inverters as

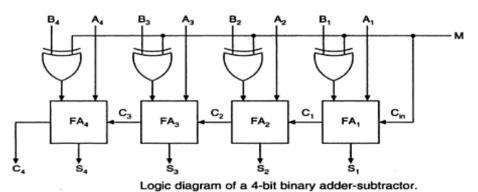

Binary-Adder Subtractor:

A 4-bit adder-subtractor, the addition and subtraction per ations are combined into one circuit with one common binary adder. This is done by including an X-OR gate with each full-adder. The mode input M controls the operation. When M=0, the circuit is an adder, and when M=1, the circuit becomes a subtractor. Each X-OR gate receives input M and one of the inputs of B. When M=0, The full-adder receives the value of B , the input carry is 0 and the circuit performs A+B. whenand  $C_1=1$ . The B inputs are complemented and a 1 is through the input carry. The circuit performs the operation A plus the 2\_s complement of B.

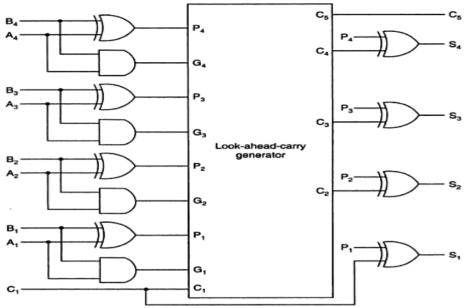

The Look-Ahead –Carry Adder:

In parallel-adder, the speed with which an addition can be performed is governed by the time required for the carries to propagate or ripple through all of the stages of the adder. The look-ahead carry adder speeds up the process by eliminating this ripple carry delay. It examines all the input bits simultaneously and also generates the carry-in bits for all the stages simultaneously.

The method of speeding up the addition process is based on the two additional functions of the full-adder, called the carry generate and carry propagate functions.

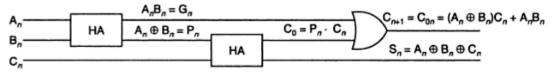

Consider one full adder stage; say the nth stage of a parallel adder as shown in fig. we know that is made by two half adders and that the half adder contains an X-OR gate to produce the sum and an AND gate to produce the carry. If both the bits  $A_n$  and  $B_n$  are 1s, a carry has to be generated in this stage regardless of whether the input carry  $C_{in}$  is a 0 or a 1. This is called generated carry, expressed as  $G_n = A_n$ .  $B_n$  which has to appear at the output through the OR gate as shown in fig.

#### A full adder (nth stage of a parallel adder).

There is another possibility of producing a carry out. X-OR gate inside the half-adder

at the input produces an intermediary sum bit- call it  $P_n$  –which is expressed as  $P_n = A_n \oplus B_n$ . Next  $P_n$  and  $C_n$  are added using the X-OR gate inside the second half adder to produce the final

sum bit and  $S_n = P_n \oplus C_n$  where  $P_n = A_n \oplus B_n$  and output carry  $C_0 = P_n \cdot C_n = (A_n \oplus B_n) \cdot C_n$  which becomes carry for the (n+1) thstage.

Consider the case of both  $P_n$  and  $C_n$  being 1. The input carry  $C_n$  has to be propagated to the output only if  $P_n$  is 1. If  $P_n$  is 0, even if  $C_n$  is 1, the and gate in the second half-adder will inhibit  $C_n$ . the carry out of the nth stage is 1 when either  $G_n=1$  or  $P_n.C_n=1$  or both  $G_n$  and  $P_n.C_n$  are equal to 1.

For the final sum and carry outputs of the nth stage, we get the following Boolean expressions.

$$S_n = P_n \oplus C_n$$

where  $P_n = A_n \oplus B_n$

$C_{on} = C_{n+1} = G_n + P_n C_n$  where  $G_n = A_n \cdot B_n$

Observe the recursive nature of the expression for the output carry at the nth stage which becomes the input carry for the (n+1)st stage it is possible to express the output carry of a higher significant stage is the carry-out of the previous stage.

Based on these, the expression for the carry-outs of various full adders are as follows,

$$\begin{split} & C_1 = G_0 + P_0 \cdot C_0 \\ & C_2 = G_1 + P_1 \cdot C_1 = G_1 + P_1 \cdot G_0 + P_1 \cdot P_0 \cdot C_0 \\ & C_3 = G_2 + P_2 \cdot C_2 = G_2 + P_2 \cdot G_1 + P_2 \cdot P_1 \cdot G_0 + P_2 \cdot P_1 \cdot P_0 \cdot C_0 \\ & C_4 = G_3 + P_3 \cdot C_3 = G_3 + P_3 \cdot G_2 + P_3 \cdot P_2 \cdot G_1 + P_3 \cdot P_2 \cdot P_1 \cdot G_0 + P_3 \cdot P_2 \cdot P_1 \cdot P_0 \cdot C_0 \\ & \text{The general expression for } n \text{ stages designated as 0 through } (n-1) \text{ would be} \end{split}$$

$$\mathbf{C}_{n} = \mathbf{G}_{n-1} + \mathbf{P}_{n-1} \cdot \mathbf{C}_{n-1} = \mathbf{G}_{n-1} + \mathbf{P}_{n-1} \cdot \mathbf{G}_{n-2} + \mathbf{P}_{n-1} \cdot \mathbf{P}_{n-2} \cdot \mathbf{G}_{n-3} + \dots + \mathbf{P}_{n-1} \cdot \dots \cdot \mathbf{P}_{0} \cdot \mathbf{C}_{0}$$

Observe that the final output carry is expressed as a function of the input variables in SOP form. Which is two level AND-OR or equivalent NAND-NAND form. Observe that the full look-ahead scheme requires the use of OR gate with (n+1) inputs and AND gates with number of inputs varying from 2 to (n+1).

Logic diagram of a 4-bit look-ahead-carry adder.

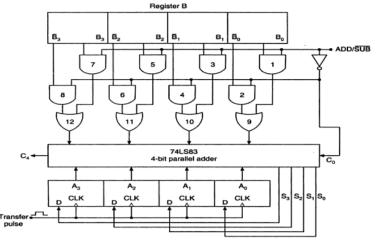

2's complement Addition and Subtraction using Parallel Adders:

Most modern computers use the 2\_s complement system to represent negative numbers and to perform subtraction operations of signed numbers can be performed using only the addition operation ,if we use the 2\_s complement form to represent negative numbers.

The circuit shown can perform both addition and subtraction in the 2\_s complement. This adder/subtractor circuit is controlled by the control signal ADD/SUB\_. When the ADD/SUB\_ level is HIGH, the circuit performs the addition of the numbers stored in registers A and B. When the ADD/Sub\_ level is LOW, the circuit subtract the number in register B from the number in register A. The operation is:

When ADD/SUB\_ is a 1:

- 1. AND gates 1,3,5 and 7 are enabled, allowing  $B_0, B_1, B_2$  and  $B_3$  to pass to the OR gates 9,10,11,12. AND gates 2,4,6 and 8 are disabled, blocking  $B_0, B_1, B_2$ , and  $B_3$  from reaching the OR gates 9,10,11 and 12.

- 2. The two levels  $B_0$  to  $B_3$  pass through the OR gates to the 4-bit parallel adder, to be added to the bits  $A_0$  to  $A_3$ . The sum appears at the output  $S_0$  to  $S_3$

- 3. Add/SUB\_=1 causes no carry into the adder. When ADD/SUB\_ is a0:

- AND gates 1,3,5 and 7 are disabled, allowing B<sub>0</sub>,B<sub>1</sub>,B<sub>2</sub>and B<sub>3</sub> from reaching the OR gates 9,10,11,12. AND gates 2,4,6 and 8 are enabled, blocking B<sub>0</sub>,B<sub>1</sub>,B<sub>2</sub>, and B<sub>3</sub> from reaching the OR gates.

- 1. The two levels  $B_0_{10}$  to  $B_{3_{10}}$  pass through the OR gates to the 4-bit parallel adder, to be added to the bits  $A_0$  to  $A_{3_{10}}$  The  $C_0$  is now thus the number in register B is converted to its 2\_s complement form.

- 2. The difference appears at the output  $S_0$  to $S_3$ .

Adders/Subtractors used for adding and subtracting signed binary numbers. In computers, the output is transferred into the register A (accumulator) so that the result of the addition or subtraction always end up stored in the register A This is accomplished by applying a transfer pulse to the CLK inputs of register A.

Logic diagram of a parallel adder/subtractor using 2's complement system.

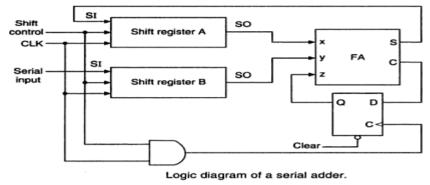

### Serial Adder:

A serial adder is used to add binary numbers in serial form. The two binary numbers to be added serially are stored in two shift registers A and B. Bits are added one pair at a time through a single full adder (FA) circuit as shown. The carry out of the full-adder is transferred to a D flip- flop. The output of this flip-flop is then used as the carry input for the next pair of significant bits. The sum bit from the S output of the full-adder could be transferred to a third shift register. By shifting the sum into A while the bits of A are shifted out, it is possible to use one register for storing both augend and the sum bits. The serial input register B can be used to transfer a new binary number while the addend bits are shifted out during the addition.

### The operation of the serial adder is:

Initially register A holds the augend, register B holds the addend and the carry flip-flop is cleared to 0. The outputs (SO) of A and B provide a pair of significant bits for the full-adder at x and y. The shift control enables both registers and carry flip-flop, so, at the clock pulse both registers are shifted once to the right, the sum bit from S enters the left most flip-flop of A, and the output carry is transferred into flip-flop Q. The shift control enables the registers for a number of clock pulses equal to the number of bits of the registers. For each succeeding clock pulse a new sum bit is transferred to A, a new carry is transferred to Q, and both registers are shifted once to the right. This process continues until the shift control is disabled. Thus the addition is accomplished by passing each pair of bits together with the previous carry through a single full adder circuit and transferring the sum, one bit at a time, into register A

Initially, register A and the carry flip-flop are cleared to 0 and then the first number is added from B. While B is shifted through the full adder, a second number is transferred to it through its serial input. The second number is then added to the content of register A while a third number is transferred serially into register B. This can be repeated to form the addition of two, three, or more numbers and accumulate their sum in register A.

Difference between Serial and Parallel Adders:

The parallel adder registers with parallel load, whereas the serial adder uses shift registers. The number of full adder circuits in the parallel adder is equal to the number of bits in the binary numbers, whereas the serial adder requires only one full adder circuit and a carry flip- flop. Excluding the registers, the parallel adder is a combinational circuit, whereas the serial adder is a sequential circuit. The sequential circuit in the serial adder consists of a full-adder and a flip-flop that stores the output carry.

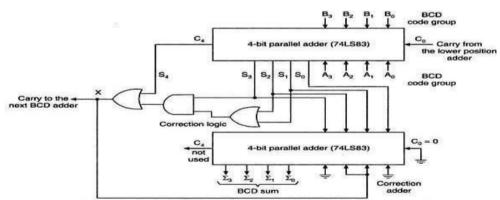

### BCD Adder:

The BCD addition process:

1. Add the 4-bit BCD code groups for each decimal digit position using ordinary binary addition.

2. For those positions where the sum is 9 or less, the sum is in proper BCD form and no correction is needed.

3. When the sum of two digits is greater than 9, a correction of 0110 should be added to that sum, to produce the proper BCD result. This will produce a carry to be added to the next decimal position.

A BCD adder circuit must be able to operate in accordance with the above steps. In other words, the circuit must be able to do the following:

1. Add two 4-bit BCD code groups, using straight binaryaddition.

2. Determine, if the sum of this addition is greater than 1101 (decimal 9); if it is, add 0110 (decimal 6) to this sum and generate a carry to the next decimal position.

The first requirement is easily met by using a 4- bit binary parallel adder such as the 74LS83 IC .For example, if the two BCD code groups  $A_3A_2A_1A_0$  and  $B_3B_2B_1B_0$  are applied to a 4-bit parallel adder, the adder will output  $S_4S_3S_2S_1S_0$ , where  $S_4$  is actually  $C_4$ , the carry –out of the MSB bits.

The sum outputs  $S_4S_3S_2S_1S_0$  can range anywhere from 00000 to 100109when both the BCD code groups are 1001=9). The circuitry for a BCD adder must include the logic needed to detect whenever the sum is greater than 01001, so that the correction can be added in. Those cases , where the sum is greater than 1001 are listed as:

| S <sub>4</sub> | S <sub>3</sub> | S <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> | Decimal number |

|----------------|----------------|----------------|----------------|----------------|----------------|

| 0              | 1              | 0              | 1              | 0              | 10             |

| 0              | 1              | 0              | 1              | 1              | 11             |

| 0              | 1              | 1              | 0              | 0              | 12             |

| 0              | 1              | 1              | 0              | 1              | 13             |

| 0              | 1              | 1              | 1              | 0              | 14             |

| 0              | 1              | 1              | 1              | 1              | 15             |

| 1              | 0              | 0              | 0              | 0              | 16             |

| 1              | 0              | 0              | 0              | 1              | 17             |

| 1              | 0              | 0              | 1              | 0              | 18             |

Let us define a logic output X that will go HIGH only when the sum is greater than 01001 (i.e, for the cases in table). If examine these cases ,see that X will be HIGH for either of the following conditions:

1. Whenever  $S_4 = 1$ (sum greater than 15)

2. Whenever  $S_3 = 1$  and either  $S_2$  or  $S_1$  or both are 1 (sum 10 to 15) This condition can be expressed as

$X = S_4 + S_3(S_2 + S_1)$

Whenever X=1, it is necessary to add the correction factor 0110 to the sum bits, and to generate a carry. The circuit consists of three basic parts. The two BCD code groups  $A_3A_2A_1A_0$  and  $B_3B_2B_1B_0$  are added together in the upper 4-bit adder, to produce the sum  $S_4S_3S_2S_1S_0$ . The logic gates shown implement the expression for X. The lower 4-bit adder will add the correction 0110 to the sum bits, only when X=1, producing the final BCD sum output represented by

$\sum_{3}\sum_{2}\sum_{1}\sum_{0}$ . The X is also the carry-out that is produced when the sum is greater than 01001. When X=0, there is no carry and no addition of 0110. In such cases,  $\sum_{3}\sum_{2}\sum_{1}\sum_{0}=S_{3}S_{2}S_{1}S_{0}$ .

Two or more BCD adders can be connected in cascade when two or more digit decimal numbers are to be added. The carry-out of the first BCD adder is connected as the carry-in of the second BCD adder, the carry-out of the second BCD adder is connected as the carry-in of the third BCD adder and so on.

Logic diagram of a BCD adder using two 4-bit adders and a correction-detector circuit.

#### EXCESS-3(XS-3) ADDER:

To perform Excess-3 additions, 1. Add two xs-3 code groups 2. If carry=1, add 0011(3) to the sum of those two codegroups If carry =0, subtract 0011(3) i.e., add 1101 (13 in decimal) to the sum of those two code groups. Ex: Add 9 and 5 1100 9 in Xs-3 +10005 in xs-3 \_ \_ 1 there is a carry 0100 add 3 to each group +00110011 \_\_\_\_\_ \_\_\_\_\_ 0100 0111 14 in xs-3 (1)(4) EX: 4 in XS-3 (b) 0111 3 in XS-3 +01101101 no carry Subtract 3 (i.e. add 13) +1101Ignore carry 1 1 0 1 0 7 in XS-3 (7)

Implementation of xs-3 adder using 4-bit binary adders is shown. The augend  $(A_3 A_2 A_1 A_0)$  and addend  $(B_3 B_2 B_1 B_0)$  in xs-3 are added using the 4-bit parallel adder. If the carry is a 1, then 0011(3) is added to the sum bits  $S_3 S_2 S_1 S_0$  of the upper adder in the lower 4-bit parallel adder. If the carry is a 0, then 1101(3) is added to the sum bits (This is equivalent to subtracting 0011(3) from the sum bits. The correct sum in xs-3 is obtained

Excess-3 (XS-3) Subtractor:

To perform Excess-3 subtraction,

1. Complement the subtrahend

2. Add the complemented subtrahend to the minuend.

3. If carry =1, result is positive. Add 3 and end around carry to the result. If carry=0, the result is negative. Subtract 3, i.e, and take the 1\_s complement of the result.

| Ex:   | Perform 9-4 |                        |

|-------|-------------|------------------------|

| 1100  |             | 9 in xs-3              |

| +1000 |             | Complement of 4 n Xs-3 |

|       |             |                        |

| (1)   | 0100        | There is a carry       |

| +0011 |             | Add 0011(3)            |

| 0111  |             |                        |

| 1     |             | End around carry       |

|       |             |                        |

| 1000  |             | 5 in xs-3              |

|       |             |                        |

The minuend and the 1\_s complement of the subtrahend in xs-3 are added in the upper 4- bit parallel adder. If the carry-out from the upper adder is a 0, then 1101 is added to the sum bits of the upper adder in the lower adder and the sum bits of the lower adder are complemented to get the result. If the carry-out from the upper adder is a 1, then 3=0011 is added to the sum bits of the lower adder and the sum bits of the lower adder give the result.

**Binary Multipliers:**

In binary multiplication by the paper and pencil method, is modified somewhat in digital machines because a binary adder can add only two binary numbers at a time.

In a binary multiplier, instead of adding all the partial products at the end, they are added two at a time and their sum accumulated in a register (the accumulator register). In addition, when the multiplier bit is a 0,0s are not written down and added because it does not affect the final result. Instead, the multiplicand is shifted left by one bit.

The multiplication of 1110 by 1001 using this processis Multiplicand 1110 Multiplier

1001

1110 The LSB of the multiplier is a 1; write down the multiplicand;

shift the multiplicand one position to the left  $(1\ 1\ 1\ 0\ 0)$

1110The second multiplier bit is a 0; write down the previous result 1110; shift the multiplicand to the left again (1 1 1 00 0)

+1110000The fourth multiplier bit is a 1 write down the new multiplicand add it to the first partial product to obtain the final product.

1111110

This multiplication process can be performed by the serial multiplier circuit, which multiplies two 4-bit numbers to produce an 8-bit product. The circuit consists of following elements

X register: A 4-bit shift register that stores the multiplier --- it will shift right on the falling edge of the clock. Note that 0s are shifted in from the left.

B register: An 8-bit register that stores the multiplicand; it will shift left on the falling edge of the clock. Note that 0s are shifted in from the right.

A register: An 8-bit register, i.e, the accumulator that accumulates the partial products. Adder: An 8-bit parallel adder that produces the sum of A and B registers. The adder outputs  $S_7$  through  $S_0$  are connected to the D inputs of the accumulator so that the sum can be transferred to the accumulator only when a clock pulse gets through the AND gate.

The circuit operation can be described by going through each step in the multiplication of 1110 by 1001. The complete process requires 4 clock cycles.

**1** Before the first clock pulse: Prior to the occurrence of the first clock pulse, the register A is loaded with 00000000, the register B with the multiplicand 00001110, and the register X with the multiplier 1001. Assume that each of these registers is loaded using its asynchronous inputs(i.e., PRESET and CLEAR). The output of the adder will be the sum of A and B,i.e., 00001110.

2 First Clock pulse: Since the LSB of the multiplier  $(X_0)$  is a 1, the first clock pulse gets through the AND gate and its positive going transition transfers the sum outputs into the accumulator. The subsequent negative going transition causes the X and B registers to shift right and left, respectively. This produces a new sum of A and.

3 Second Clock Pulse: The second bit of the original multiplier is now in  $X_0$ . Since this bit is a 0, the second clock pulse is inhibited from reaching the accumulator. Thus, the sum outputs are not transferred into the accumulator and the number in the accumulator does not change. The negative going transition of the clock pulse will again shift the X and B registers. Again a new sum is produced.

4 Third Clock Pulse: The third bit of the original multiplier is now in  $X_0$ ; since this bit is a 0, the third clock pulse is inhibited from reaching the accumulator. Thus, the sum outputs are not transferred into the accumulator and the number in the accumulator does not change. The negative going transition of the clock pulse will again shift the X and B registers. Again a new sum is produced.

**5** Fourth Clock Pulse: The last bit of the original multiplier is now in  $X_0$ , and since it is a 1, the positive going transition of the fourth pulse transfers the sum into the accumulator. The accumulator now holds the final product. The negative going transition of the clock pulse shifts X and B again. Note that, X is now 0000, since all the multiplier bits have been shifted out.

#### Code converters:

The availability of a large variety of codes for the same discrete elements of information results in the use of different codes by different digital systems. It is sometimes necessary to use the output of one system as the input to another. A conversion circuit must be inserted between the two systems if each uses different codes for the same information. Thus a code converter is a logic circuit whose inputs are bit patterns representing numbers (or character) in one cod and whose outputs are the corresponding representation in a different code. Code converters are usually multiple output circuits.

To convert from binary code A to binary code B, the input lines must supply the bit combination of elements as specified by code A and the output lines must generate the corresponding bit combination of code B. A combinational circuit performs this transformation by means of logic gates.

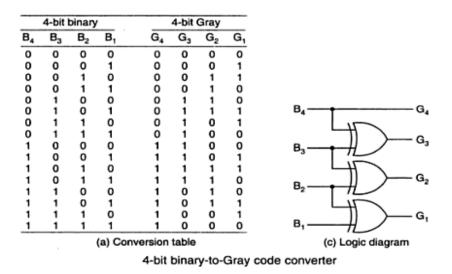

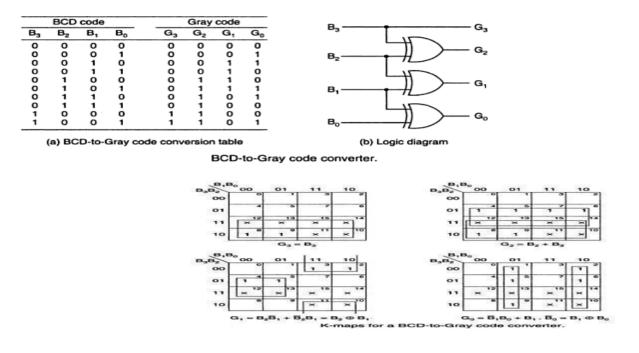

For example, a binary –to-gray code converter has four binary input lines  $B_4$ ,  $B_3$ ,  $B_2$ ,  $B_1$  and four gray code output lines  $G_4$ ,  $G_3$ ,  $G_2$ ,  $G_1$ . When the input is 0010, for instance, the output should be 0011 and so forth. To design a code converter, we use a code table treating it as a truth table to express each output as a Boolean algebraic function of all the inputs.

In this example, of binary –to-gray code conversion, we can treat the binary to the gray code table as four truth tables to derive expressions for  $G_4$ ,  $G_3$ ,  $G_2$ , and  $G_1$ . Each of these four expressions would, in general, contain all the four input variables  $B_4$ ,  $B_3$ ,  $B_2$ , and  $B_1$ . Thus, this code converter is actually equivalent to four logic circuits, one for each of the truth tables.

The logic expression derived for the code converter can be simplified using the usual techniques, including \_don\_t cares\_ if present. Even if the input is an unweighted code, the same cell numbering method which we used earlier can be used, but the cell numbers --must correspond to the input combinations as if they were an 8-4-2-1 weighted code. s

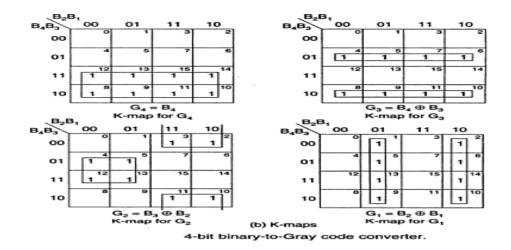

Design of a 4-bit binary to gray code converter:

| $G_4 = \Sigma m(8, 9, 10, 11, 12, 13, 14, 15)$ | $G_4 = B_4$                                                                                                                     |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| $G_3 = \Sigma m(4, 5, 6, 7, 8, 9, 10, 11)$     | $\mathbf{G}_3 = \mathbf{\overline{B}}_4 \mathbf{B}_3 + \mathbf{B}_4 \mathbf{\overline{B}}_3 = \mathbf{B}_4 \oplus \mathbf{B}_3$ |

| $G_2 = \Sigma m(2, 3, 4, 5, 10, 11, 12, 13)$   | $\mathbf{G}_2 = \overline{\mathbf{B}}_3 \mathbf{B}_2 + \mathbf{B}_3 \overline{\mathbf{B}}_2 = \mathbf{B}_3 \oplus \mathbf{B}_2$ |

| $G_1 = \Sigma m(1, 2, 5, 6, 9, 10, 13, 14)$    | $G_1 = \overline{B}_2 B_1 + B_2 \overline{B}_2 = B_2 \oplus B_1$                                                                |

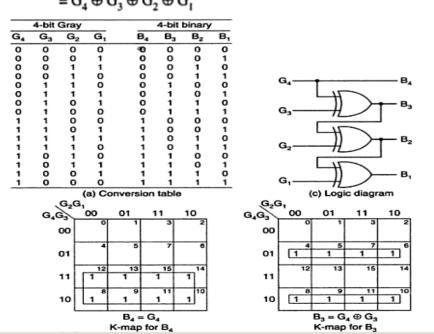

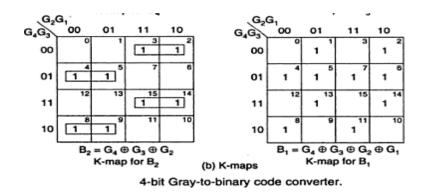

Design of a 4-bit gray to Binary code converter:

$$B_4 = \Sigma m(12, 13, 15, 14, 10, 11, 9, 8) = \Sigma m(8, 9, 10, 11, 12, 13, 14, 15)$$

$$B_3 = \Sigma m(6, 7, 5, 4, 10, 11, 9, 8) = \Sigma m(4, 5, 6, 7, 8, 9, 10, 11)$$

$$B_2 = \Sigma m(3, 2, 5, 4, 15, 14, 9, 8) = \Sigma m(2, 3, 4, 5, 8, 9, 14, 15)$$

$$B_1 = \Sigma m(1, 2, 7, 4, 13, 14, 11, 8) = \Sigma m(1, 2, 4, 7, 8, 11, 13, 14)$$

$$\begin{split} \mathbf{B}_4 &= \mathbf{G}_4 \\ \mathbf{B}_3 &= \mathbf{\overline{G}}_4 \mathbf{G}_3 + \mathbf{G}_4 \mathbf{\overline{G}}_3 = \mathbf{G}_4 \oplus \mathbf{G}_3 \\ \mathbf{B}_2 &= \mathbf{\overline{G}}_4 \mathbf{G}_3 \mathbf{\overline{G}}_2 + \mathbf{\overline{G}}_4 \mathbf{\overline{G}}_3 \mathbf{G}_2 + \mathbf{G}_4 \mathbf{\overline{G}}_3 \mathbf{\overline{G}}_2 + \mathbf{G}_4 \mathbf{G}_3 \mathbf{G}_2 \\ &= \mathbf{\overline{G}}_4 (\mathbf{G}_3 \oplus \mathbf{G}_2) + \mathbf{G}_4 (\mathbf{\overline{G}}_3 \oplus \mathbf{G}_2) = \mathbf{G}_4 \oplus \mathbf{G}_3 \oplus \mathbf{G}_2 = \mathbf{B}_3 \oplus \mathbf{G}_2 \\ \mathbf{B}_1 &= \mathbf{\overline{G}}_4 \mathbf{\overline{G}}_3 \mathbf{\overline{G}}_2 \mathbf{G}_1 + \mathbf{\overline{G}}_4 \mathbf{\overline{G}}_3 \mathbf{G}_2 \mathbf{\overline{G}}_1 + \mathbf{\overline{G}}_4 \mathbf{G}_3 \mathbf{G}_2 \mathbf{G}_1 + \mathbf{G}_4 \mathbf{G}_3 \mathbf{\overline{G}}_2 \mathbf{\overline{G}}_1 + \mathbf{G}_4 \mathbf{G}_3 \mathbf{\overline{G}}_2 \mathbf{\overline{G}}_1 \\ &\quad + \mathbf{G}_4 \mathbf{G}_3 \mathbf{G}_2 \mathbf{\overline{G}}_1 + \mathbf{G}_4 \mathbf{\overline{G}}_3 \mathbf{G}_2 \mathbf{\overline{G}}_1 + \mathbf{G}_4 \mathbf{\overline{G}}_3 \mathbf{\overline{G}}_2 \mathbf{\overline{G}}_1 \end{split}$$

$$= \overline{G}_4 \overline{G}_3 (G_2 \oplus G_1) + G_4 G_3 (G_2 \oplus G_1) + \overline{G}_4 G_3 (\overline{G_2 \oplus G_1}) + G_4 \overline{G}_3 (\overline{G_2 \oplus G_1})$$

$$= (G_2 \oplus G_1) (\overline{G_4 \oplus G_3}) + (\overline{G_2 \oplus G_1}) (G_4 \oplus G_3)$$

$$= G_4 \oplus G_2 \oplus G_3 \oplus G_4$$

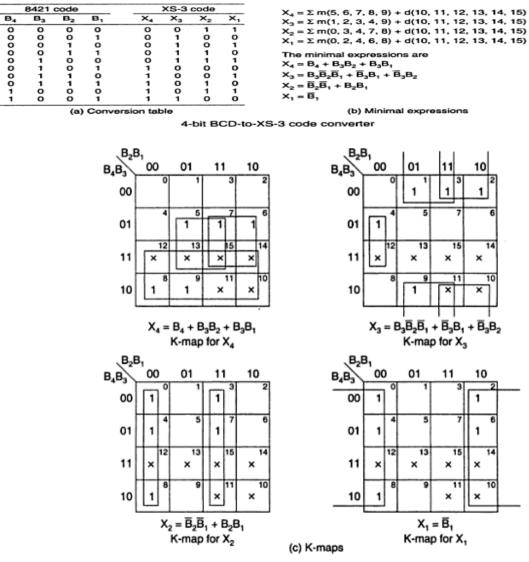

Design of a 4-bit BCD to XS-3 code converter:

4-bit BCD-to-XS-3 code converter.

Design of aBCD to gray code converter:

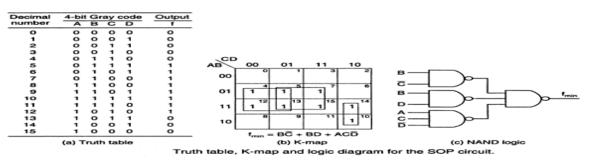

DesignofaSOPcircuittoDetecttheDecimalnumbers5through12ina4-bitgraycode Input:

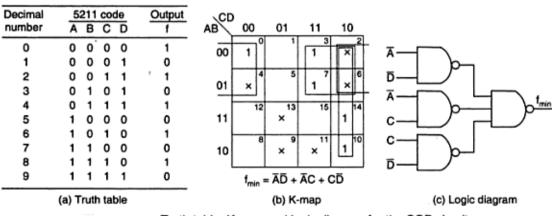

Design of a SOP circuit to detect the decimal numbers 0,2,4,6,8 in a 4-bit 5211 BCD code input:

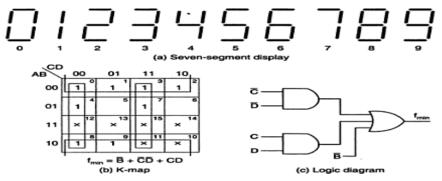

Truth table, K-map and logic diagram for the SOP circuit.

DesignofaCombinationalcircuittoproducethe2'scomplementofa4-bitbinarynumber:

| Input |   |   |   |  | Output |   |     |   |

|-------|---|---|---|--|--------|---|-----|---|

| Α     | в | С | D |  | Е      | F | G   | н |

| 0     | 0 | 0 | 0 |  | 0      | 0 | 0   | 0 |

| 0     | 0 | 0 | 1 |  | 1      | 1 | 1   | 1 |

| 0     | 0 | 1 | 0 |  | 1      | 1 | 1 - | 0 |

| 0     | 0 | 1 | 1 |  | 1      | 1 | 0   | 1 |

| 0     | 1 | 0 | 0 |  | 1      | 1 | 0   | 0 |

| 0     | 1 | 0 | 1 |  | 1      | 0 | 1   | 1 |

| 0     | 1 | 1 | 0 |  | 1      | 0 | 1   | 0 |

| 0     | 1 | 1 | 1 |  | 1      | 0 | 0   | 1 |

| 1     | 0 | 0 | 0 |  | 1      | 0 | 0   | 0 |

| 1     | 0 | 0 | 1 |  | 0      | 1 | 1   | 1 |

| 1     | 0 | 1 | 0 |  | 0      | 1 | 1   | 0 |

| 1     | 0 | 1 | 1 |  | 0      | 1 | 0   | 1 |

| 1     | 1 | 0 | 0 |  | 0      | 1 | 0   | 0 |

| 1     | 1 | 0 | 1 |  | 0      | 0 | 1   | 1 |

| 1     | 1 | 1 | 0 |  | 0      | 0 | 1   | 0 |

| 1     | 1 | 1 | 1 |  | 0      | 0 | 0   | 1 |

(a) Conversion table

Conversion table and K-maps for the circuit

Comparators:

$\text{EQUALITY} = (\textbf{A}_3 \odot \textbf{B}_3)(\textbf{A}_2 \odot \textbf{B}_2)(\textbf{A}_1 \odot \textbf{B}_1)(\textbf{A}_0 \odot \textbf{B}_0)$

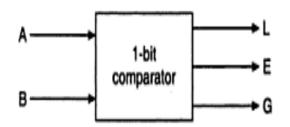

Block diagram of a 1-bit comparator.

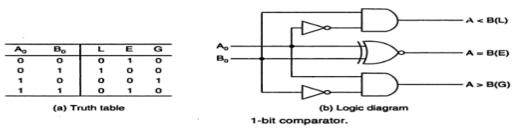

The logic for a 1-bit magnitude comparator: Let the 1-bit numbers be  $A = A_0$  and  $B = B_0$ . If  $A_0 = 1$  and  $B_0 = 0$ , then A > B. Therefore,

$A > B: G = A_0 \overline{B}_0$

If  $A_0 = 0$  and  $B_0 = 1$ , then A < B. Therefore,

$$A < B: L = A_0 B$$

If  $A_0$  and  $B_0$  coincide, i.e.  $A_0 = B_0 = 0$  or if  $A_0 = B_0 = 1$ , then A = B. Therefore,

$$\mathbf{A} = \mathbf{B} : \mathbf{E} = \mathbf{A}_0 \odot \mathbf{B}_0$$

1. Magnitude Comparator:

1- bit Magnitude Comparator:

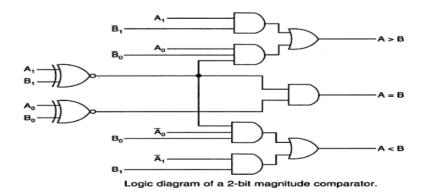

The logic for a 2-bit magnitude comparator: Let the two 2-bit numbers be  $A = A_1 A_0$  and  $B = B_1 B_0$ .

1. If  $A_1 = 1$  and  $B_1 = 0$ , then A > B or

2. If  $A_1$  and  $B_1$  coincide and  $A_0 = 1$  and  $B_0 = 0$ , then A > B. So the logic expression for A > B is  $A > B : G = A_1\overline{B}_1 + (A_1 \odot B_1)A_0\overline{B}_0$

1. If  $A_1 = 0$  and  $B_1 = 1$ , then A < B or 2. If  $A_1$  and  $B_1$  coincide and  $A_0 = 0$  and  $B_0 = 1$ , then A < B. So the expression for A < B is

$$\mathbf{A} < \mathbf{B} : \mathbf{L} = \overline{\mathbf{A}}_{1}\mathbf{B}_{1} + (\mathbf{A}_{1} \odot \mathbf{B}_{1})\overline{\mathbf{A}}_{0}\mathbf{B}_{0}$$

If  $A_1$  and  $B_1$  coincide and if  $A_0$  and  $B_0$  coincide then A = B. So the expression for A = B is

$$\mathbf{A} = \mathbf{B} : \mathbf{E} = (\mathbf{A}_1 \odot \mathbf{B}_1)(\mathbf{A}_0 \odot \mathbf{B}_0)$$

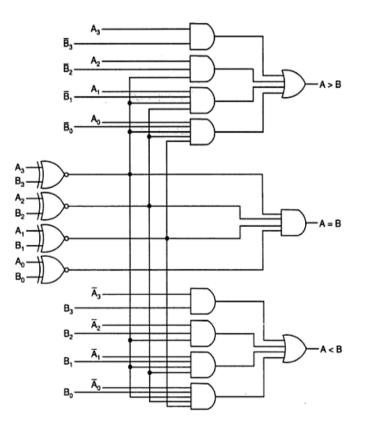

The logic for a 4-bit magnitude comparator: Let the two 4-bit numbers be  $A = A_3A_2A_1A_0$  and  $B = B_3B_2B_1B_0$ .

- 1. If  $A_3 = 1$  and  $B_3 = 0$ , then A > B. Or

- 2. If A<sub>3</sub> and B<sub>3</sub> coincide, and if A<sub>2</sub> = 1 and B<sub>2</sub> = 0, then A > B. Or

- 3. If  $A_3$  and  $B_3$  coincide, and if  $A_2$  and  $B_2$  coincide, and if  $A_1 = 1$  and  $B_1 = 0$ , then A > B. Or

- 4. If  $A_3$  and  $B_3$  coincide, and if  $A_2$  and  $B_2$  coincide, and if  $A_1$  and  $B_1$  coincide, and if  $A_0 = 1$  and  $B_0 = 0$ , then A > B.

From these statements, we see that the logic expression for A > B can be written as

$\begin{aligned} (\mathbf{A} > \mathbf{B}) &= \mathbf{A}_3 \overline{\mathbf{B}}_3 + (\mathbf{A}_3 \odot \mathbf{B}_3) \mathbf{A}_2 \overline{\mathbf{B}}_2 + (\mathbf{A}_3 \odot \mathbf{B}_3) (\mathbf{A}_2 \odot \mathbf{B}_2) \mathbf{A}_1 \overline{\mathbf{B}}_1 \\ &+ (\mathbf{A}_3 \odot \mathbf{B}_3) (\mathbf{A}_2 \odot \mathbf{B}_2) (\mathbf{A}_1 \odot \mathbf{B}_1) \mathbf{A}_0 \overline{\mathbf{B}}_0 \end{aligned}$

Similarly, the logic expression for A < B can be written as

$$A < B = \overline{A}_3 B_3 + (A_3 \odot B_3) \overline{A}_2 B_2 + (A_3 \odot B_3) (A_2 \odot B_2) \overline{A}_1 B_1$$

$$+ (A_3 \odot B_3) (A_2 \odot B_2) \overline{A}_1 B_1$$

+

$$(A_3 \odot B_3)(A_2 \odot B_2)(A_1 \odot B_1)A_0B_0$$