# **LECTURE NOTES**

## ON

## **EMBEDDED SYSTEM DESIGN**

**B.Tech VI Semester (AUTONOMOUS)**

(Regulation: IARE-R16)

(2018-2019)

Mr. N Nagaraju Assistant professor

## **INFORMATION TECHNOLOGY**

INSTITUTE OF AERONAUTICAL ENGINEERING (AUTONOMOUS) DUNDIGAL, HYDERABAD - 500043

## UNIT-I EMBEDDED COMPUTING

#### **INTRODUCTION**

This chapter introduces the reader to the world of embedded systems. Everything that we look around us today is electronic. The days are gone where almost everything was manual. Now even the food that we eat is cooked with the assistance of a microchip (oven) and the ease at which we wash our clothes is due to the washing machine. This world of electronic items is made up of embedded system. In this chapter we will understand the basics of embedded system right from its definition.

#### **DEFINITION OF AN EMBEDDED SYSTEM**

- An embedded system is a combination of 3 things:

- a. Hardware

- b. Software

- c. Mechanical Components

And it is supposed to do one specific task only.

#### • Example 1: Washing Machine

A washing machine from an embedded systems point of view has:

- a. Hardware: Buttons, Display & buzzer, electronic circuitry.

- b. Software: It has a chip on the circuit that holds the software which drives controls & monitors the various operations possible.

- c. Mechanical Components: the internals of a washing machine which actually wash the clothes control the input and output of water, the chassis itself.

## • Example 2: Air Conditioner

An Air Conditioner from an embedded systems point of view has:

- a. Hardware: Remote, Display & buzzer, Infrared Sensors, electronic circuitry.

- b. Software: It has a chip on the circuit that holds the software which drives controls & monitors the various operations possible. The software monitors the external temperature through the sensors and then releases the coolant or suppresses it.

- c. Mechanical Components: the internals of an air conditioner the motor, the chassis, the outlet, etc

- An embedded system is designed to do a specific job only. Example: a washing machine can only wash clothes, an air conditioner can control the temperature in the room in which it is placed.

- The hardware & mechanical components will consist all the physically visible

things that are used for input, output, etc.

• An embedded system will always have a chip (either microprocessor or microcontroller) that has the code or software which drives the system.

## HISTORY OF EMBEDDED SYSTEM

- The first recognised embedded system is the Apollo Guidance Computer(AGC) developed by MIT lab.

- AGC was designed on 4K words of ROM & 256 words of RAM.

- The clock frequency of first microchip used in AGC was 1.024 MHz.

- The computing unit of AGC consists of 11 instructions and 16 bit word logic.

- It used 5000 ICs.

- The UI of AGC is known DSKY(display/keyboard) which resembles a calculator type keypad with array of numerals.

- The first mass-produced embedded system was guidance computer for the Minuteman-I missile in 1961.

- In the year 1971 Intel introduced the world's first microprocessor chip called the 4004, was designed for use in business calculators. It was produced by the Japanese company Busicom.

## EMBEDDEDSYSTEM & GENERAL PURPOSE COMPUTER

The Embedded System and the General purpose computer are at two extremes. The embedded system is designed to perform a specific task whereas as per definition the general purpose computer is meant for general use. It can be used for playing games, watching movies, creating software, work on documents or spreadsheets etc.

Following are certain specific points of difference between embedded systems and general purpose computers:

| Criteria            | General Computer<br>Purpose                  | Embedded system                                                                                                |

|---------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Contents            | generic hardware and a                       | It is combination of special purpose<br>hardware and embedded OS for<br>executing specific set of applications |

| Operating<br>System | It contains general purpose operating system | It may or may not contain operating system.                                                                    |

| Alterations         | Applications are alterable by the user.      | Applications are non-alterable by the user.                                                                    |

| Key factor           | Performance is key factor. | Application specific requirements are key factors. |

|----------------------|----------------------------|----------------------------------------------------|

| Power<br>Consumption | More                       | Less                                               |

| Response<br>Time     | Not Critical               | Critical for some applications                     |

## CLASSIFICATION OF EMBEDDEDSYSTEM

The classification of embedded system is based on following criteria's:

- ➢ On generation

- On complexity & performance

- On deterministic behaviour

- > On triggering

## On generation

- 1. First generation(1G):

- Built around 8bit microprocessor & microcontroller.

- Simple in hardware circuit & firmware developed.

- Examples: Digital telephone keypads.

## 2. Second generation(2G):

- Built around 16-bit μp & 8-bit μc.

- They are more complex & powerful than 1G  $\mu$ p &  $\mu$ c.

- Examples: SCADA systems

## **3.** Third generation(3G):

- Built around 32-bit µp & 16-bit µc.

- Concepts like Digital Signal Processors(DSPs), Application Specific Integrated Circuits(ASICs) evolved.

- Examples: Robotics, Media, etc.

## 4. Fourth generation:

- Built around 64-bit µp & 32-bit µc.

- The concept of System on Chips (SoC), Multicore Processors evolved.

- Highly complex & very powerful.

- Examples: Smart Phones.

## **On complexity & performance**

## 1. Small-scale:

- Simple in application need

- Performance not time-critical.

- Built around low performance & low cost 8 or 16 bit  $\mu p/\mu c$ .

- Example: an electronic toy

## 2. Medium-scale:

- Slightly complex in hardware & firmware requirement.

- Built around medium performance & low cost 16 or 32 bit  $\mu p/\mu c$ .

- Usually contain operating system.

- Examples: Industrial machines.

## 3. Large-scale:

- Highly complex hardware & firmware.

- Built around 32 or 64 bit RISC  $\mu p/\mu c$  or PLDs or Multicore Processors.

- Response is time-critical.

- Examples: Mission critical applications.

## On deterministic behavior

- This classification is applicable for "Real Time" systems.

- The task execution behavior for an embedded system may be deterministic or non-deterministic.

- Based on execution behavior Real Time embedded systems are divided into Hard and Soft.

## **On triggering**

- Embedded systems which are "Reactive" in nature can be based on triggering.

- Reactive systems can be:

- ✓ Event triggered

- ✓ Time triggered

## APPLICATION OF EMBEDDED SYSTEM

The application areas and the products in the embedded domain are countless.

- 1. Consumer Electronics: Camcorders, Cameras.

- 2. Household appliances: Washing machine, Refrigerator.

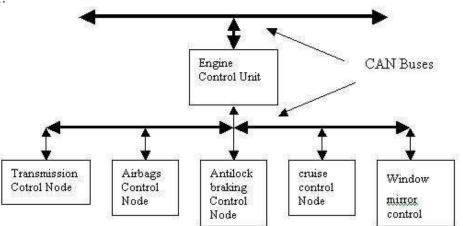

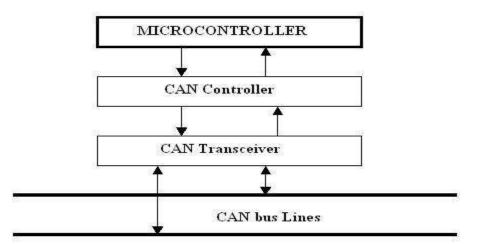

- 3. Automotive industry: Anti-lock breaking system(ABS), engine control.

- 4. Home automation & security systems: Air conditioners, sprinklers, fire alarms.

- 5. Telecom: Cellular phones, telephone switches.

- 6. Computer peripherals: Printers, scanners.

- 7. Computer networking systems: Network routers and switches.

- 8. Healthcare: EEG, ECG machines.

- 9. Banking & Retail: Automatic teller machines, point of sales.

- 10. Card Readers: Barcode, smart card readers.

### COMPLEX SYSTEMS AND MICROPROCESSORS

What is an *embedded computer system*? Loosely defined, it is any device that includes a programmable computer but is not itself intended to be a general-purpose computer. Thus, a PC is not itself an embedded computing system, although PCs are often used to build embedded computing systems. But a fax machine or a clock built from a microprocessor is an embedded computing system. This means that embedded computing system design is a useful skill for many types of product design. Automobiles, cell phones, and even household appliances make extensive use of microprocessors. Designers in many fields must be able to identify where microprocessors can be used, design a hardware platform with I/O devices that can support the required tasks, and implement software that performs the required processing. Computer engineering, like mechanical design or thermodynamics, is a fundamental discipline that can be applied in many different domains. But of course, embedded computing system design does not stand alone. Many of the challenges encountered in the design of an embedded computing system are not computer engineering-for example, they may be mechanical or analog electrical problems. In this book we are primarily interested in the embedded computer itself, so we will concentrate on the hardware and software that enable the desired functions in the final product.

#### **Embedding Computers**

Computers have been embedded into applications since the earliest days of computing. One example is the Whirlwind, a computer designed at MIT in the late 1940s and early 1950s. Whirlwind was also the first computer designed to support *real-time* operation and was originally conceived as a mechanism for controlling an aircraft simulator. Even though it was extremely large physically compared to today's computers (e.g., it contained over 4,000 vacuum tubes), its complete design from components to system was attuned to the needs of real-time embedded computing. The utility of computers in replacing mechanical or human controllers was evident from the very beginning of the computer era—for example, computers were proposed to control chemical processes in the late 1940s [Sto95].

A microprocessor is a single-chip CPU. Very large scale integration (VLSI) the acronym is the name technology has allowed us to put a complete CPU on a single chip since 1970s, but those CPUs were very simple. The first microprocessor, the Intel 4004, was designed for an embedded application, namely, a calculator. The calculator was not a generalpurpose computer-it merely provided basic arithmetic functions. However, Ted Hoff of Intel realized that a general-purpose computer programmed properly could implement the required function, and that the computer-on-a-chip could then be reprogrammed for use in other products as well. Since integrated circuit design was (and still is) an expensive and time consuming process, the ability to reuse the hardware design by changing the software was a key breakthrough. The HP-35 was the first handheld calculator to perform transcendental functions [Whi72]. It was introduced in 1972, so it used several chips to implement the CPU, rather than a single-chip microprocessor. However, the ability to write programs to perform math rather than having to design digital circuits to perform operations like trigonometric functions was critical to the successful design of the calculator. Automobile designers started making use of the microprocessor soon after single-chip CPUs became available. The most important and sophisticated use of microprocessors in automobiles was to control the engine: determining when spark plugs fire, controlling the fuel/air mixture, and so on. There was a trend toward electronics in automobiles in general—electronic devices could be used to replace the mechanical distributor. But the big push toward microprocessor-based engine control came from two nearly simultaneous developments: The oil shock of the 1970s caused consumers to place much higher value on fuel economy, and fears of pollution resulted in laws restricting automobile engine emissions. The combination of low fuel consumption and low emissions is very difficult to achieve; to meet these goals without compromising engine performance, automobile manufacturers turned to sophisticated control algorithms that could be implemented only with microprocessors.

Microprocessors come in many different levels of sophistication; they are usually classified by their word size. An 8-bit *microcontroller* is designed for low-cost applications and includes on-board memory and I/O devices; a 16-bit microcontroller is often used for more sophisticated applications that may require either longer word lengths or off-chip I/O and memory; and a 32-bit *RISC* microprocessor offers very high performance for computation-intensive applications. Given the wide variety of microprocessor types available, it should be no surprise that microprocessors are used in many ways. There are many household uses of microprocessors. The typical microwave oven has at least one microprocessor to control oven operation. Many houses have advanced thermostat systems, which change the temperature level at various times during the day. The modern camera is a prime example of the powerful features that can be added under microprocessor control.

Digital television makes extensive use of embedded processors. In some cases, specialized CPUs are designed to execute important algorithms—an example is the CPU designed for audio processing in the SGS Thomson chip set for DirecTV [Lie98]. This processor is designed to efficiently implement programs for digital audio decoding. A programmable CPU was used rather than a hardwired unit for two reasons: First, it made the system easier to design and debug; and second, it allowed the possibility of upgrades and using the CPU for other purposes. A high-end automobile may have 100 microprocessors, but even inexpensive cars today use 40 microprocessors. Some of these microprocessors do very simple things such as detect whether seat belts are in use. Others control critical functions such as the ignition and braking systems. Application Example describes some of the microprocessors used in the BMW 850i.

#### **Application Example**

#### BMW 850i brake and stability control system

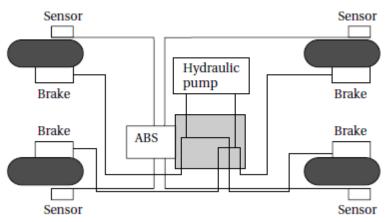

The BMW 850i was introduced with a sophisticated system for controlling the wheels of the car. An antilock brake system (ABS) reduces skidding by pumping the brakes. An automatic stability control (ASC\_T) system intervenes with the engine during maneuvering to improve the car's stability. These systems actively control critical systems of the car; as control systems, they require inputs from and output to the automobile.

Let's first look at the ABS. The purpose of an ABS is to temporarily release the brake on a wheel when it rotates too slowly—when a wheel stops turning, the car starts skidding and becomes hard to control. It sits between the hydraulic pump, which provides power to the brakes, and the brakes themselves as seen in the following diagram. This hookup allows the ABS system to modulate the brakes in order to keep the wheels from locking. The ABS

system uses sensors on each wheel to measure the speed of the wheel. The wheel speeds are used by the ABS system to determine how to vary the hydraulic fluid pressure to prevent the wheels from skidding. The ASC \_ T system's job is to control the engine power and the brake to improve the car's stability during maneuvers. The ASC \_ T controls four different systems: throttle, ignition timing, differential brake, and (on automatic transmission cars) gear shifting. The ASC\_T can be turned off by the driver, which can be important when operating with tire snow chains. The ABS and ASC \_ T must clearly communicate because the ASC \_ T interacts with the brake system. Since the ABS was introduced several years earlier than the ASC \_ T, it was important to be able to interface ASC \_ T to the existing ABS module, as well as to other existing electronic modules. The engine management, and electronic transmission control. The ASC \_ T control unit has two microprocessors on two printed circuit boards, one of which concentrates on logic-relevant components and the other on performance-specific components.

#### THE EMBEDDED SYSTEM DESIGN PROCESS

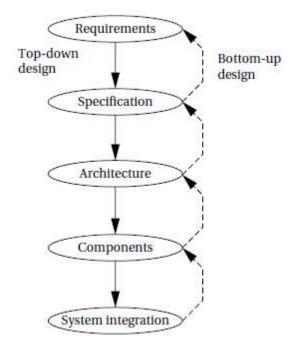

This section provides an overview of the embedded system design process aimed at two objectives. First, it will give us an introduction to the various steps in embedded system design before we delve into them in more detail. Second, it will allow us to consider the design *methodology* itself. A design methodology is important for three reasons. First, it allows us to keep a scorecard on a design to ensure that we have done everything we need to do, such as optimizing *performance* or performing functional tests. Second, it allows us to develop computer-aided design tools. Developing a single program that takes in a concept for an embedded system and emits a completed design would be a daunting task, but by first breaking the process into manageable steps, we can work on automating (or at least semi automating) the steps one at a time. Third, a design methodology makes it much easier for members of a design team to communicate. By defining the overall process, team members can more easily understand what they are supposed to do, what they should receive from other team members at certain times, and what they are to hand off when they complete their assigned steps. Since most embedded systems are designed by teams, coordination is perhaps the most important role of a well-defined design methodology. Figure summarizes the major steps in the embedded system design process.

In this top-down view, we start with the system *requirements*. In the next step,

*specification*, we create a more detailed description of what we want. But the specification states only how the system behaves, not how it is built. The details of the system's internals begin to take shape when we develop the architecture, which gives the system structure in terms of large components. Once we know the components we need, we can design those components, including both software modules and any specialized hardware we need. Based on those components, we can finally build a complete system.

In this section we will consider design from the *top-down*—we will begin with the most abstract description of the system and conclude with concrete details. The alternative is a **bottom–up** view in which we start with components to build a system. Bottom–up design steps are shown in the figure as dashed-line arrows. We need bottom–up design because we do not have perfect insight into how later stages of the design process will turn out. Decisions at one stage of design are based upon estimates of what will happen later: How fast can we make a particular function run? How much memory will we need? How much system bus capacity do we need? If our estimates are inadequate, we may have to backtrack and amend our original decisions to take the new facts into account. In general, the less experience we have with the design of similar systems, the more we will have to rely on bottom-up design information to help us refine the system. But the steps in the design process are only one axis along which we can view embedded system design. We also need to consider the major goals of the design:

- manufacturing cost;

- performance (both overall speed and deadlines); and

- power consumption.

We must also consider the tasks we need to perform at every step in the design process. At each step in the design, we add detail:

• We must *analyze* the design at each step to determine how we can meet the specifications.

■ We must then *refine* the design to add detail.

■ And we must verify the design to ensure that it still meets all system goals, such as cost, speed, and so on.

#### Requirements

Clearly, before we design a system, we must know what we are designing. The initial stages of the design process capture this information for use in creating the architecture and components. We generally proceed in two phases: First, we gather an informal description from the customers known as requirements, and we refine the requirements into a specification that contains enough information to begin designing the system architecture. Separating out requirements analysis and specification is often necessary because of the large gap between what the customers can describe about the system they want and what the architects need to design the system. Consumers of embedded systems are usually not themselves embedded system designers or even product designers. Their understanding of the system is based on how they envision users' interactions with the system. They may have unrealistic expectations as to what can be done within their budgets; and they may also express their desires in a language very different from system architects' jargon. Capturing a consistent set of requirements from the customer and then massaging those requirements into a more formal specification is a structured way to manage the process of translating from the consumer's language to the designer's.

Requirements may be *functional* or *nonfunctional*. We must of course capture the basic functions of the embedded system, but functional description is often not sufficient. Typical nonfunctional requirements include:

• *Performance:* The speed of the system is often a major consideration both for the usability of the system and for its ultimate cost. As we have noted, performance may be a combination of soft performance metrics such as approximate time to perform a user-level function and hard deadlines by which a particular operation must be completed.

■ *Cost:* The target cost or purchase price for the system is almost always a consideration. Cost typically has two major components: *manufacturing cost* includes the cost of components and assembly; *nonrecurring engineering* (NRE) costs include the personnel and other costs of designing the system.

■ *Physical size and weight:* The physical aspects of the final system can vary greatly depending upon the application. An industrial control system for an assembly line may be designed to fit into a standard-size rack with no strict limitations on weight. A handheld device typically has tight requirements on both size and weight that can ripple through the entire system design.

■ *Power consumption:* Power, of course, is important in battery-powered systems and is often important in other applications as well. Power can be specified in the requirements stage in terms of battery life—the customer is unlikely to be able to describe the allowable wattage.

Validating a set of requirements is ultimately a psychological task since it requires understanding both what people want and how they communicate those needs. One goodway to refine at least the user interface portion of a system's requirements is to build a *mock-up*. The mock-up may use canned data to simulate functionality in a restricted demonstration, and it may be executed on a PC or a workstation. But it should give the

customer a good idea of how the system will be used and how the user can react to it. Physical, nonfunctional models of devices can also give customers a better idea of characteristics such as size and weight.

Name Purpose Inputs Outputs Functions Performance Manufacturing cost Power Physical size and weight

Requirements analysis for big systems can be complex and time consuming. However, capturing a relatively small amount of information in a clear, simple format is a good start toward understanding system requirements. To introduce the discipline of requirements analysis as part of system design, we will use a simple requirements methodology. Figure shows a sample *requirements form* that can be filled out at the start of the project. We can use the form as a checklist in considering the basic characteristics of the system. Let's consider the entries in the form:

■ *Name:* This is simple but helpful. Giving a name to the project not only simplifies talking about it to other people but can also crystallize the purpose of the machine.

■ *Purpose:* This should be a brief one- or two-line description of what the system is supposed to do. If you can't describe the essence of your system in one or two lines, chances are that you don't understand it well enough.

■ *Inputs and outputs:* These two entries are more complex than they seem. The inputs and outputs to the system encompass a wealth of detail: — *Types of data:* Analog electronic signals? Digital data? Mechanical inputs? — *Data characteristics:* Periodically arriving data, such as digital audio samples? Occasional user inputs? How many bits per data element? — *Types of I/O devices:* Buttons? Analog/digital converters? Video displays?

■ *Functions:* This is a more detailed description of what the system does. A good way to approach this is to work from the inputs to the outputs: When the system receives an input, what does it do? How do user interface inputs affect these functions? How do different functions interact?

■ *Performance:* Many embedded computing systems spend at least some time controlling physical devices or processing data coming from the physical world. In most of these cases, the computations must be performed within a certain time frame. It is essential that the performance requirements be identified early since they must be carefully measured during implementation to ensure that the system works properly.

■ *Manufacturing cost:* This includes primarily the cost of the hardware components. Even if you don't know exactly how much you can afford to spend on system components, you should have some idea of the eventual cost range. Cost has a substantial influence on architecture: A machine that is meant to sell at \$10 most likely has a very different internal structure than a \$100 system.

• *Power:* Similarly, you may have only a rough idea of how much power the system can consume, but a little information can go a long way. Typically, the most important decision is whether the machine will be battery powered or plugged into the wall. Battery-powered machines must be much more careful about how they spend energy.

■ *Physical size and weight:* You should give some indication of the physical size of the system to help guide certain architectural decisions. A desktop machine has much more flexibility in the components used than, for example, a lapel mounted voice recorder.

A more thorough requirements analysis for a large system might use a form similar to Figure as a summary of the longer requirements document. After an introductory section containing this form, a longer requirements document could include details on each of the items mentioned in the introduction. For example, each individual feature described in the introduction in a single sentence may be described in detail in a section of the specification. After writing the requirements, you should check them for internal consistency: Did you forget to assign a function to an input or output? Did you consider all the modes in which you want the system to operate? Did you place an unrealistic number of features into a battery-powered, low-cost machine? To practice the capture of system requirements, Example creates the requirements for a GPS moving map system.

#### Example

#### Requirements analysis of a GPS moving map

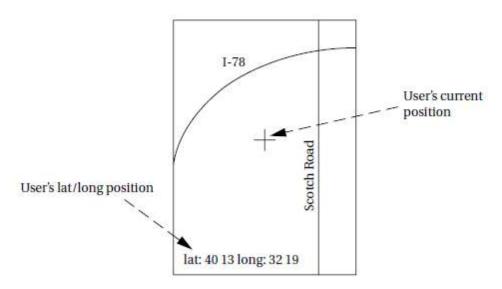

The moving map is a handheld device that displays for the user a map of the terrain around the user's current position; the map display changes as the user and the map device change position. The moving map obtains its position from the GPS, a satellite-based navigation system. The moving map display might look something like the following figure.

What requirements might we have for our GPS moving map? Here is an initial list:

■ *Functionality:* This system is designed for highway driving and similar uses, not nautical or aviation uses that require more specialized databases and functions. The

system should show major roads and other landmarks available in standard topographic databases.

• User interface: The screen should have at least  $400_{600}$  pixel resolution. The device should be controlled by no more than three buttons. A menu system should pop up on the screen when buttons are pressed to allow the user to make selections to control the system.

• *Performance:* The map should scroll smoothly. Upon power-up, a display should take no more than one second to appear, and the system should be able to verify its position and display the current map within 15 s.

■ *Cost:* The selling cost (street price) of the unit should be no more than \$100.

■ *Physical size and weight:* The device should fit comfortably in the palm of the hand.

■ *Power consumption:* The device should run for at least eight hours on four AA batteries.

Note that many of these requirements are not specified in engineering units—for example, physical size is measured relative to a hand, not in centimeters. Although these requirements must ultimately be translated into something that can be used by the designers, keeping a record of what the customer wants can help to resolve questions about the specification that may crop up later during design. Based on this discussion, let's write a requirements chart for our moving map system:

| Name                     | GPS moving map                                                                                                     |

|--------------------------|--------------------------------------------------------------------------------------------------------------------|

| Purpose                  | Consumer-grade moving map for driving use                                                                          |

| Inputs                   | Power button, two control buttons                                                                                  |

| Outputs                  | Back-lit LCD display $400 \times 600$                                                                              |

| Functions                | Uses 5-receiver GPS system; three user-selectable resolu-<br>tions; always displays current latitude and longitude |

| Performance              | Updates screen within 0.25 seconds upon movement                                                                   |

| Manufacturing cost       | \$30                                                                                                               |

| Power                    | 100 mW                                                                                                             |

| Physical size and weight | No more than 2" $\times$ 6, " 12 ounces                                                                            |

#### Specification

The specification is more precise—it serves as the contract between the customer and the architects. As such, the specification must be carefully written so that it accurately reflects the customer's requirements and does so in a way that can be clearly followed during design. Specification is probably the least familiar phase of this methodology for neophyte designers, but it is essential to creating working systems with a minimum of designer effort. Designers who lack a clear idea of what they want to build when they begin typically make faulty assumptions early in the process that aren't obvious until they have a working system. At that point, the only solution is to take the machine apart, throw away some of it, and start again. The specification should be understandable enough so that someone can verify that it meets system requirements and overall expectations of the customer. It should also be unambiguous enough that designers know what they need to build. Designers can run into several different types of problems caused by unclear specifications. If the behavior of some feature in a particular situation is unclear from the specification, the designer may implement the wrong functionality. If global characteristics

of the specification are wrong or incomplete, the overall system architecture derived from the specification may be inadequate to meet the needs of implementation.

A specification of the GPS system would include several components:

- Data received from the GPS satellite constellation.

- Map data.

- User interface.

- Operations that must be performed to satisfy customer requests.

- Background actions required to keep the system running, such as operating the GPS receiver.

UML, a language for describing specifications, will be introduced later and we will use it to write a specification. We will practice writing specifications in each chapter as we work through example system designs. We will also study specification techniques in more later.

## **Architecture Design**

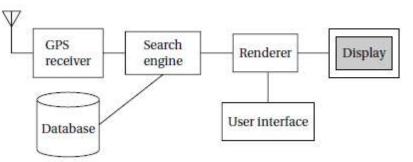

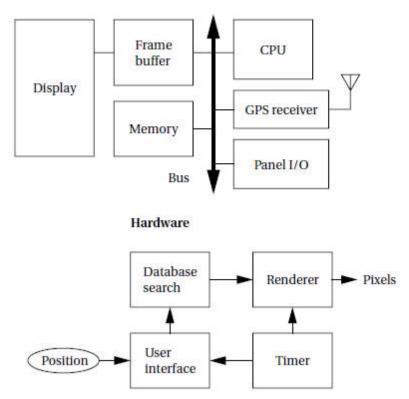

The specification does not say how the system does things, only what the system does. Describing how the system implements those functions is the purpose of the architecture. The architecture is a plan for the overall structure of the system that will be used later to design the components that make up the architecture. The creation of the architecture is the first phase of what many designers think of as design. To understand what an architectural description is, let's look at sample architecture for the moving map of Example Figure shows sample system architecture in the form of a *block diagram* that shows major operations and data flows among them.

This block diagram is still quite abstract—we have not yet specified which operations will be performed by software running on a CPU, what will be done by special-purpose hardware, and so on. The diagram does, however, go a long way toward describing how to implement the functions described in the specification. We clearly see, for example, that we need to search the topographic database and to render (i.e., draw) the results for the display. We have chosen to separate those functions so that we can potentially do them in parallel—performing rendering separately from searching the database may help us update the screen more fluidly.

Only after we have designed an initial architecture that is not biased toward too many implementation details should we refine that system block diagram into two block diagrams: one for hardware and another for software. These two more refined block diagrams are shown in Figure 1.4. The hardware block diagram clearly shows that we have one central CPU surrounded by memory and I/O devices. In particular, we have chosen to use two memories: a frame buffer for the pixels to be displayed and a separate

program/data memory for general use by the CPU. The software block diagram fairly closely follows the system block diagram, but we have added a timer to control when we read the buttons on the user interface and render data onto the screen. To have a truly complete architectural description, we require more detail, such as where units in the software block diagram will be executed in the hardware block diagram and when operations will be performed in time. Architectural descriptions must be designed to satisfy both functional and nonfunctional requirements. Not only must all the required functions be present, but we must meet cost, speed, power, and other nonfunctional constraints. Starting out with a system architecture and refining that to hardware and software architectures

is one good way to ensure that we meet all specifications: We can concentrate on the functional elements in the system block diagram, and then consider the nonfunctional constraints when creating the hardware and software architectures. How do we know that our hardware and software architectures in fact meet constraints on speed, cost, and so on? We must somehow be able to estimate the properties of the components of the block diagrams, such as the search and rendering functions in the moving map system. Accurate estimation derives in part from experience, both general design experience and particular experience with similar systems. However, we can sometimes create simplified models to help us make more accurate estimates. Sound estimates of all nonfunctional constraints during the architecture phase are crucial, since decisions based on bad data will show up during the final phases of design, indicating that we did not, in fact, meet the specification.

#### **Designing Hardware and Software Components**

The architectural description tells us what components we need. The component design effort builds those components in conformance to the architecture and specification. The components will in general include both hardware-FPGAs, boards, and so on-and software modules. Some of the components will be ready-made. The CPU, for example, will be a standard component in almost all cases, as will memory chips and many other components. In the moving map, the GPS receiver is a good example of a specialized component that will nonetheless be a predesigned, standard component. We can also make use of standard software modules. One good example is the topographic database. Standard topographic databases exist, and you probably want to use standard routines to access the database—not only is the data in a predefined format, but it is highly compressed to save storage. Using standard software for these access functions not only saves us design time, but it may give us a faster implementation for specialized functions such as the data decompression phase. You will have to design some components yourself. Even if you are using only standard integrated circuits, you may have to design the printed circuit board that connects them. You will probably have to do a lot of custom programming as well. When creating these embedded software modules, you must of course make use of your expertise to ensure that the system runs properly in real time and that it does not take up more memory space than is allowed. The power consumption of the moving map software example is particularly important. You may need to be very careful about how you read and write memory to minimize power-for example, since memory accesses are a major source of power consumption, memory transactions must be carefully planned to avoid reading the same data several times.

#### **System Integration**

Only after the components are built do we have the satisfaction of putting them together and seeing a working system. Of course, this phase usually consists of a lot more than just plugging everything together and standing back. Bugs are typically found during system integration, and good planning can help us find the bugs quickly. By building up the system in phases and running properly chosen tests, we can often find bugs more easily. If we debug only a few modules at a time, we are more likely to uncover the simple bugs and able to easily recognize them. Only by fixing the simple bugs early will we be able to uncover the more complex or obscure bugs that can be identified only by giving the system a hard workout. We need to ensure during the architectural and component design phases that we make it as easy as possible to assemble the system in phases and test functions relatively independently.

System integration is difficult because it usually uncovers problems. It is often hard to observe the system in sufficient detail to determine exactly what is wrong— the debugging facilities for embedded systems are usually much more limited than what you would find on desktop systems. As a result, determining why things do not stet work correctly and how they can be fixed is a challenge in itself. Careful attention to inserting appropriate debugging facilities during design can help ease system integration problems, but the nature of embedded computing means that this phase will always be a challenge.

#### FORMALISMS FOR SYSTEM DESIGN

As mentioned in the last section, we perform a number of different design tasks at different levels of abstraction throughout this book: creating requirements and specifications, architecting the system, designing code, and designing tests. It is often helpful to conceptualize these tasks in diagrams. Luckily, there is a visual language that can be used to capture all these design tasks: the *Unified Modeling Language (UML)*.

UML was designed to be useful at many levels of abstraction in the design process. UML is useful because it encourages design by successive refinement and progressively adding detail to the design, rather than rethinking the design at each new level of abstraction. UML is an *object-oriented* modeling language. We will see precisely what we mean by an object in just a moment, but object-oriented design emphasizes two concepts of importance:

■ It encourages the design to be described as a number of interacting objects, rather than a few large monolithic blocks of code.

■ At least some of those objects will correspond to real pieces of software or hardware in the system. We can also use UML to model the outside world that interacts with our system, in which case the objects may correspond to people or other machines. It is sometimes important to implement something we think of at a high level as a single object using several distinct pieces of code or to otherwise break up the object correspondence in the implementation. However, thinking of the design in terms of actual objects helps us understand the natural structure of the system. Object-oriented (often abbreviated OO) specification can be seen in two complementary ways:

• Object-oriented specification allows a system to be described in a way that closely models real-world objects and their interactions.

• Object-oriented specification provides a basic set of primitives that can be used to describe systems with particular attributes, irrespective of the relationships of those systems' components to real-world objects. Both views are useful. At a minimum, object-oriented specification is a set of linguistic mechanisms. In many cases, it is useful to describe a system in terms of real-world analogs. However, performance, cost, and so on may dictate that we change the specification to be different in some ways from the real-world elements we are trying to model and implement. In this case, the object-oriented specification mechanisms are still useful. What is the relationship between an object-oriented specification language may not be executable. But both object-oriented specification and programming languages provide similar basic methods for structuring large systems.

Unified Modeling Language (UML)—the acronym is the name is a large language, and covering all of it is beyond the scope of this book. In this section, we introduce only a few basic concepts. In later chapters, as we need a few more UML concepts, we introduce them to the basic modeling elements introduced here. Because UML is so rich, there are many graphical elements in a UML diagram. It is important to be careful to use the correct drawing to describe something—for instance, UML distinguishes between arrows with open and filled-in arrowheads, and solid and broken lines. As you become more familiar with the language, uses of the graphical primitives will become more natural to you. We also won't take a strict object-oriented approach. We may not always use objects for certain elements of a design—in some cases, such as when taking particular aspects of the

implementation into account, it may make sense to use another design style. However, object-oriented design is widely applicable, and no designer can consider himself or herself design literate without understanding it.

#### **Structural Description**

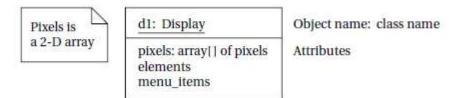

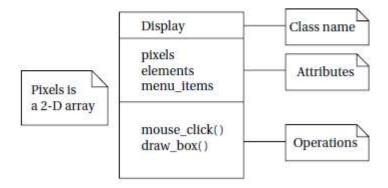

By *structural description*, we mean the basic components of the system; we will learn how to describe how these components act in the next section. The principal component of an object-oriented design is, naturally enough, the *object*. An object includes a set of attributes that define its internal state. When implemented in a programming language, these attributes usually become variables or constants held in a data structure. In some cases, we will add the type of the attribute after the attribute name for clarity, but we do not always have to specify a type for an attribute. An object describing a display (such as a CRT screen) is shown in UML notation in Figure. The text in the folded-corner page icon is a *note*; it does not correspond to an object in the system and only serves as a comment. The attribute is, in this case, an array of pixels that holds the contents of the display. The object is identified in two ways: It has a unique name, and it is a member of a *class*. The name is underlined to show that this is a description of an object and not of a class. A class is a form of type definition—all objects derived from the same class have the same characteristics, although their attributes may have different values. A class defines the attributes that an object may have. It also defines the *operations* that determine how the object interacts with the rest of the world. In a programming language, the operations would become pieces of code used to manipulate the object. The UML description of the Display class is shown in Figure. The class has the name that we saw used in the d1 object since d1 is an instance of class *Display*. The *Display* class defines the *pixels* attribute seen in the object; remember that when we instantiate the class an object, that object will have its own memory so that different objects of the same class have their own values for the attributes. Other classes can examine and modify class attributes; if we have to do something more complex than use the attribute directly, we define a behavior to perform that function.

An object in UML notation.

A class defines both the *interface* for a particular type of object and that object's *implementation*. When we use an object, we do not directly manipulate its attributes—we can only read or modify the object's state through the operations that define the interface to the object. (The implementation includes both the attributes and whatever code is used to implement the operations.) As long as we do not change the behavior of the object seen at the interface, we can change the implementation as much as we want. This lets us improve the system by, for example, speeding up an operation or reducing the amount of memory required without requiring changes to anything else that uses the object.

Clearly, the choice of an interface is a very important decision in object-oriented design. The proper interface must provide ways to access the object's state (since we cannot directly see the attributes) as well as ways to update the state. We need to make the object's interface general enough so that we can make full use of its capabilities. However, excessive generality often makes the object large and slow. Big, complex interfaces also make the class definition difficult for designers to understand and use properly. There are several types of *relationships* that can exist between objects and classes:

- *Association* occurs between objects that communicate with each other but have no ownership relationship between them.

- *Aggregation* describes a complex object made of smaller objects.

- *Composition* is a type of aggregation in which the owner does not allow access to the component objects.

- *Generalization* allows us to define one class in terms of another.

The elements of a UML class or object do not necessarily directly correspond to statements in a programming language—if the UML is intended to describe something more abstract than a program, there may be a significant gap between the contents of the UML and a program implementing it. The attributes of an object do not necessarily reflect variables in the object. An attribute is some value that reflects the current state of the object. In the program implementation, that value could be computed from some other internal variables. The behaviors of the object would, in a higher-level specification, reflect the basic things that can be done with an object. Implementing all these features may require breaking up a behavior into several smaller behaviors—for example, initialize the object before you start to change its internal state-derived classes.

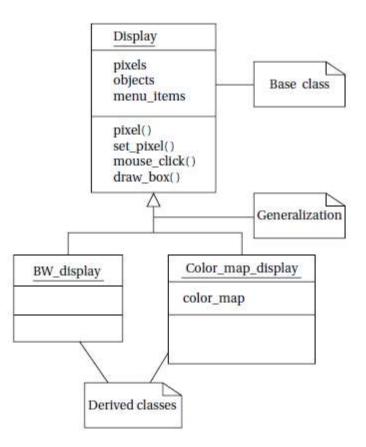

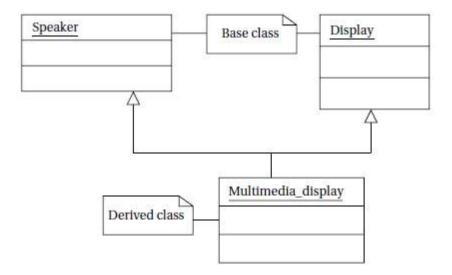

Unified Modeling Language, like most object-oriented languages, allows us to define one class in terms of another. An example is shown in Figure, where we **derive** two particular types of displays. The first, *BW\_ display*, describes a black and- white display. This does not require us to add new attributes or operations, but we can specialize both to work on one-bit pixels. The second, *Color\_map\_display*, uses a graphic device known as a color map to allow the user to select from a

large number of available colors even with a small number of bits per pixel. This class defines a *color\_map* attribute that determines how pixel values are mapped onto display colors. A *derived class* inherits all the attributes and operations from its *base class*. In this class, *Display* is the base class for the two derived classes. A derived class is defined to include all the attributes of its base class.

This relation is transitive—if *Display* were derived from another class, both *BW\_display* and *Color\_map\_display* would inherit all the attributes and operations of *Display's* base class as well. Inheritance has two purposes. It of course allows us to succinctly describe one class that shares some characteristics with another class. Even more important, it captures those relationships between classes and documents them. If we ever need to change any of the classes, knowledge of the class structure helps us determine the reach of changes—for example, should the change affect only *Color\_map\_display* objects or should it change all Display objects?

**Unified Modeling Language** considers inheritance to be one form of generalization. A generalization relationship is shown in a UML diagram as an arrow with an open (unfilled) arrowhead. Both *BW\_display* and *Color\_map\_display* are specific

versions of *Display*, so *Display* generalizes both of them. UML also allows us to define *multiple inheritance*, in which a class is derived from more than one base class. (Most object-oriented programming languages support multiple inheritance as well.) An example of multiple inheritance is shown in Figure; we have omitted the details of the classes' attributes and operations for simplicity. In this case, we have created a *Multimedia\_display* class by combining the *Display* class with a *Speaker* class for sound. The derived class inherits all the attributes and operations of both its base classes, *Display* and *Speaker*. Because multiple inheritance causes the sizes of the attribute set and operations to expand so quickly, it should be used with care.

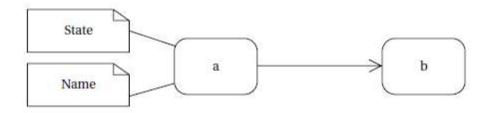

A *link* describes a relationship between objects; association is to link as class is to object. We need links because objects often do not stand alone; associations let us capture type information about these links. Figure 1.9 shows examples of links and an association. When we consider the actual objects in the system, there is a set of messages that keeps track of the current number of active messages (two in this example) and points to the active messages. In this case, the link defines the *contains* relation. When generalized into classes, we define an association between the message set class and the message class. The association is drawn as a line between the two labeled with the name of the association, namely, *contains*. The ball and the number at the message class end indicate that the message set may include zero or more message objects. Sometimes we may want to attach data to the links themselves; we can specify this in the association by attaching a class-like box to the association's edge, which holds the association's data.

Typically, we find that we use a certain combination of elements in an object or class many times. We can give these patterns names, which are called *stereotypes*

| message                                | msgl: message     |

|----------------------------------------|-------------------|

| msg = msg1                             | set1: message se  |

| length = $1102$                        | message set       |

| msg2:                                  | message count = 2 |

|                                        |                   |

| message                                |                   |

| message<br>msg = msg2<br>length = 2114 |                   |

| message                              | contains | message set    |

|--------------------------------------|----------|----------------|

| msg: ADPCM_stream<br>length: integer | 0* 1     | count: integer |

Association between classes

Links and association.

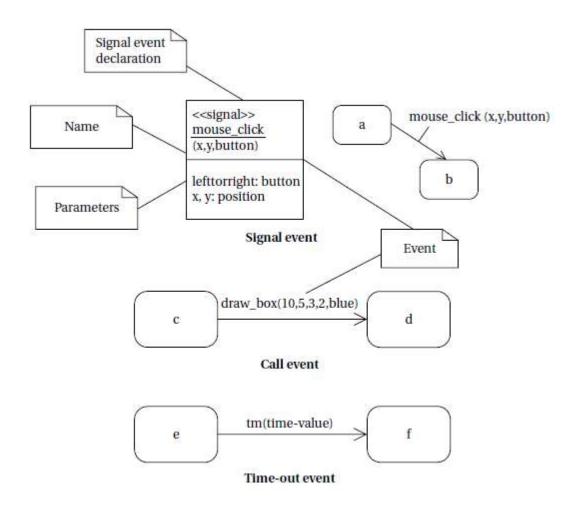

in UML. A stereotype name is written in the form <<signal>>. Figure shows a stereotype for a signal, which is a communication mechanism.

## **Behavioral Description**

We have to specify the behavior of the system as well as its structure. One way to specify the behavior of an operation is a *state machine*. Figure shows UML states; the transition between two states is shown by a skeleton arrow. These state machines will not rely on the operation of a clock, as in hardware; rather, changes from one state to another are triggered by the occurrence of *events*.

An event is some type of action. The event may originate outside the system, such as a user pressing a button. It may also originate inside, such as when one routine finishes its computation and passes the result on to another routine. We will concentrate on the following three types of events defined by UML, as illustrated in Figure.

• A *signal* is an asynchronous occurrence. It is defined in UML by an object that is labeled as a  $\langle\langle signal \rangle\rangle$ . The object in the diagram serves as a declaration of the event's existence. Because it is an object, a signal may have parameters that are passed to the signal's receiver.

• A *call event* follows the model of a procedure call in a programming language.

• A *time-out event* causes the machine to leave a state after a certain amount of time. The label tm(time-value) on the edge gives the amount of time after which the transition occurs. A time-out is generally implemented with an

external timer. This notation simplifies the specification and allows us to defer implementation details about the time-out mechanism. We show the occurrence of all types of signals in a UML diagram in the same way— as a label on a transition.

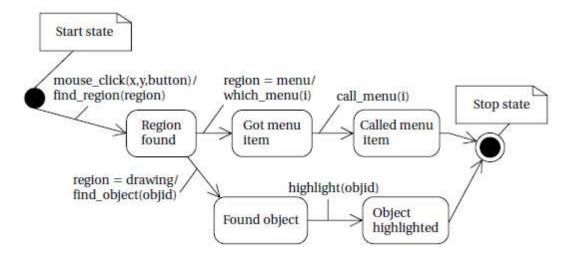

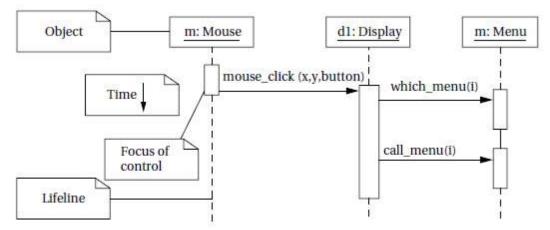

Let's consider a simple state machine specification to understand the semantics of UML state machines. A state machine for an operation of the display is shown in Figure. The start and stop states are special states that help us to organize the flow of the state machine. The states in the state machine represent different conceptual operations. In some cases, we take conditional transitions out of states based on inputs or the results of some computation done in the state. In other cases, we make an unconditional transition to the next state. Both the unconditional and conditional transitions make use of the call event. Splitting a complex operation into several states helps document the required steps, much as subroutines can be used to structure code. It is sometimes useful to show the sequence of operations over time, particularly when several objects are involved. In this case, we can create a sequence diagram, like the one for a mouse click scenario shown in Figure. A sequence diagram is somewhat similar to a hardware timing diagram, although the time flows vertically in a sequence diagram, whereas time typically flows horizontally in a timing diagram. The sequence diagram is designed to show a particular scenario or choice of events—it is not convenient for showing a number of mutually exclusive possibilities. In this case, the sequence shows what happens when a mouse click is on the menu region. Processing includes three objects shown at the top of the diagram. Extending below each object is its *lifeline*, a dashed line that shows how long the object is alive. In this case, all the objects remain alive for the entire sequence, but in other cases objects may be created or destroyed during processing. The boxes

along the lifelines show the *focus of control* in the sequence, that is, when the object is actively processing. In this case, the mouse object is active only long enough to create the *mouse\_click* event. The display object remains in play longer; it in turn uses call events to invoke the menu object twice: once to determine which menu item was selected and again to actually execute the menu call. The find\_region() call is internal to the display object, so it does not appear as an event in the diagram.

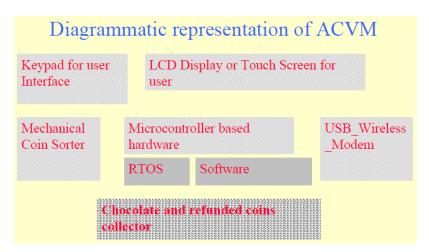

### **DESIGN PROCESS EXAMPLES** Automatic Chocolate vending machine

Keypad on the top of the machine. LCD display unit on the top of the machine. It displays menus, text entered into the ACVM and pictograms, welcome, thank and other messages. Graphic interactions with the machine. Displays time and date. Delivery slot so that child can collect the chocolate and coins, if refunded. Internet connection port so that owner can know status of the ACVM sales from remote.

## **ACVM Hardware units**

Microcontroller or ASIP (Application Specific Instruction Set Processor). RAM for storing temporary variables and stack. ROM for application codes and RTOS codes for scheduling the tasks. Flash memory for storing user preferences, contact data, user address, user date of birth, user identification code, answers of FAQs. Timer and Interrupt controller. A

TCP/IP port (Internet broadband connection) to the ACVM for remote control and for getting ACVM status reports by owner. ACVM specific hardware. Power supply.

## **ACVM Software components**

- \_ Keypad input read

- \_ Display

- \_ Read coins

- \_ Deliver chocolate

- \_ TCP/IP stack processing

- \_ TCP/IP stack communication

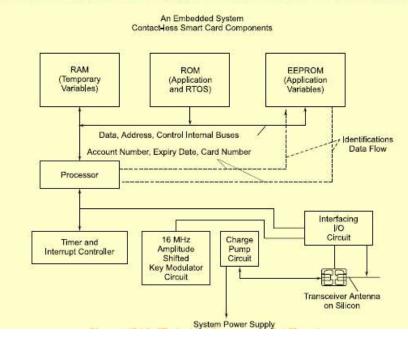

## Smart Card

Smart card- a plastic card in ISO standard dimensions, 85.60 mm x 53.98 x 0.80 mm.

- \_ Embedded system on a card.

- \_ SoC (System-On-Chip).

\_ ISO recommended standards are ISO7816 (1 to 4) for host-machine contact based cards and ISO14443 (Part A or B) for the contact-less cards.

\_ Silicon chip is just a few mm in size and is concealed in-between the layers. Its very small size protects the card from bending

## Embedded hardware components in a contact less smart card

## **Embedded hardware components**

\_ Microcontroller or ASIP (Application Specific Instruction Set Processor)

- \_ RAM for temporary variables and stack

- \_ ROM for application codes and RTOS codes for scheduling the tasks

\_ EEPROM for storing user data, user address, user identification codes, card number and expiry date

\_ Timer and Interrupt controller

\_ A carrier frequency ~16 MHz generating circuit and Amplitude Shifted Key (ASK)

\_ Interfacing circuit for the I/Os

\_ Charge pump

## ROM

Fabrication key, Personalization key An utilization lock.

\_ RTOS and application using only the logical addresses

### **Embedded Software**

\_ Boot-up, Initialisation and OS programs

- \_ Smart card secure file system

- \_ Connection establishment and termination

- \_ Communication with host

- \_ Cryptography

- \_ Host authentication

- \_ Card authentication

\_ Addition parameters or recent new data sent by the host (for example, present balance left).

## **Smart Card OS Special features**

\_ Protected environment.

- \_ Every method, class and run time libraryshould be scalable.

- \_ Code-size generated be optimum.

- \_ Memory should not exceed 64 kB memory.

\_ Limiting uses of specific data types; multidimensional arrays, long 64-bit integer and floating points

## **Smart Card OS Limiting features**

\_ Limiting uses of the error handlers, exceptions, signals, serialization, debugging and profiling. [Serialization means process of converting an object is converted into a data stream for transferring it to network or from one process to another. At receiver end there is de-serialization Smart Card OS File System and Classes

\_ Three-layered file system for the data.

\_ Master file to store all file headers.

\_ Dedicated file to hold a file grouping and headers of the immediate successor elementary files of the group.

- \_ Elementary file to hold the file header and its file data.

- \_ Fixed-length or variable-file length management

\_ Classes for the network, sockets, connections, data grams, character-input output and streams, security management, digital-certification, symmetric and asymmetric keys-based cryptography and digital signatures..

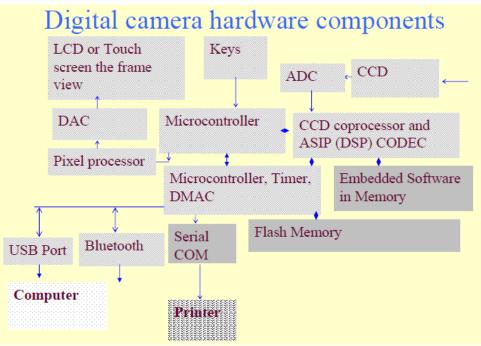

## **Digital Camera**

#### A typical Camera

\_ 4 M pixel/6 M pixel still images, clear visual display (ClearVid) CMOS sensor, 7 cm wide LCD photo display screen, enhanced imaging processor, double anti blur solution and high-speed processing engine, 10X optical and 20X digital zooms

\_ Record high definition video-clips. It therefore has speaker microphone(s) for high quality recorded sound.

\_ Audio/video Out Port for connecting to a TV/DVD player.

#### Arrangements

\_ Keys on the camera.

\_ Shutter, lens and charge coupled device (CCD) array sensors

\_ Good resolution photo quality LCD display unit

\_ Displays text such as image-title, shooting data and time and serial number. It displays messages. It displays the GUI menu when user interacts with the camera.

\_ Self-timer lamp for flash.

#### **Internal units**

\_ Internal memory flash to store OS and embedded software and limited number of image files

\_ Flash memory stick of 2 GB or more for large storage.

\_ Universal Serial Bus (USB), Bluetooth and serial COM port for connecting it to computer, mobile and printer. LCD screen to display frame view.

\_ Saved images display using the navigation keys.

\_ Frame light falls on the CCD array, which through an ADC transmits the bits for each pixel in each row in the frame and for the dark area pixels in each row for offset correction in CCD signaled light intensities for each row.

\_ The CCD bits of each pixel in each row and column are offset corrected by CCD signal processor (CCDSP).

#### ASIP and Single purpose processors

\_ For Signals compression using a JPEG CODEC and saved in one jpg file for each frame.

\_ For DSP for compression using the discrete cosine transformations (DCTs) and decompression.

\_ For DCT Huffman coding for the JPEG compression.

\_ For decompression by inverse DCT before the DAC sends input for display unit through pixel processor.

\_ Pixel processor (for example, image contrast, brightness, rotation, translation, color adjustment)

#### **Digital Camera Hardware units**

\_ Microcontroller or ASIP (Application Specific Instruction Set Processor)

\_ Multiple processors (CCDSP, DSP, Pixel Processor and others)

\_ RAM for storing temporary variables and stack

\_ ROM for application codes and RTOS codes for scheduling the tasks Timer, Flash memory for storing user preferences, contact data, user address, user date of birth, user identification code, ADC, DAC and Interrupt controller

\_ The DAC gets the input from pixel processor, which gets the inputs from JPEG file for the saved images and also gets input directly from the CCDSP through pixel processor or the frame in present view

\_ USB controller Direct Memory Access controller

\_LCD controller

\_ Battery and external charging circuit

## **Digital Camera Software components**

- \_ CCD signal processing for off-set correction

- \_ JPEG coding

- \_ JPEG decoding

- \_ Pixel processing before display

- \_ Memory and file systems

- \_ Light, flash and display device drivers

\_ LCD, USB and Bluetooth Port device- drivers for port operations for display, printer and Computer communication control

Light, flash and display device drivers CCD signal processing JPEG coding JPEG decoding Pixel co-processing LCD and USB Port device drivers LCD, Bluetooth COM and USB Port device drivers

## UNIT-II THE 8051 ARCHITECTURE

#### **INTRODUCTION TO MICRO CONTROLLERS**

#### **INTRODUCTION:**

We have noticed that Microprocessor is just not self-sufficient, and it requires other components like memory and input/output devices to form a minimum workable system configuration. To have all these components in a discrete form and to assemble them on a PCB is usually not an affordable solution for the following reasons:

- 1) The overall system cost of a microprocessor based system built around a CPU, memory and other peripherals is high as compared to a microcontroller based system.

- 2) A large sized PCB is required for assembling all these components, resulting in an enhanced cost of the system.

- Design of such PCBs requires a lot of effort and time and thus the overall product design requires more time.

- 4) Due to the large size of the PCB and the discrete components used, physical size of the product is big and hence it is not handy.

- 5) As discrete components are used, the system is not reliable nor is it easy to troubleshoot such a system.

Considering all these problems, Intel decided to integrate a microprocessor along with I/O ports and minimum memory into a single package. Another frequently used peripheral, a programmable timer, was also integrated to make this device a self-sufficient one. This device which contains a microprocessor and the above mentioned components has been named a microcontroller. A microcontroller is a microprocessor with integrated peripherals. Design with microcontrollers has the following advantages:

- 1. As the peripherals are integrated into a single chip, the overall system cost is very low.

- 2. The size of the product is small as compared to the microprocessor based systems thus very handy.

- 3. The system design requires very little efforts and is easy to troubleshoot and maintain.

- 4. As the peripherals are integrated with a microprocessor, the system is more reliable.

- 5. Though a microcontroller may have on-chip RAM, ROM and I/O ports, additional RAM, ROM and I/O ports may be interfaced externally, if required.

6. The microcontrollers with on-chip ROM provide a software security feature which is not available with microprocessor based systems using ROM/EPROM.

However, in case of a larger system design, which requires more number of I/O ports and more memory capacity, the system designer may interface external I/O ports and memory with the system. In such cases, the microcontroller based systems are not so attractive as they are in case of the small dedicated systems. Figure 17.1 shows a typical microcontroller internal block diagram.

As a microcontroller contains most of the components required to form a microprocessor system, it is sometimes called a single chip microcomputer, since it also has the ability to easily implement simple control functions.

#### **OVERVIEW OF 8051 MICRO CONTROLLER**

Let us look at Intel's 8-bit microcontroller family, popularly known as MCS-51 family. The earlier versions of Intel's microcontrollers do not have on-chip EPROM. 8031 was one such microcontroller from Intel, followed by the 8051 family. 8751 was the first microcontroller version with on-chip EPROM, followed by a number of 8751 versions with slight modifications. Recently, an electrically programmable and erasable version of 8051, named as 8951, has been introduced. Table shows the comparison between different versions of 8051. All these members of the 8051 family have identical instruction set and similar architecture with slight variations as shown in Table.

#### **ARCHITECTURE OF 8051**

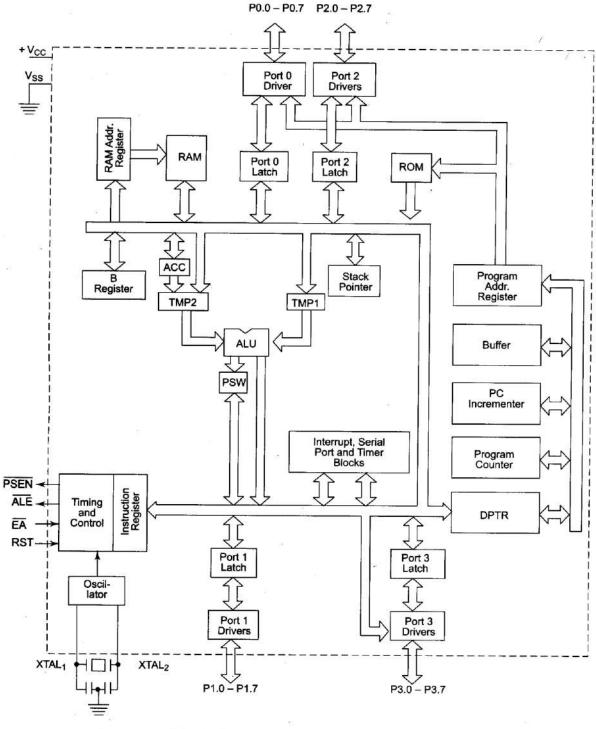

The internal architecture of 8051 is presented in Fig.

The functional description of each block is presented briefly below.

Accumulator (ACC): The accumulator register (ACC or A) acts as an operand register, in case of some instructions. This may either be implicit or specified in the instruction.

**B Register:** This register is used to store one of the operands for multiply and divide instructions. In other instructions, it may just be used as a scratch pad.

Program Status Word (PSW): This set of flags contains the status information.

**Stack Pointer (SP):** This 8-bit wide register is incremented before the data is stored onto the stack using push or call instructions. This register contains 8-bit stack top address. The

stack may be defined anywhere in the on-chip 128-byte RAM. After reset, the SP register is initialised to 07. After each write to stack operation, the 8-bit contents of the operand are stored onto the stack, after incrementing the SP register by one. Thus if SP contains 07 H, the forthcoming PUSH operation will store the data at address 08H in the internal RAM. The SP content will be incremented to 08.

Fig. 17.2 8051 Block Diagram (Intel Corp.)

**Data Pointer (DTPR):** This 16-bit register contains a higher byte (DPH) and the lower byte (DPL) of a 16-bit external data RAM address. It is accessed as a 16-bit register or two 8-bit registers as specified above.

Port 0 to 3 Latches and Drivers: These four latches and driver pairs are allotted to each

of the four on-chip I/O ports. Using the allotted addresses, the user can communicate with these ports. These are identified as P0, PI, P2 and P3.

**Serial Data Buffer:** The serial data buffer internally contains two independent registers. One of them is a transmit buffer which is necessarily a parallel-in serial-out register. The other is called receive buffer which is a serial-in parallel-out register. The serial data buffer is identified as SBUF.

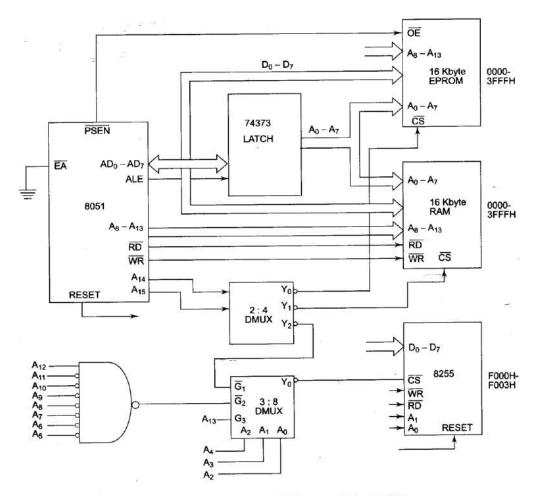

**Timer Registers:** These two 16-bit registers can be accessed as their lower and upper bytes. For example, TL0 represents the lower byte of the timing register 0, while TH0 represents higher bytes of the timing register 0. Similarly, TL1 and TH1 represent lower and higher bytes of timing register 1.

**Control Registers:** The special function registers IP, IE, TMOD, TCON, SCON and PCON contain control and status information for interrupts, timers/counters and serial port. **Timing and Control Unit:** This unit derives all the necessary timing and control signals required for the internal operation of the circuit. It also derives control signals required for controlling the external system bus.

**Oscillator:** This circuit generates the basic timing clock signal for the operation of the circuit using crystal oscillator.

**Instruction Register:** This register decodes the opcode of an instruction to be executed and gives information to the timing and control unit to generate necessary signals for the execution of the instruction.

**EPROM and Program Address Register:** These blocks provide an on-chip EPROM/PROM and a mechanism to internally address it. Note that EPROM is not available in all 8051 versions.

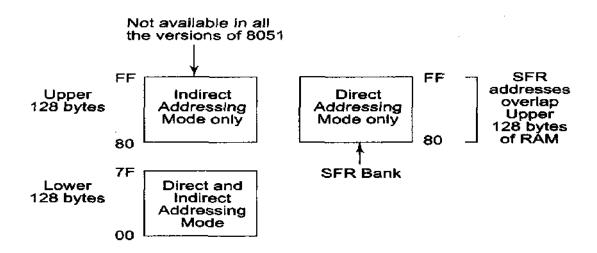

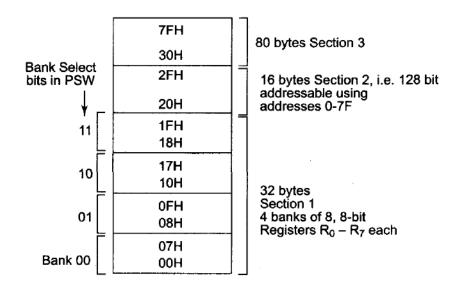

**RAM and RAM Address Register:** These blocks provide internal 128 bytes of RAM and a mechanism to address it internally.

**ALU:** The arithmetic and logic unit performs 8-bit arithmetic and logical operations over the operands held by the temporary registers TMP1 and TMP2. Users cannot access these temporary registers.

**SFR Register Bank:** This is a set of special function registers, which can be addressed using their respective addresses which lie in the range 80H to FFH.

Finally, the interrupt, serial port and timer units control and perform their specific functions under the control of the timing and control unit.

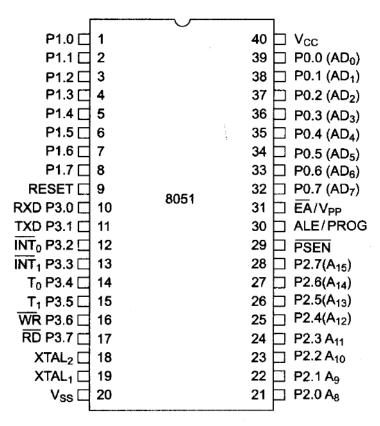

#### **PIN DESCRIPTIONS OF 8051**

8051 is available in a 40-pin plastic and ceramic DIP packages. The pin diagram of 8051 is shown in Fig. 17.3 followed by description of each pin.

Fig. 17.3 8051 Pin Configuration (Intel Corp.)

V<sub>cc</sub> This is a +5 V supply voltage pin

V<sub>ss</sub> This is a return pin for the supply.

**RESET** The reset input pin resets the 8051, only when it goes high for two or more machine cycles. For a proper reinitialization after reset, the clock must be running.

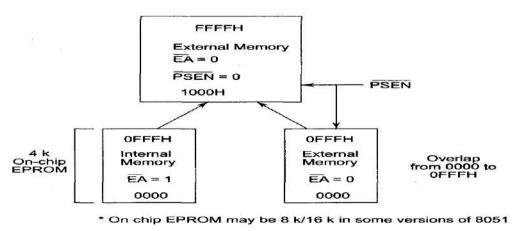

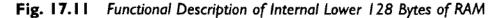

**ALE/PROG** The address latch enable output pulse indicates that the valid address bits are available on their respective pins. This ALE signal is valid only for external memory accesses. Normally, the ALE pulses are emitted at a rate of one-sixth of the oscillator frequency. This pin acts as program pulse input during on-chip EPROM programming. ALE may be used for external timing or clocking purpose. One ALE pulse is skipped during each access to external data memory.

$\overline{\mathbf{EA}} / \mathbf{V_{pp}}$  External access enable pin, if tied low, indicates that the 8051 can address external program memory. In other words, the 8051 can execute a program in external memory, only if  $\overline{\mathbf{EA}}$  is tied low.

For execution of programs in internal memory, the  $\overline{EA}$  must be tied high. This pin also receives 21 volts for programming of the on-chip EPROM.

**PSEN** Program store enable is an active-low output signal that acts as a strobe to read the external program memory. This goes low during external program memory accesses.

**Port 0 (P0.0-P0.7)** Port 0 is an 8-bit bidirectional bit addressable I/O port. This has been allotted an address in the SFR address range. Port 0 acts as multiplexed address/data lines during external memory access, i.e. when  $\overline{EA}$  is low and ALE emits a valid signal. In case of controllers with on-chip EPROM, Port 0 receives code bytes during programming of the internal EPROM.

**Port 1 (P1.0-P1.7)** Port 1 acts as an 8-bit bidirectional bit addressable port. This has been allotted an address in the SFR address range.

**Port 2 (P2.0-P2.7)** Port 2 acts as 8-bit bidirectional bit addressable I/O port. It has been allotted an address in the SFR address range of 8051. During external memory accesses, port 2 emits higher eight bits of adress ( $A_8$ - $A_{15}$ ) which are valid, if ALE goes high and EA is low. P2 also receives higher order address bits during programming of the on-chip EPROM.

**Port 3 (P3.0-P3.7)** Port 3 is an 8-bit bidirectional bit addressable I/O port which has been allotted an address in the SFR address range of 8051. The port 3 pins also serve the alternative functions as listed in the Table 17.2.

$\mathbf{XTAL_1}$  and  $\mathbf{XTAL_2}$  There is an inbuilt oscillator which derives the necessary clock frequency for the operation of the controller.  $\mathbf{XTAL_1}$  is the input of amplifier and  $\mathbf{XTAL_2}$  is the output of the amplifier. A crystal is to be connected externally between these two pins to complete the feedback path to start oscillations. The controller can be operated on an external clock. In this case the external clock is fed to the controller at pin  $\mathbf{XTAL_2}$  and  $\mathbf{XTAL_1}$  pin should be grounded. Commercially available versions of 8051 run on 12 MHz to 16 MHz frequency.

#### **REGISTER SET OF 8051**

8051 has two 8-bit registers, registers A and B, which can be used to store operands, as allowed by the instruction set. Internal temporary registers of 8051 are not user accessible. Including these A and B registers, 8051 has a family of special purpose registers known as, Special Function Registers (SFRs). There are, in total, 21-bit addressable, 8-bit registers. ACC (A), B, PSW, PO, PI, P2, P3, IP, IE, TCON and SCON are all 8-bit, bit-addressable registers. The remaining registers, namely, SP, DPH, DPL, TMOD, TH0, TL0, TH1, TL1, SBUF and PCON registers are to be addressed as bytes, i.e. they are not bit-addressable. The registers DPH and DPL are the higher and lower bytes of a 16-bit register DPTR, i.e. data pointer, which is used for accessing external data memory. Starting 32-bytes of on-chip RAM may be used as general purpose registers. They have been allotted addresses in the range from 0000H to 001FH. These 32, 8-bit registers are divided into four groups of 8 registers each, called register banks. At a time only one of these four groups, i.e. banks can be accessed. The register bank to be accessed can be

selected using the RS1 and RS0 bits of an internal register called program status word.

The registers THO and TLO form a 16-bit counter/timer register with H indicating the upper byte and L indicating the lower byte of the 16-bit timer register T0. Similarly, TH1 and TLl form the 16-bit count for the timer Tl. The four port latches are represented by P0, P1, P2 and P3. Any communication with these ports is established using the SFR addresses to these registers. Register SP is a stack pointer register. Register PSW is a flag register and contains status information. Register IP can be programmed to control the interrupt priority. Register IE can be programmed to control interrupts, i.e. enable or disable the interrupts. TCON is called timer/counter control register. Some of the bits of this register are used to turn the timers on or off. This register also contains interrupt control flags for external interrupts  $\overline{INT_0}$  and  $\overline{INT_1}$ . The register TMOD is used for programming the modes of operation of the timers/counters. The SCON register is a serial port mode control register and is used to control the operation of the serial port. The SBUF register acts as a serial data buffer for transmit and receive operations. The PCON register is called power control register. This register contains power down bit and idle bit which activate the power down mode and idle mode in 80C51BH. There are two power saving modes of operation provided in the CHMOS version, namely, idle mode and power down mode.